# 3D Silicon Coincidence Avalanche Detector (3D-SiCAD): preliminary results on charged particle detection

M. M. Vignetti (a)\*, F. Calmon (a), P. Pittet (a), G. Pares (b), R. Cellier (a), L. Quiquerez (a), T. Chaves de Albuquerque (a) \*\*, E. Bechetoille (c), E Testa (c), J.-P. Lopez (c), D. Dauvergne (d), J. Hérault (e), A. Savoy-Navarro (f)

(a) Institut des Nanotechnologies de Lyon, Villeurbanne (France), (b) CEA-LETI, Grenoble (France), (c) Institut de Physique Nucléaire de Lyon, Villeurbanne (France), (d) Laboratoire de Physique Subatomique & Cosmologie, Grenoble (France), (e) Centre Antoine Lacassagne, Nice (France), (f) Laboratoire d'AstroParticule et Cosmologie, Université Paris-Diderot, Paris (France)

(\*) Supported by the 2012-FP7-ITN, nr 317446, INFIERI EU programme. (\*\*) Supported by Auvergne Rhone Alpes region (ARC6 research programme)

#### Introduction

This study aims at developing new charged particle detectors based on recent advances in 3D CMOS microelectronics for high energy physics and emerging medical applications such as hadrontherapy and Proton Computed Tomography (pCT). These 3D CMOS integrated detectors are based on two aligned avalanche diodes operated in Geiger mode with on-chip coincidence detection. Such detectors will provide an alternative to existing technologies with expected advantages in terms of limit of detection (very low noise count rate resulting from on chip coincidence detection), spatial (pixel size < 50x50µm²) and timing (10-100ps with an hold-off time of 10-100ps) resolutions, high counting rate (>10MHz), scalable solution (with detection areas from tens of µm² to hundreds of mm²), co-integrated low-complexity readout electronics (digital), low material budget, compact and efficient implementation based on standard CMOS technology.

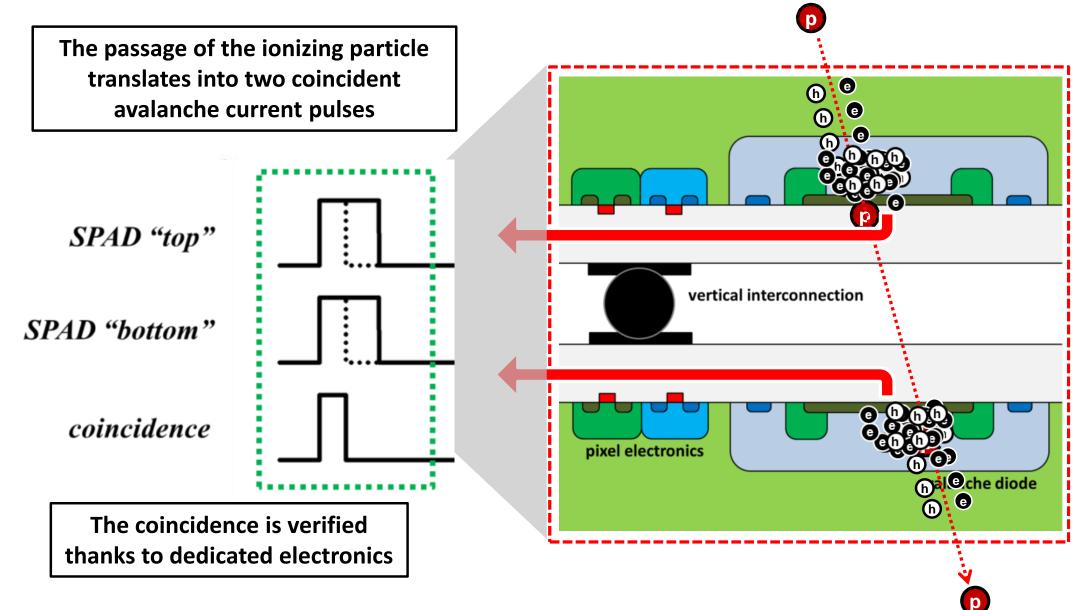

#### A coincidence-based avalanche detector

#### 3D-SICAD: a novel position sensitive detector for charged particle tracking, exploiting modern 3D-integration techniques

- The passage of an ionizing particle through the pair of vertically aligned avalanche diodes triggers a breakdown process in each cell, producing two substantially coincident electrical signals

- The detection of a coincidence event allows discrimination of the signal produced by an incoming ionizing particle from background ultra-violet, visible and near-infrared photons and thermal dark counts

The avalanche diode working above the breakdown voltage (Geiger mode) is called SPAD (Single Photon Avalanche Diode)

#### Avalanche diode design in a commercial CMOS technology

TCAD study to choose the correct architecture (AMS HV-CMOS 0.35µm technology implementation)

Premature Edge Breakdown prevented

Expected low band-to-band tunneling generation thanks to a low n-type doping in the multiplication region

Already used for design of CMOS avalanche diodes showing good Dark Count Rate (DCR) levels

Diode architecture and CMOS technology eventually chosen according to a trade-off between performance (based on simulation and literature results) and affordable tape-out costs

# 3.044e+05 5.363e+05 4.022e+05

2.681e+05

1.341e+05

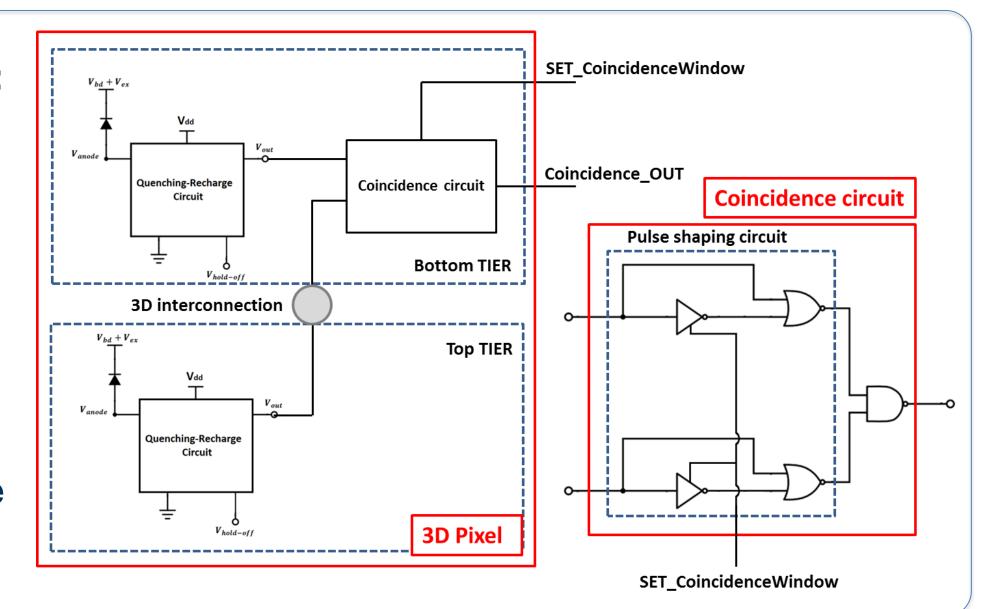

# Pixel electronics

# **3D-level pixel electronics:**

Check in a tunable timewindow, a coincidence between a pair of vertically aligned avalanche diodes.

> 3D-electronics minimizing the impact of possible parasitics introduced by the vertical interconnections.

**Electric Field (TCAD simulation)**

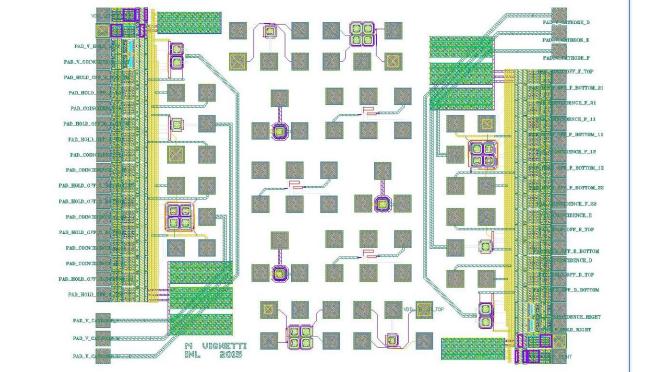

# Tape-out and 3D integration

A test-chip has been submitted for tape-out on April 2015 in a MPW run.

- Avalanche diode test structures

- Several 3D pixels cells for coincidence-based detection

- Small 2x2 matrix cells exploiting a hybrid coincidence-based detection:

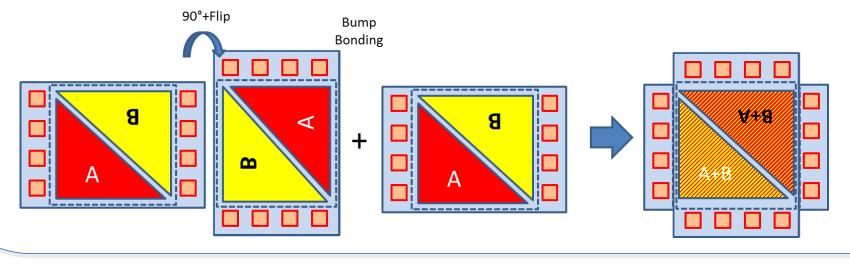

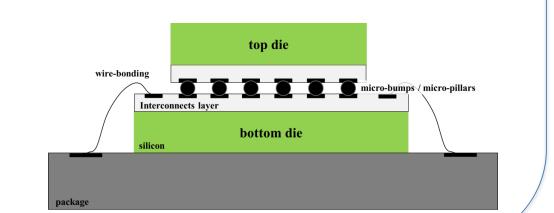

# 3D integration: flip-chip assembly

Flip-chip assembly of 2 identical test-chips after 90° rotation and flip of one test chip

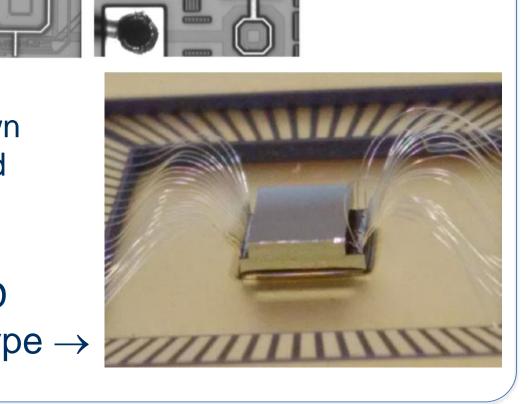

# Prototype realization

- a single pixel 3D-SiCAD cell

- a 2 × 2 matrix 3D-SiCAD cell

- test-structures for characterization purposes

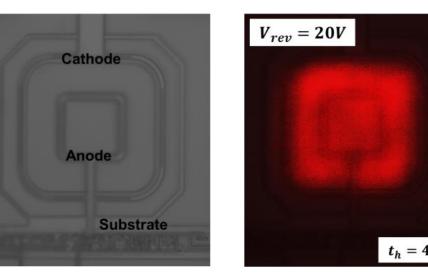

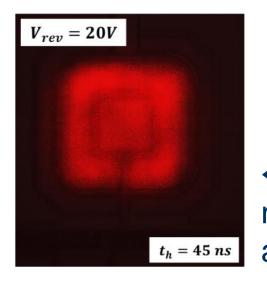

← pixel luminescence: no Premature Edge Breakdown and no hot spots are observed

Measured Dark Count Noise (DCR) median value of around 70  $Hz/\mu m^2$

3D-SiCAD stacked prototype →

DCR<sub>TOP</sub> = 88,5 kHz, DCR<sub>ROTTOM</sub> = 174,2 kHz

**Acknowledgment:**

CIME

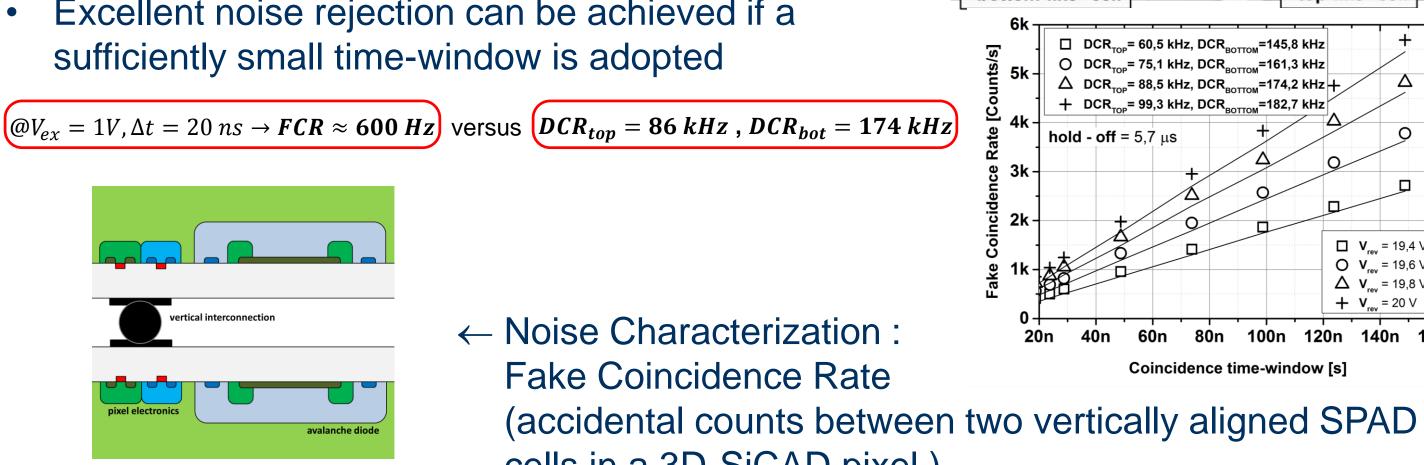

#### Benefit of the "coincidence-mode" operation

Validation of the "coincidence-mode" operation →

(coincidence counts between two adjacent SPAD pixels) and coincidence

- Measured data match very well with the predicted fake coincidence rate

- Excellent noise rejection can be achieved if a sufficiently small time-window is adopted

- cells in a 3D-SiCAD pixel)

- Measured data do not match with the predicted fake coincidence rate

- The recorded FCR is larger than expected

- FCR curves are shifted by a certain off-set related to the adopted reverse bias voltage

- The observed off-set can be explained by real coincidence counts due to optical cross-talk occurring between the two SPADs (can be avoided with metal layers between SPAD)

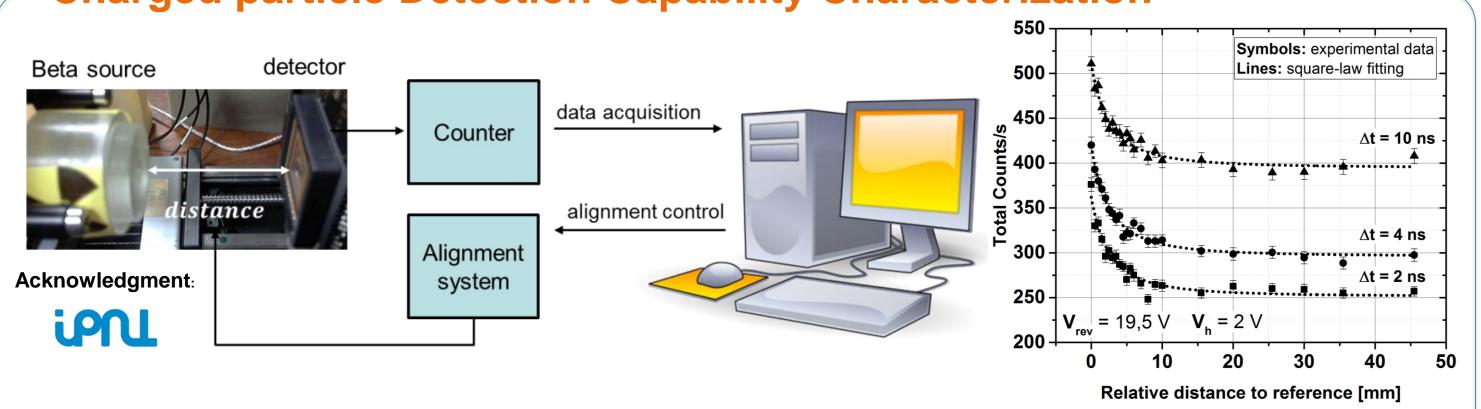

# Charged particle Detection Capability Characterization

- Results demonstrated particle detection capability for the realized 3D-SiCAD prototype (90Sr source)

- Fitting study of inverse square law data provided an estimation of the activity of the adopted <sup>90</sup>Sr source which is in excellent agreement with the nominal value

- The use of single SPAD devices would not allow distinguishing the signal of beta particle from the background counts in a acquisition time of "only" 10 seconds

Thinned top detector

(face active down)

**Bottom detector**

(active face up)

# **Perspectives**

<u>S</u> 12k − × 21,3V − ⇒ 21,8V

New prototype with state of the art 3D integration technology:

- Micro-bumps between the two stacked dies

- > Through Silicon Vias (TSV) to avoid wire-bondings

- Allow abutted 3D chips onto printed circuit board for large detector area

# References

[1] M. Vignetti et al. "Design guidelines for the integration of Geiger-mode avalanche diodes in standard CMOS technologies", Microelectronics Journal, vol. 46, no. 10, pp. 900-910, 2015.

[2] M. Vignetti et al. "A time-integration based quenching circuit for Geiger-mode avalanche diodes", 13th IEEE International New Circuits and Systems Conference (NEWCAS 2015), Grenoble (France), June 7-10, 2015.

[3] M. Vignetti et al. "Development of a 3D Silicon Coincidence Avalanche Detector for Charged Particle Tracking in Medical Applications", IEEE Nuclear Science Symposium and Medical Imaging Conference, Strasbourg (France), 29 October – 6 November 2016. [4] M. Vignetti et al. "New developments on Avalanche Pixels and R&D results" INFIERI 8th Workshop, Fermi Labs (USA), 17 - 21 Oct. 2016.