# PCI Express avec Qsys

Simon Deprez

14 février 2014

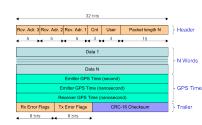

### L'électronique développée au LAPP

### Distribution du temps GPS

- Synchronisation des cartes

- Horodatage de données

#### Réseau de communication TOLM

- Liaisons optiques, longues distances

- Transmissions sous forme de paquets de données, configuration...

- On cherche a minimiser les temps de transfert et la latence

Simon Deprez 2 / 13

#### Utilisation de machines temps-réel

- Boucles de contrôle rapides

- Acquisition et traitement des données

#### Carte TOLM PCI

- 3 SFP

- 1 LEMO

- 1 RJ-45 (temps GPS)

- 1 PCI 64 bits 66 MHz

### Carte proto Démodulation Numérique

- 2 SFP, 1 LEMO, 1 RJ-45

- 1 PCle x8

Simon Deprez 3 / 13

# Validation de la carte prototype

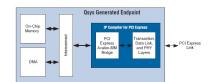

### Utilisation d'un reference design

- Accès en lecture et écriture

- Transferts DMA

#### Gestion du temps GPS

- Mesure de la latence

- Temps de transfert en lecture et écriture

- Tests longue durée

Simon Deprez 4 / 13

# PCI Express gen1x8 avec les outils Qsys

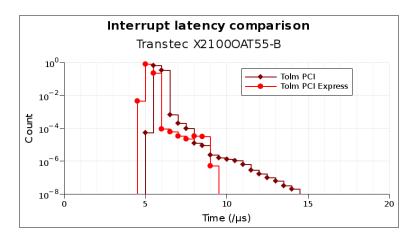

Meilleur temps de réponse aux interruptions que la TOLM PCI

Simon Deprez 5 / 13

## PCI Express gen1x8 avec les outils Qsys

Simon Deprez 6 / 13

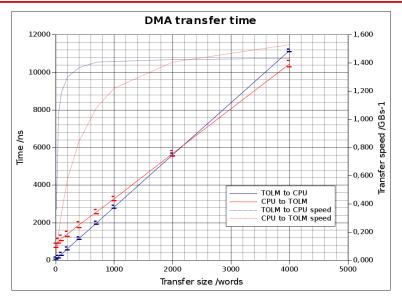

## PCI Express gen1x8 avec les outils Qsys

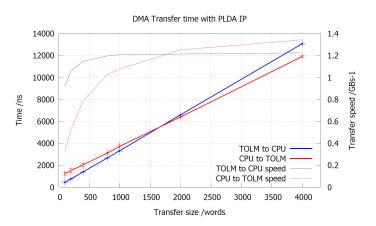

- Temps de transfert divisé par 2.7

- Vitesse de transfert limitée par le découpage des données en paquets (128 octets)

- Transferts full-duplex

- Performances suffisantes pour prendre le relai des cartes PCI-X 64bits 66MHz

Simon Deprez 7 / 13

### Test de l'IP EZDMA de PLDA

- Gestion des transferts bidirectionnels

- Utilisation de toutes les possibilités du hard block PCle

- Paquets de données jusqu'à 2kB (Max Payload Size)

Simon Deprez 8 / 13

### PCI Express gen1x8 avec l'IP PLDA

- La taille des paquets est limité à 128 octets par la machine.

- Temps de transfert supérieur.

Simon Deprez 9 / 13

# Possibilités des FPGA (PCIe Hard IP)

- Stratix IV

- Hard IP: gen2x8, 2kB payload

- Module Qsys: gen2x4, gen1x8, 256B payload

- Arria V

- Hard IP: gen2x4, 512B payload

- Module Qsys: gen2x4, gen1x8 256B payload

- Arria V GZ

- Hard IP: gen3x8, 2kB payload

- Module Qsys: gen3x4, gen2x8, 256B payload

Simon Deprez 10 / 13

Simon Deprez 11 / 13

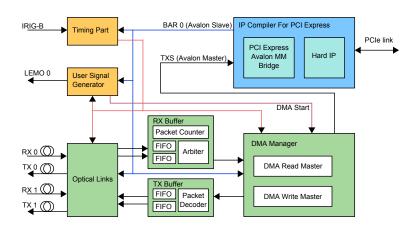

# **Transferts DMA**

- Utilisation de l'interface Avalon MM Slave de l'IP PCI Express

- Adaptation du système à la taille et la fréquence du bus pour optimiser les transferts.

- Contrôleur DMA sur mesure reprenant le fonctionnement de l'ancienne carte.

Simon Deprez 12 / 13

- Qsys permet de développer facilement un système basé sur une interface PCI Express

- Le développement de composants Qsys est nécessaire

- La structure d'un projet existant n'est pas toujours adaptée

Simon Deprez 13 / 13