#### **Electronics in TUNE**

- ASIC and WR

Prof. Yinong Liu

Department of Engineering Physics Tsinghua University, Beijing, China

2014.4

### The Laboratory

- TUNE The Laboratory of Nuclear Electronics at Tsinghua University, Beijing, China

- Chinese "т清华u大学ν核ε电子学"

Established since 1956

#### Education

- Courses

- Nuclear Electronics

- Nuclear Instrumentation

- Electro-Magnetic Compatibility

- Embedding System

- Real-time operation system µCOS

#### Education

- Student Exercise

- Preamp, Noise measurements

- Pulse Shaping , Pulse Height Analyzer

- Discriminator, Time

- μC, FPGA

- ARM Freescale University program

#### Research

- Analog

- ASIC low noise amplifier

- **—** ...

- Digital

- WR Ethernet based, sub-nanosecond time distribution network

**—** ...

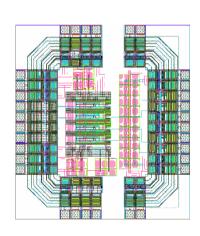

#### ASIC – low noise

- Low noise preamplifiers

- CMOS MPW  $0.6 \rightarrow 0.35 \rightarrow 0.18 \mu m$

- GEM, CZT, point contact HPGe

- Zhi Deng, Associate Professor

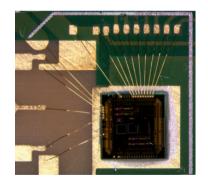

## **CASAGEM**

|             | CASA            | PASA        | LEGS-TPC    | PCA         |

|-------------|-----------------|-------------|-------------|-------------|

| Noise       | 293-455e@7.7pF  | 560e@12pF   | 100e+25e/pF | 270e@10pF   |

| Gain        | 1-19mV/fC       | 12mV/fC     | 17-32mV/fC  | 9.5mV/fC    |

| Pulse Width | 100-400ns, peak | 188ns, FWHM | 600ns, peak | 100ns, FWHM |

| Crosstalk   | <0.98%          | <0.1%       | unknown     | 0.3%        |

| Power       | 8.9mW/ch        | 11mW/ch     | 1.25mW/ch   | 10mW/ch     |

| Process     | 0.35μm          | 0.35μm      | 0.25μm      | 0.13μm      |

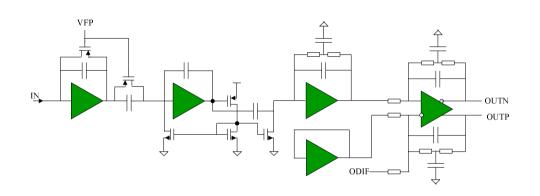

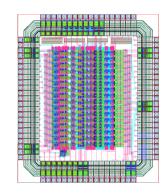

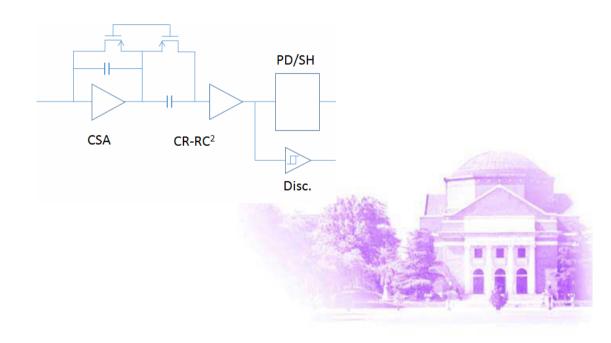

### **CAPS**

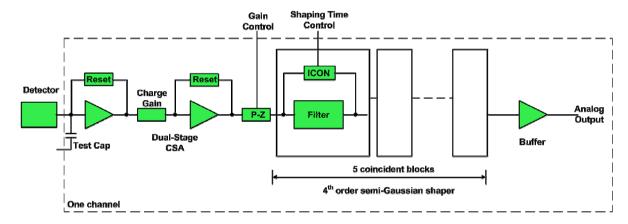

#### CZT, CSA, shaper

Channel

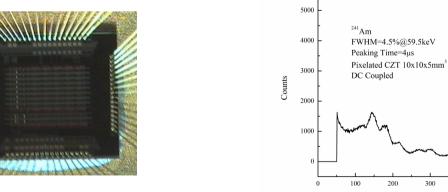

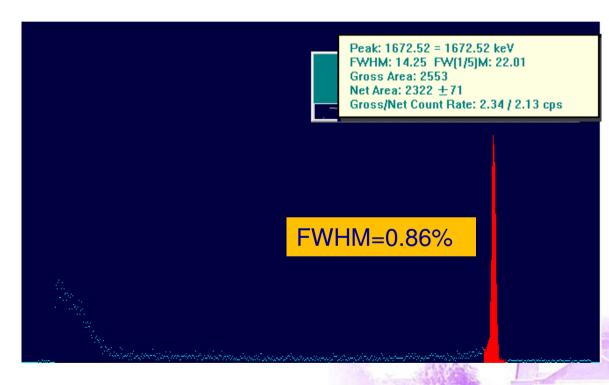

### PPC-HPGe

~1pF capacitance

Am-241 Spectrum (Cd~3pF, Id=23pA)

### **CAPS**

32 channels, CZT, CR-(RC)<sup>2</sup> shaper, discriminator, peak detection/holding, serial output

### CAD

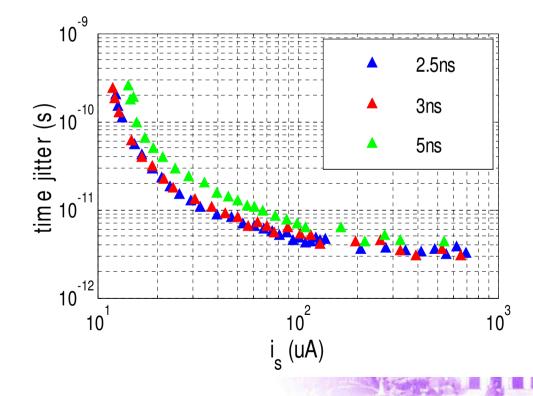

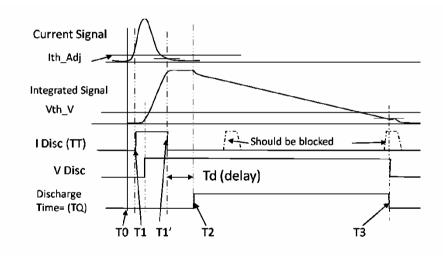

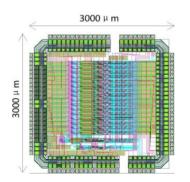

# 4 channels current amplifier and discriminator jitter < 10 ps ( $i > 20~\mu A$ ), for MRPC

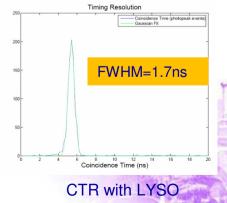

### **TIMPIC**

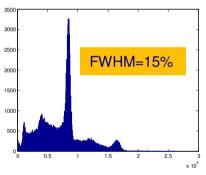

# 16 channels, SiPM read out time and amplitude TDC reading

#### Na-22 spectrum with LYSO

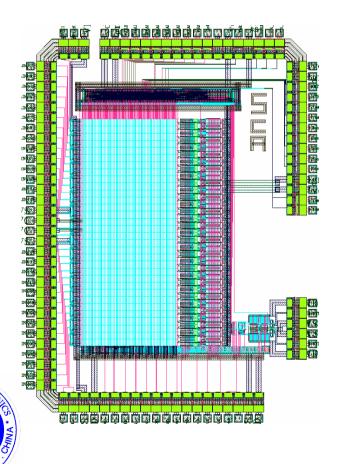

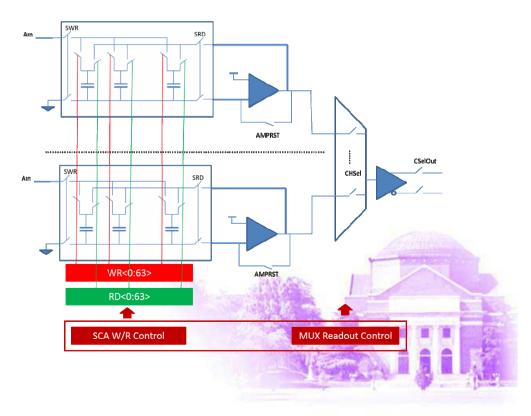

### SCA

#### 32 channels Switch Capacitor Array

#### White Rabbit

- WR White Rabbit

- Ethernet based, sub-nanosecond time distribution network

- Guanghua Gong, Associate Professor

#### White Rabbit

- Main features

- Transparent, high-accuracy synchronization

- Low-latency, deterministic data delivery

- Designed for high reliability

- Accelerator's control and timing

- International Collaboration

- Based on Well-known technologies

## Applications of WR

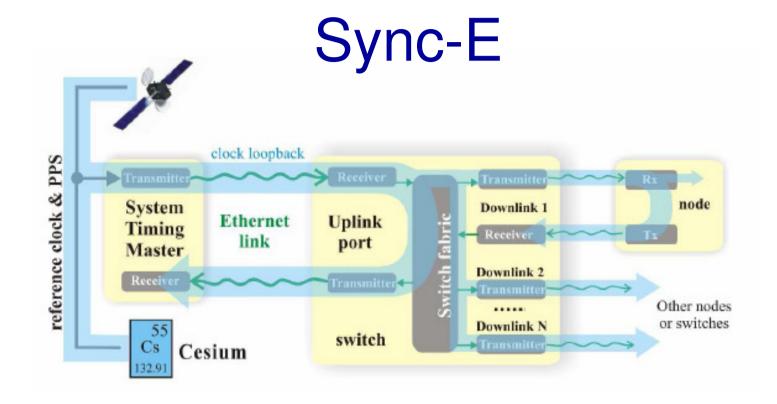

### WR — sub-ns synchronization

Long distance: 10km

Multi Nodes : 2000~10000

Accuracy : <1ns Precision : 10ps

- Common clock for the entire network

- All devices use the same physical layer clock

- Clock encoded in the Ethernet carrier

- Recovered by the receiver chip

- Not affected by network traffic load

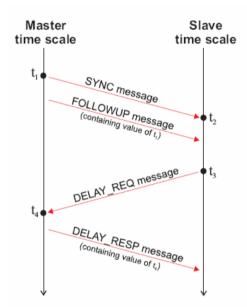

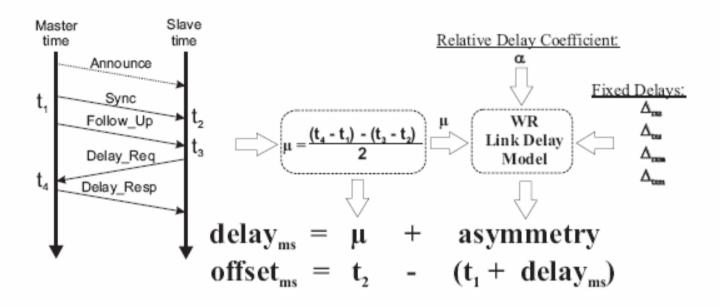

#### Precision Time Protocol (IEEE1588)

Having values of  $t_1...t_4$ , slave can:

- calculate one-way link delay:  $\delta_{ms} = \frac{(t_4 t_1) (t_3 t_2)}{2}$

- syntonize its clock rate with the master by tracking the value of t<sub>2</sub> - t<sub>1</sub>

- compute clock offset:  $offset = t_2 t_1 + \delta_{ms}$

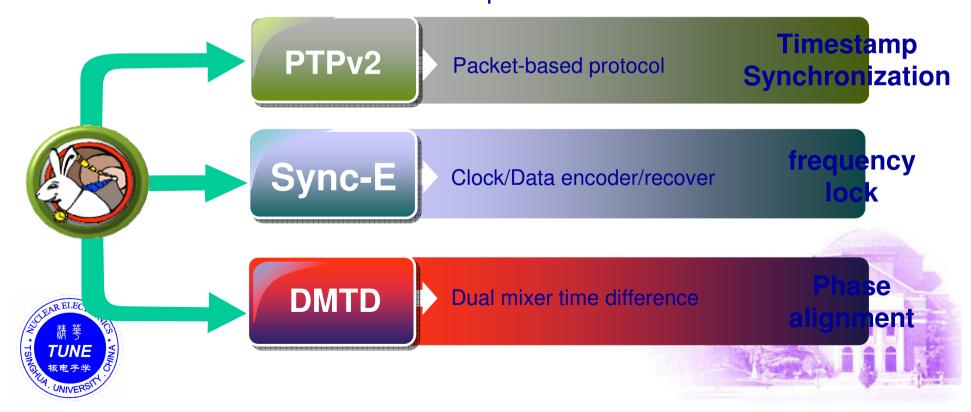

Timestamp Synchronization

- Precision time protocol(IEEE1588-2008)

- Targeted for LXI (LAN-based eXtensions for Instrumentation) application.

- Exchange of packages with timestamp embedded

- delay and offset are calculated and compensated.

- ~100ns precision achieved

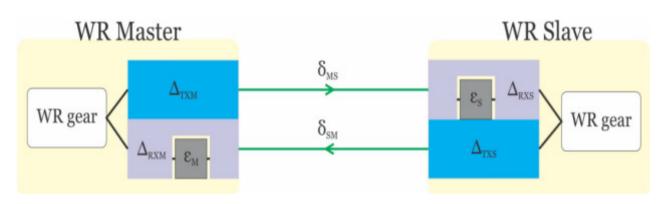

## WR Asymmetric link model

- Link delay

- Propagation speed difference due to W Diber calibration

- Fixed delay

- PCB layout delay

- Pin-to-Reg delay inside FPGA

- Fiber driver/Receiver delay

### WR Asymmetric link model

Solution for Ethernet over a Single-mode Optical Fiber

asymmetry =

$$\Delta_{tx_m} + \Delta_{rx_s} - \frac{\Delta - \alpha\mu + \alpha\Delta}{2 + \alpha}$$

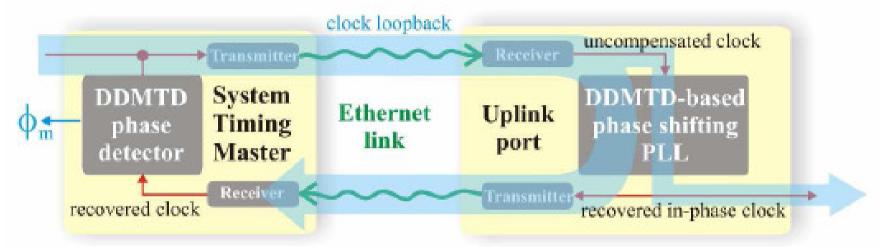

#### **DMTD**

PTP limitation

**TUNE**

- Clock-cycle granularity (8ns for 125MHz)

- Take advantage of SyncE and measure phase shift

- tx/loopback clock phase shift measured at master side

- Recovered clock adjusted by PLL at slave side

- Phase tracking by DDMTD

- Dual Mixer Time Difference

- Digital implementation: linear, low cost, resource saving

Phase

alignment

## WR components

A White Rabbit network is composed of

Clock/Freq reference (optional)

WR switch

Fiber links/cables

WR nodes

Proof

### WR Switch

by Seven Solutions

- Xilinx Virtex 6, Atmel AT91SAM9G45

- 18 cages for Gigabit SFPs, 10/100 Ethernet management port

- 5 SMC connectors (1-PPS in/out, CLK in/out)

- designed and produced by Seven Solutions in cooperation with CERN

- schematics, PCB design and mechanical drawings in the public OpenHardware repository

- Central element of WR network

- Original design optimized for timing, designed from scratch

- 18 1000BASE-BX10 ports

- Capable of driving 10 km of SM fiber

- Open design (H/W and S/W)

#### WR Node: carrier boards

- PCI-Express/VME/PXI/uTCA form carrier boards:

- Logic/Memory/Process

- WR circuit/SPF-Port/WRPC

- FMC mezzanine connectors

- AD/DA/IO with FMC mezzanine cards

ADC

DAC

Time-to-Digtal

Fine delay

WR port

Application mode for CERN/GSI

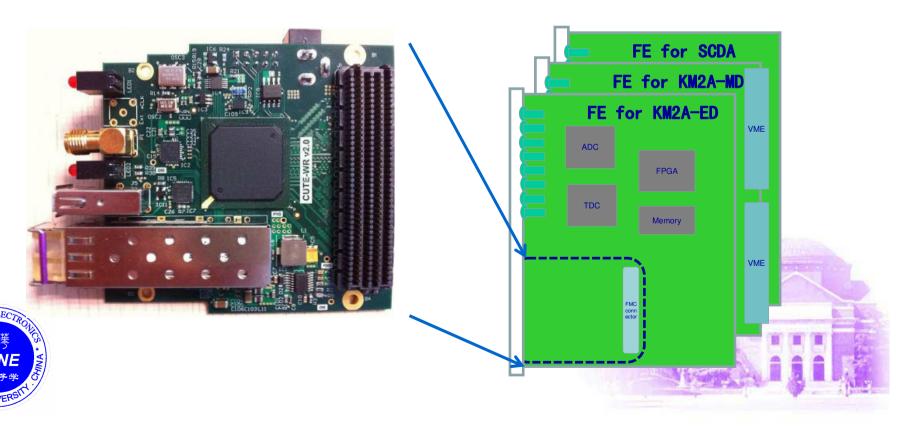

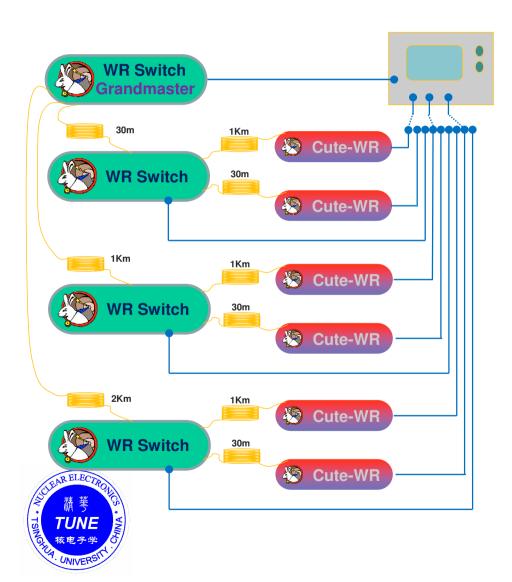

#### WR Nodes: Cute-WR

- FMC form WR mezzanine

- WR circuit/SFP-Port/WRPC

- FMC mezzanine connector

Application mode for LHAASO

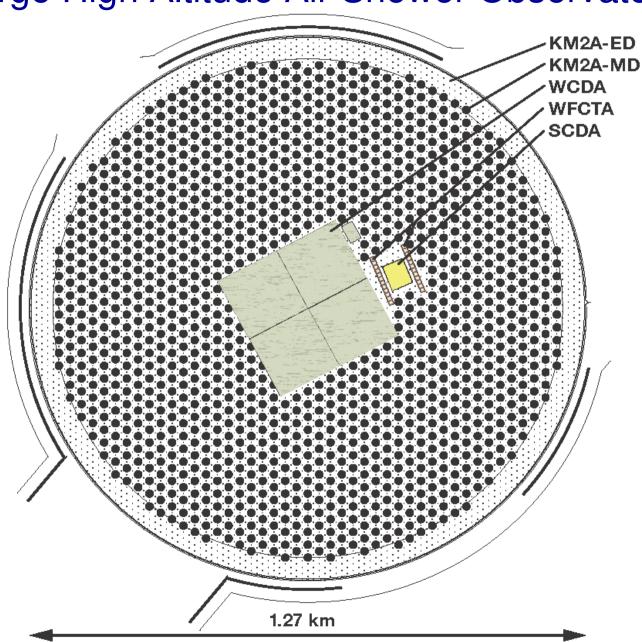

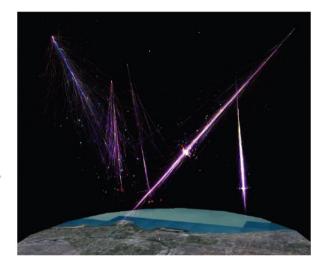

#### Large High Altitude Air Shower Observatory

#### LHAASO detector

- KM2A:

- 5632 Electron detector, 15m spacing

- 1221  $\mu$  detector, 30m spacing

- WCDA: Water Cherenkov Detector Array

- $-4 \times (150 \times 150) \text{ m}^2$

- 3600 detector units

- WFCTA: Wide FOV Cherenkov Telescope Array

- 24, 300m spacing

- SCDA: Shower Core Detector Array

- 5000m<sup>2</sup>, 452 core detectors

Over 6,000 detector units Spread around 1km<sup>2</sup> area

0.5° Angular resolution for shower reconstruct from *timing* of hits TOA

Synchronous timing among detectors

1000m coax cable in 30°C change,  $\Delta$  delay = 15ns!

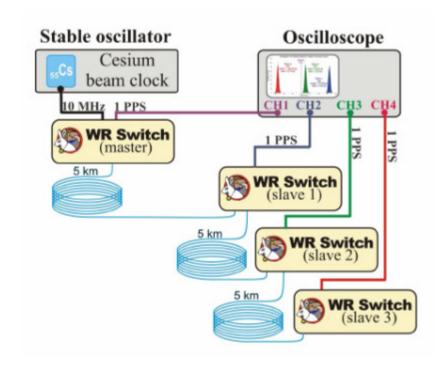

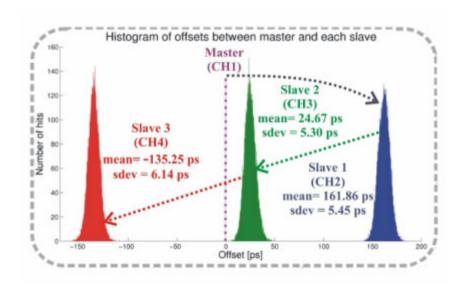

## WR performance (@CERN)

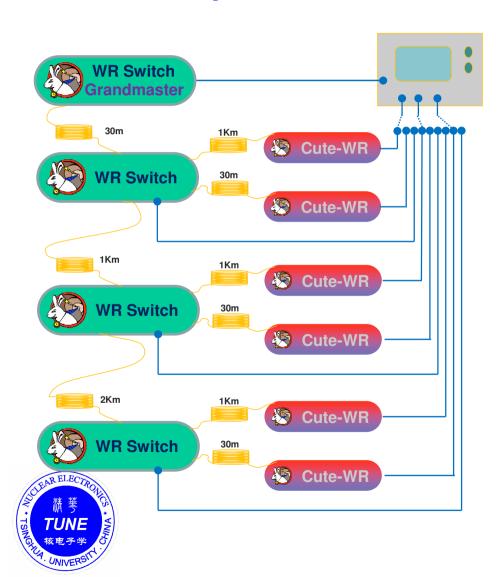

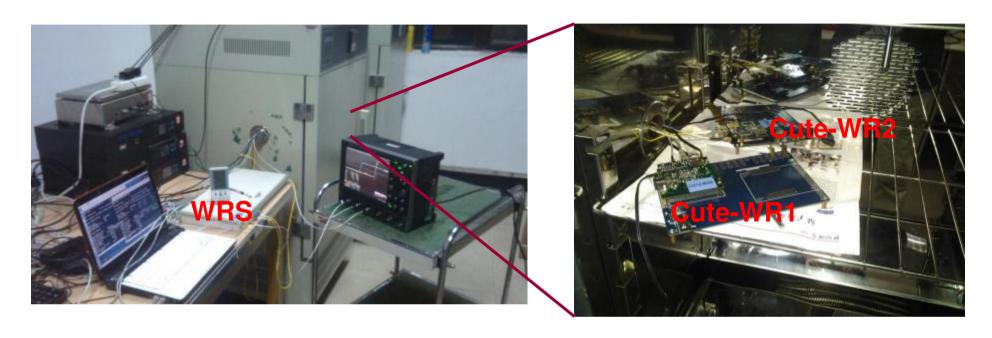

## WR test (@Tsinghua)

- Test includes:

- 4 WR switch v3.3

- 8 Cute-WR nodes

- Rolls of SM fiber (few km each)

- Performance test

- Precision/accuracy test

- Consistency test

- Topology test

- measurement

- Set the PPS from top-level WRS as reference.

- Measure the offset between PPS signals from other WRS/Cute-WR

- Results include different situations:

- Fiber length, WR nodes, SFP modules, WRS ports, connections, power-cycle, link-up, components exchange,

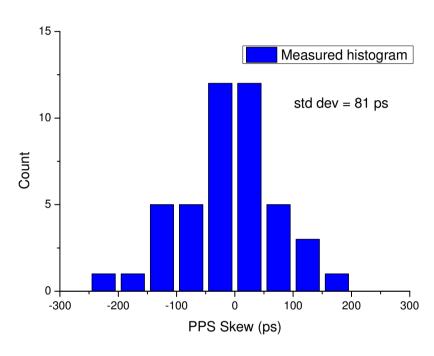

### WR performance (@Tsinghua)

#### **Parallel topoloty**

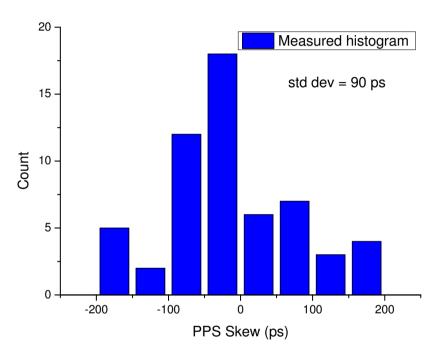

### WR performance (@Tsinghua)

**Cascade topoloty**

One layer less than KM2A deployment

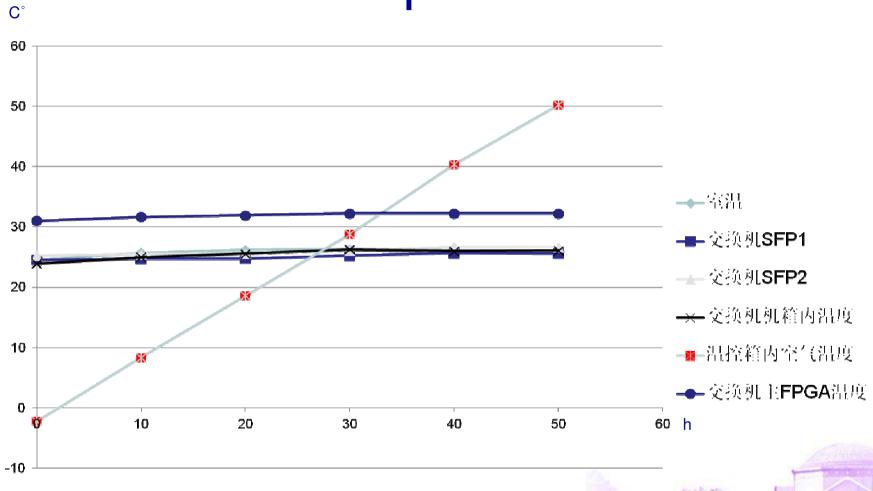

### WR temp. effect

Fiber temp. variation is compensated by DMTD&PTPv2

Temp. effect of Cute-WR fixed delay can be problem

- Temp. range 0-50 degree

- Environmental temp. are monitored.

## Temp. record

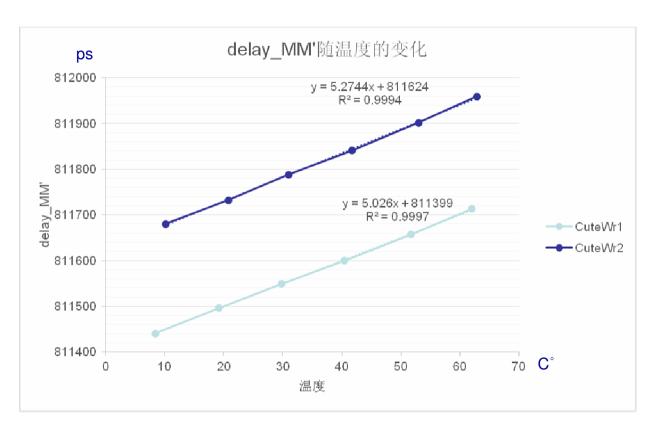

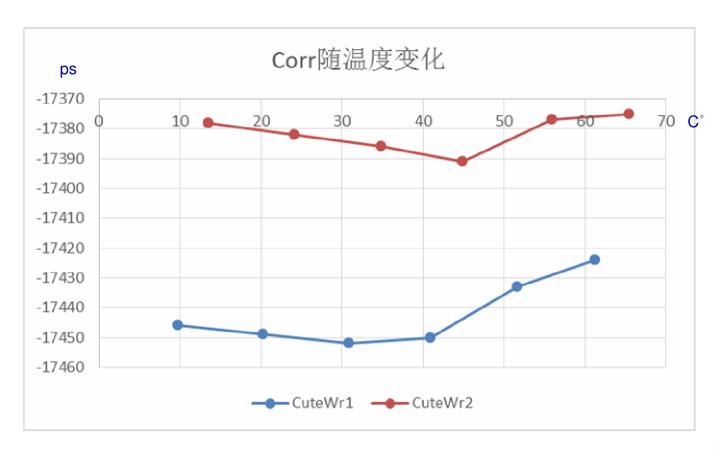

#### temp. dependency of Cute-WR fixed delay

$$\blacksquare (\delta_{\rm txs} + \delta_{\rm rxs}) \sim 5 \rm ps/^{\circ} C$$

## After temp. compensation

■ A temp. range of 50°C, 50ps accuracy can be achieved after temp. compensation