# ROC chips for imaging calorimetry at the International Linear Collider

**CHEF 2013**

Nathalie Seguin-Moreau on behalf of OMEGA microelectronics group

IN2P3-CNRS, Ecole Polytechnique, Palaiseau (France)

### Outline

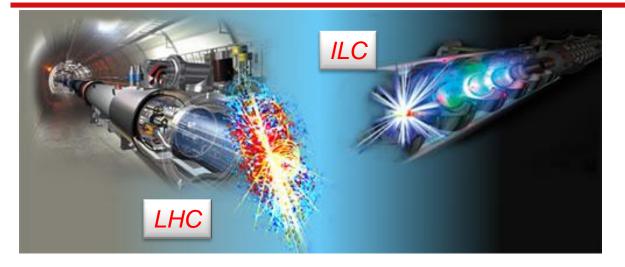

### **Imaging calorimetry at the International Linear Collider**

- $\Rightarrow$  New detectors with one hundred million channels

- $\Rightarrow$  Readout electronics: must be highly integrated (System On Chip) and ultra low power to be embedded inside the detectors

- ⇒ Readout ASICs: HARDROC, MICROROC, SPIROC and SKIROC in SiGe 350 nm technology (AMS) by OMEGA group

http://omega.in2p3.fr/

- Requirements for **electronics**

- Large dynamic range (15 bits)

- Auto-trigger on ½ MIP

- On chip zero suppress

- Integration issues

- 10<sup>8</sup> channels, Compactness

- Front-end embedded in detector

### => Ultra-low power

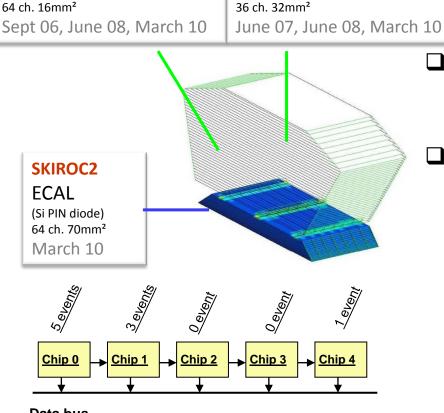

# ASICs for ILC prototypes

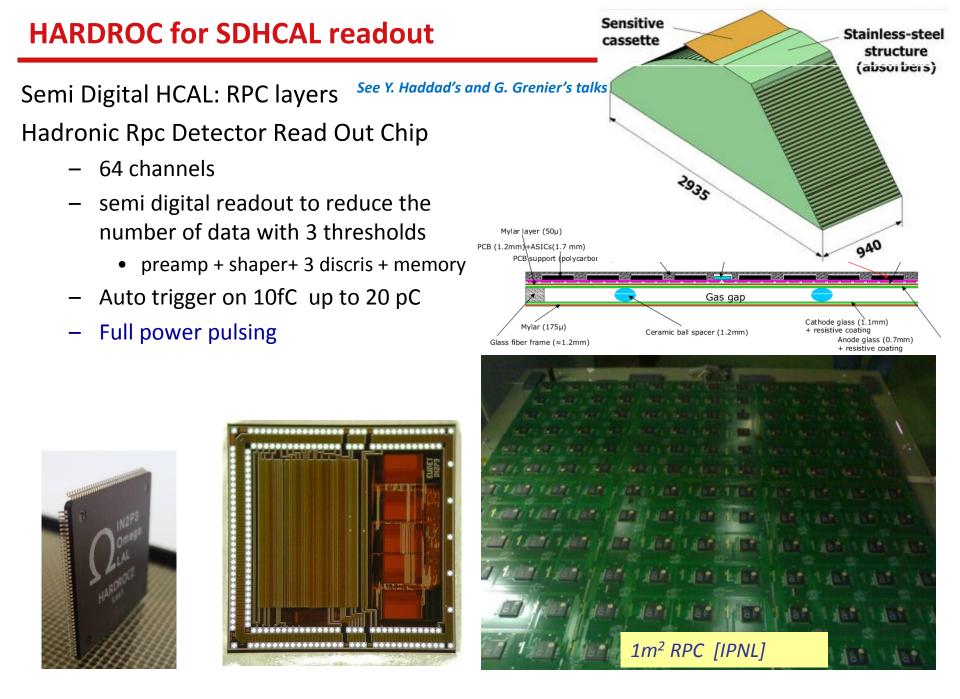

HARDROC2 and MICROROC

Digital HCAL (DHCAL)

(RPC, µmegas or GEMs)

SPIROC2

(SiPM)

Analog HCAL (AHCAL)

#### Data bus

| Chip 0 | Acquisition        | <u>A/D conv.</u>   | DAQ         |     | IDLE MODE    |                    |  |

|--------|--------------------|--------------------|-------------|-----|--------------|--------------------|--|

| Chip 1 | Acquisition        | <u>A/D conv.</u>   | IDLE        | DAQ |              | IDLE MODE          |  |

| Chip 2 | <u>Acquisition</u> | <u>A/D conv.</u>   | IDLE        |     |              | IDLE MODE          |  |

| Chip 3 | Acquisition        | <u>A/D conv.</u>   | IDLE        |     |              | IDLE MODE          |  |

| Chip 4 | <u>Acquisition</u> | A/D conv.          | IDLE        |     | DAQ          | IDLE MODE          |  |

|        | <u>1ms (.5%)</u>   | <u>.5ms (.25%)</u> | .5ms (.25%) |     |              | <u>198ms (99%)</u> |  |

|        | 1% duty cycle      |                    |             | 99  | % duty cycle |                    |  |

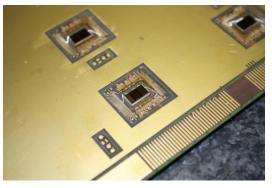

1st generation ASICs: FLC-PHY3 and FLC SiPM (2003) for physics prototypes

2<sup>nd</sup> generation ASICs: ROC chips for technological prototypes

- Address integration issues  $\checkmark$

- Auto-trigger, analog storage, internal digitization, power pulsing

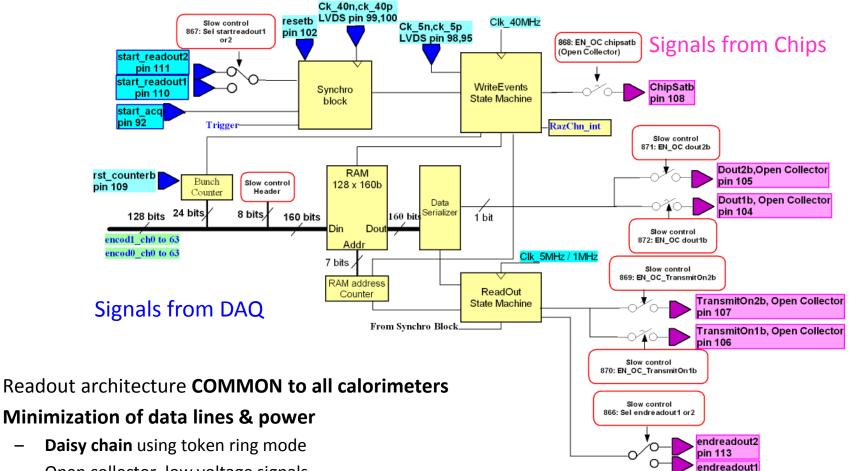

- $\checkmark$ Readout architecture **common to all calorimeters** and minimization of data lines & power

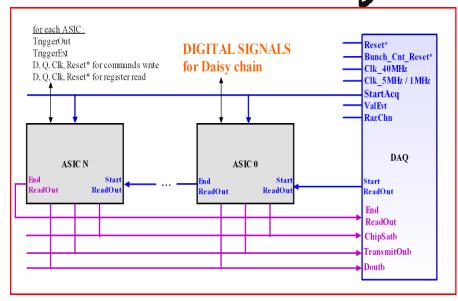

- Daisy chain using token ring mode

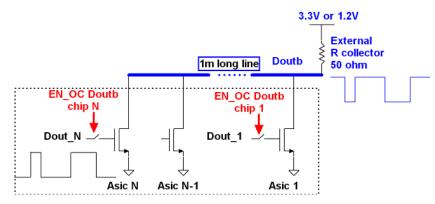

- Open collector, low voltage signals

- Low capacitance lines

- 3<sup>rd</sup> generation ASICs (AIDA funded)

Independent channels to perform Zero suppress

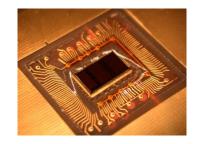

# **SKIROC2 for ECAL readout**

- « Imaging » calorimetry for « particle flow algorithm » => 30%/VE jet resolution

- High granularity and segmentation of the calorimeters

See D. Jeans and T. Frisson's talk

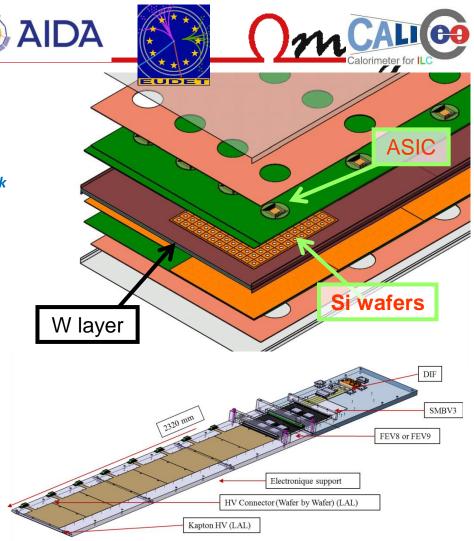

### **Si W Calorimeter**

- ✓ Active medium: SILICON SENSORS (WAFERS)

- ✓ 325µm thick Silicon Wafers => 25000e<sup>-</sup>/MIP ie 1MIP=4 fC

- ✓ High granularity : 5x5 mm<sup>2</sup>

High segmentation: 45 000 cells with embedded electronics for the technological prototype

### Final ECAL: 30 layers, 100 M channels

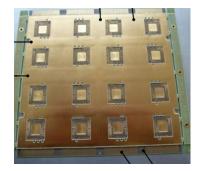

- SKIROC2 embedded inside the detector, No (few) external components

- Front End boards: crucial element

- □ stitchable" motherboards (Active Sensor Units)

- Minimize connections between boards

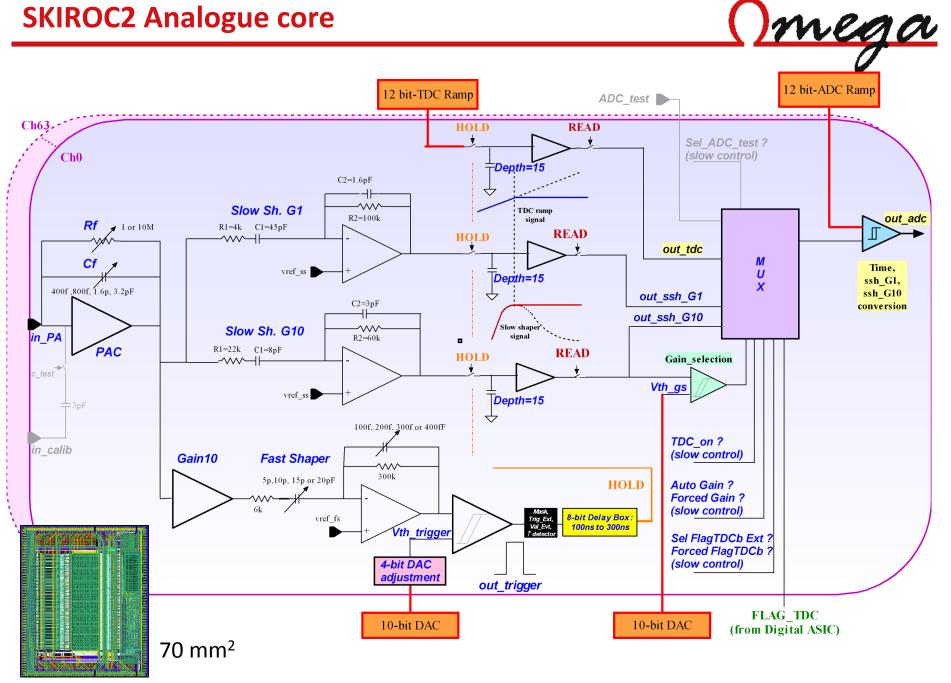

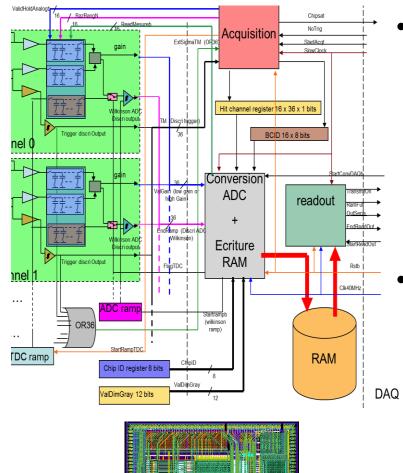

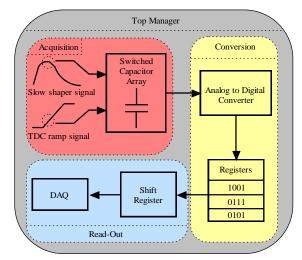

# **SKIROC 2** main features

- Energy measurement : 14 bits

- 2 gains (1-10) + 12 bit ADC: 1 Mip (4fC) → 2500 Mip (10pC)

- Variable shaping time from 50ns to 100ns

- Mip/noise ratio > 10

- Auto-trigger on 1/2 MIP (2 fC)

- MIP/noise ratio on trigger channel >10

- Fast shaper : ~30 ns

- Auto-Trigger on ½ MIP

- Time measurement :

- 12-bit Bunch Crossing ID + 12 bit TAC step~100 ps

- Analog memory for time and charge measurement : depth = 15

- 12 bit-ADC, 4k internal memory

- Daisy chain readout

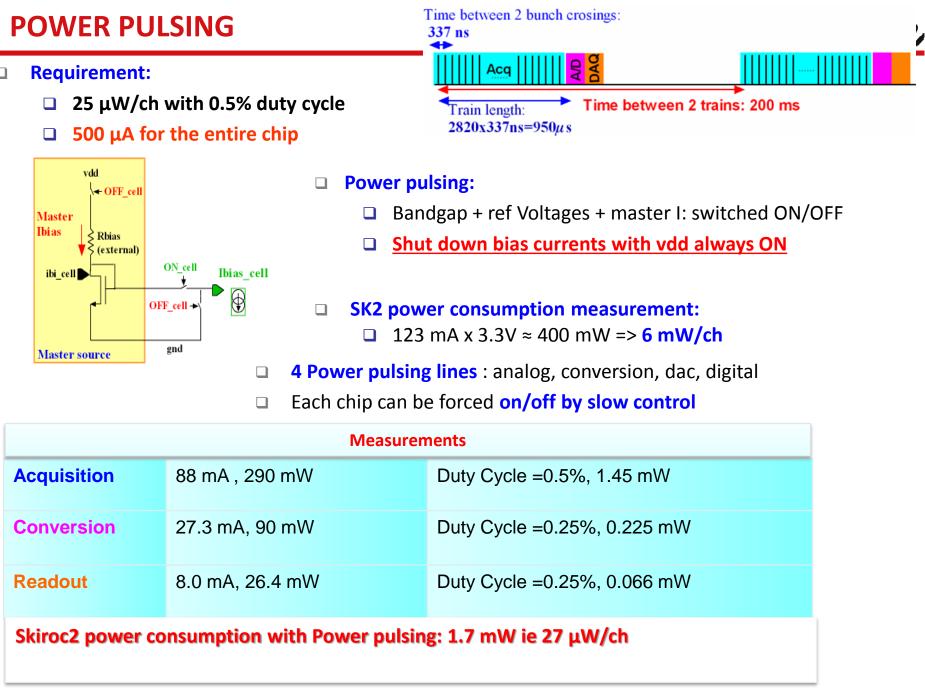

- Low consumption : ~25  $\mu$ W per channel (in power pulsing mode)

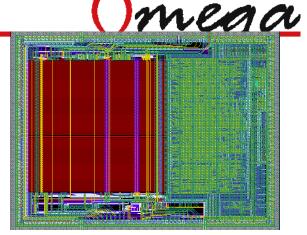

### **SKIROC2** Analogue core

# **SKIROC2 digital features**

- Common features with Hardroc & Spiroc (compatibility with any CALICE DAQ system)

- Open Collector token-ring ReadOut

- Multiplexed Slow Control & Probe

- Redundancy on Data Out & Transmit On signal lines

<u>()mega</u>

- 2 switchable StartReadOut Inputs & EndReadOut Outputs :

- to prevent chip failure

- Very Complex Digital Part (~10% of the Die)

- Manage Acquisition, Conversion, 15 SCA control, RAM, I/Os...

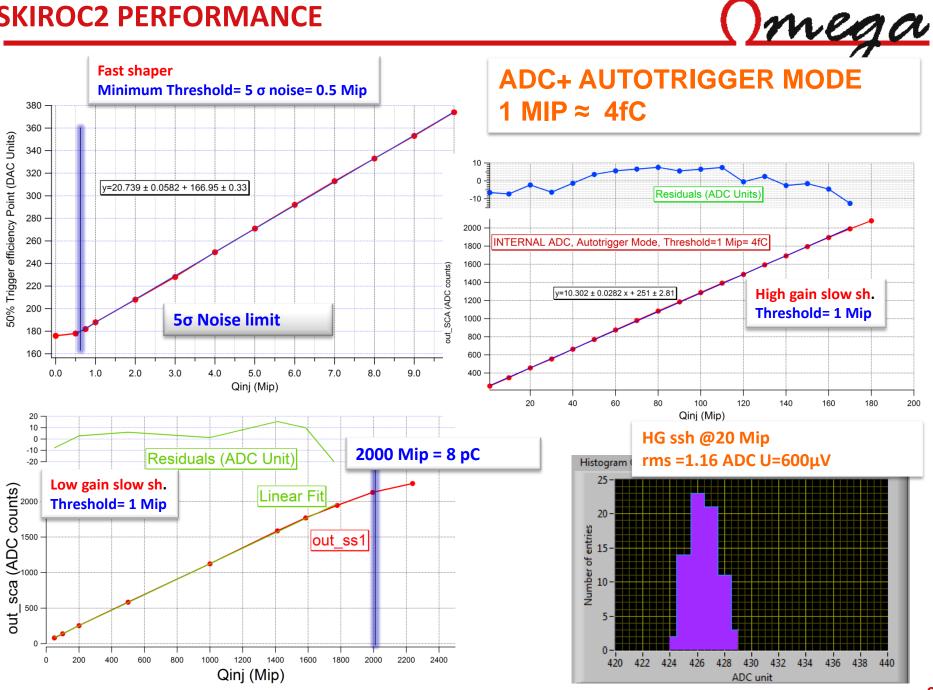

# **SKIROC2 PERFORMANCE**

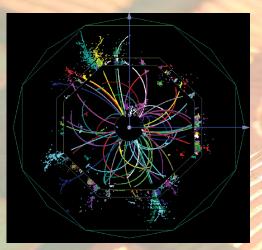

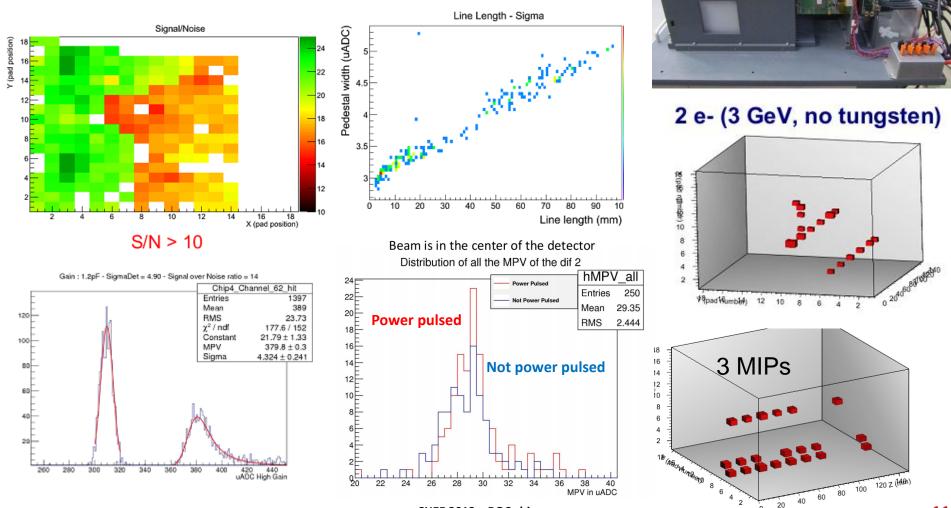

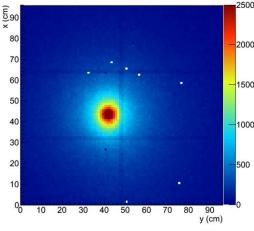

### **TESTBEAMs with SKIROC2**

Successful test beams @ DESY in 2012 (1 to 6 layers) and 2013 (8 layers), power pulsing mode, autotrigger mode, e- (1 to 5GeV)

- ✓ 4 packaged skiroc2/slab

- ✓ Nice event displays

CHEF 2013 ROC chips

<u>()mega</u>

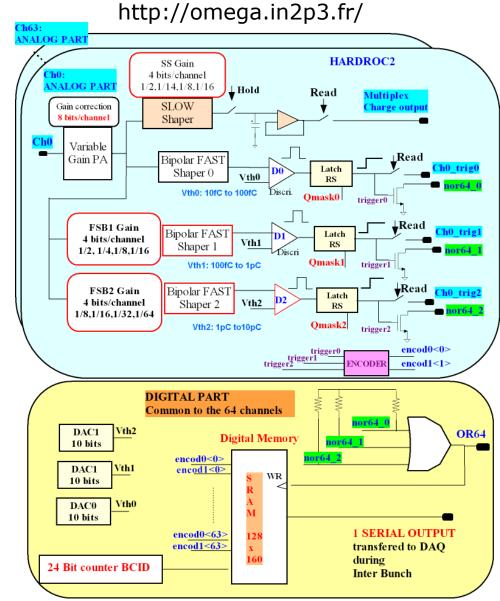

# **HARDROC: simplified schematics**

# <u> Mega</u>

### HARDROC2

#### Current preamp with 8 bits gain correct: G=0 to 255 (analog G=0 to 2)

- **3 shapers**, variable Rf,Cf and gains:

- □ Fsb1, G= ½,**1/4**,1/8,1/16

- □ Fsb2, G= 1/8,**1/16**,1/32,1/64

#### 3 discriminators

64 inputs

- 3 10 bit-DACs to set the thresholds (100fC, 1pC, 10pC)

- Encoded in 2 bits

- Auto-trigger down to 10fC up to 10pC

- All channels and BCID stored for every hit in a 127 bit deep digital memory

- Data format : 127 (depth)\*[2bit\*64ch+24bit(BCID)

+8bit(Header)] = 20 320 bits

- 872 SC registers, default config

- Mask of bad channels

- Full power pulsing: < 10μW/ch

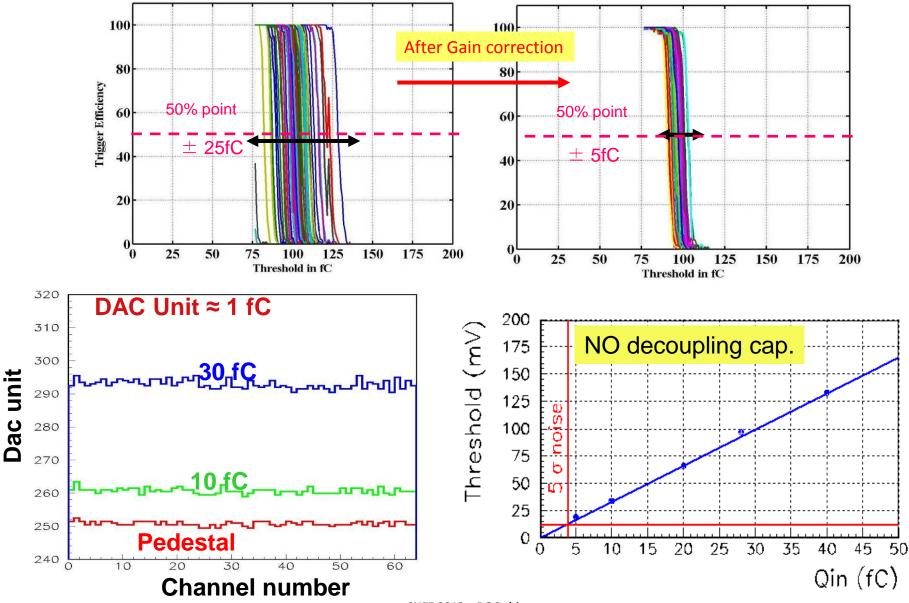

### HARDROC2 PERFORMANCE

CHEF 2013 ROC chips

mega

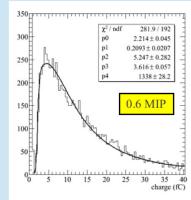

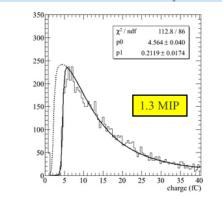

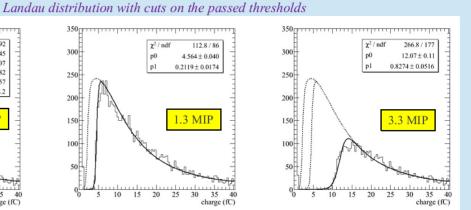

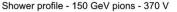

# **HARDROC** in **TB**

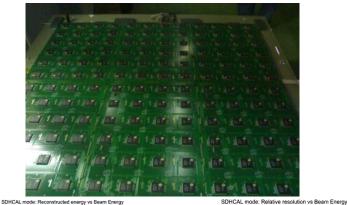

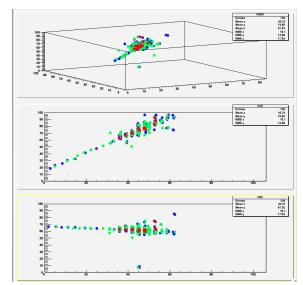

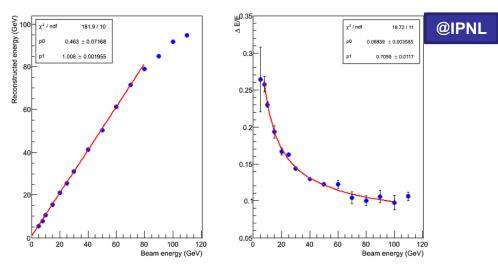

- SDHCAL technological proto with 40 layers (5760 HR2 chips) built in 2010-2011.

- Scalable readout scheme successfully tested

- Complete system in TB with 370 000 channels,

AUTOTRIGGER mode and power pulsing (5%)

#### Vth0 Vth1 Vth2

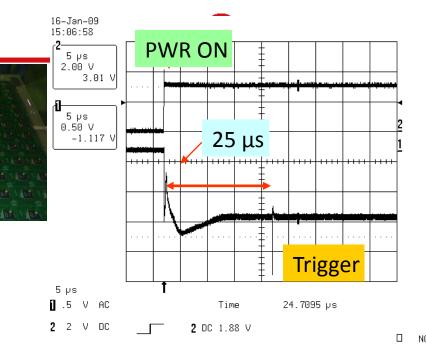

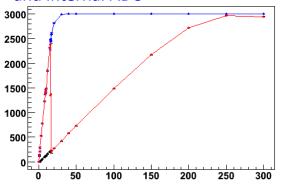

# **Power pulsing**

- Power dissipation

- 1.5 mW/ch continuous

- 25 µs awake time

- $-7.5 \,\mu\text{W/ch}$  with 0.5% duty cycle

- 10 μW/ch = 24h operation of full slab with 2 AAA batteries !

Testbeam: 370 000 channels power pulsed (5% duty cycle)

Colours correspond to the three thresholds: Green (114 fC), Blue (5 pC), Red (15 pC)

# **MICROROC (variant of hardroc)**

# 64 channels to readout a DHCAL equipped with MICROMEGAS

See Max Chefdeville's talk

- Very similar to HARDROC except for the input preamp (@LAPP) and shapers (100-150 ns)

- Noise: 0.2fC (Cd=80 pF). Auto trigger on 1fC up to 500fC

- Pulsed power: **10 µW/ch** (0.5 % duty cycle)

- 4 Micromegas prototypes of 1x1 m<sup>2</sup> were constructed in 2011-2012 and tested in particle beams inside the DHCAL steel structure in 2012

#### **U** Very good performance of the electronics and detector in autotrigger mode and with threshold set to 1fC

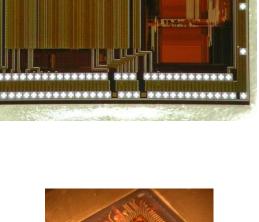

# HARDROC3

### 3<sup>rd</sup> generation chip for ILD

□ Independent channels (zero suppress):

Each of the hundred millions of channels:

will sense that it gets a signal,

will measure its charge on 16 bits and its time to a fraction of ns

and will send its zero-suppressed digital information to the

reconstruction farms. This scheme has never been implemented before inside any detector,

on such scale, but will certainly be a major change in the next generation of detectors

I2C link (@IPNL) for Slow Control parameters and triple voting

□ HARDROC3: 1<sup>st</sup> of the 3<sup>rd</sup> generation chip to be submitted

- No major change in the analog part

- PLL: integrated to generate clocks internally,

- Submitted in Feb 2013 (SiGe 0.35μm), funded by AIDA, expected in June 2013

- Die size ~30 mm<sup>2</sup> (6.3 x 4.7 mm<sup>2</sup>)

- To be packaged in a TQFP208, will equip 2-3m RPC chambers

#### - 2013: dedicated to the test of HR3 before submitting other chips

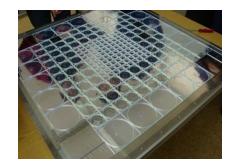

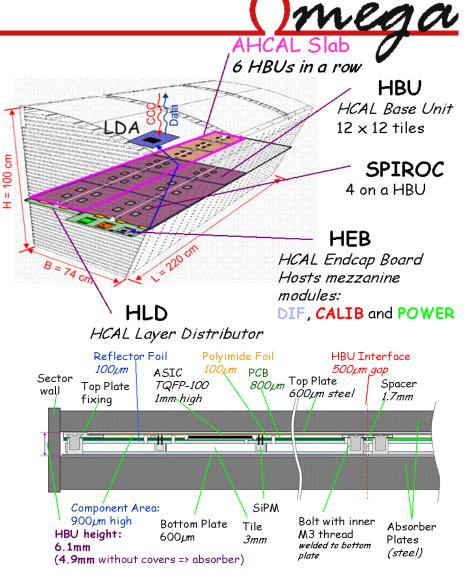

# **SPIROC2 for AHCAL readout**

Analog HCAL: See Marco Ramilli 's talk

✓ 40 layers of 1.5 m<sup>2</sup> 2 cm thick steel plates interleaved with cassettes of 296 scintillating tiles (3x3 cm<sup>2</sup>) readout by SiPMs

- FE Chip embedded inside the detector

- Thickness:critical issue, mother boards (HBU) are sandwiched between 2 absorber plates

See Katja Krüger 's talk

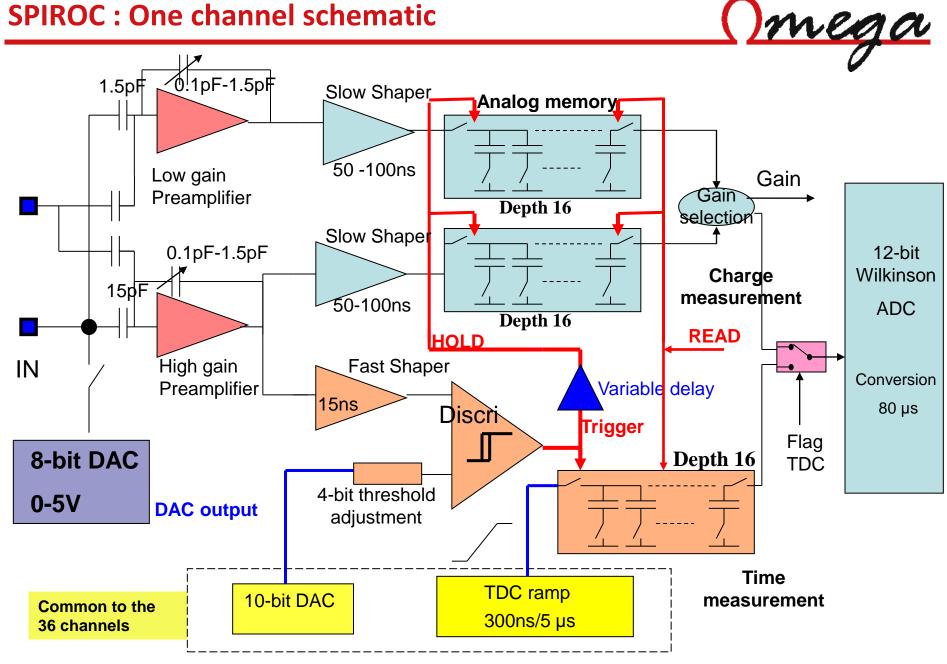

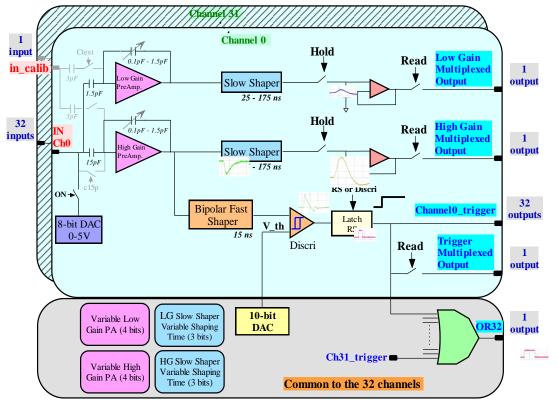

# **SPIROC** main features

- Internal input 8-bit DAC (0-5V) for individual SiPM gain adjustment

- Energy measurement : 14 bits

- 2 gains (1-10) + 12 bit ADC: 1 pe → 2000 pe

- Variable shaping time from 50ns to 100ns

- pe/noise ratio : 11

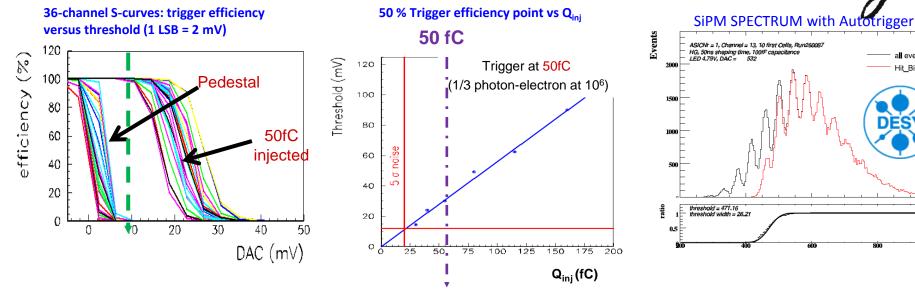

- Auto-trigger on 1/3 pe (50 fC)

- pe/noise ratio on trigger channel : 24

- Fast shaper : ~10 ns

- Auto-Trigger on ½ pe

- Time measurement :

- 12-bit Bunch Crossing ID

- 12 bit TDC step~100 ps

- Analog memory for time and charge measurement : depth = 16

- 4k internal memory and Daisy chain readout

- Low consumption : ~25  $\mu$ W per channel (in power pulsing mode)

- Individually addressable calibration injection capacitance

- Embedded bandgap for voltage references

- Embedded 10 bit DAC for trigger threshold and gain selection

- Multiplexed analog output for physics prototype DAQ

# **SPIROC : One channel schematic**

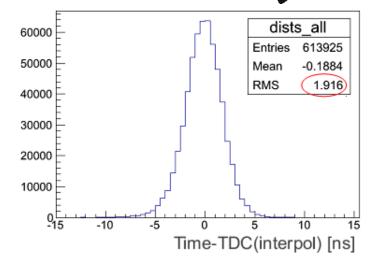

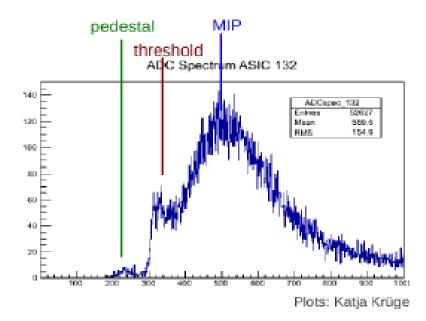

# **SPIROC2 PERFORMANCE**

al events

Hit\_Bit = 1

ADC

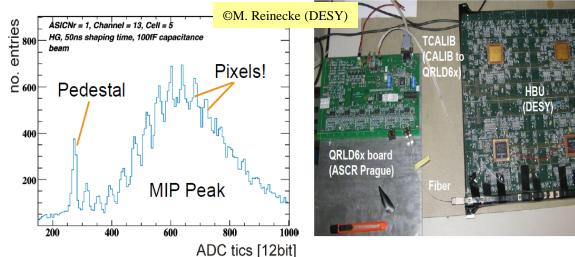

**MIP response in DESY** 6 GeV electron testbeam

linearity using the auto gain mode and internal ADC

## **TEST BEAMs with SPIROC2b**

576 channel AHCAL layer prototype successfully tested at CERN and at DESY in 2012

TDC: First tests of TDC ramps in SPIROC2b show promising results

- ✓ Several corrections needed: memory cell and channel wise offsets correction, chip wise ramp corrections

- ✓ Electronics resolution ~ 2 ns, allows neutrons identification

□ Multi layer prototype in TB at DESY in June 2013

# **EASIROC: SIMPLER VERSION OF SPIROC**

- <u>32-channel</u> front-end readout (analogue part of SPIROC)

- <u>2 multiplexed analog outputs</u> (high gain, low gain) [tri state outputs]

mega

- Trigger output

- <u>32 Trigger outputs</u>

- OR32 output

- <u>Trigger multiplexed output</u> (latch included) [Tri state output]

- Low power : 4.84 mW/channel, 155 mW/chip

#### SipMed, IMNC, LAL, OMEGA

### Many applications:

- Astrophysics (CTA Palermo),

- Nuclear physics (KEK, Tohoku),

- PET (Roma, Pisa, Valencia),

- Vulcanology (Napoli, IPN Lyon)

JPARC

## **SUMMARY**

Imaging calorimetry possible thanks to ROC chips, also used for many other applications (astrophysics, vulcanology, medical imaging)

γ ray camera readout with Hardroc

- Complete systems with up to 400k channels run at system level in auto trigger mode and with power pulsing

- □ 3<sup>rd</sup> and last generation of chips (= completely independent channels, triggerless) underway

- $\Rightarrow$  Intelligence brought inside the chips

- $\Rightarrow$  Major change for the next generation of detectors

25

@IMNC

- Open collector, low voltage signals

- Low capacitance lines

mega

pin112

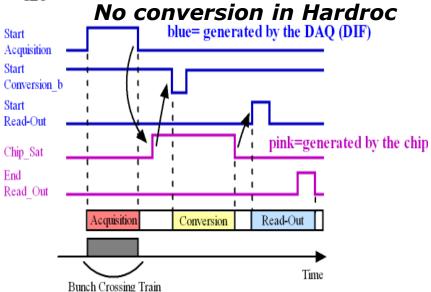

# Main signals of the DAISY CHAIN

**COMMON** to all the ROC chips

#### StartAcq

- □ Start acquisition, generated by DAQ

- ChipSat (Open Collector signal):

Generated by chip, « 1 »: digital memory is full or acq is finished

- StartReadout:

- Generated by DAQ, start of the readout

- EndReadout

- Generated by chip, End of the readout

- Dout: data out (OC signal)

- TransmitOn (OC signal)

- Generated by chip, Data out are transmitted

### Buffers integrated for OC signals

mega

ILC