# LHCb Calorimeter Upgrade Electronics

E. Picatoste (Universitat de Barcelona) On behalf of the LHCb group

CHEF 2013 – 22-25th April 2013 – Paris

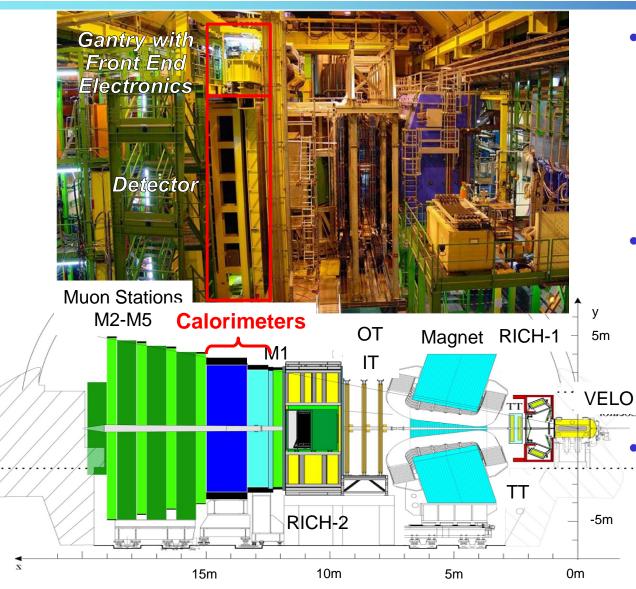

### LHCb Upgrade

<sup>•</sup> Statistical improvement if:

- Increase of data rate from 1 to 5fb<sup>-1</sup>/year

- Increase luminosity to 2x10<sup>33</sup> cm<sup>-2</sup>s<sup>-1</sup>

- Increase trigger efficiencies

- Current L0 trigger limited by electronics ⇒upgrade:

- Trigger in software

- Use data from every bunch crossing

- Upgrade electronics and DAQ

- Scheduled for the long LHC shutdown in 2018.

More details on "LHCb Calorimeter upgrade": talk of Yu. Guz, this conference

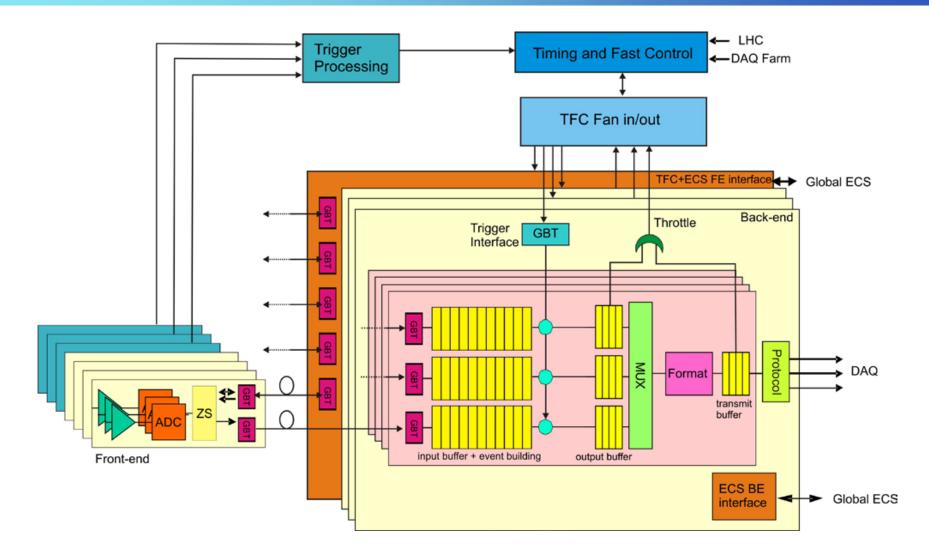

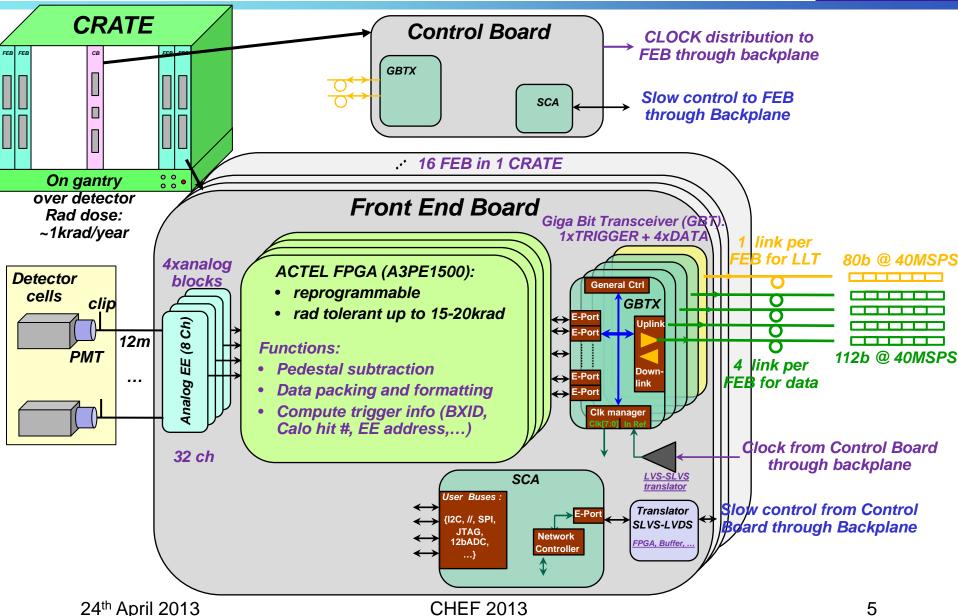

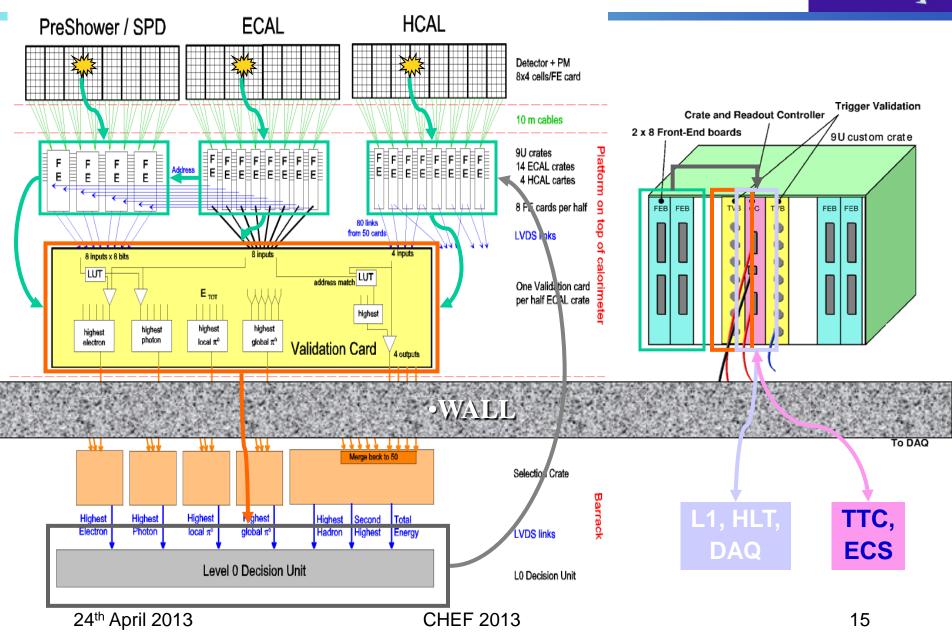

#### **Upgrade** Architecture

#### More details on "LHCb Calorimeter upgrade": talk of Yu. Guz, this conference

24th April 2013

CHEF 2013

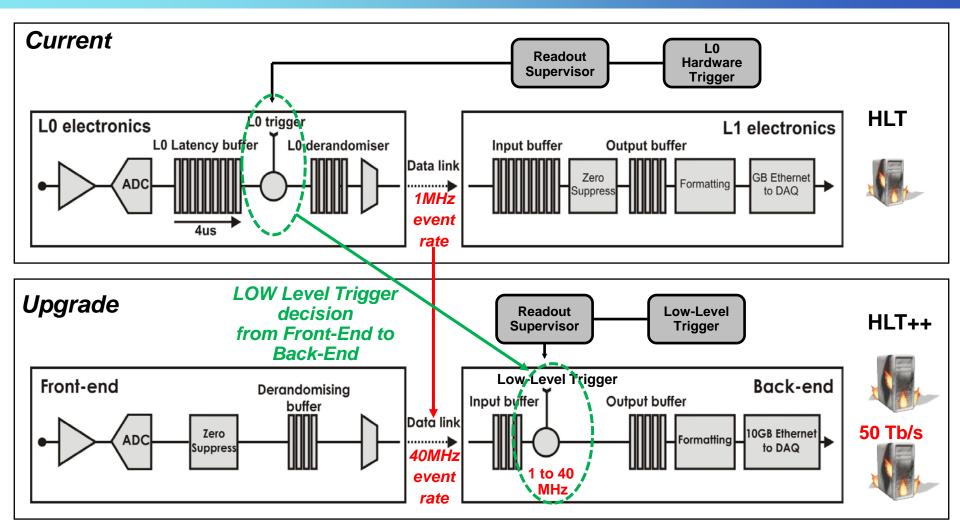

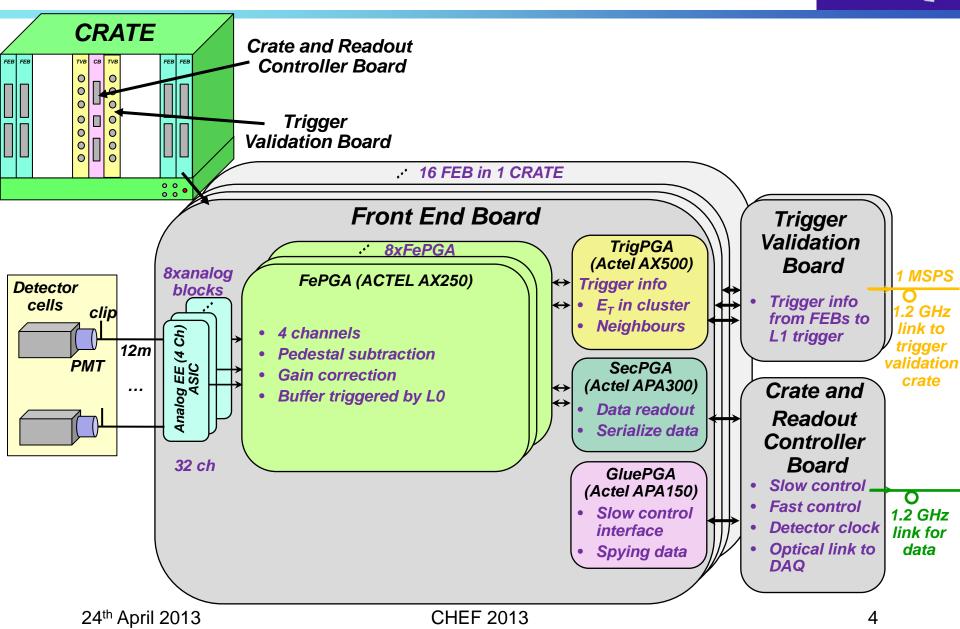

#### **Current Front-End Electronics**

LHC

#### **Upgrade Front-End Electronics**

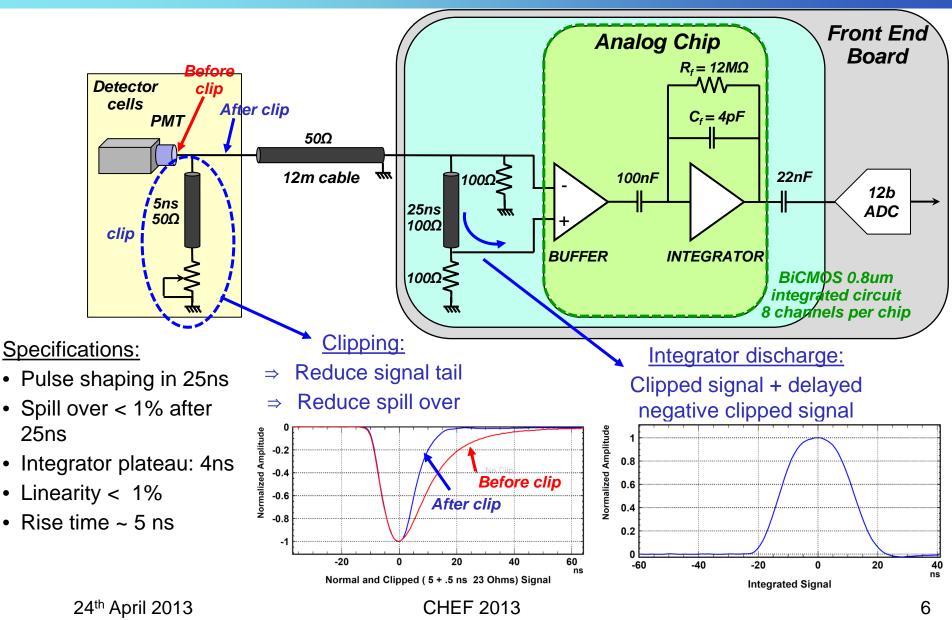

### **Current Analog Signal Processing**

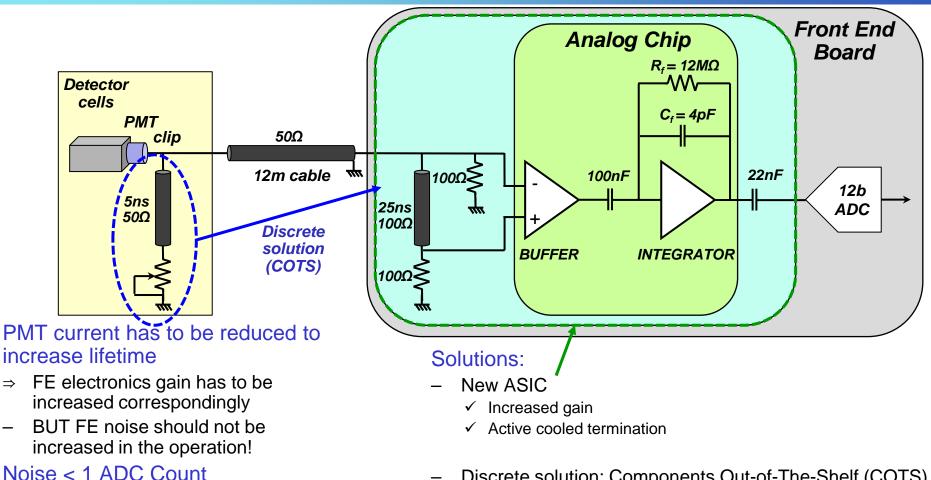

## Analog Electronics Upgrade Motivation

- For 12 bit DR, input referred noise <1nV/sqrt(Hz)

- ⇒ Termination resistor at input generates too much noise

$\Rightarrow$

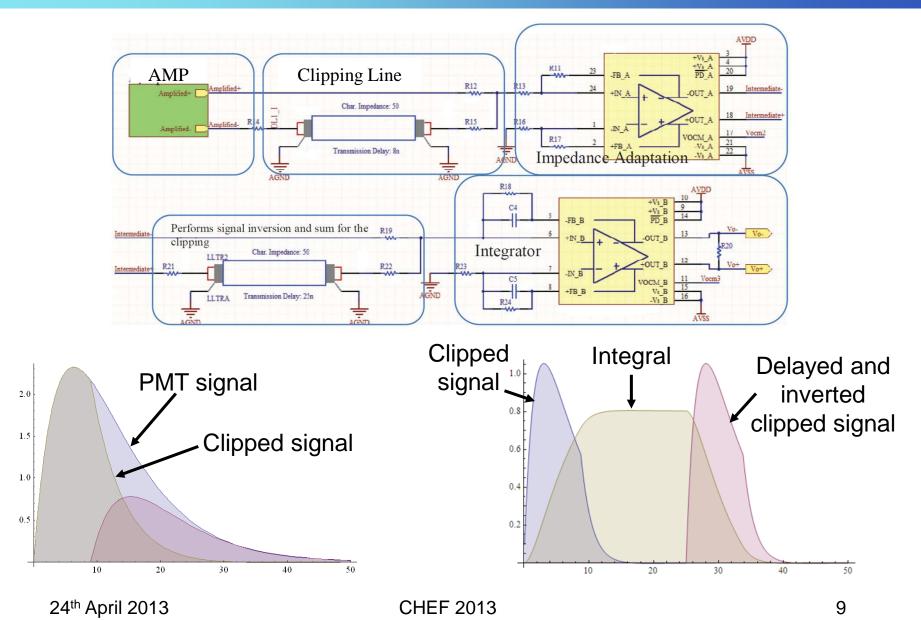

#### Discrete solution: Components Out-of-The-Shelf (COTS)

- $\checkmark$  2/3 of the signal are lost by clipping

- Remove clipping at the PM base (detector)

- ✓ Perform clipping after amplification in FE using delay lines

24<sup>th</sup> April 2013

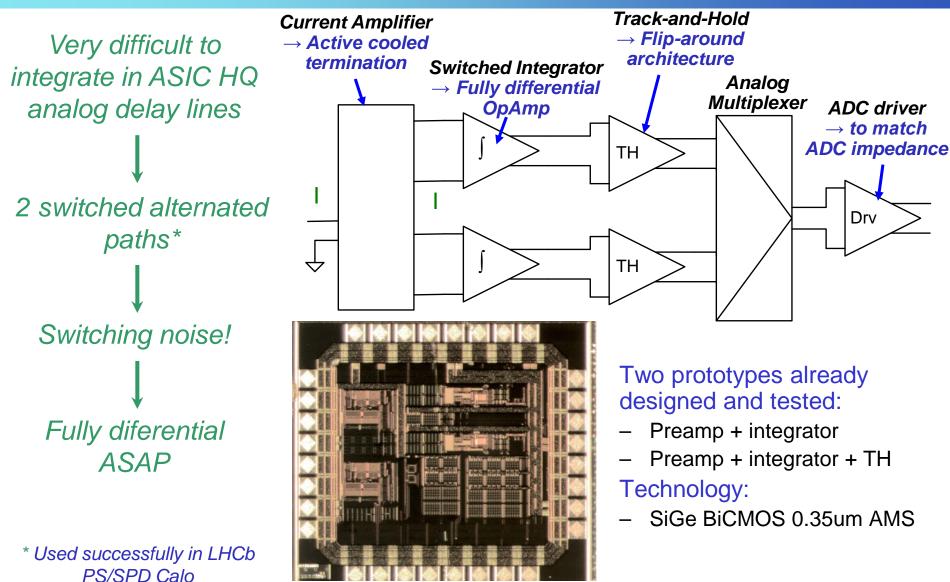

### **ASIC Channel Architecture**

24th April 2013

CHEF 2013

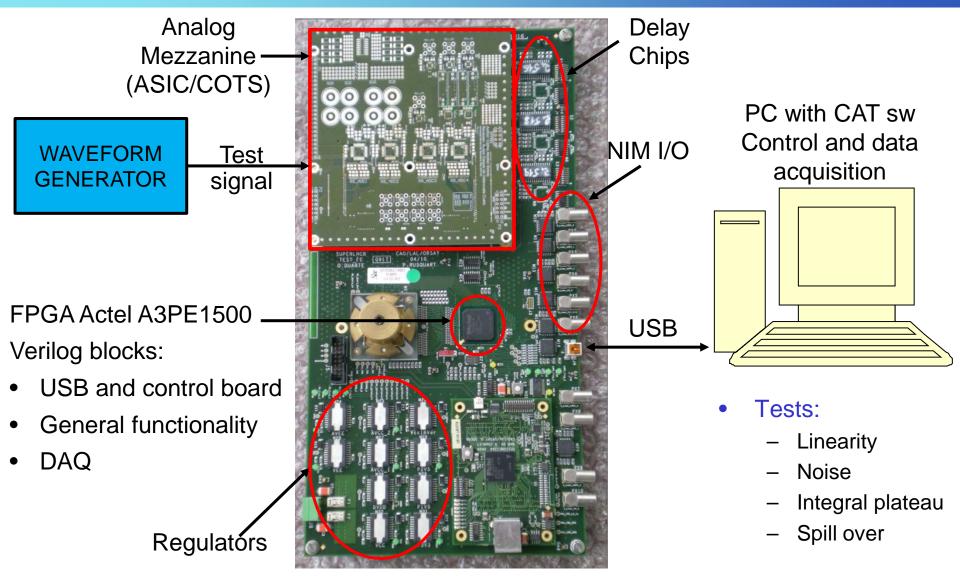

#### **COTS Channel Architecture**

#### Front End Board Prototype Tests

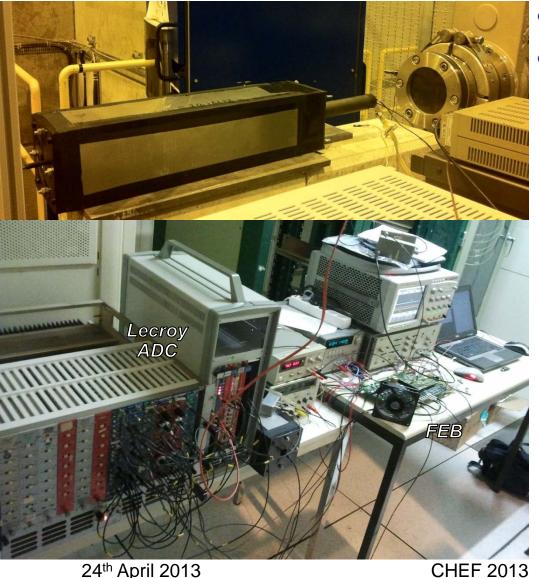

### Test Beam Measurements (Nov. 2012)

#### ECAL channel+PMT+same 12m cable

- Used e- of 50 to 125GeV

- Measurements:

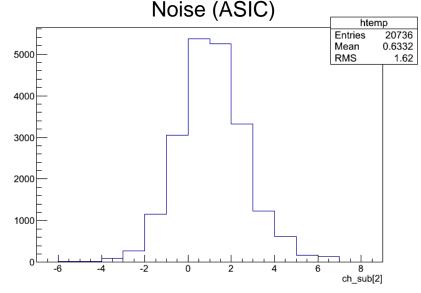

- Noise after pedestal subtraction: ~1.6 ADC (ASIC) and ~2.6 ADC (COTS)

- → Contribution of 10-15% due to the use of a "T" to distribute the signal

11

#### Test Beam Measurements (Nov. 2012)

• Measurements (cont'd):

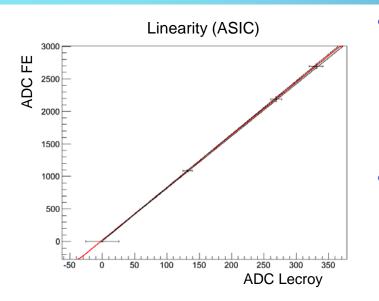

- Linearity better than 1%

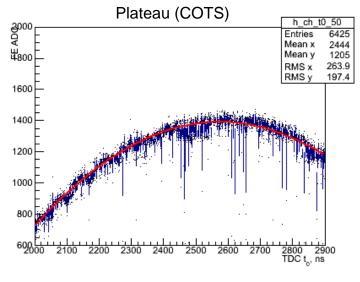

- Integral plateau ~1.6% at ±2ns (ASIC) and <1% (COTS)</li>

- Spill over of ~8% in following sample (ASIC)

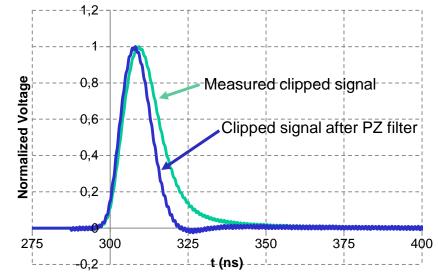

- Pulse width underestimated (due to cable and clipping effects):

- Affects plateau and spill over

- ⇒ Pole-zero filter proposed for final version of ASIC/COTS

24th April 2013

CHEF 2013

#### Summary

- Upgrade architecture with new Front-End electronics board

- 40MHz readout

- Re-use FE crate

- Actel FPGA reprogrammable A3PE family

- Analog shaping electronics: two solutions

- ASIC:

- cooled input termination for reduced noise

- 2 interleaved channels and switched integrators: no deadtime

- Full 4 channel ASIC to be sent in June 2013

- Discrete elements (COTS):

- Clipping removed from PMT base and installed in the FEB: increase in signal

- Definitive version scheduled by end of May 2013

- Final decision before September 2013

- Prototypes tested both at lab and at a test beam

- Radiation qualification tests foreseen

- Technical Design Report (TDR): September 2013

#### **Current Trigger and Readout Architecture**

#### **Upgrade** Architecture