# R&D chip de lecture pour détecteur gazeux en vue d'un DHCAL auprès de l'ILC

Réunion électronique DHCAL France IPN Lyon

Renaud Gaglione

Institut de Physique Nucléaire de Lyon Bâtiment Paul Dirac 4 rue Enrico Fermi 69 622 VILLEURBANNE Cedex

15 février 2008

# Plan

Introduction

Architecture

Carte de test et acquisition

Premiers résultats

Fonctionnalité

DACs

Chaîne complète RPC

Chaîne complète Micromégas

Bruit de déclenchement

Alimentation

## Plan

#### Introduction

Architecture

Carte de test et acquisition

Premiers résultats

Fonctionnalité

DACs

Chaîne complète RPO

Chaîne complète Micromégas

Bruit de déclenchement

Alimentation

# Cahier des charges

Etre compatible avec deux détecteurs pour les comparer dans des conditions similaires :

|                      | GRPC      | Micromégas |

|----------------------|-----------|------------|

| Charge               | 0.1~10 pC | 1~100 fC   |

| $C_{det}\ (1\ cm^2)$ | 80 pF     | 80 pF      |

| t <sub>r</sub>       | 2 ns      | <2 ns      |

| largeur              | 20 ns     | <10 ns     |

|                      |           |            |

...et respecter les caractéristiques temporelles du faisceau :

|                  | Minimum | Nominal | Maximum |

|------------------|---------|---------|---------|

| Nombre de bunchs | 1320    | 2625    | 5120    |

| Période (ns)     | 189     | 369     | 480     |

| Répétition (Hz)  | 5       |         |         |

# Historique

#### 1<sup>er</sup> circuit:

$4\ voies$  analogiques + blocs de test. Fondu printemps 2006. 25 circuits encapsulés. Testés. Concept validé.

#### 2<sup>e</sup> circuit:

64 voies numériques. Fondu printemps 2007. 6 circuits en cours de test.

#### 3<sup>e</sup> circuit:

64 voies numériques. Fonderie printemps 2008?

## Plan

Introduction

#### Architecture

Carte de test et acquisition

Premiers résultats

Fonctionnalité

DACs

Chaîna asmanlista [

Chaîne complète RP(

Chaîne complète Micromégas

Bruit de déclenchement

Alimentation

## **Fonctionnement**

Architecture synchrone sur les horloges (trains et paquets) de la machine :

#### Pendant les trains :

- Faisceau on : intégration des charges ;

- Faisceau off : comparaisons aux seuils, stockage des résultats.

#### Hors des trains :

- Mise en veille;

- Utilisation de l'horloge pour lire les données;

- Slow control.

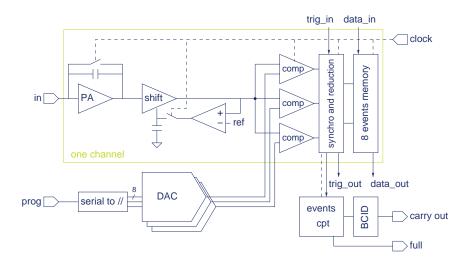

# Synoptique

#### Analogiques:

- 2 blocs de 32 entrées analogiques;

- Sélection du gain;

- Mise en veille.

#### Numériques :

- Entrée/sortie des données séries;

- Horloge;

- Remise à zéro;

- Commande de lecture/écriture;

- Commandes des DAC (in, out, enable);

- Flags : fin de comptage du BCID, mémoire pleine.

# Caractéristiques principales

- Technologie économique AMS CMOS 0.35 μm;

- Consommation <1 mW par voie + power pulsing à 1 % :  $<10~\mu\text{W}$  par voie ;

- 2 gains : 100 mV/pC et 5 mV/fC;

- 3 seuils sur 8 bits pour 1 V (256 valeurs) chacun, soit 3.9 mV/DAC;

- $\rightarrow$  40 fC/DAC et 0.8 fC/DAC

- BCID 12 bits (4096 valeurs);

- Mémoire interne de 8 évènements;

- Amincis à 300 μm pour faciliter l'intégration;

- Brochage facilitant le routage sur le détecteur : entrées de chaque côté.

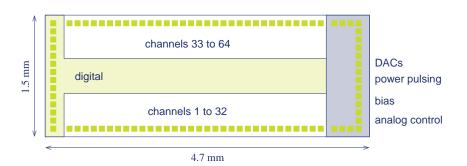

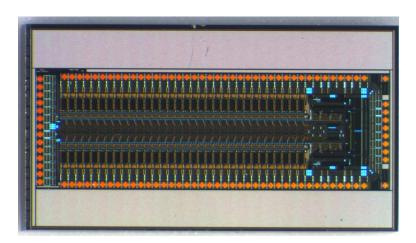

# Description physique

Run MPW CMP A35C7 $\_$ 3. 6 puces encapsulées en boitiers CQFP-144 + 20 puces nues.

Seulement 7  $\mathrm{mm}^2$ .

Introduction

Architecture

#### Carte de test et acquisition

Premiers résultats

Fonctionnalité

DACs

Chaîne complète RPO

Chaîne complète Micromégas

Bruit de déclenchement

Alimentation

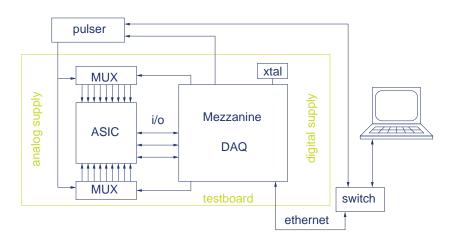

## Banc de test

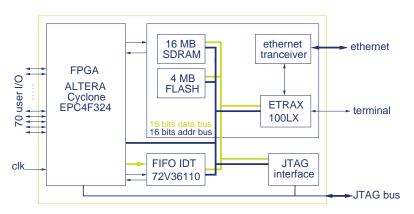

## Mezzanine d'acquisition

Mezzanine de la DAQ d'OPERA (C. Girerd).

# Implémentation

#### FPGA:

- FSM pour la programmation des DACs;

- FSM pour la lecture/écriture des ASICs;

- Gestion de l'excitation des voies;

- VHDL vectoriel qui permet de passer immédiatement à n circuits.

#### MCM:

- Interface ethernet et serveur TCP;

- Routines en C pour le jeu de commandes de l'ASIC;

- Scripts pour les initialisations.

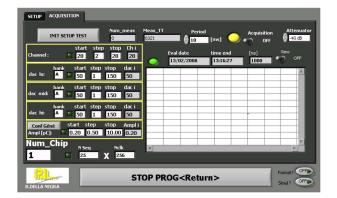

# Carte de test

Banc de test écrit en Labview sous MS Windows pour l'instant. Très facilement transposable dans n'importe quel langage supportant l'envoi de paquet TCP!

## Plan

Introduction

Architecture

Carte de test et acquisition

#### Premiers résultats

Fonctionnalité

DACs

Chaîne complète RPC

Chaîne complète Micromégas

Bruit de déclenchement

Alimentation

## Plan

Introduction

Architecture

Carte de test et acquisition

## Premiers résultats Fonctionnalité

DACs

Chaîne complète RPC

Chaîne complète Micromégas

Rruit de déclarchement

Alimentation

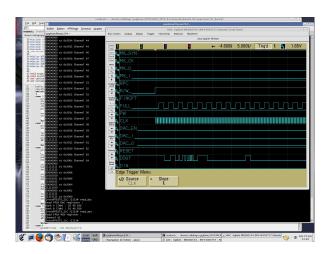

## Premiers tests

Fonctionnel : la voie déclenchée est bien la voie excitée. Les BCID correspondent à la séquence envoyée.

## Plan

Introduction

Architecture

Carte de test et acquisition

#### Premiers résultats

Fonctionnalité

#### DACs

Chaîne complète Micromégas

Bruit de déclenchement

Alimentation

## Bruit

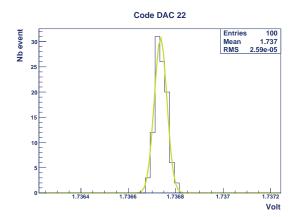

Histogramme du bruit des DACs. Exemple code 22 du DAC n° 1 :

$\sigma \approx$  50 μV pour l'ensemble des DACs testés.

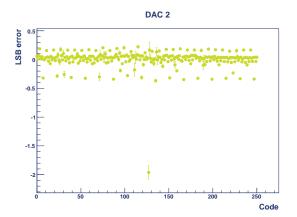

## Non-linéarité différentielle

Exemple de résultat : DAC n° 2 :

DNL=2 LSB

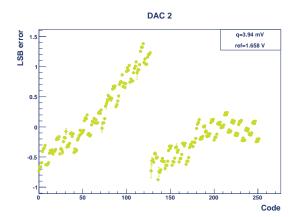

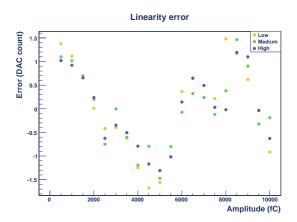

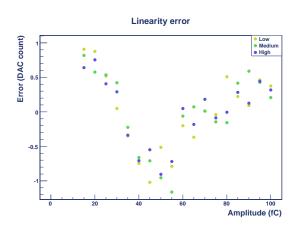

# Non-linéarité intégrale

Exemple de résultat : DAC n° 2 :

Résultat du fit : q=3.94 mV

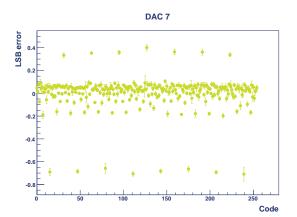

## Non-linéarité différentielle

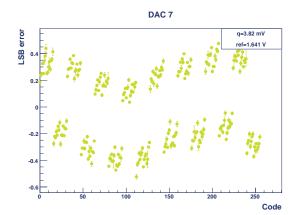

Exemple de résultat : DAC nº 7 :

DNL=1.2 LSB

# Non-linéarité intégrale

Exemple de résultat : DAC n° 7 :

Résultat du fit : q=3.82 mV

Architecture

Carte de test et acquisition

#### Premiers résultats

Fonctionnalité

DACs

Chaîne complète RPC

Chaîne complète Micromégas

Bruit de déclenchement

Alimentation

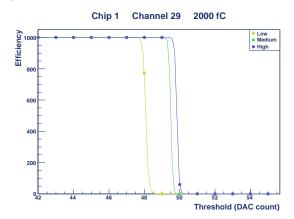

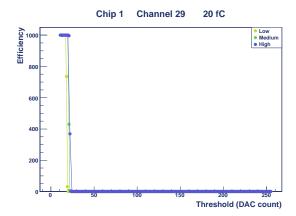

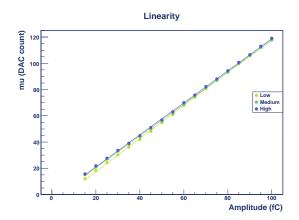

## S-curve

Fit avec une distribution de Fermi-Dirac :

$S(x) = \frac{max}{1 + e^{\frac{x-\mu}{w}}}$  $\mu$  : abcisse du point d'inflexion

w : pente de la courbe

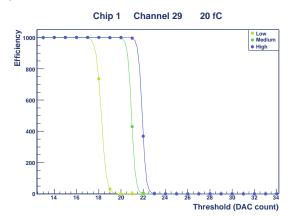

# S-curve (zoom)

C<sub>det</sub>=40 pC

Passage de 100% à 0% <50 fC Dispersion entre les 3 seuils : 2 LSB, soit 80 fC

La dispersion entre les trois seuils dépend de la valeur des seuils : correction prévue !

L'écart à la linéarité est contenu dans  $\pm 1.5$  LSB, soit  $\pm 60$  fC

Introduction

Architecture

Carte de test et acquisition

#### Premiers résultats

Fonctionnalité

DACs

Chaîne complète RPO

Chaîne complète Micromégas

Bruit de déclenchement

Alimentation

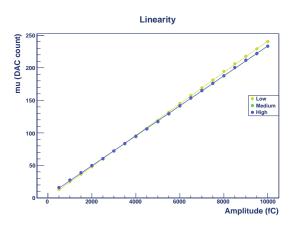

# S-curve (zoom)

C<sub>det</sub>=40 pC

Passage de 100% à 0% <2.4 fC Dispersion entre les 3 seuils : 2.5 LSB, soit 2 fC

L'écart à la linéarité est contenu dans  $\pm 1$  LSB, soit  $\pm 0.8$  fC

Introduction

Architecture

Carte de test et acquisition

#### Premiers résultats

Fonctionnalité

DACs

Chaîne complète RPC

Chaîne complète Micromégas

Bruit de déclenchement

Alimentation

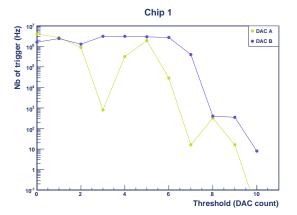

## Bruit de déclenchement

Pas d'entrée. Taux de faux déclenchements en fonction du seuil.

Difficultés pour déclencher convenablement aux seuils en dessous de 10 (semble lié au setup : en cours!).

## Plan

Introduction

Architecture

Carte de test et acquisition

#### Premiers résultats

Fonctionnalité

DACs

Chaîne complete RPC

Chaîne complète Micromég

Bruit de déclenchement

Alimentation

## Consommation

## Courants consommés en $\mu A$ sous 3.3 V :

|      | PAC | Servo DC | Comp. | DAC cells         | OTA DAC |

|------|-----|----------|-------|-------------------|---------|

| Bias | 220 | 6        | 11    | 11                | 13      |

| Voie | 220 | 61       | 3×11  | _                 | _       |

| DACs | _   | -        | _     | $11+0.3 \times n$ | 23      |

#### Soit une puissance dissipée de :

- 13.5 μW/voie pour les polarisations;

- 1 mW par voie, modulo le power pulsing;

- 4 μW/voie pour un DAC au code 128.

# Power pulsing

Temps de mise en route <800 ns.

#### En cours

#### Il reste à faire :

- Baisser le seuil au maximum avec un fonctionnement convenable (nécessite une nouvelle carte de test). Valeurs actuelles: 10 fC en mode micromégas et 200 fC en mode RPC:

- Mesurer les dispersions entre voies et entre circuits.

- Incidence du découplage sur le bruit (mesure du PSRR).

## Plan

Introduction

Architecture

Carte de test et acquisition

Premiers résultats

Fonctionnalité

DACs

Chaîne complète RP

Chaîne complète Micromégas

Bruit de déclenchement

Alimentation

## Premier chip 64 voies réalisé à Lyon!

- Topologie "entrées de chaque côté" ;

- Architecture synchrone;

- Power pulsing;

- Caractéristiques analogiques (linéarité et gain).

## Prochaine version

- Ajouter une correction de pente et d'offset sur les DACs;

- Non linéarité (seuils à 0.1 1 10)???

- Possibilité de masquer une voie bruyante;

- Inclure le circuit d'injection;

- Horloge en LVDS;

- Correction d'un bug mineur sur la logique de déclenchement;

- Sortie analogique (différentielle?) multiplexée.

R. Gaglione 15 fév 2008 Evolutions 46 / 47

Merci de votre attention!