#### The ATLAS tracker upgrade towards the SLHC era

#### G.Calderini (LPNHE, Paris)

on behalf of the French Laboratories working for this effort

# Why working now for the upgrade?

Every time that people think about the luminosity upgrade, there is the impression that it's a very distant phase in the future

So, why to bother with it now?

#### General answer)

Everybody who took part to the design of an experiment knows that it takes several years (the construction and installation itself is typically 5-6 years, after the R&D and design phase is finished) Time flows fast!

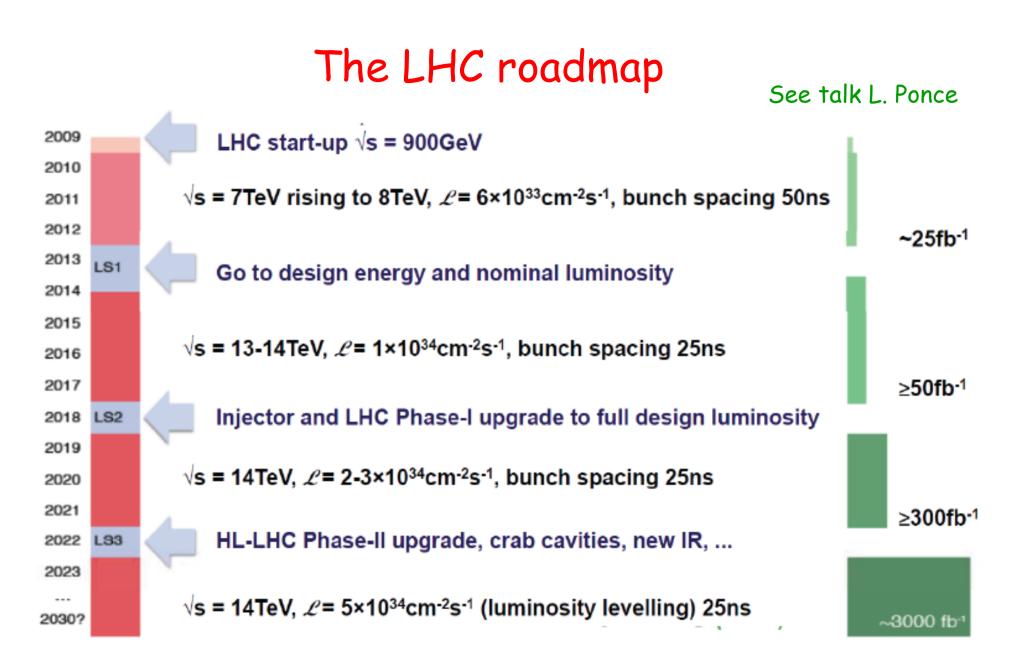

("Not-so-obvious-to-everybody" answer) LHC will not be the same between now and 2020 Radical improvements making it impossible to run until then with the initial detector ("Phase I upgrade")

#### Just a reminder of the present Silicon Tracker

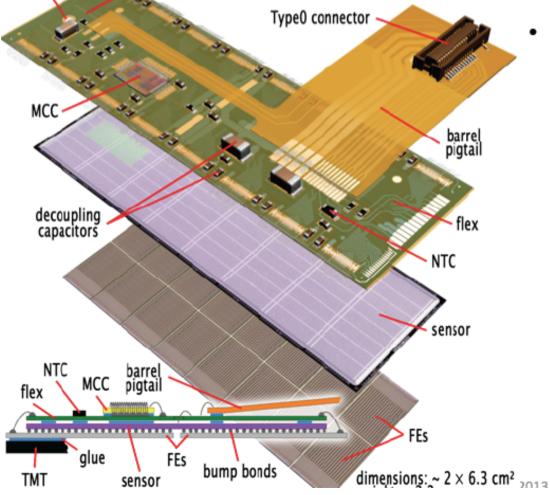

#### A FE-I3 based pixel module

- Sensor: planar 250 µm thick n-on-n sensor

- Typical pixel size 50 x 400 µm<sup>2</sup>

- Bias voltage 150 V (up to 600 V)

Readout:

(50 x 600 µm<sup>2</sup> pixels in gaps between FE chips)

- 16 FE chips, 2880 pixels each

- 47232 (328 x 144) pixels

- Zero suppression in the FE chip

- Controller ( MCC ) builds

module event

- Charge measured by means

of Time over Threshold

- Data transfer 40 160 Mbit/s depending on layer

л

### First tracker upgrade: the IBL

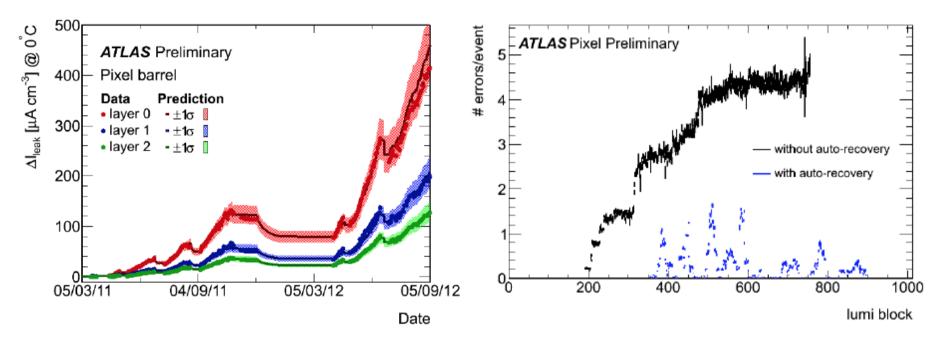

The present tracker (especially the layer\_0) will be in trouble at a certain point due to radiation damage and occupancy

## Behavior of leakage current normalized at 0C as a function of date

Module de-synchronizations at the beginning of each fill (FE-I3)

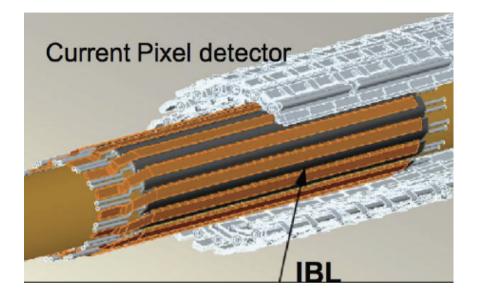

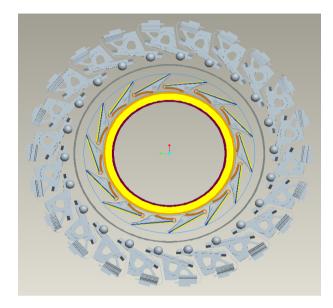

#### The IBL: Insertable B-Layer

Fourth hit in pixel tracking Small radius 3.3 cm (beam pipe 2.65 cm) Low material budget of 1.9% X0 Smaller segmentation (50x250 um) Higher dose tolerance (FE-I4, 250 Mrad) 14 staves with 32 FE-I4 chips per stave Planar n-in-n (double chips) 3D n-in-p (one chip) at high-eta

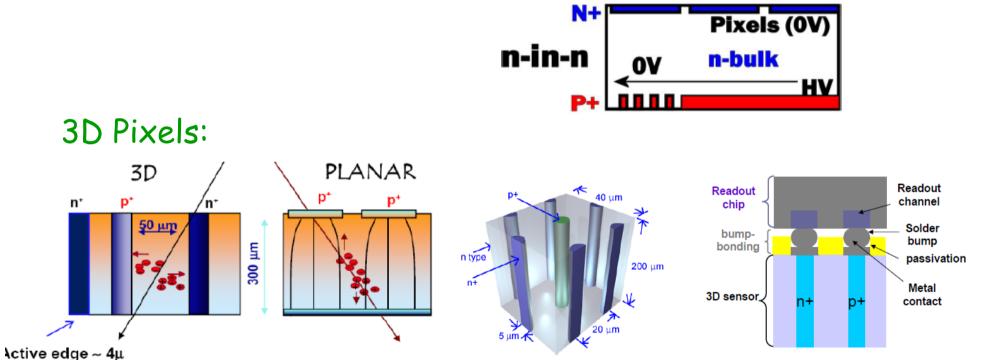

## Two sensor technologies co-exist in the IBL Planar pixels n-in-n

- The same technology used in the present trackers

- Well known and tested

- Here the electrodes are columns passing from one face to the other

- In this way the electric field is parallel to the face of the sensor and the charge drift evolves in a few tens of um

- Intrinsically more radiation hard G.Calderini – LHC France Annecy 2013

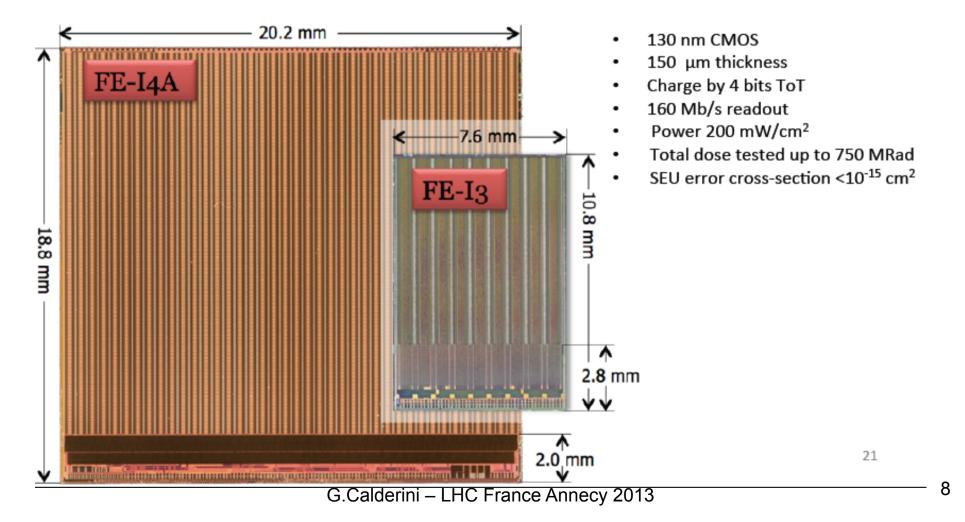

## Upgraded readout electronics: the FE-I4

- Largest hybrid pixel chip in HEP 80 col x 336 rows of 50x250 μm pixels

- 26880 pixels, 80M transistors, up to 200 kHz trigger rate

- maximize active area, reduce bump bonding cost

- distributed memory, zero suppression inside pixels, small size periphery

- time-walk improved by digital treatment inside 4 pixel regions

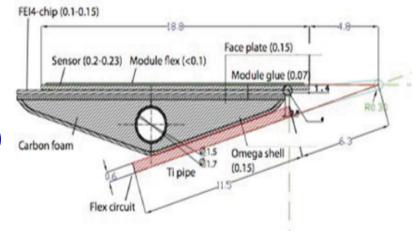

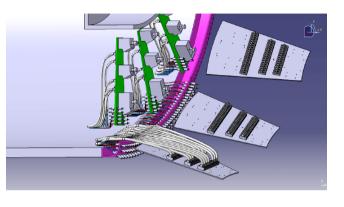

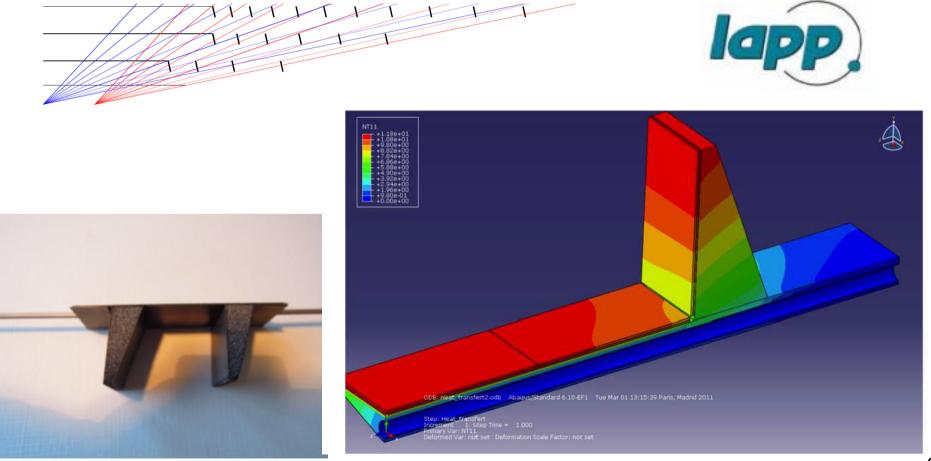

## Big French contribution in the design of services

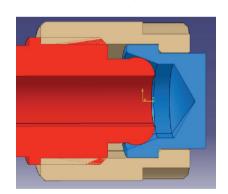

Design of PP1 connections

Fittings and Ti pipes

lapp

- No industrial solution fitting the IBL envelope (and PP1!) - Leak tight @ 20bars CO2, radhard (no organic), reliable

design much more relaible of the present ATLAS fitting Electron beam welding, laser welding, brazing techniques under investigation (already good results)

#### **IBL** status

#### Two staves (OA and OB) already produced and tested

Now entering 'factory' mode

#### Access for installation has started

Pixel detector will be brought to the surface and undergo maintenance (4% of dead modules should be hopefully repaired)

G.Calderini

## The long-term upgade: 'Phase-II'

#### Physics

- Higgs: BRs, self-coupling

- WW, ZZ scattering

- W', Z', quark substructure

Completely new tracker (more pixels layers + strips)

- LOI in preparation for running after Phase-II (-2030, 3000 fb-1)

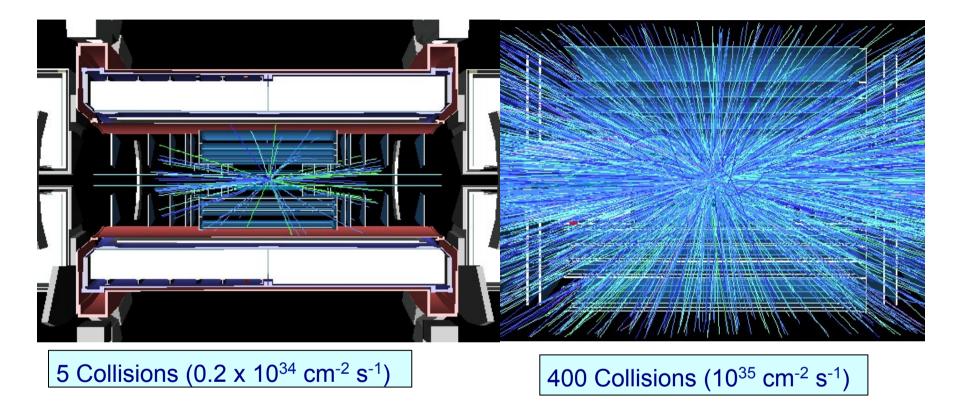

- Leveled luminosity of 5 x 10<sup>34</sup> cm<sup>-2</sup> s<sup>-1</sup>

- Innermost layers should be rad-hard up to 1 Grad

#### Critical R&D necessary

- Sensors

- Electronics

- Strong dependence on the general design

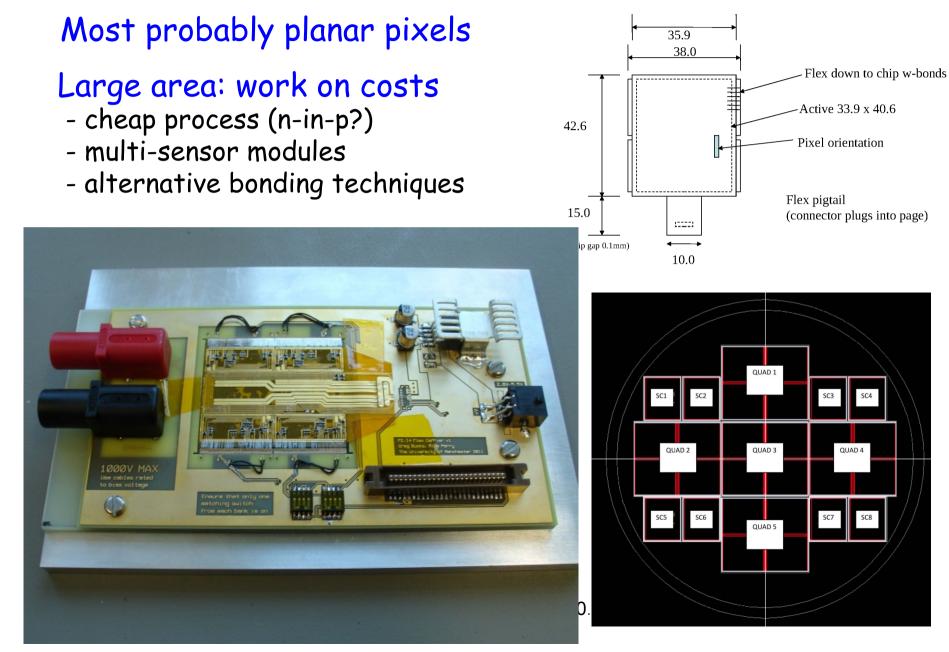

## Sensors

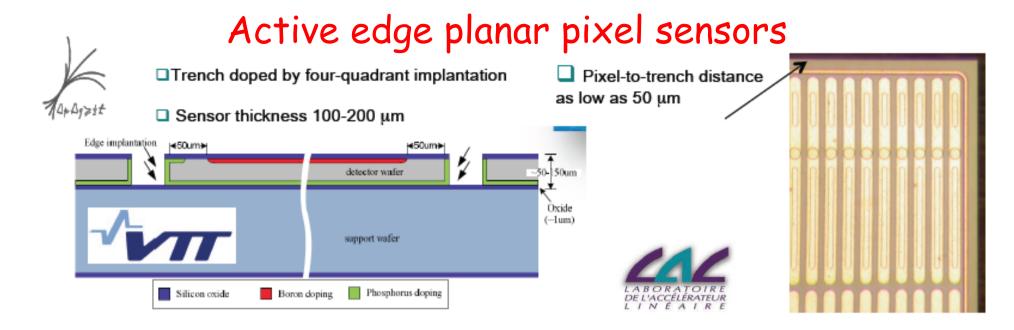

Need to go to radiation hard  $\rightarrow 2 \times 10^{16}$ thin  $\rightarrow < 200 \ \mu m$ cheap  $\rightarrow$  n-in-p (?), new bonding techniques ? efficient  $\rightarrow$  reduce the inactive region at the edge

As mentioned, a big effort has been made on n-in-n and 3D pixels, already at this time for the IBL construction. This will go on.

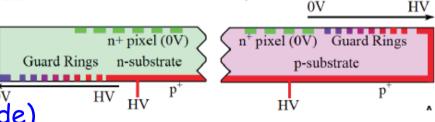

In parallel, n-in-p planar pixels are also being developed

- Promising technology

- p-type doesn't invert with dose

- cheaper (pixel and GR on the same side)

We think n-in-p will become very important in view of tracker replacement

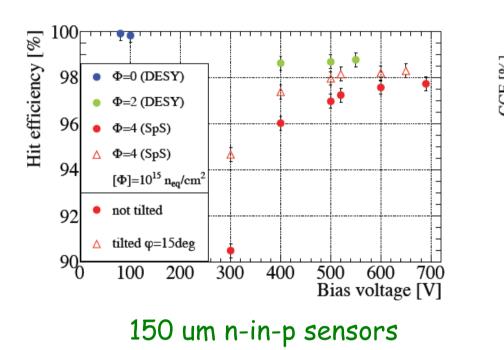

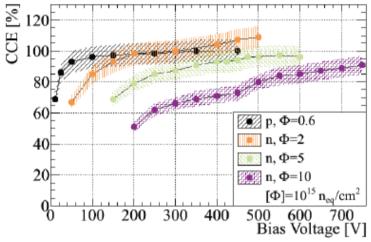

#### Thin sensors to reduce the material budget and optimize the charge collection efficiency

A.Macchiolo et al, arXiv: 1210.7933

75 um n-in-p sensors

In a partial depletion regime, the undepleted region is just acting as a charge trap

Trench doped by diffusion

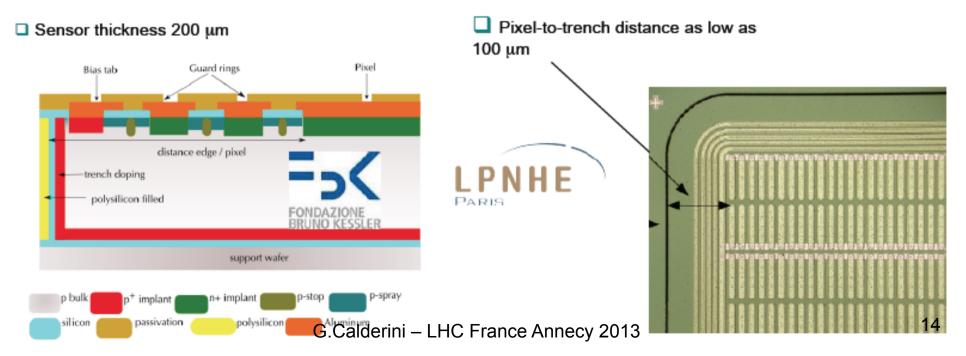

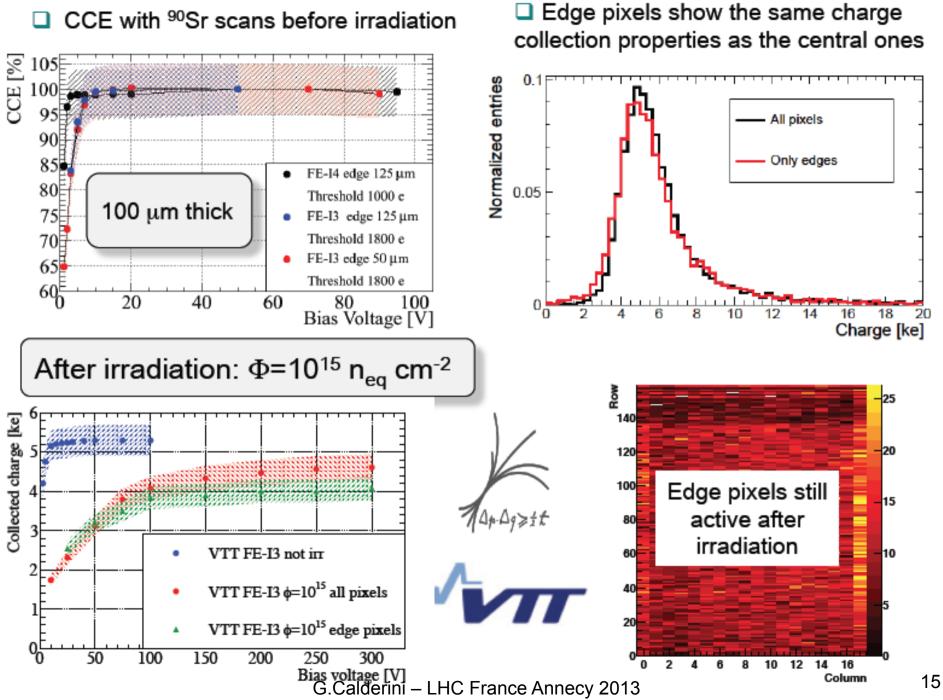

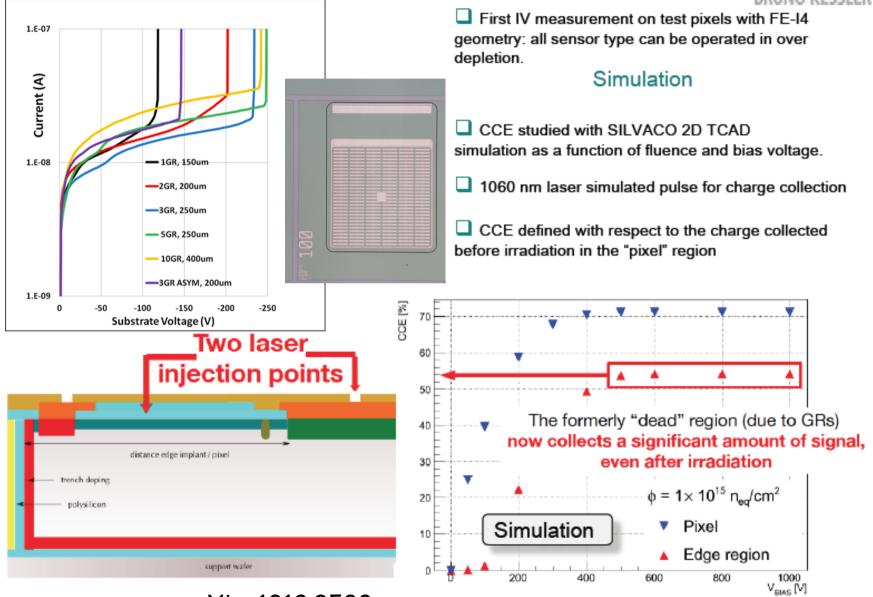

#### Active edge pixels – FBK LPNHE

M. Bomben et al., arXiv: 1212.3580

īΟ

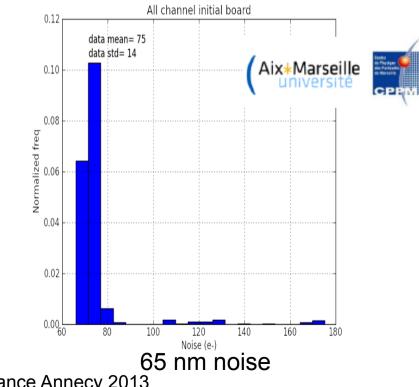

## **Electronics**

Huge work on the readout electronics to improve performance and radiation hardness

- Going to deep-submicron process (now 65nm, then more)

Intrinsically more radiation hard

Allows smaller segmentation

- 3D/Vertical Integration R&D

- Save space

Allow separation of functionalities (analog vs digital)

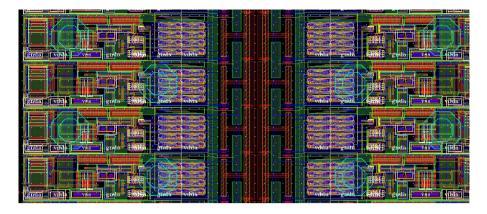

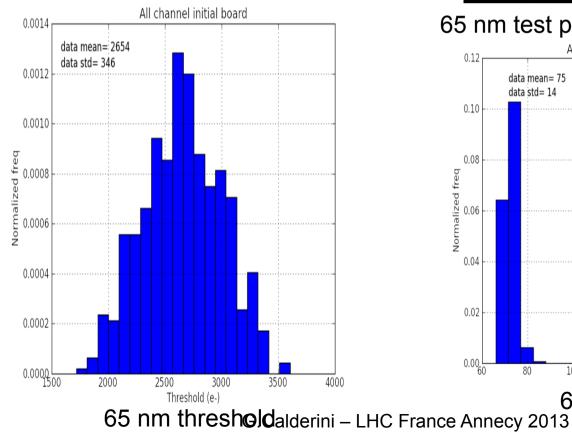

#### 65 nm prototype, 25 x 125

#### 65 nm test pixel matrix 16col x 32 rows

G.Calderini – LHC France Annecy 2013

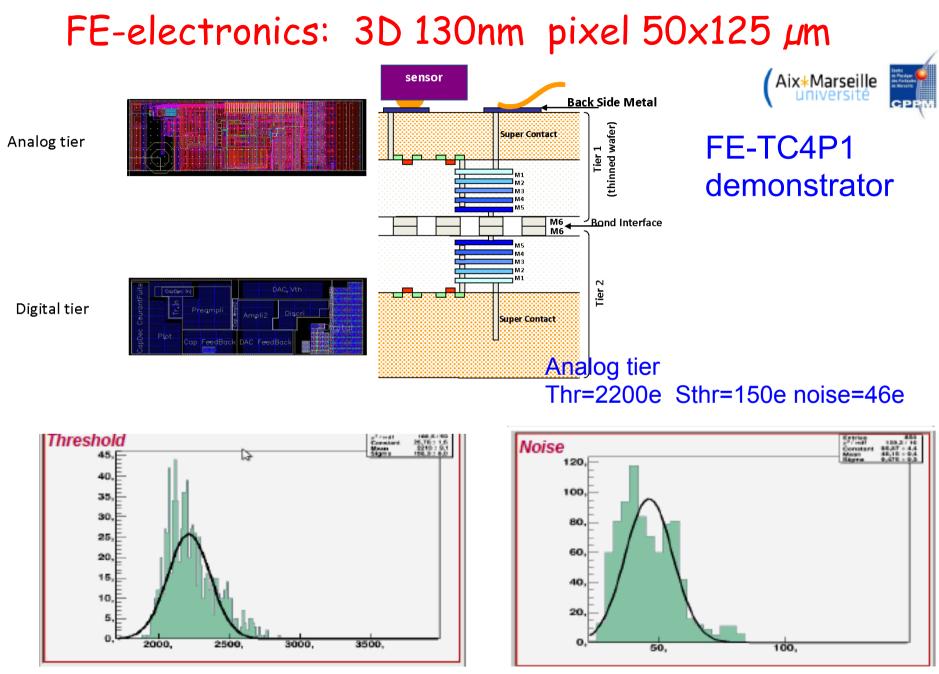

### **HV CMOS**

# Monolithic sensor+electronics 180nm HV2FEI4 ATLAS chip with capacitive coupling to FEI4 subpixel 33x125 $\mu m$

## **Outer Pixels**

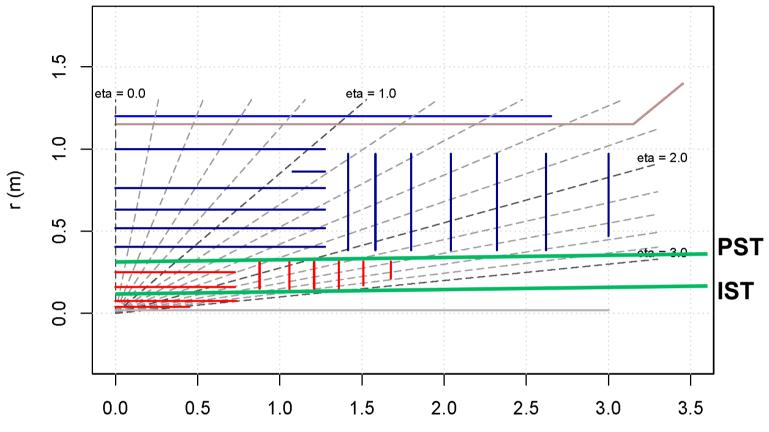

## Lol layout

- Classical layout only barrel cylinders and disks

- Radius of the PST R=34.5 cm bigger than current radius R=24.5 cm

- 2 innermost pixel layers should be replaceable in IST R=11 cm

- Full pixel package should be replaceable

## Lol pixel layout

- Innermost pixel layer: 3.9 cm, second 7.8 cm

- Outer pixel layers at 16 25 cm

- Eta pixel coverage up to 2.7 to match muons

- Barrel part of 4 pixel layers

- 6 pixel disks z=88-168 cm

- Up to 8 pixel hits at high n > 2.0 reinforced

- Inner+Outer+Disk= 0.8+4.3+3.1= 8.2 m<sup>2</sup>

- 638 Millions of pixels

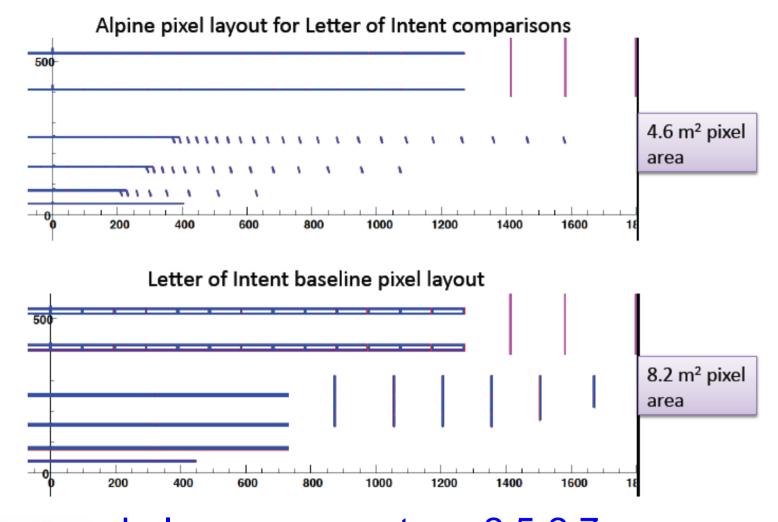

### Some design allows to reduce the surface

#### Lol coverage up to n=2.5-2.7 Some aggressive design to extend it to more than 4

G.Calderini – LHC France Annecy 2013

- "Alpine staves" in LoI layout

- Possibility to reducing number of disks

G.Calderini – LHC France Annecy 2013

# Conclusions

- Remarkable French contribution to the ATLAS tracker upgrade effort

- The calendar between now and 2020 is already very tight and dense. Time flows fast ! Move quickly !

- LHC started in an impressive way

- We cannot afford having detectors which don't keep the pace of the machine !

- In exchange for high luminosity, running conditions could be different from design ! We need safety margin !

- Most likely not enough funding to have independent CMS and ATLAS R&D programs We need to work together !