#### INFN - Milano University of Milano Department of Physics

### Digital Preamplifiers: Where we are ?

#### Alberto Pullia

10th AGATA Week Nov. 22- 26, Lyon, France

Speaker: Alberto Pullia Nov. 23, 2010

Speaker: Alberto Pullia

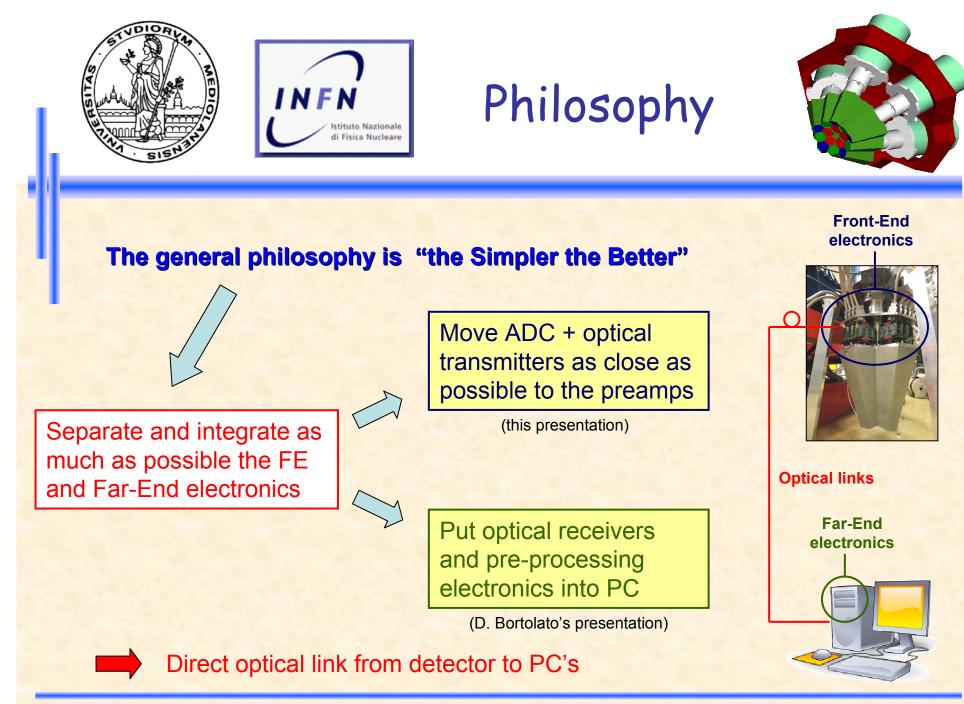

- System structure as simple as possible cost effective, compact, low power

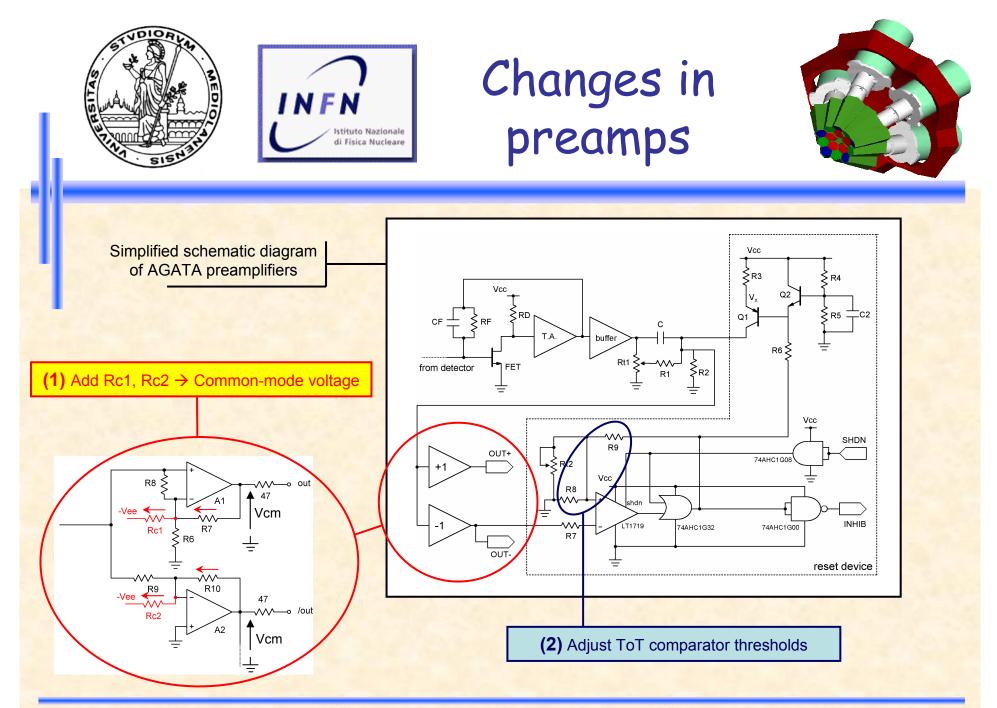

- Precondition the preamp signal to match the ADC specs differential signal with proper common-mode level

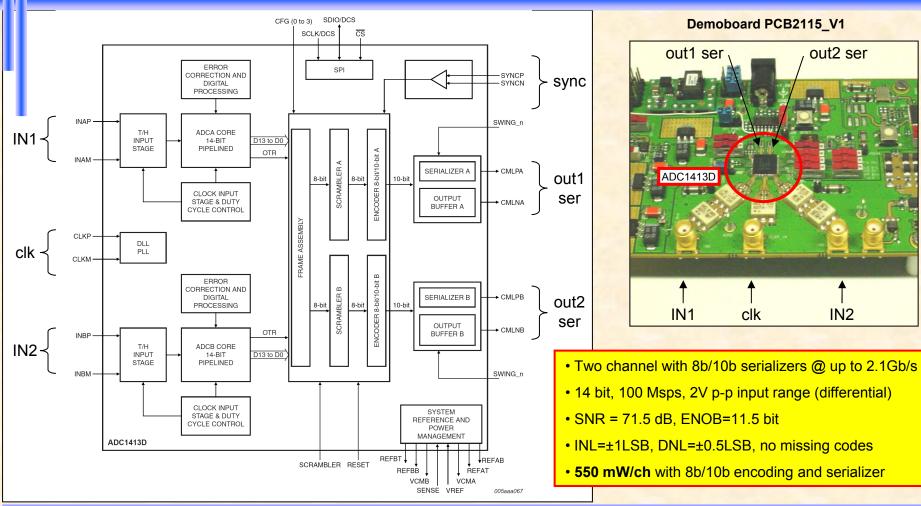

- Use of state-of-the art ADC's and Transceivers performance @ low-power consumption

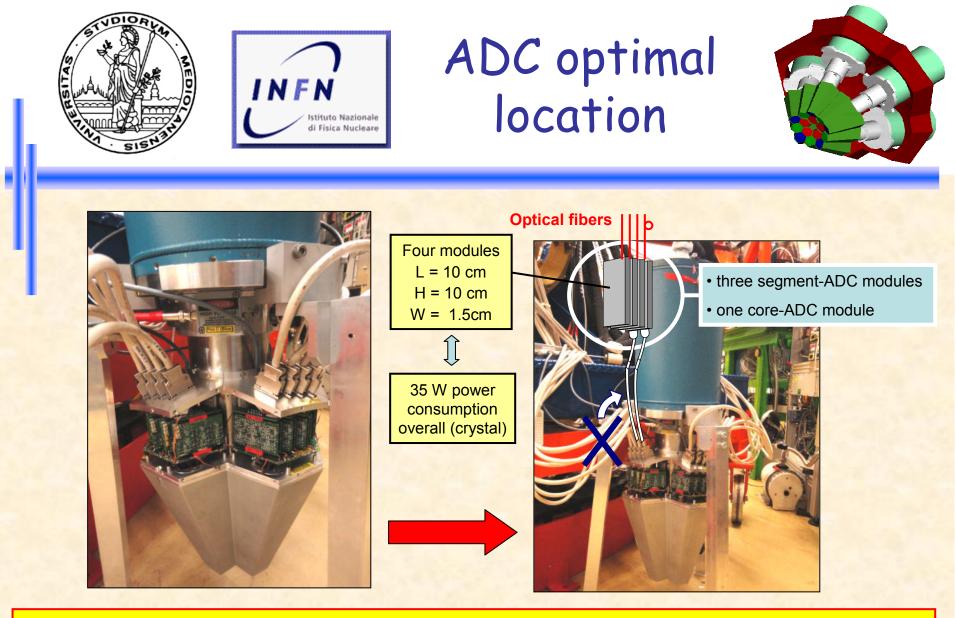

- Move ADCs/optical-transmitters close or on preamps low noise, no termination-resistor needed

- Minimize digital transmission errors 8b/10b encoding

## Power consumption

#### Estimation of power consumption for a 12-ch ADC module

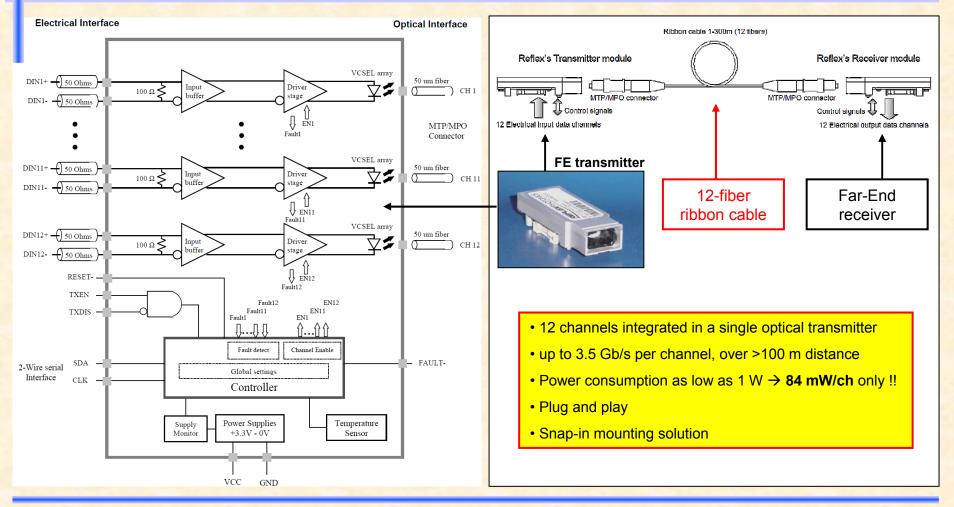

| ADC+8b/10b ser encoding:<br>(NXP ADC1413D105) | ~1200 mW × 6 = 7.2 W | (3V, 1900mA - 1.8V, 800mA) |

|-----------------------------------------------|----------------------|----------------------------|

| Optical Transmitter:                          | ~1.2 W (3.3V, 364mA) |                            |

Overall (nominal):

~8.4 W

Assuming 20% more power for other functionalities (PS voltage regulators, clock distribution etc) Overall (realistic): ~10 W (for n. 12 ADC chs w 8b/10b encoder, ser & optical transmitter)

Power per digital channel: ~0.8 W/ch

(the most power-eager block is 8b/10b encoding + serialization, which sinks as much as 450mW/ch) to be compared with 0.28 W/ch of the analog part (single segment preamplifier channel)

A digitizer + 8b/10b encoder + serializer + optical transmitter consumes three times as much as a preamplifier channel. Too much to be fitted into cryostat !

Speaker: Alberto Pullia

This scenario is much less "invasive" than putting the ADC's on the preamps !

> We will work in this direction first. The ADC (alone) could further move towards the preamplifier in a second R&D phase

Speaker: Alberto Pullia

Speaker: Alberto Pullia

Speaker: Alberto Pullia

# The optical transmitter

Speaker: Alberto Pullia

# Schedule and cost

- Man Power: 1 FTE

- Time needed: 12 months after qualification of ADC

- Estimated cost of digitizer: ~Eur 200,00 / ch

Istituto Nazionale di Fisica Nucleare

- Qualification of NXP ADC1413D coming soon, with factory demoboard as linked to AGATA pre-processing electronics

- Prototype development to start immediately after qualification