## Possible avenues of Pulse processing

## Vandana Nanal, TIFR

- R&D in digital signal processing in our lab

- ASIC development in India

- Possible contribution to PARIS readout

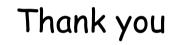

# DSP based DAQ for 24 CS-Clovers and Ancillary detectors INGA at TIFR (R. Palit, TIFR)

- ■100 MHz & 12-bit ADC's

- ■Data rate: 80 MB/sec

- E resolution better than analog

- Handle high count rate with good E,T.

- Particle ID in CsI detectors using digital pulse shaping

- ■Trigger less system

- ■For in-beam Clover + CsI expts and off-line expts with planar detectors.

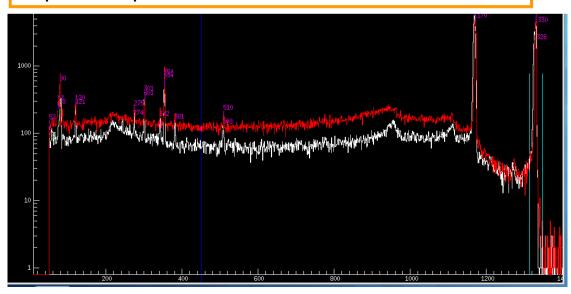

Commercial PXI system

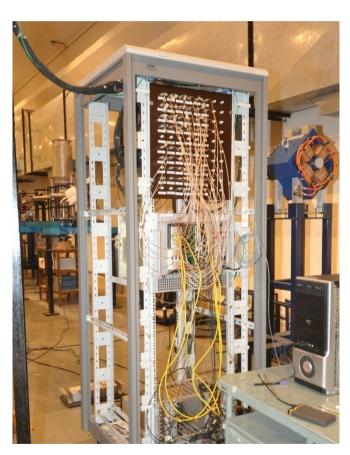

## Coincident spectra for level scheme of <sup>185</sup>Au with New DDAQ

## R&D on digital electronics (J.A. Gore & S.G. Kulkarni, NPD-BARC)

- High speed analog I/O board

- High speed digital I/O board

- BPM digitizer

- CAMAC modules

- Controller

- ADC, DAC

- Output register

- Stand alone analog I/O board

## High speed digital I/O board

#### Features:

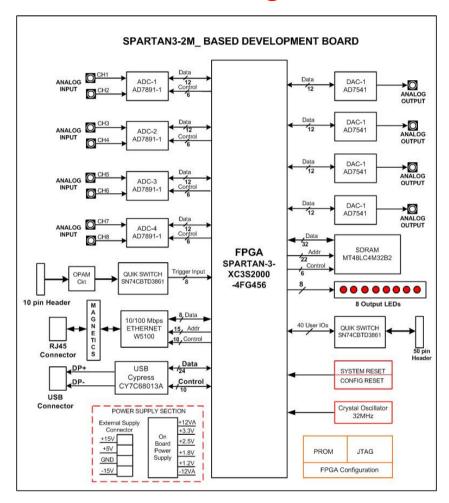

- Spartan -3 (XC3s400)

- 140 impedance matched I/Os

- RS-422 interface

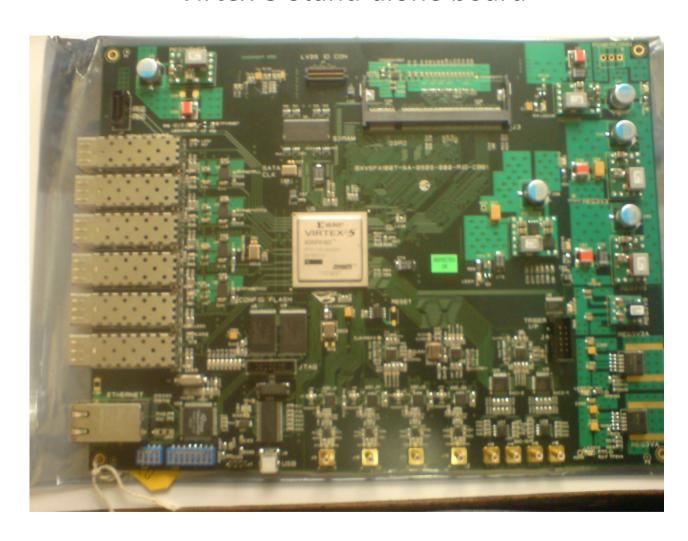

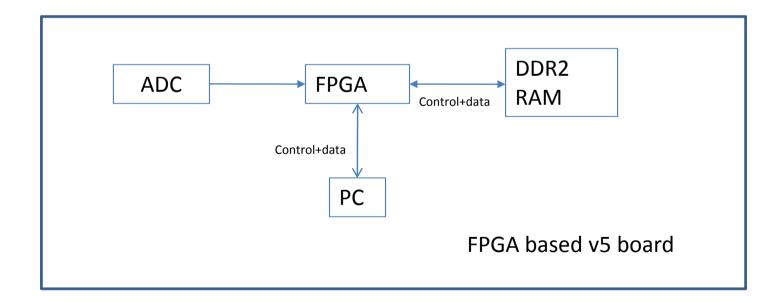

## Virtex-5 Stand-alone board

### Standalone analog I/O board

- •Plan to use for Low level RF control

- •Board with 1 GHz sampling rate has been designed, fabrication in process

#### **Board Details:**

- 4, 14 bits, 125 MHz Analog inputs.

- 4, 14 bits, 125 MHz Analog outputs.

- On-board, 2 GB DDR2 RAM.

- 6 SFP connectors (Connected to Rocket IO), Tested

@1.5Gbps

- On-board USB and ethernet interfaces.

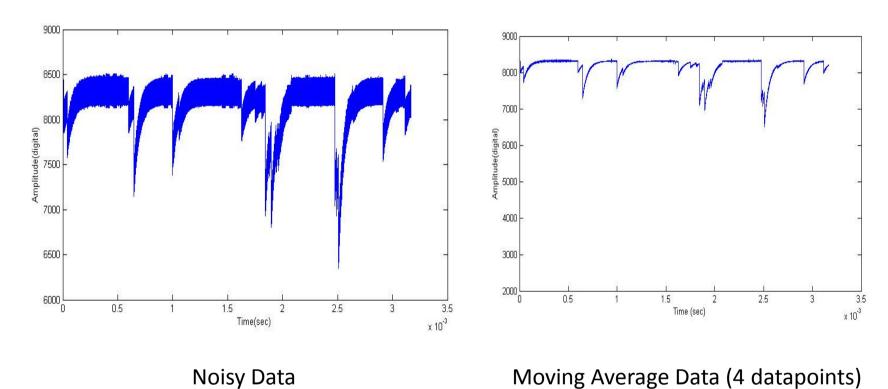

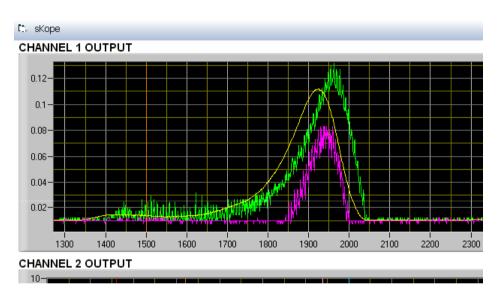

## Pulse\_data

- •Data Acquired for ~3 msec.

- •Filtered with a simple moving average filter implemented in VHDI

- •Data transfer through a USB interface.

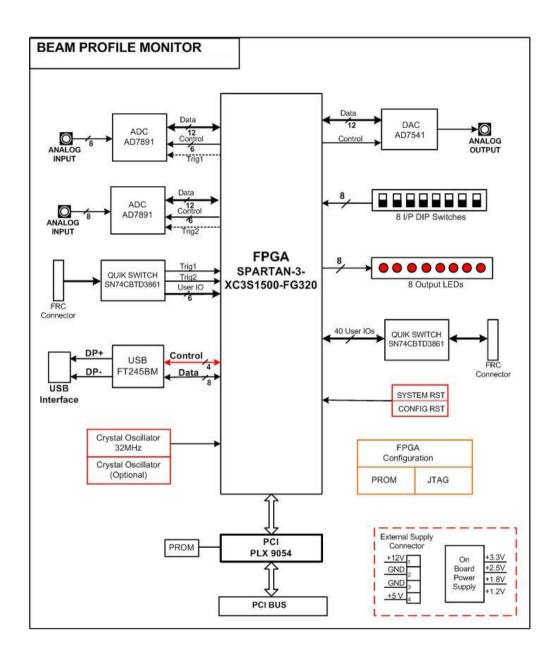

#### FPGA based boards designed and developed

#### Beam Profile monitor digitizer

- 12 bit, upto 500KHz, 2 channels

- 32 bit, 33 MHz PCI interface

#### GUI in visual basic for BPM

40 uncommitted I/Os can be used to acquire/control additional accelerator

parameters.

#### **PCI-Express card**

- •8 lane interface with PCI Express and uses Xilinx Virtex-5 FPGA for protocol implementation.

- •48 differential pairs for interfacing with external components .

- Two SFP fibre channel interfaces which can facilitate high speed data transfer from PC to other devices.

#### ASIC developments in India

V.B. Chandratre et al., BARC Newsletter Oct. 2007

### Detectors, devices, modeling new process:

Silicon strip detectors micro/macro & pixel, Avalanche photodiode (APD), Silicon drift detectors (SDD),

Extended gate devices

Novel semiconductor process development with Spice modeling & PDK development

## • Application Specific Integrated Circuit design :

ASICS for detector signal processing PDK kit integration

## • System Circuit design & prototyping :

HMC, FPGA, IP core, device driver development

#### Nuclear Instrumentation: Detectors, ASIC's and Hybrid Microcircuits (HMC's)

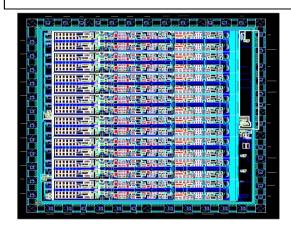

#### ASIC's: 0.7u Mixed CMOS Process

#### **Detector Front-End Signal Processing ASIC's**

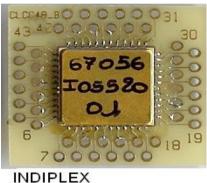

**INDIPLEX**

16-Channel Pulse Processing ASIC

ANU-SHIKHAR ASIC

**SINGLEPLEX**

Single Channel Pulse Processing ASIC

Low Noise Pulse Processing Channel for Silicon Drift Detector

## Sensors : Silicon Drift Detectors

Hexagonal SDD

Linear SDD

SDD with Jfet

**Imaging Array**

#### **Data Conversion ASIC's**

Low Power Peak Detect & Hold Circuit

ANUSMRITI ASIC

128-Cell, 500MHz Analog Memory

Spiral SDD

### Hybrid Micro Circuits (HMC's) "Singleplex" ASIC in Hybrid

FS 500ns-10us Resolution 75ps@500ns FS

Time To Amplitude

Converter

Peak stretcher for 8K Nuclear ADC

For Neutron Monitors

Fast Preamp family for Indian neutrino Observatory Gas RPC tr 1.5 ns 27,000 Qty requirement

## Indiplex and Singleplex ASICS Sub-micron 0.7u CMOS process

**INDIPLEX:** 16 channel pulse processing ASIC comprising CSA, PZ-block & Semi Gaussian shaper.

#### **SINGLEPLEX:**

Single pulse processing channel ASIC similar to INDIPLEX

High Dynamic Range (+/- 600fC)

Low Noise with Low Noise Slope (600e @0pf, 7e/pf Noise slope)

Output Signal Swing +/-2V

Active DC pedestal cancellation

Optimized for Proportional pad detectors made BY VECC for ALICE experiment

## ANUSMRITI ASIC Analog Memory

Digital delay line based analog memory

## **Specifications:**

Read-out Frequency 1 MHz

Dynamic range 2V

Power Supply 0-5V

Power Consumption 400mW

Die Area 4.5 mm by 2.5 mm

Package CLCC-44

High Speed transient Digitization 500MHz, 128 bin

#### ANU-KSHAN ASIC

#### DLL based Time to Digital Converter

Anu-Kshan is a DLL based Time to Digital Conveter implementing real time stamping of events with a resolution of 65 psec.

#### **Key Features:**

- 10 MHz Reference Clock

- 32-bit coarse counter for real time stamping

- Delay Locked Loop based Vernier Counter providing 1:100

## Various ongoing projects involving R&D on digital signal processing

- Nustar/R3B FAIR

- Exogam2

- SPIRAL2 BPM readout

- RPC based large scale detector at Indian Neutrino Observatory

- Cryogenic bolometer array for neutrinoless double beta decay

## What we plan to do for PARIS

- Tests with 2x2 cluster with 4 LaBr<sub>3</sub>+NaI Phoswich

- Start with PXI based system/ Commercial CAEN system for LaBr<sub>3</sub> and phoswich readout

- Sampling rate 100 MHz- 1GHz

- Contribute to R&D as well as production of Readout electronics

- Contribute 4 detectors to prototype

- R&D on 1"/2" CeBr<sub>3</sub>