# DCC pour DHCAL Calice (un projet autour du partage de code)

Journées VLSI/IN2P3 - 2010

Franck Gastaldi LLR Polytechnique

### IR

## Sommaire

- Aspect scientifique du projet

- Présentation du projet

- Spécifications

- Architecture fonctionnelle de la DAQ

- Firmware: blocs fonctionnels

- Solutions utilisées

- Organisation des tests

- Quelques résultats de tests

- Conclusion

# Aspect scientifique du projet

- Etude d'une DAQ pour le calorimètre hadronique semi-digital dans le cadre d'une R&D de détecteur pour un futur collisionneur linéaire

- Concept DHCAL :

- compter le nombre de cellules touchées pour calculer l'énergie déposée par la particule incidente.

- Avantage :

- Faible quantité d'information à transmettre

- Faible consommation

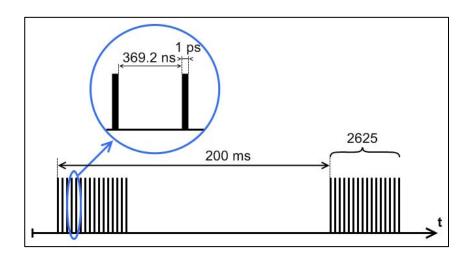

- Structure en temps de l'ILC :

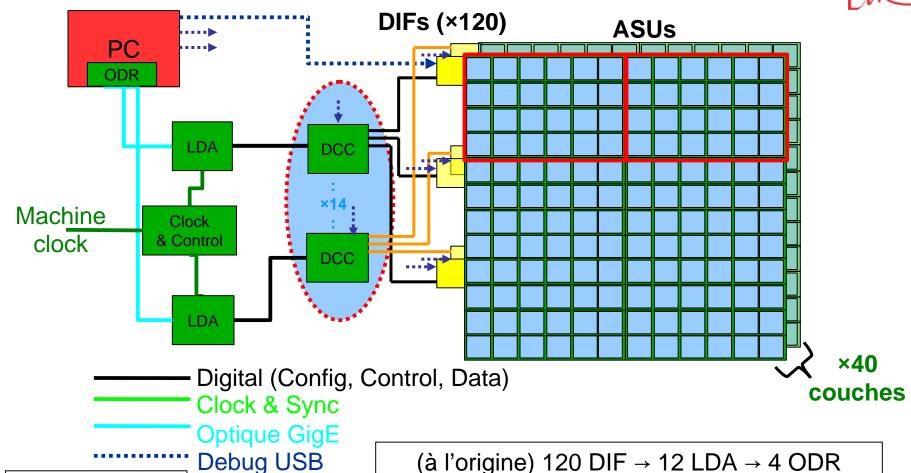

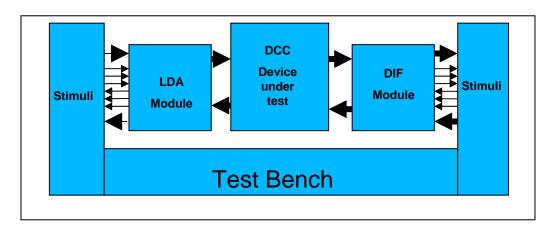

LDA: Link Data Aggregator

**DIF**: Detector InterFace

**ODR**: Off Detector Receiver

(à l'origine) 120 DIF → 12 LDA → 4 ODR

(à notre arrivée) 120 DIF → 14 DCC → 2 LDA → 1 ODR

- But principal

- Réduire le nombre de cartes LDA et ODR

- Être autant que possible le plus « transparent » sur la chaine DAQ

- Caractéristiques

- Envoyer/Recevoir des données & l'horloge d'une LDA

- Piloter 9 voies DIFs

- 1 DIF gère environ123 KB

- Débit par voie 50 Mb/s

- Connexion HDMI

- Distribuer l'horloge

- Distribuer les Commandes rapides

- Distribution ou accès unique pour l'envoie de commandes de configurations

- Lire les blocs de données provenant des DIFs les uns après les autres en les identifiant

- Permettre un accès USB pour un contrôle lent sur la DCC (debug,...)

# Architecture fonctionnelle de la DAQ

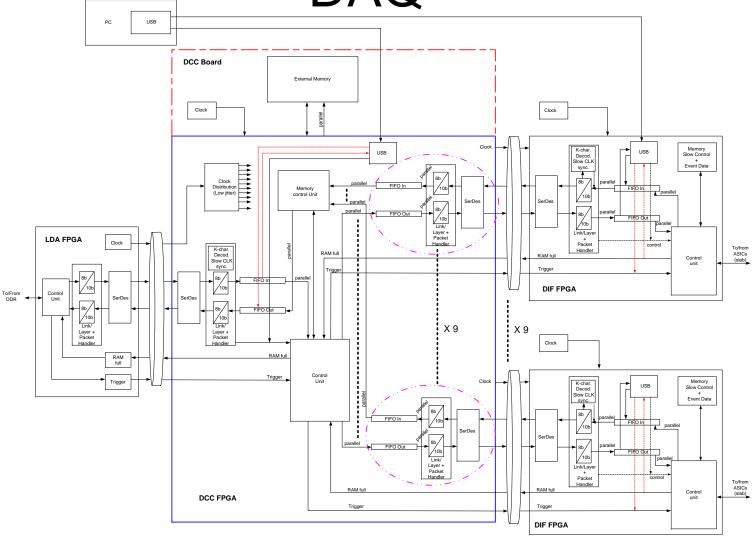

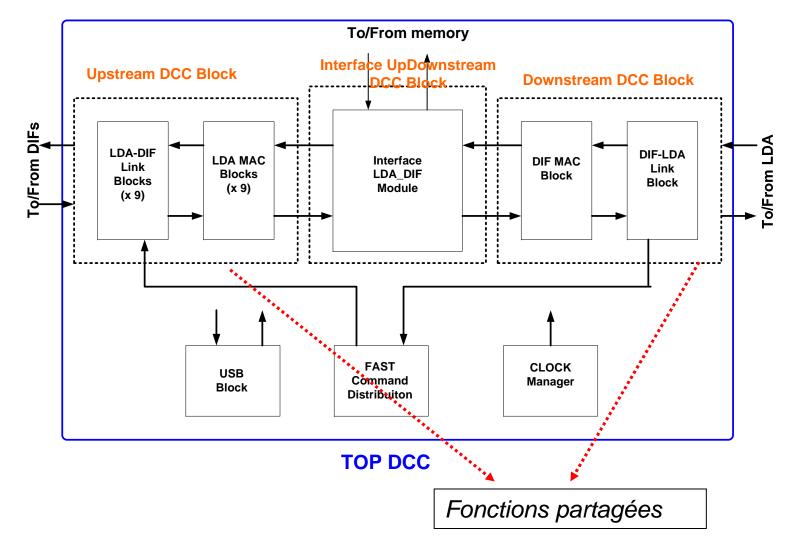

# Firmware: Blocs fonctionnels

## Solutions utilisées

- Réutilisation et partage de code

- « Reference design » FPGA

- Blocs fonctionnels communs

- Outil de partage : SVN/CVS

- Outils mis en œuvre en interne

- XILINX ISE 10.1.03

- Modelsim XE III/Starter 6.3C

Architecture de simulation

- Fabrication de 2 prototypes

- Possibilité de les utiliser en mode LDA ou DIF

- Tests « basic » via USB

- Validation de la communication sur le lien série

- Matériel mis en œuvre

- PC: software de tests en langage Python

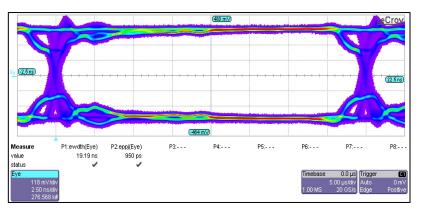

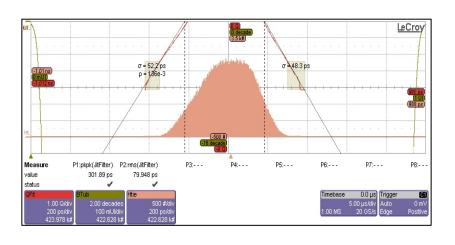

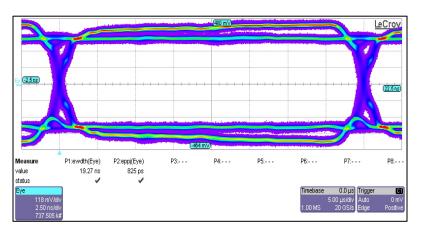

- Validation du lien : Analyseur de données série Lecroy:

- SDA 1100 avec décodage 8B/10B

- SDA 735ZI avec hardware trigger et décodage 8B/10B

- Test FPGA : utilisation de ChipScope et FPGA editor pour l'implantation de sonde virtuelle

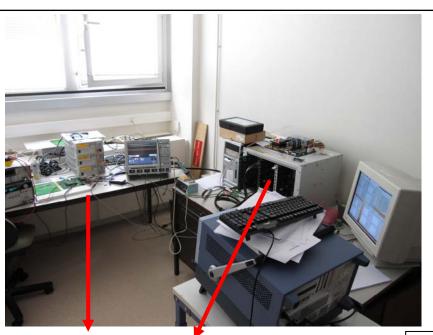

# DAQ sous tests

CCC

**LDA**

**DCC**

DIF **LAPP**

Test Bench: vue d'ensemble

DIF

Chassis DCC

Carte CCC

DCC<sub>1</sub>

DCC 2

générateur CLK

Chassis CCC & DCC

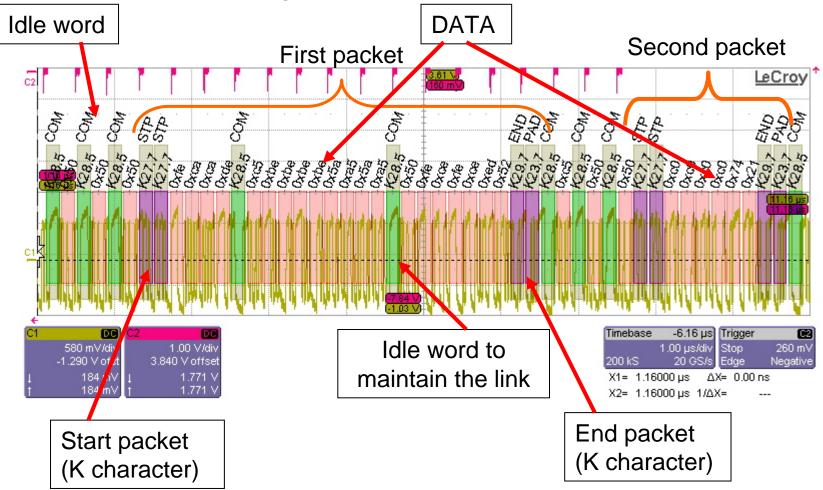

# Quelques résultats de tests

Décodage de paquets sur le lien série

# Quelques résultats de tests

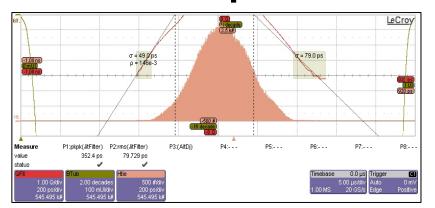

#### Mesures sur le lien DIF vers DCC

Mesures sur le lien DCC vers LDA

#### DCC Finale

- 1 connexion d'entrée : connexion LDA

- 9 connexions de sortie : connexion vers DIFs

- 1 entrée USB (lecture écriture pour debug)

- Option 1: espace mémoire (SRAM) de 18Mb

- Option 2 : connexion supplémentaire par connecteurs HE10 (26 pins)

- Débit max. actuel sur les liens : 50 Mb/s

- 5 paires LVDS sur chaque connexion (connecteur HDMI)

#### Conclusion

- Production des cartes lancée la semaine dernière

- Premiers tests en faisceau : fin 2010 → 2011

- Partage de code

- Avantage :

- Gain de temps sur l'étude

- Avoir des blocs adaptables ou réadaptables sans trop repartir de zéro

- Mais...

- Un manque de documentation => ré-étude