Orsay Micro Electronics Group Associated

21/06/2010

**DULUCQ Frederic**

#### **Table of contents**

- Part 1: PMM2 & PARISROC Overview

- Part 2: Why a second PARISROC

- Part 3: Presentation of PARISROC2

- Part 4: Measurements

- Part 5: Conclusion & future

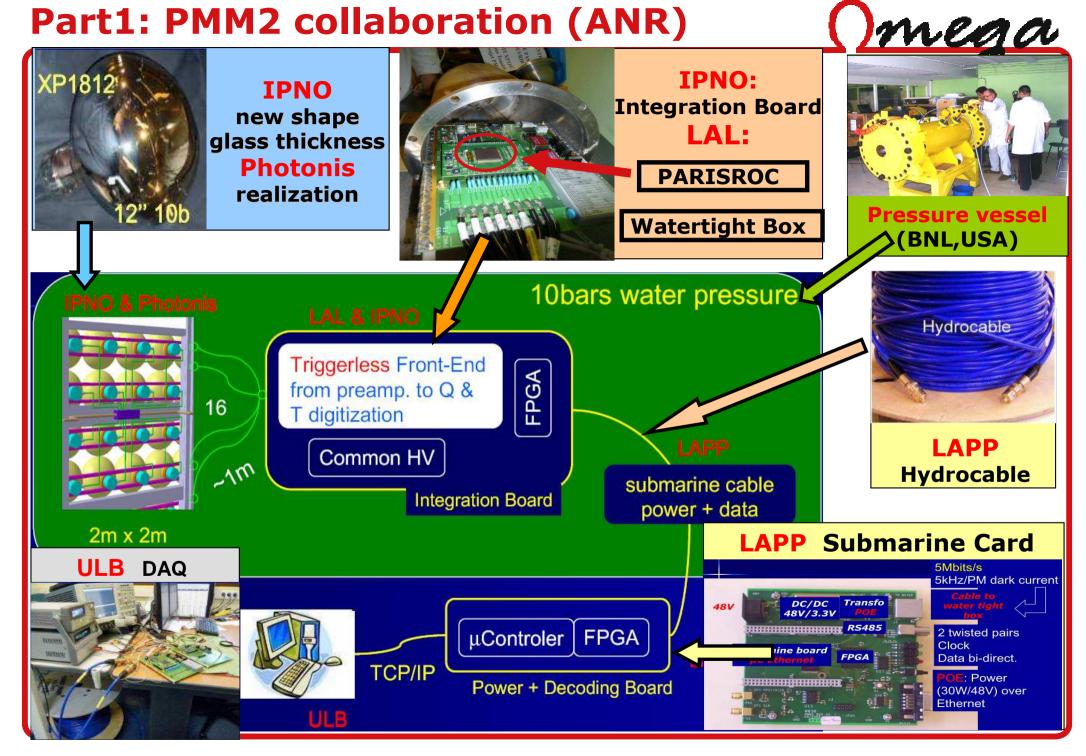

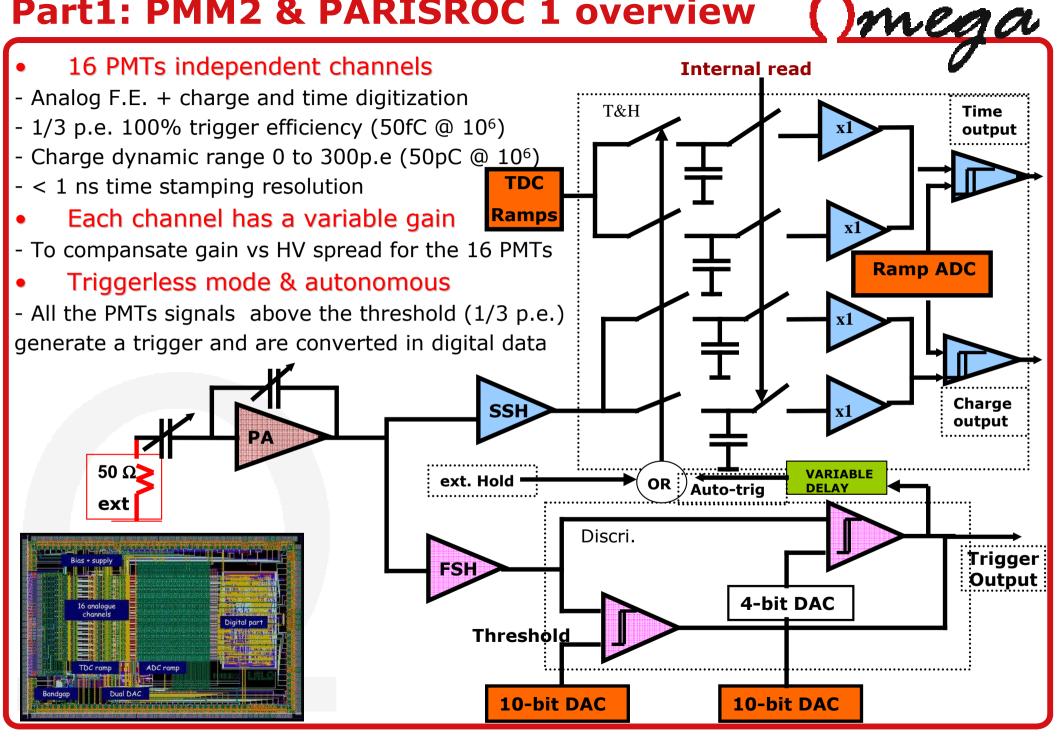

#### Part1: PMM2 & PARISROC 1 overview

# Part2: PARISROC 1 limitations (charge) () mega

#### Good overall performance of PARISROC1

- Good analog signals

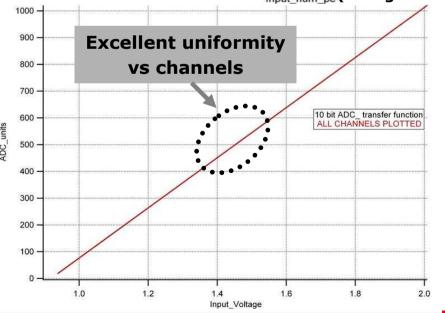

- Good chip uniformity vs channels

- Good complete chain results

#### BUT, some extra noise observed

- Low frequency noise

- Clock noise

- Coupling signal

#### Trigger limited to 10 $\sigma$ due to discriminator coupling (Noise 13 fC)

### Part2: PARISROC 1 limitations (time)

mega

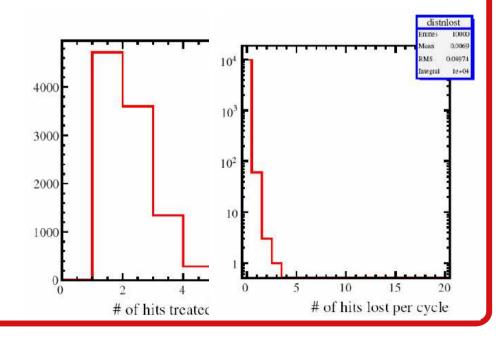

Hit rate → Parisroc1 has too high loss rate (up to 16%) for our physics (depends on PMT)

|           | $R_{ m bkg}$ | n <sub>SCA</sub> | $n_{ m bits}$ | $F_{RO}$ | Taux de pertes (%) |

|-----------|--------------|------------------|---------------|----------|--------------------|

| Parisroc1 | 5 kHz        | 2                | 12            | 10 MHz   | 16 ± 12            |

|           | 0.1 kHz      | 2                | 12            | 10 MHz   | $0.008 \pm 0.6$    |

|           | 5 kHz        | 2                | 10            | 10 MHz   | 6 ± 10             |

• Time measurement: Delay box jitter (max 300 ps) in time measurement

#### Part3: PARISROC 2 analog meaa ime output **Ramp TDC SCA fine time Added blocs** Depth 2 Ramp ADC Charge output **SCA low gain** SSH **MUX** Depth 2 **SCA** high gain 50 Ω SSH Depth 2 ext **↑**.Hold Thieshold gain **VARIABLE** ext. Hold Output OR :7 Auto-trig Discri. **FSH** Adjustable gain amplifier **Trigger** Adjust = 1-4Output **Threshold** Ramp TDC, Ramp ADC and 10-bit DAC 10-bit DAC 10-bit DAC 10-bit DAC common to all channels

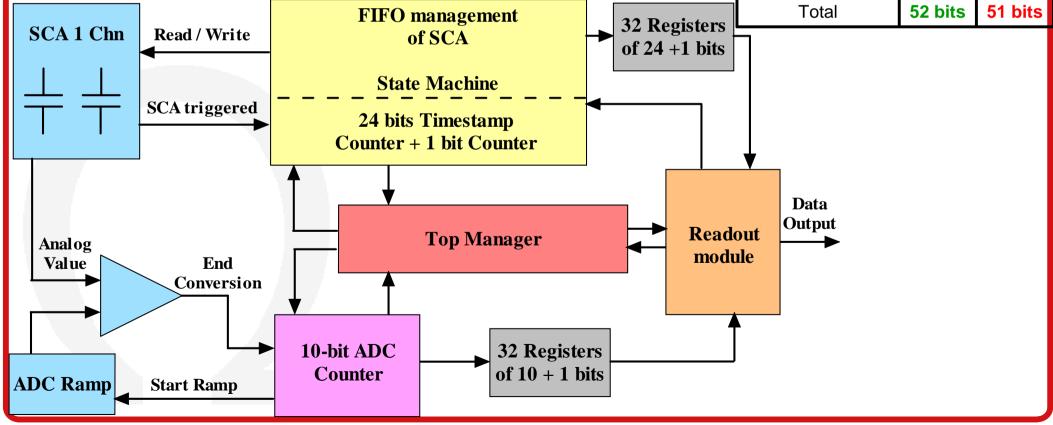

# Part3: PARISROC 2 digital (1)

- SCA management of 16 channels independents

- SCA management with depth of 2 for time and charge

- SCA management like FIFO (ping-pong)

- Timestamp 24b +1b counters @ 10 MHz (1.67s)

- 40 MHz clock for ADC + SCA management + readout

|                   | v1      | v2      |

|-------------------|---------|---------|

| Channel #         | 4       | 4       |

| Coarse time       | 24      | 24      |

| Extra Coarse time | NA      | 1       |

| Gain used         | NA      | 1       |

| Fine time (ADC)   | 12      | 10      |

| Ramp used         | NA      | 1       |

| Charge (ADC)      | 12      | 10      |

| Total             | 52 bits | 51 bits |

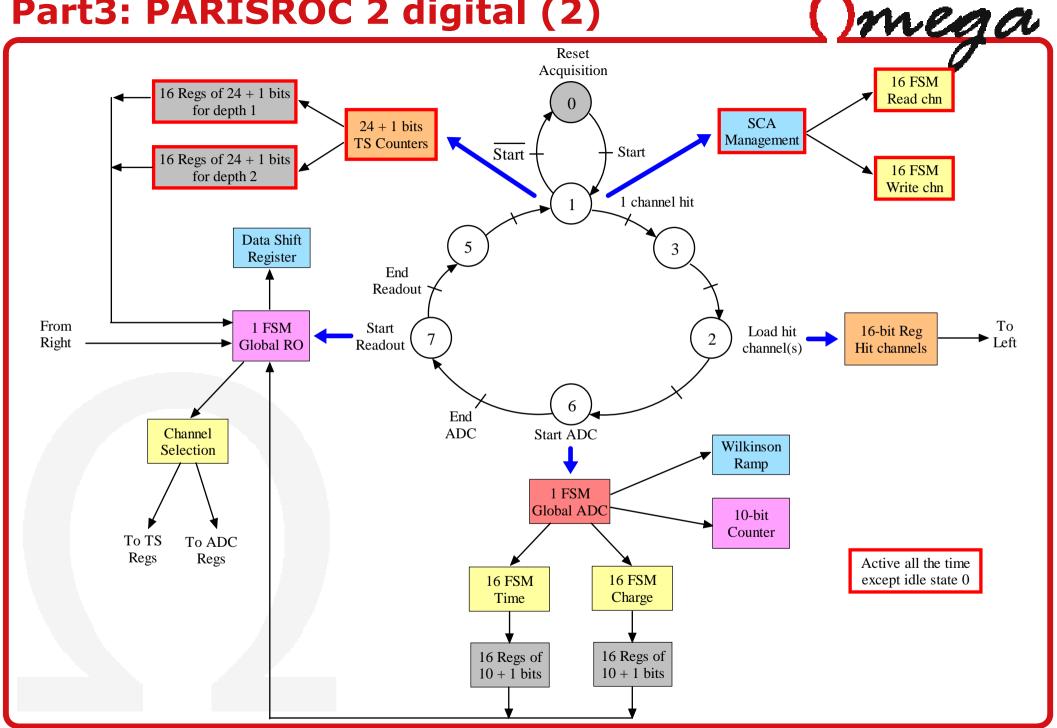

Part3: PARISROC 2 digital (2)

### **Part3: Hit rate improvement**

mega

Parisroc2 must be faster than Parisroc1 (gain of 4 minimum)

|              | $ m R_{bkg}$ | $n_{ m SCA}$ | $n_{ m bits}$ | $F_{RO}$ | Taux de pertes (%)           |

|--------------|--------------|--------------|---------------|----------|------------------------------|

| Parisroc1    | 5 kHz        | 2            | 12            | 10 MHz   | 16 ± 12                      |

|              | 0.1 kHz      | 2            | 12            | 10 MHz   | $0.008 \pm 0.6$              |

|              | 5 kHz        | 2            | 10            | 10 MHz   | $6\pm10$                     |

| Parisroc2 -> | 5 kHz        | 2            | 8*            | 40 MHz   | $0.24 \pm 3.1$               |

|              | 5 kHz        | 4            | 9*            | 40 MHz   | $\boldsymbol{0.007 \pm 0.7}$ |

- Conversion 8-9-10 bits by selecting ramp slope

- 8-9 bits is enough accuracy for time and for charge

- Internal counter now 10-bit

- Max conversion time: 25 us @ 10 bits

- Readout @ 40 MHz

- Max readout time 25 us

|            | PARISROC1 | PARISROC2 |

|------------|-----------|-----------|

| Conversion | 103 us    | 26 us     |

| Readout    | 101 us    | 25 us     |

| Total      | 204 us    | 51 us     |

Worst case: 16 chn hit + ADC Ovfl

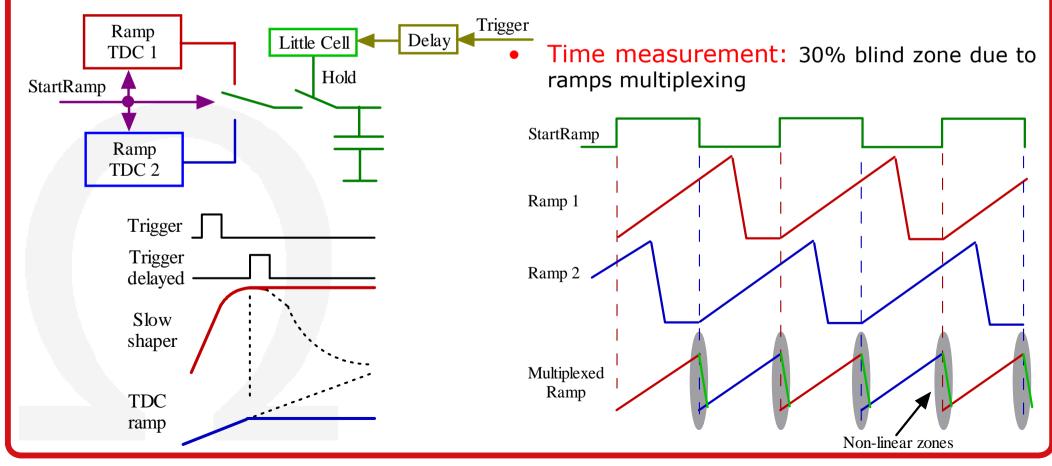

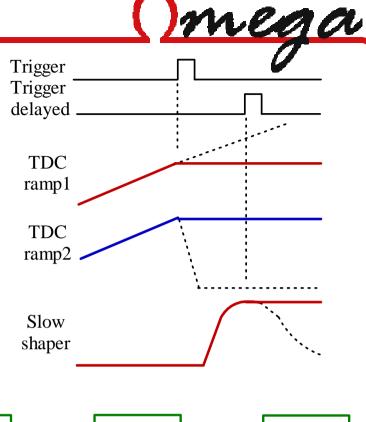

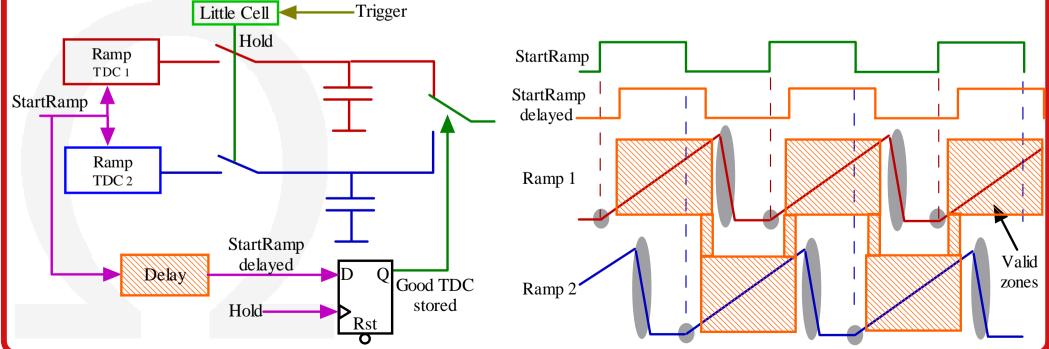

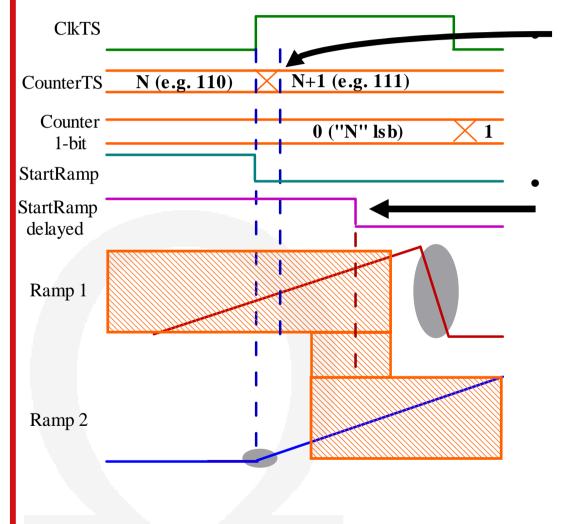

# **Part3: Fine time improvement**

- New fine time (Measurement → Talk S.DROUET)

- The 2 ramps are stored in a capacitors

- Overlap around 40ns between ramps

- Separate hold for charge and time (jitter issue)

- Need a signal to know which ramp is active and linear

→ StartRamp delayed by 20ns

- In overlap zones, coarse time counter has already counted "+1" as delay > clock tree latency + clock skew

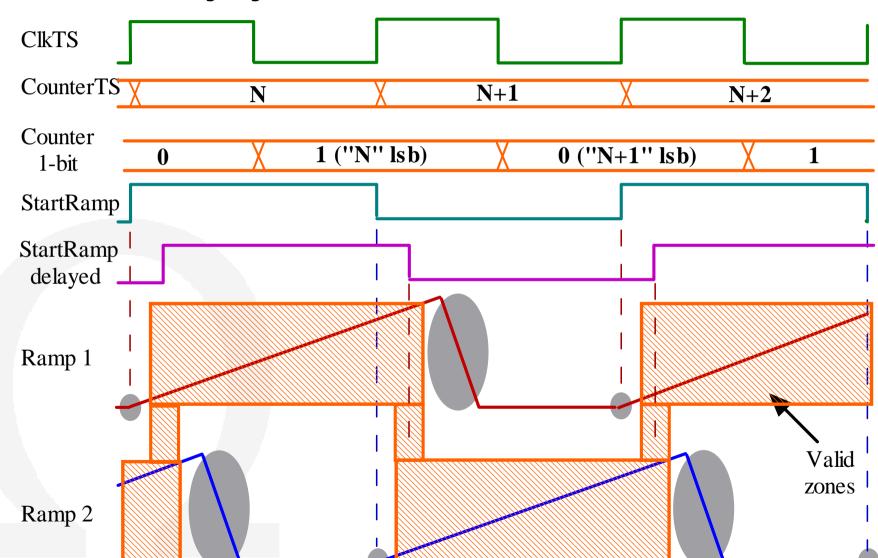

### Part3: Coarse time (1)

- mega

- In PARISROC1, possible error in TS for triggers synchronous with clock

- In v2, 2 counters are implemented:

- A 24-bit gray @ rising edge of 10MHz (same as v1)

- A 1-bit @ falling edge of 10MHz

### Part3: Coarse time (2)

• Thanks to overlap, we assume that converted fine time is always good (selection made with 1-bit reg in analog part).

For trigger synchronous with counter →

Data stored = (N or N+1), Cpt1Bit and Ttdc

meaa

For trigger synchronous with StartDelayed → Data stored = N+1, Cpt1Bit and (TtdcRamp1 or TtdcRamp2)

Recover real time →

If (Ttdc > 90 ns) then

If LSB(BIN(CptTS)) = (Cpt1Bit) then

Time = CptTS + Ttdc

else

Time = (CptTS-1) +Ttdc

else

Time = CptTS + Ttdc

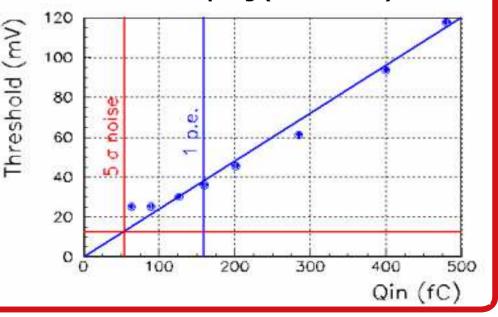

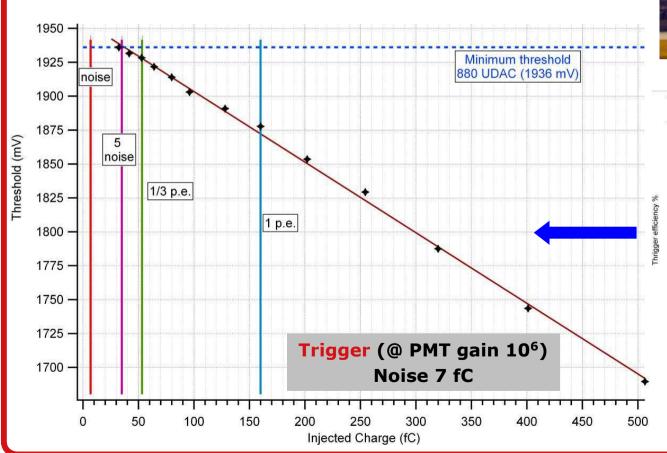

# Part4: First results (charge)

- Improvement in noise low noise; no clock noise

- No coupling signal

- Trigger improvement@ 1/3 of p.e. (50fC @ PMT gain 10<sup>6</sup>)

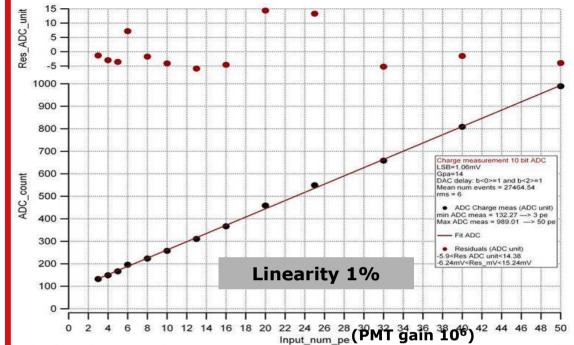

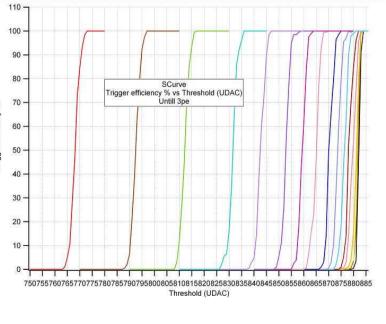

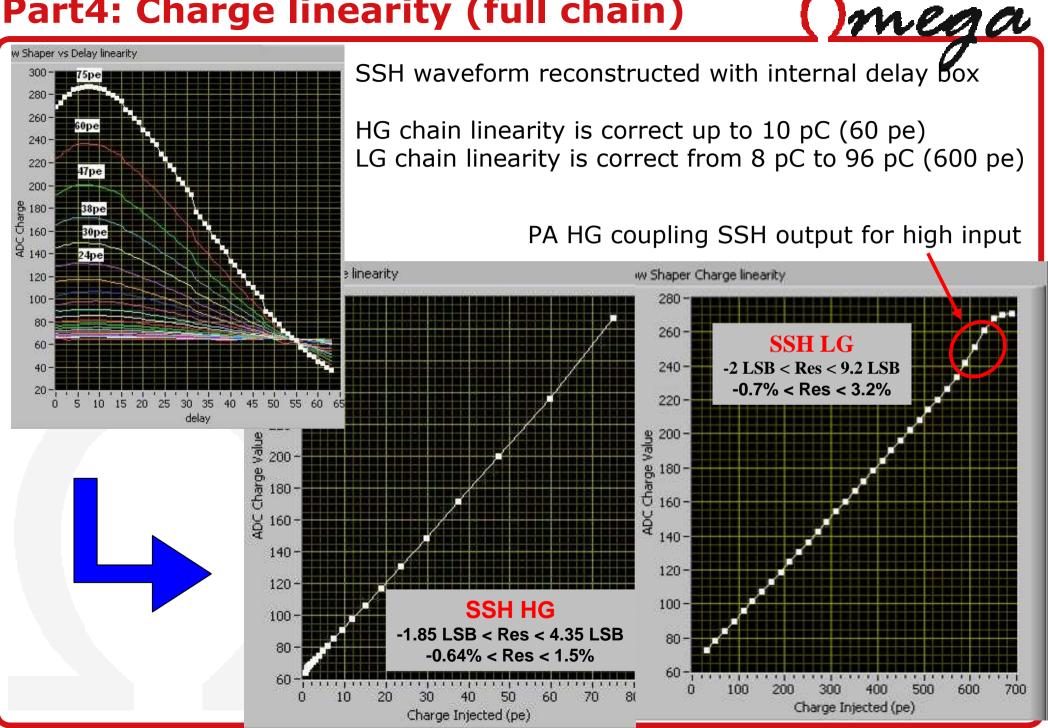

### Part4: Charge linearity (full chain)

#### **Part5: Conclusion & future**

- PARISROC2 up to now:

- Auto-trigger + chn independent OK

- No clock noise

- No Trigger coupling

- Noise OK to see signal 1/3pe (50fC)

- Digital part speed up OK

- New TDC integrated (see S. DROUET Talk)

meaa

- PARISROC is evaluated by other experiments:

- DUSEL (large water cerenkov)

- LENA (liquid scintillator)

- IHEP Beijing

- PARISROC for the future:

- Improve rate capability

- Need move to pipeline ADC and multiple data lines

| Wilki <b>≺</b> | Present<br>chips |

|----------------|------------------|

|                | Pipeline<br>MSPS |

|   | PARISROC            | Hit Rate<br>(KHz) |

|---|---------------------|-------------------|

| 7 | V1                  | 5.4               |

| ſ | V2                  | 21.4              |

|   | 2V1 (80 MHz)        | 42.7              |

|   | 2V2 (80 MHz + 8 SL) | 83.1              |

|   | 3V1 (40MHz + 8 SL)  | 216.2             |

|   | 3V2 (80MHz + 8 SL)  | 432.4             |