**Journées vlsi 2010 LAL Orsay** 24 juin | 11:00 | 11:20

jehanno@lal.in2p3.fr

# **PLAN**

- Introduction (3)

- Characteristic (4) Le système DAQ (4)

- Exemples d'implémentation dans le FPGA (10)

- Identification

- Filtres numériques

- La fonction Pound-Drever-Hall numérique

ANR-08-BLAN-0280-01

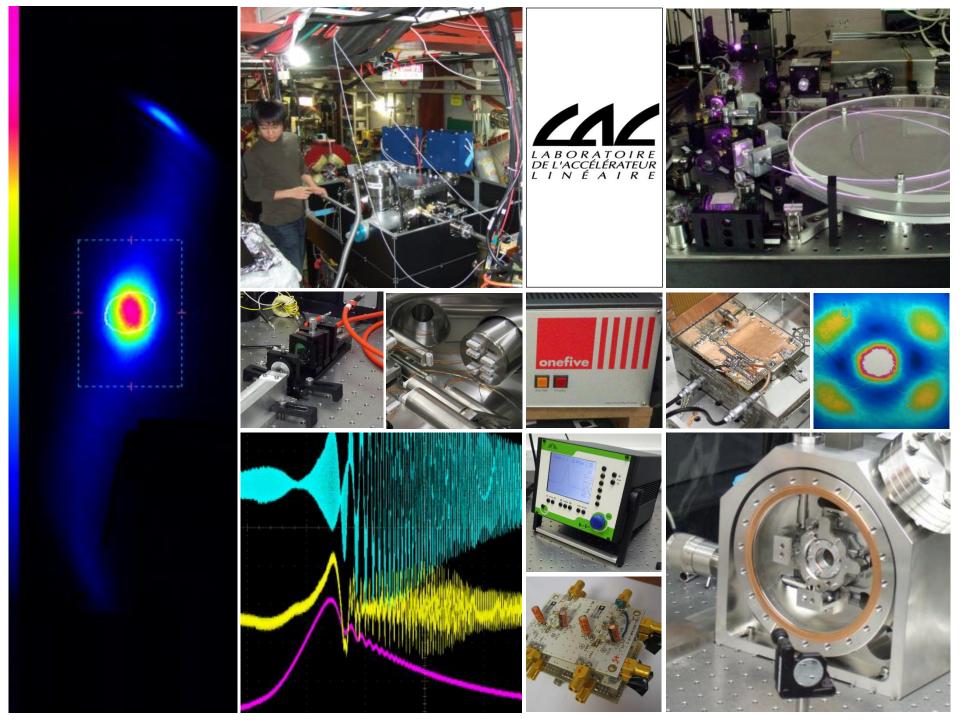

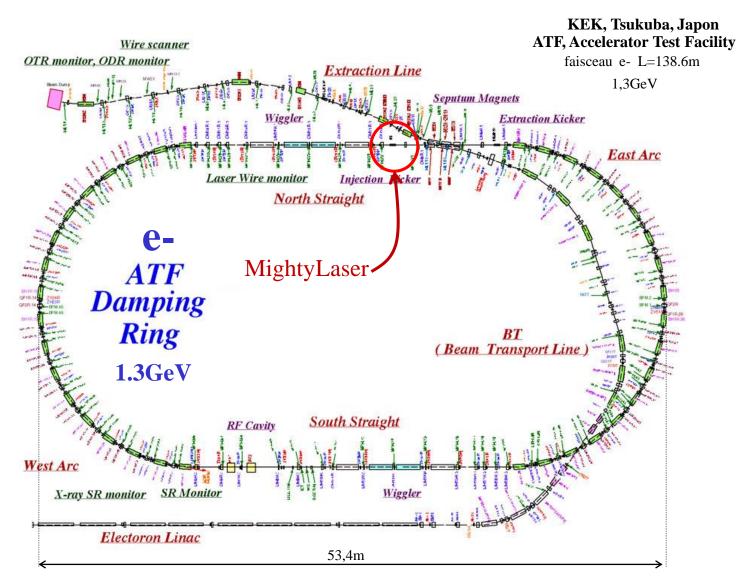

Amplification dans une cavité Fabry-Perot d'un laser à fibre picoseconde de très forte puissance moyenne • Application à la production de rayons gamma par interaction compton

### Introduction

2

17

$$\lambda = \frac{C}{V}$$

E = h.v

$$E = h \frac{C}{\lambda}$$

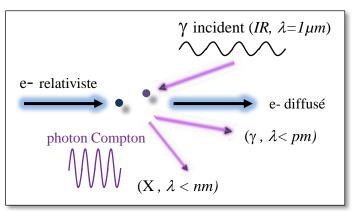

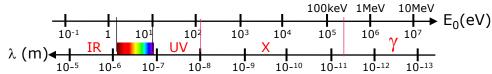

### diffusion Compton inverse

interaction matière - lumière diffusion d'un électron (e-) sur un photon γ les γ **absorbent** une partie de l'énergie des e-

**production de γ,X monochromatiques** *sélection angulaire*

applications

- médecine (imagerie, radiothérapie)

- analyses (cristallographie)

- analyse non-destructive (oeuvres d'art)

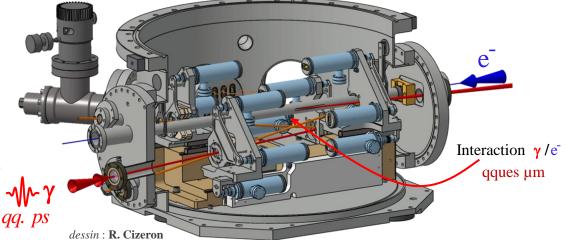

cavité 4 miroirs Fabry-Perot Ø=1m V= 1/3m<sup>3</sup> P~10<sup>-9</sup>mbar

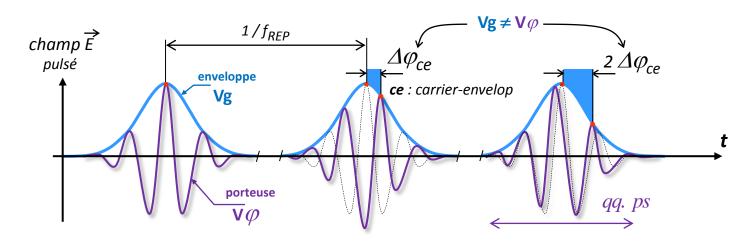

> les photons sont issus d'un **laser pulsé** (f<sub>REP</sub>=178.5MHz)

Amplification par **sommation** du champ laser incident avec le champ intra-cavité : **résonance** de la cavité Phénomène **instable** (*bruits*) : la DAQ doit réaliser des **asservissements** de **longueurs**

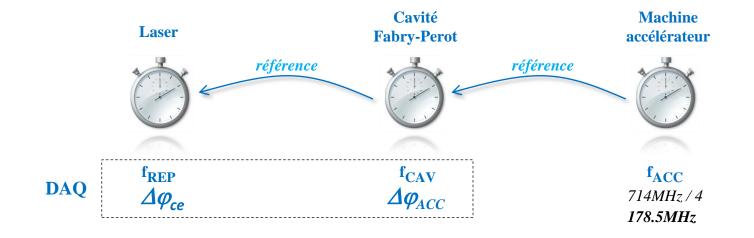

Système: Laser / Cavité Fabry-Perot

| Amplification optique |                           |  |  |

|-----------------------|---------------------------|--|--|

| $f_{REP} = f_{CAV}$   | $\Delta \varphi_{ce} = 0$ |  |  |

Système: Cavité Fabry-Perot / Accélérateur

| Interaction Compton |                            |  |  |

|---------------------|----------------------------|--|--|

| $f_{CAV} = f_{ACC}$ | $\Delta \varphi_{ACC} = 0$ |  |  |

# **PLAN**

- O Introduction (3)

- Le système DAQ (4)

- Exemples d'implémentation dans le FPGA (10)

- Identification

- Filtres numériques

- La fonction Pound-Drever-Hall numérique

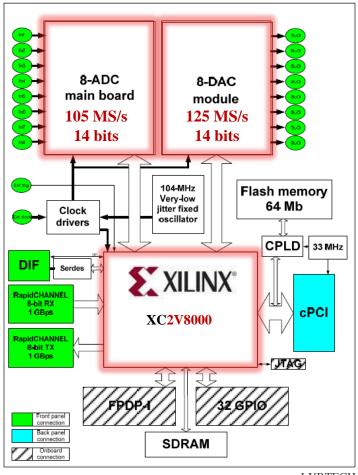

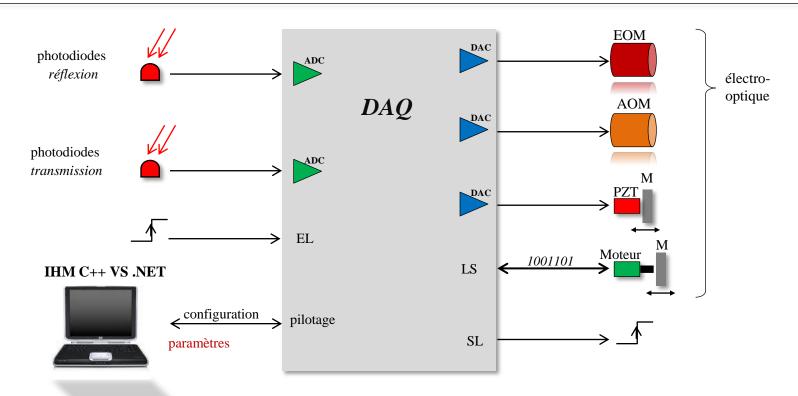

#### • Carte VHS ADAC V2 (LYRTECH)

dans un châssis cPCI

photo: LAL

- -- Pas de processeur calcul en virgule fixe

- -- bruit de sortie BF non prévu (conception) impose sorties différentielles

#### • Synoptique fonctionnel

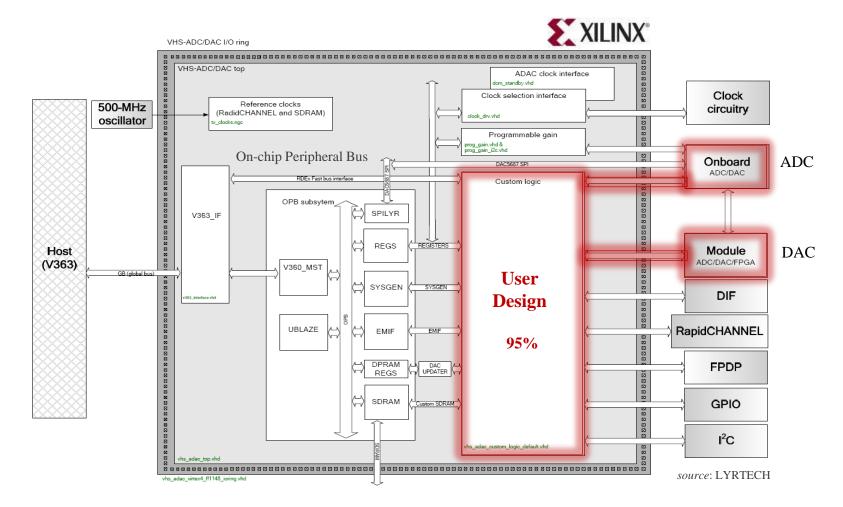

source: LYRTECH

- ++ 8 voies IN / 8 voies OUT

- ++ Temps in/out 100ns

important pour les marges de phase

- ORA ACCÉI NÉ

- Le code du FPGA contient la **gestion des I/O** (cPCI gateway, GPIO, SDRAM...) et une partie **User Design**.

- L'ADC et le DAC sont connectés directement au FPGA (fil à fil)

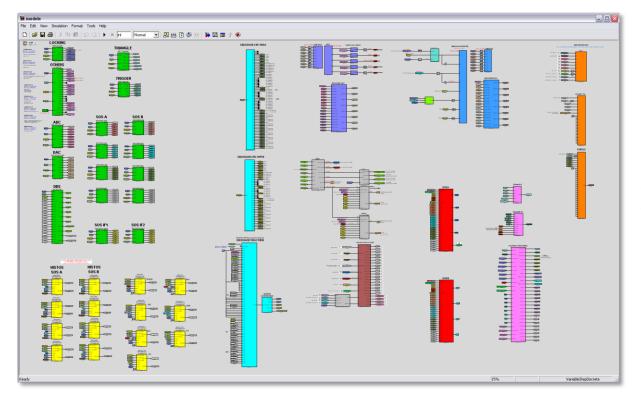

### **Environnement MATLAB/SIMULINK**

6

17

- Ecriture d'un modèle (.mdl) sous Simulink : ensemble de blocs fonctionnels connectés entre eux

- Blocs: SIMULINK (discarded), XILINX (100, compiled), LYRTECH propriétaires (ADC, DAC), VHDL user (black box)

Interface **Simulink** *modele*, *mdl*

- Outil System Generator : concaténation / création d'un modele\_files.vhd (port map automatique du top)

- Appel de xflow.exe : Synthèse / Placement / Routage / Generation bitstream / Chargement / Run

modele\_files.vhd: 87000 lignes T synthèse: 40 minutes Slices utilisées @XC2V8000: 33747 / 46592 (72%)

| ENTREES                            | TRAITEMENTS réalisés par le FPGA   |                                                          | SORTIES                             |

|------------------------------------|------------------------------------|----------------------------------------------------------|-------------------------------------|

| acquisition signaux<br>analogiques | algorithmes (FSM)                  | calculs                                                  | produire des signaux<br>analogiques |

|                                    | synthèse de filtres                | identification                                           |                                     |

| acquisition signaux<br>logiques    | démultiplexage en<br>bande de base | synthèse de fréquences<br>DDS (Direct Digital Synthesis) | produire des signaux<br>logiques    |

|                                    | synthèse de                        | debug                                                    |                                     |

| acquisition liaison<br>série RX    | signaux (triangle)                 | (traces, histos,)                                        | piloter <mark>liaison</mark>        |

|                                    | record                             | playback                                                 | série TX                            |

# **PLAN**

- O Introduction (3)

- C Le système DAQ (4)

- Exemples d'implémentation dans le FPGA (10)

- Identification

- Filtres numériques

- O La fonction Pound-Drever-Hall numérique

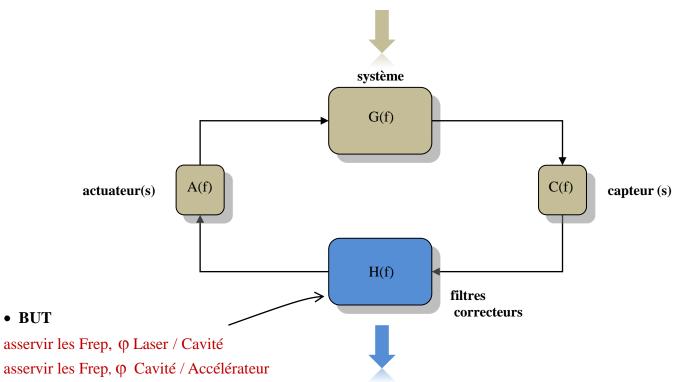

• BUT

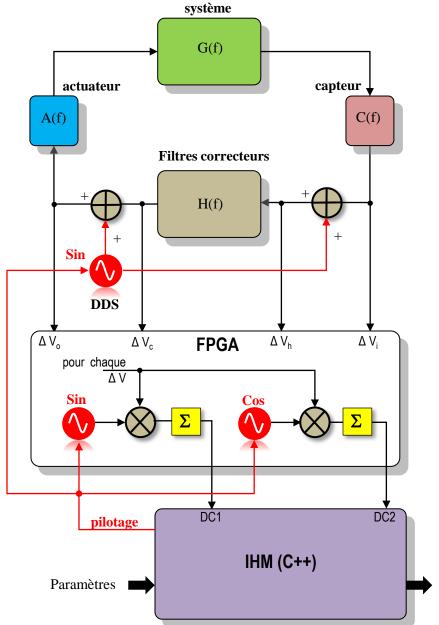

#### • Eléments du système

Système, Capteur, Actuateur

#### • Choix des filtres

la structure et les coefficients des filtres correcteurs dépendent des réponses en fréquence des éléments A, G et C

#### • Identification

vise à déterminer ces fonctions de transfert (ie : 1Hz à 10MHz)

## **Exemple 1 : Identification** (*Fonction de transfert, Gain/Phase*)

• Principe

Balayage de fréquence (DDS) piloté par l'IHM

- Intervalle Fstart / Fstop

- Temps d'intégration

- Nb de points

- Equi-répartition (Lin, Log)

- Gabarit Sinus

Le FPGA est chargé de calculer les  $\Sigma$  sur des **nombres entiers** de périodes

- intégration pour obtenir le DC

Extraction Gain/Phase par l'IHM à partir du DC

Production en sortie de fichiers .dat

- compatibles **Matlab**

- plusieurs scans traçables sur la même courbe avec des résolutions différentes

- Utilisation

- Auto-identification H(f) *validation du principe*

- A(f), C(f), G(f)

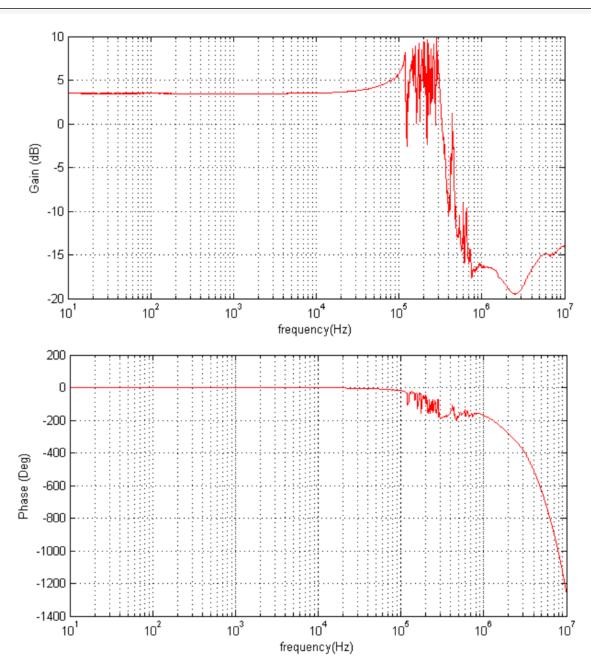

Identification d'un actuateur PZT

Gain

**Phase**

Filtre FIR Finite Impulse Response

Certains filtres non réalisables (intégrateurs) Consomme beaucoup de ressources FPGA calcul virgule fixe

$$Y(n) = \boldsymbol{B_1}.X(n\text{-}1) + \boldsymbol{B_2}.X(n\text{-}2) + \boldsymbol{B_3}.X(n\text{-}3)$$

$$y(n) = \sum_{k=1}^{N} B(k) x(n-k)$$

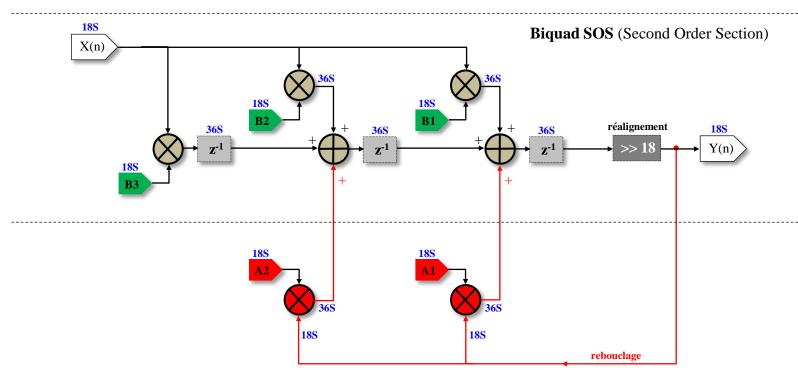

Filtre IIR Infinite Impulse Response

Simplicité de synthèse Moins de coefficients pour un FIR équivalent calcul virgule fixe

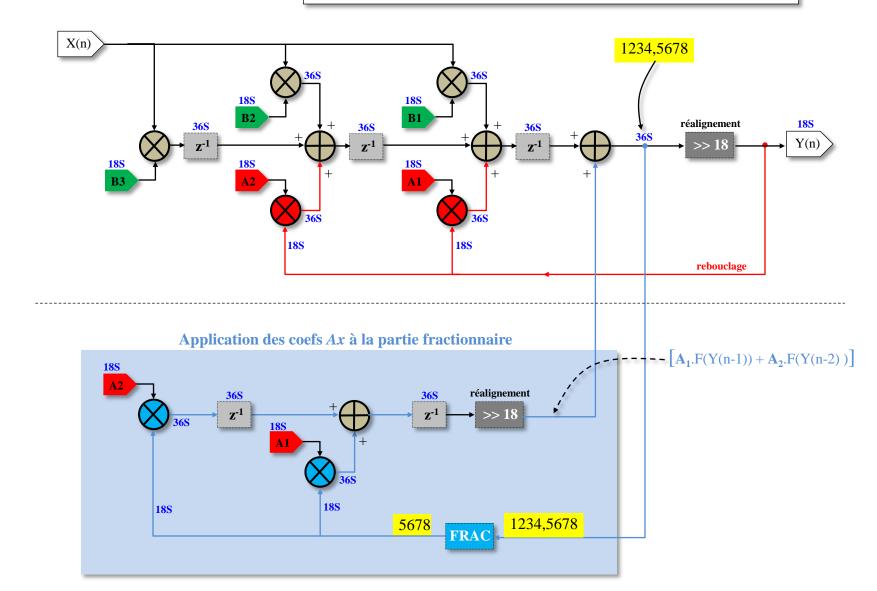

$$Y(n) = [B_1.X(n-1) + B_2.X(n-2) + B_3.X(n-3)] - [A_1.Y(n-1) + A_2.Y(n-2)]$$

$$y(n) = \sum_{k=1}^{K} B(k) x(n-k) - \sum_{m=1}^{M} A(m) y(n-m)$$

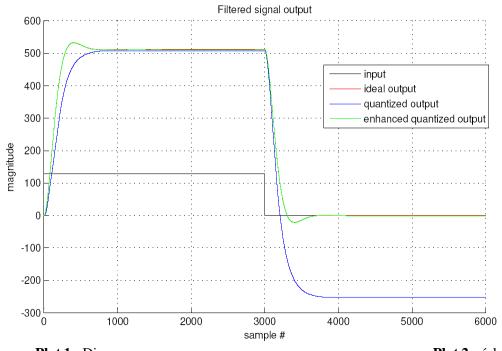

perte de précision due au réalignement

#### Troncature des résultats

Récursivité introduit une propagation des erreurs Instabilité

Structure SOS (Second Order Section) : limitation de ces effets Mais ne suffit pas !

**Enhanced IIR** (Infinite Impulse Response)

$$Y(n) = [B_1.X(n-1) + B_2.X(n-2) + B_3.X(n-3)] - [A_1.Y(n-1) + A_2.Y(n-2)]$$

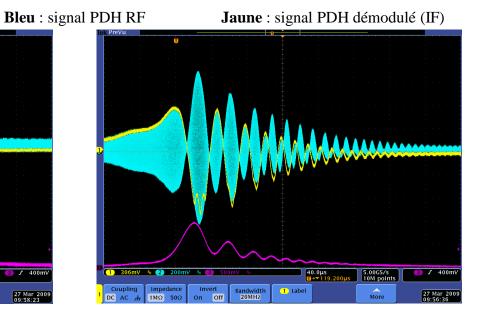

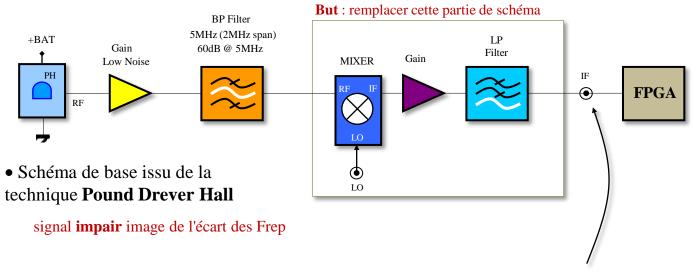

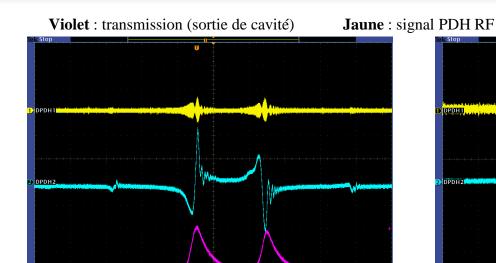

## Exemple 3: la fonction DPDH (démodulation @5MHz)

15 17

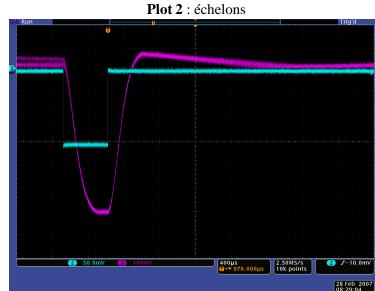

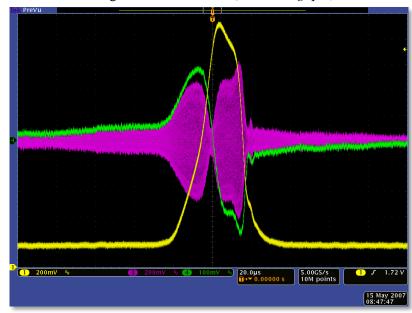

### **Version 1:** tout analogique

Version 2: mixer et filtre dans le FPGA

- Simplification du front-end analogique encombrement réduit sur la table optique

- Plus de fluctuations du DC de la démodulation le mixer analogique laisse passer le DC gênant pour l'asservissement

- Plus de non linéarité du mixer le mixer analogique est NL

Signal PDH démodulé (tout analogique)

RR Equiripple

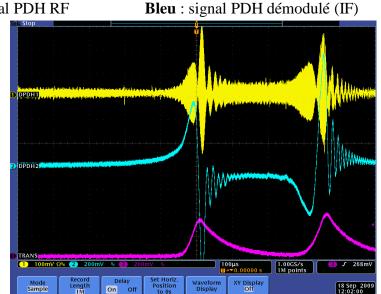

## Exemple 4: la fonction DPDH (démodulation @5MHz)

FIR *filtre* CORRECTION d'OFFSET IF\_OUT = IF - OFFSET IF 20MHZ 32**S** 32S mis avant décalage 32**S** 51.17S IF OUT ECRETEUR FIR [1S, 31 Entier] [1S, 32 Entier, 17 frac] Down Sample5 mixer\_config produit 32**S** Reinterpret5 32**S** CORRECTION\_OFFSET\_IF Reinterpretfi somme Generated by MATLAB(R) 7.4 and the Signal Processing Toolbox 6.7. Generated on: 12-May-2009 10:31:r22 [0.00109100341796875 0.0065765380859375 0.02259063720703125 0.05594635009765625 0.108917236328125 017314910888671875 0.22786712646484375 0.2464752197265625 0.2105560302734375 0.12364959716796875 0.014617919921875 -0.0742645263671875 -0.109405517578125 -0.00454132080078125 -0.02356719970703125 0.03479766845703125 0.0602264404296875 0.0466156005859375 0.01117706298828125 -0.02048492431640625 -0.03151702880859375 -0.217132568359375 -0.00315093994140625 0.0107574462890625 0.0137939453125 0.0083160400390625 0.000701904296875 -0.00405120849609375 -0.00479888916015625 -0.0031890869140625 -0.0013275146484375 -0.00028228759765625 0.0000228881835937] configuration Coefficient Format: Decimal Function Block Parameters: FIR Xilinx Finite Impulse Response Filter (mask) (link) % Discrete-Time FIR Filter (real) Finite impulse response (FIR) filter. % Filter Structure : Direct-Form FIR Hardware notes: Implemented using distributed arithmetic (DA). The hardware over sampling rate % Filter Length : 33 determines the degree of parallelism. A rate of one produces a fully parallel DA filter. A rate of n (resp. % Stable : Yes n+1) for an n-bit input signal produces a fully serial implementation for a non-symmetric (resp., symmetric) % Linear Phase impulse response. Intermediate values produce implementations with intermediate levels of parallelism. % Arithmetic : fixed % Numerator : s16,17 -> [-2.500000e-001 2.500000e-001) % Input : s32,0 -> [-2.147484e+009 2.147484e+009) % Filter Internals : Full Precision [0.00109100341796875 0.0065765380859375 0.02259063720703125 0.05594635009765625 0.10891 Output : s50,17 -> [-4.294967e+009 4.294967e+009) (auto determined) Coefficient Structure Inferred from Coefficients Product : s47,17 -> [-536870912 536870912) (auto determined) : s50,17 -> [-4.294967e+009 4.294967e+009) (auto determined) Number of Bits per Coefficient (always treated as signed) Round Mode : No rounding Binary Point for Coefficients Paramétrage du bloc FIR Number of Channels 1 Polyphase Behavior | Single Rate: sample in - sample out Outil Matlab: FDA Tools Hardware Over-Sampling Rate Use Explicit Sample Period Provide Coefficient Reload Ports Provide Valid Ports Override with Doubles Filter Tupe ----- Show Implementation Parameters Bandpass Bandstop Fpass: 9600 Recopie des coefficients Fstop: 180000

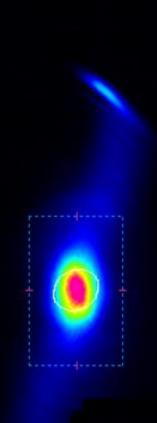

## Exemple 4: la fonction DPDH (démodulation @5MHz)

18 Sep 2009

17 17

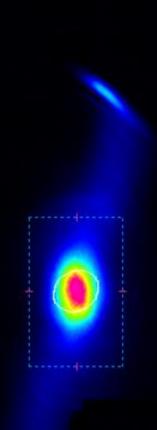

Violet: transmission (sortie de cavité)

Bleu: si

10.0us

11-7-2.40000µs

10M points

Coupling Impedance Invert Bandwidth

DC AC # 11M2 500 On Off Bandwidth

27 Mar 2009

10 1 1 Label More 675.5823