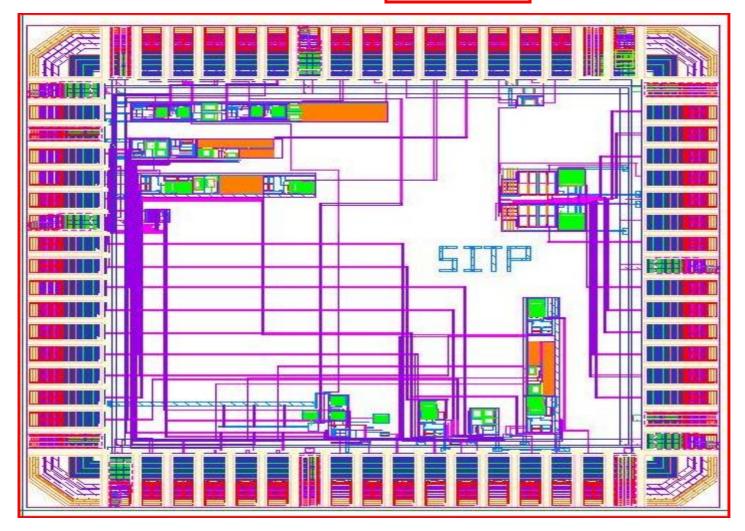

# SITR BLOCS

- ☐ Design intermédiaire avant celui d'un circuit multivoies

- ☐ Circuit dédié à la lecture des micro-pistes en silicium ( ILC )

- ☐ CMOS IBM 130 nm ( 1.5 V)

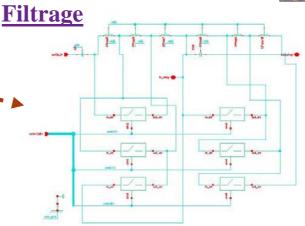

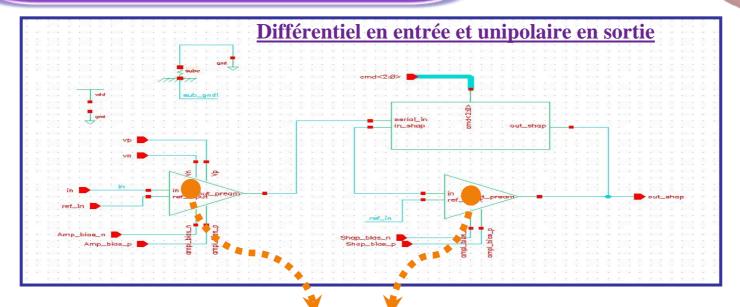

- □ 3 amplifier-shaper différents (CR-RC programmable; 3 bit)

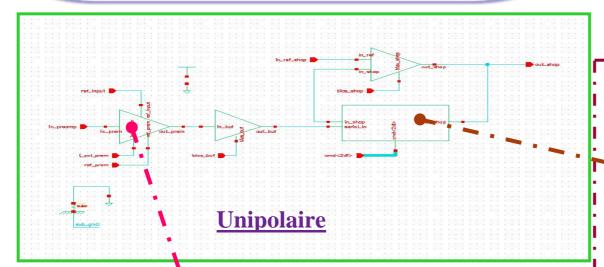

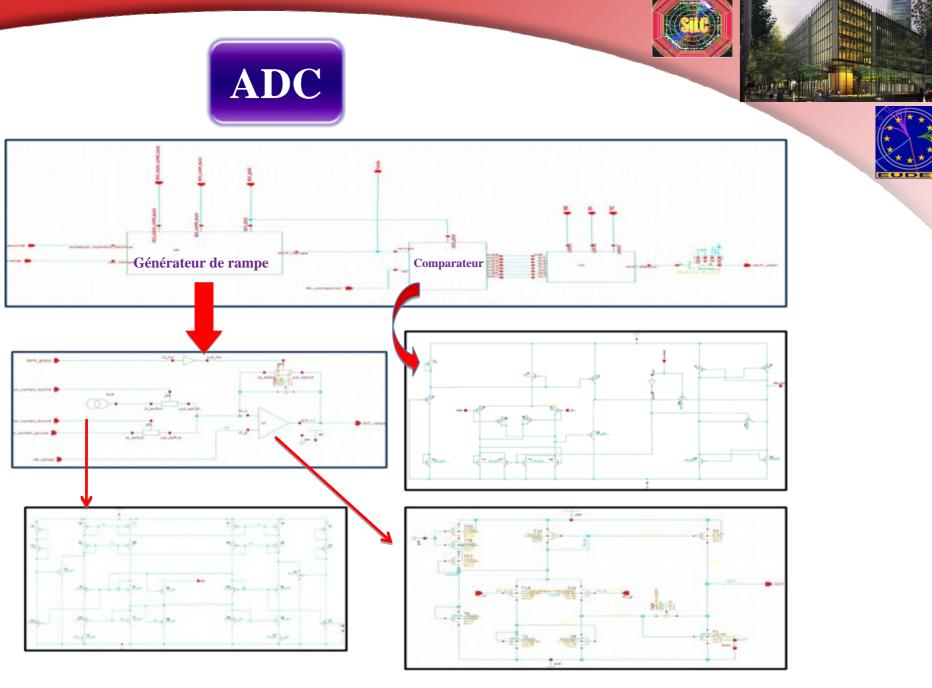

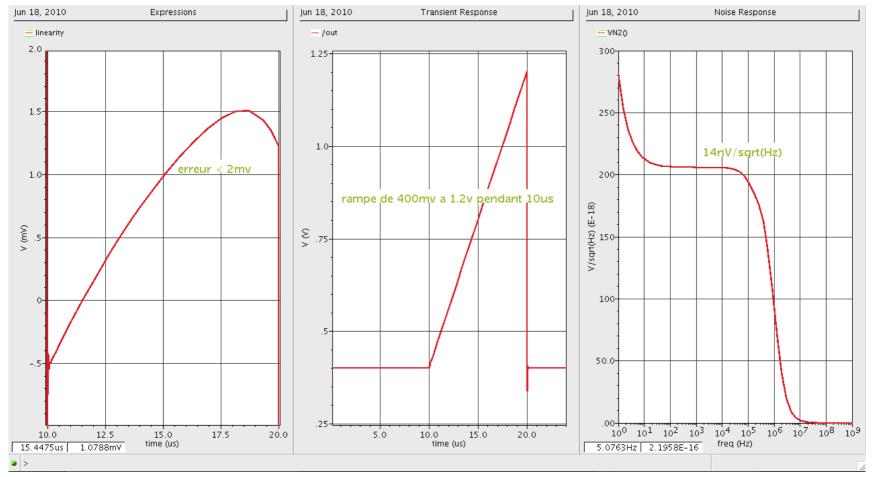

- **□ ADC** Wilkinson simple rampe (8 bits)

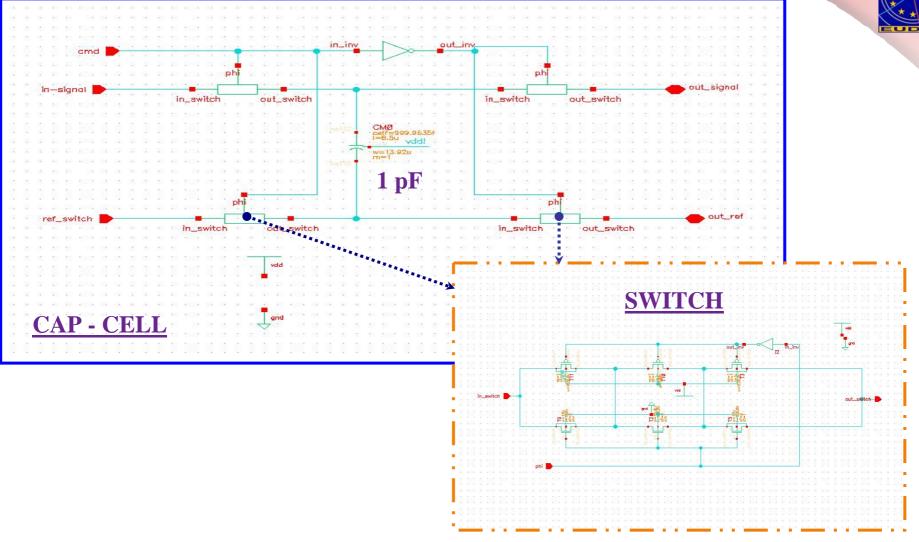

- ☐ Une cellule mémoire avec ses switchs d'écriture et de lecture.

- **☐** Run en cours via le CERN

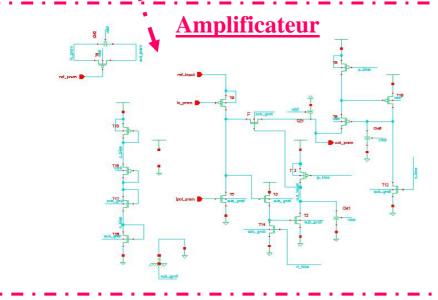

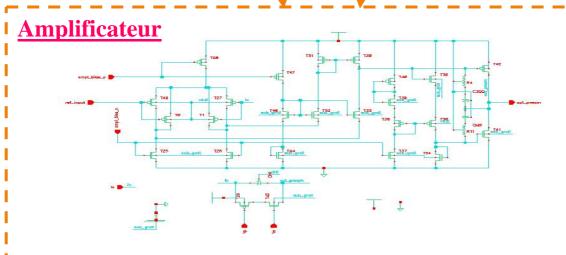

## **Amplifier - Shaper V1**

Gain: 19.4 mV/MIP

**Sh** \_**Time:** 600ns – 1us

**Bruit** @ 1 us : ~ 346 + 19,5 e/pF

**Linéarité** < 1% ( 15 MIP )

Consommation: 450 uW

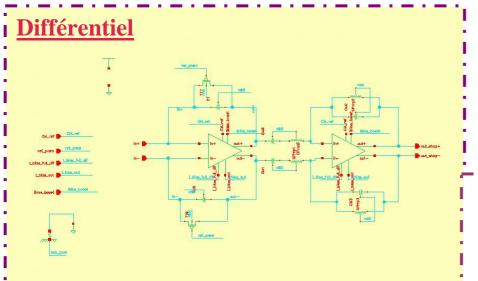

### **Amplifier - Shaper V2**

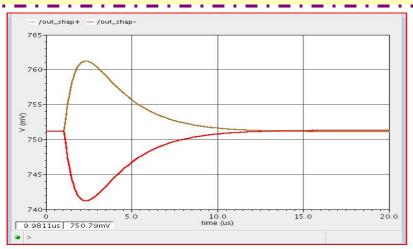

Gain: 20 mV/MIP

**Sh** \_**Time: 550ns** – **1us**

**Bruit** @ 1 us : ~ 189 + 18,9 e/pF

**Linéarité** < 1% ( 15 MIP )

Consommation: 334 uW

Sh  $\_$ Time: 700 ns -1 us

**Bruit** @ 1 us : ~ 698 + 17.7 e/pF

Linéarité < 1% (15 MIP)

Consommation: 540 uW

### La cellule mémoire