# Microélectronique au LAPP

Journées VLSI Orsay 24-27 juin 2010

R. Gaglione pour l'équipe électronique

Laboratoire d'Annecy-le-Vieux de Physique des Particules, Université de Savoie, CNRS/IN2P3 FRANCF

23 juin 2010

Introduction

**MAPRA**

FE-I4

**MICROROC**

Introduction

MAPRA

FF-14

MICROROO C

#### Introduction

#### Situation actuelle de l'équipe électronique :

- 19 personnes + 3 stagiaires en 2010

- 3 personnes spécialisées en microélectronique s'appuient sur les ressources du service (DAQ, CAO PCB, support CAO, tests...)

Équipe importante et expérimentée, grande perméabilité entre les multiples compétences.

Introduction

**MAPRA**

FF-14

MICROROO C

## Expérience POLAR

### L'expérience

- Détecteur satellisé

- Polarimètre Compton pour les rayons X issus des sursauts gamma

#### l e détecteur

25 cellules de détections  $(5 \times 5)$  composée chacune de :

- 64 scintillateurs BC400 (6 mm×6 mm/8 mm×8 mm×20 cm)

- MAPMT H8500, 64 voies

### L'ASIC MAPRA

Multi-anodes Photomultiplier Read-Out Asic: basé sur PARISROC (collaboration avec le LAL/OMEGA, *cf* presentation de Frédéric).

### Signaux

- 1 keV déposés dans le scintillateur ightarrow 1 pe sur la photocathode

- Gain du PM  $10^6 o 1$  pe = 160 fC

#### Déclenchement.

- Trouver une coïncidence entre 2 pixels dans une fenêtre de 100 ns

- Seuil bas 5 keV

- Seuil haut 500 keV (réjection des cosmiques)

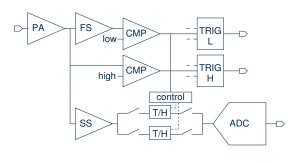

# Synoptique

- PA en tension avec gain ajustable et clamping

- Shaper rapide (15 ns)

- Discriminateur faible offset

- Double suiveur/bloqueur

- ADC Wilkinson 12 bits (100 μs)

- Logique de déclenchement rapide (<3 ns)</li>

# État

- MAPRA 16 voies en 0.35 µm SiGe AMS testé avec succès

- Passage à 64 voies en cours (collaboration avec OMEGA/LAL)

- Fonderie prévue pour fin 2010

Introduction

MAPRA

FE-I4

MICRORO (

# Expérience ATLAS

### L'expérience

- Mise à niveau du détecteur de trace d'ATLAS

- Forte implication du LAPP dans l'IBL, volonté de participer aussi à l'effort de microélectronique pour les différentes phases d'upgrade

#### Le contexte

- Acitivité de physique liée au tracking qui démarre au LAPP

- Priorité affichée par la direction

- Collaboration avec le CPPM

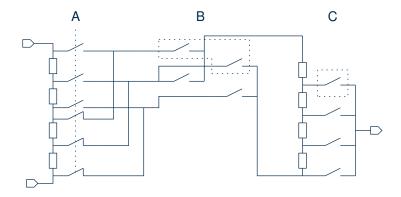

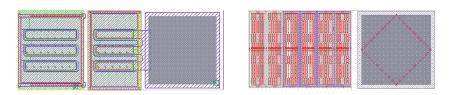

## DAC 10 bits

DAC d'un ADC à approximation successive (slow-control: température, courant de fuite des pixels) réalisé par le CPPM pour le chip FE-I4 (IBM 130 nm, cf présentation de Denis) Dynamique:  $1.5 \text{ V} \rightarrow \text{LSB}$ : 1.5 mV

### **Fonctionnement**

- A: choix de la gamme (MSB)

- B: matrice de connexion de la résistance choisie

- C: pont diviseur de sortie (LSB)

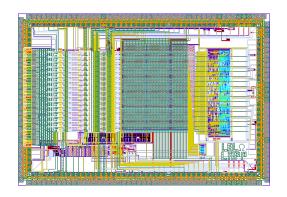

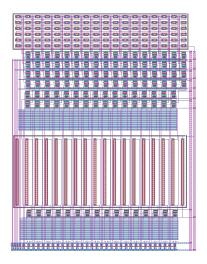

# Layout

Introduction

MAPRA

FF-14

**MICROROC**

# Expérience ILC/CLIC

### L'expérience

- Futurs colisionneurs linéaires e<sup>+</sup>e<sup>-</sup> (ILC et CLIC)

- Calorimètre hadronique digital (2 bits seulement)

- Prototype de 40 plans (1 m<sup>3</sup> : 400 000 voies)

#### Le détecteur

- Détecteurs gazeux de type bulk MICROMEGAS à réponse proportionelle (MIP MPV=20 fF)

- Grande segmentation : anode de 1 cm<sup>2</sup> (Cdet=80 pF)

## Tests des chips

Plusieurs prototypes de détecteurs construits avec des chips disponibles :

- Gassiplex (CERN) : lecture analogique, forte consommation

- Dirac (IPNL) : lecture digitale, fonctionnement synchrone

- Hardroc (LAL/OMEGA) : lecture digitale, conçu pour les RPC

Conception d'un nouvel ASIC (MICROROC) en collaboration avec le LAL/OMEGA basé sur le Hardroc avec un nouvel étage d'entrée optimisé pour les détecteurs MICROMEGAS.

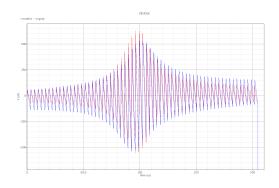

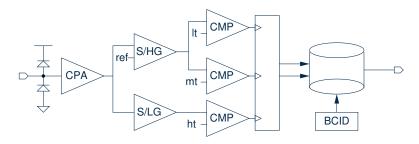

# Synoptique simplifié

Chaque seuil programmable par DAC, référence du shaper ajustable par DAC. *Power pulsing*.

Soumis à la fonderie AMS SiGe 0.35 µm de juin 2010.

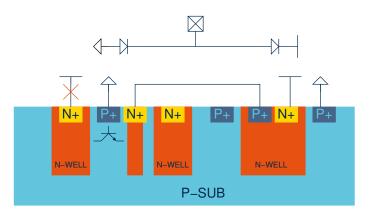

### **Protections**

Des claquages pouvant se produire dans les détecteurs gazeux : il est nécessaire de protéger l'électronique. Problème rencontré avec les chips en technologie AMS  $0.35~\mu m$  :

### Nouvelles diodes

#### Quelques règles de dessin supplémentaires :

- Enlever les PMOS sur le chemin d'entrée

- Augmenter la distance NWell PWell (DRC  $\times 2$  ou  $\times 3$ ))

- Utiliser la distance minimum entre N+ et NWell des diodes

- Minimiser les résistances d'accès

Nouvelles diodes diponibles et compatibles avec les pads AMS. D'autres variantes vont être soumises en *building block*.

Introduction

MAPRA

FE-14

**MICRORO**

## Perspectives

#### **Priorités**

- Terminer les projet en cours : ILC/CLIC, POLAR

- Continuer la collaboration avec le CPPM sur FF-14

- Début d'une collaboration avec le LAL/OMEGA sur OMEGAPIX

#### Autres activités

- Participation au design d'un ASIC pour les chambre à muons d'ATLAS

- Design d'un chip rad-hard pour CTF3/CLIC (beam monitoring)

#### Conclusions

#### Activité microélectronique en forte croissance !

- Tous les chips se font au sein de collaborations

- Fort soutient de la part de la direction du laboratoire, en particulier pour ATLAS

- Conversion d'un numéricien FPGA vers ASIC à plein temps

- Deux personnes supplémentaires sont formées et prêtes à reprendre une activité de design en microélectronique