# 3D technologies at CERN: stacking and tracking for future physics

# ERIK H.M. HEIJNE CERN Genève Ecole Polytechnique 29 November 2007

Erik HEIJNE CERN PH Department

# **ACTIVITY in Si TECHNOLOGY at CERN**

### **MOST RESOURCES GO INTO LHC MACHINE TERMINATION**

**PH MICROELECTRONICS GROUP ME (Marchioro) :**

FOLLOW-UP of CHIP DESIGNS ATLAS, CMS, ALICE, TOTEM, ... MPW + RUNS + SUPPORT CMOS 0.25 um NOW / SOON ALSO 0.13 um and 90 nm

RADHARD CHIPS STUDIES total dose, SEU MODELS, .. (Faccio)

**NEW EXPERIMENTS : NA62**

**EXTERNALLY FUNDED DEVELOPMENT:**

**AMORPHOUS Si (Jarron cs) MEDIPIX (Campbell cs)**

#### PH SUPPORT GROUP TA1(Joram) :

EP Si FACILITY : LHC CONSTRUCTION (Moll) RADHARD Si DETECTORS COORD RD50 IRRADIATION FACILITIES PS p,n (Glaser)

# FUTURE SI ACTIVITY SLHC / ILC / CLIC

EVALUATE + INTRODUCE NEW CMOS TECHNOLOGY CMOS 0.25 um SUCCESFUL, SPECIAL RADHARD LIBRARY EVALUATION of 0.13 um and 90 nm from FEW FOUNDRIES RADHARD STUDIES, MODELS, LIBRARY SOME FOUNDRIES PROMISE 3D BACK END TECHNOLOGY through-wafer vias

pads with under-bump-metal

thinning down to 20 (?) um

**SPECIFIC PROJECTS :**

**CHIP DESIGN**

e.g. DC/DC POWER SUPPLIES, OPTICS DRIVERS, GASEOUS DETECTORS with DIRECT CHIP READOUT: TIMEPIX EUDET (NIKHEF-SACLAY-FREIBURG-)

### OTHER? e.g.FP7?

**NEW COLLABORATIONS ??**

Erik HEIJNE CERN PH Department

# 'RECENT' Si ACTIVITY at CERN

Erik HEIJNE CERN PH Department

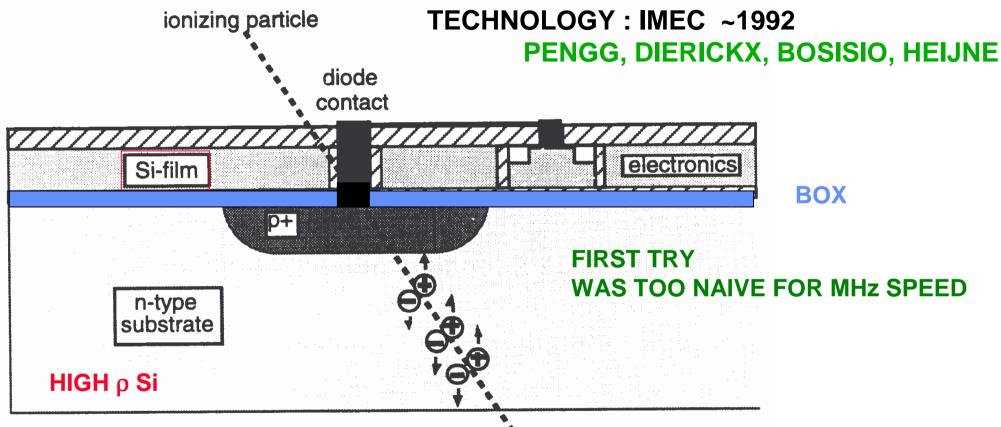

# SOI on HR Si in RD19

Erik HEIJNE CERN PH Department

## **SOI PIXEL DETECTORS**

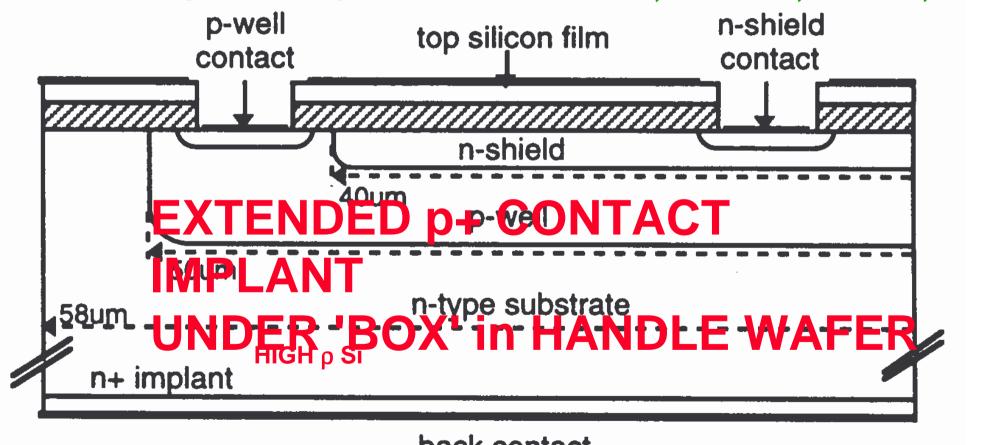

### EXTENDED p+ CONTACT UNDER 'BOX' in HANDLE WAFER

Erik HEIJNE CERN PH Department

### **SOI PIXEL DETECTORS**

#### MORE SOPHISTICATED DESIGN CAREFU L DESIGN for THERMAL BUDGET INCLUDES DEEP p-WELL 'COLLECTOR' and THIN n+ SHIELDING PENGG, DIERICKX, BOSISIO, HEIJN

# COMPLEX SIGNAL PROCESSING

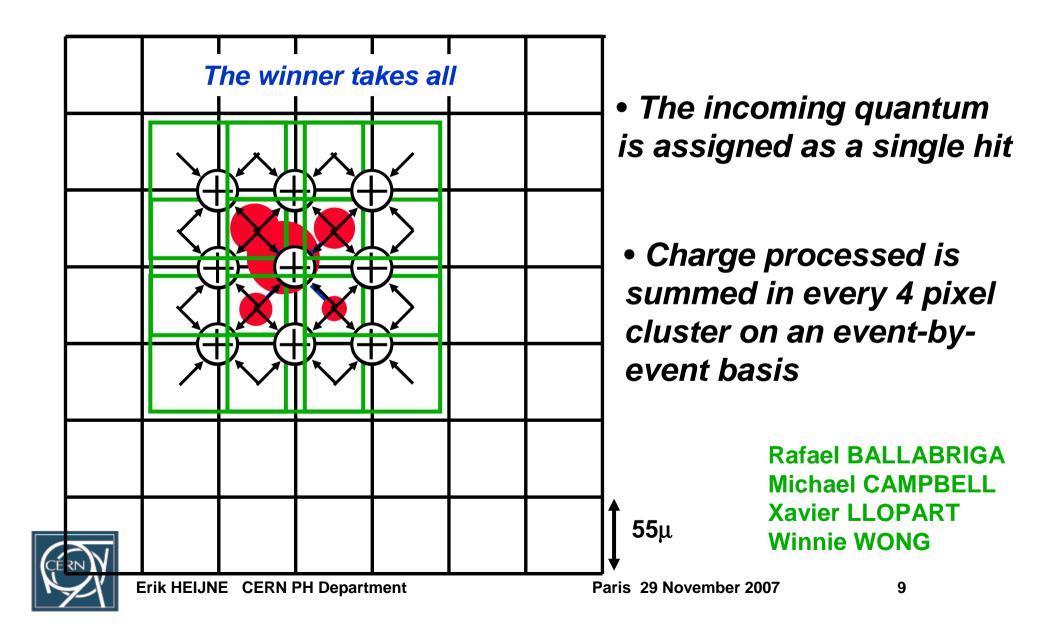

### INCREASED FUNCTIONALITY INTER-PIXEL COMMUNICATION MEDIPIX3

Erik HEIJNE CERN PH Department

#### Medipix3 – charge summing concept

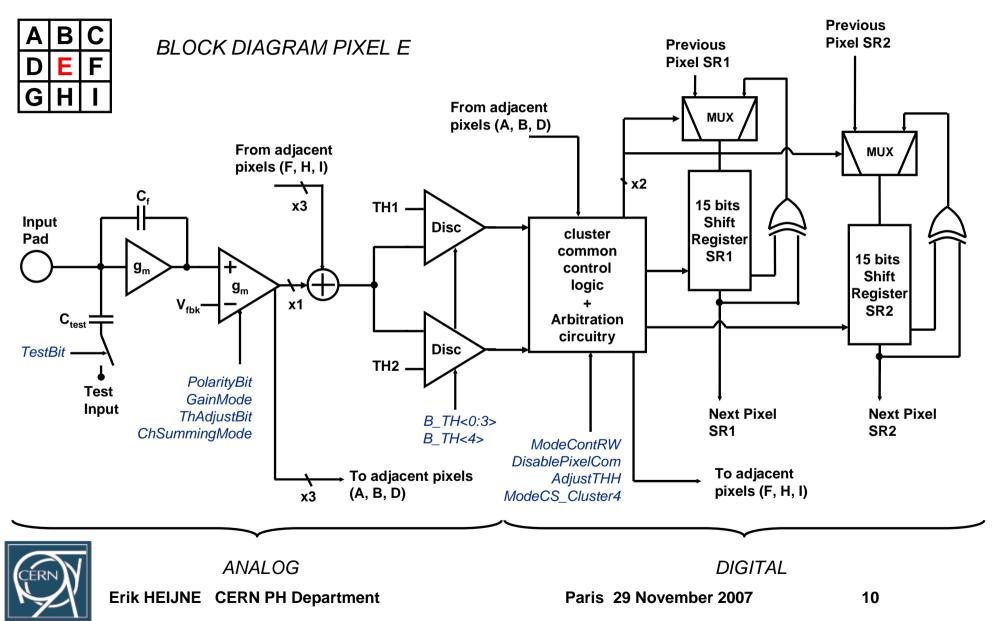

#### Medipix3 prototype – pixel block diagram

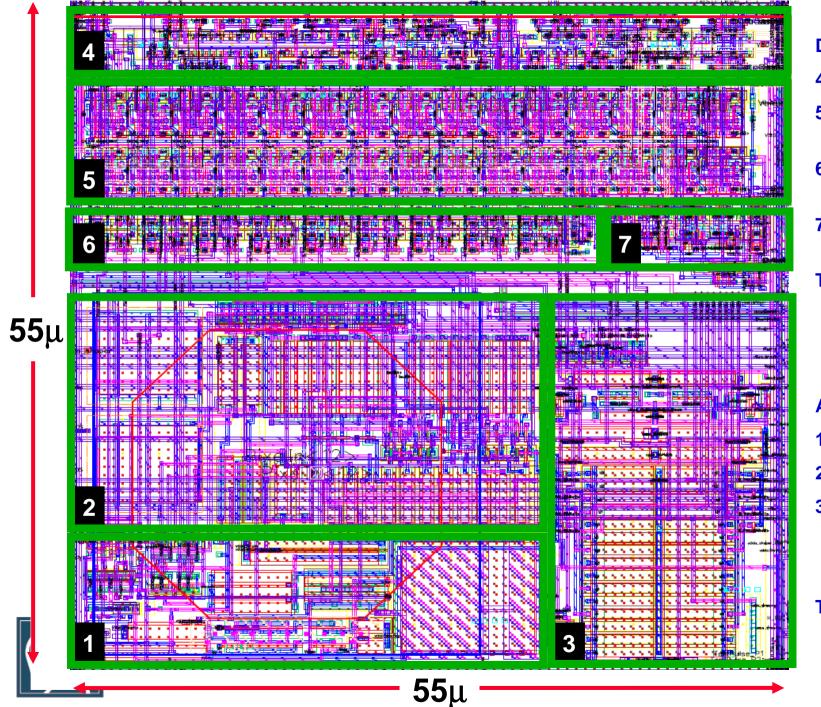

#### **DIGITAL CIRCUITRY**

- 4. Control logic (124)

- 5. 2x15bit counters / shift registers (480)

- 6. Configuration latches (152)

- 7. Arbitration circuits (100)

**Total digital 856**

#### **ANALOG CIRCUITRY**

- 1. Preamplifier (24)

- 2. Shaper (134)

- 3. Discriminators and Threshold Adjustment Circuits (72)

**Total analog 230**

**Rafael BALLABRIGA**

# STACKING of HYBRID SENSORS + CHIPS

# Si, $\alpha$ -Si, MCP, GAS,...

Erik HEIJNE CERN PH Department

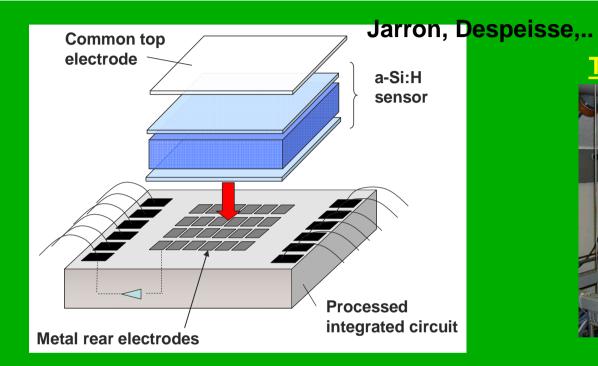

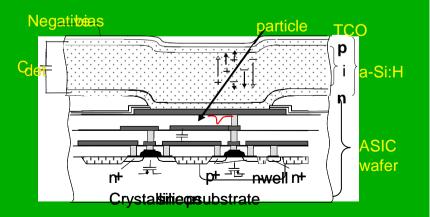

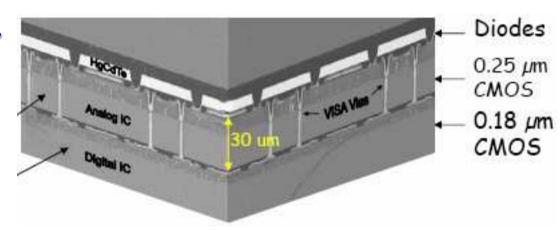

# **α-Si THIN FILM on ASIC (TFA)**

Deposition of hydrogenated amorphous silicon on ASIC Very High Frequency Plasma Enhanced Chemical Vapor Deposition (VHF - PECVD)

Micromorph module production at UNAXIS

large-volume, low-cost manufacturing of thin-film silicon PV modules KAI simultaneous coating of 20 glass plates of 1.4 m<sup>2</sup> each

#### Institute of Micro-Technology in Neuchatel

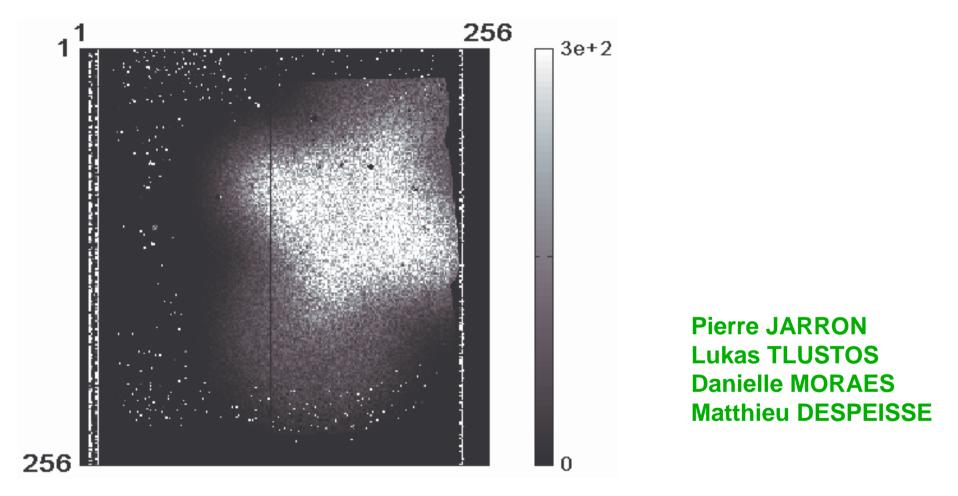

### **Medipix2 with amorphous Si**

# Image with 20 keV electrons (Class D chip) No bump bonding, 'evaporated' $\alpha$ Si Si layer thickness ~ 5 $\mu$ m

Erik HEIJNE CERN PH Department

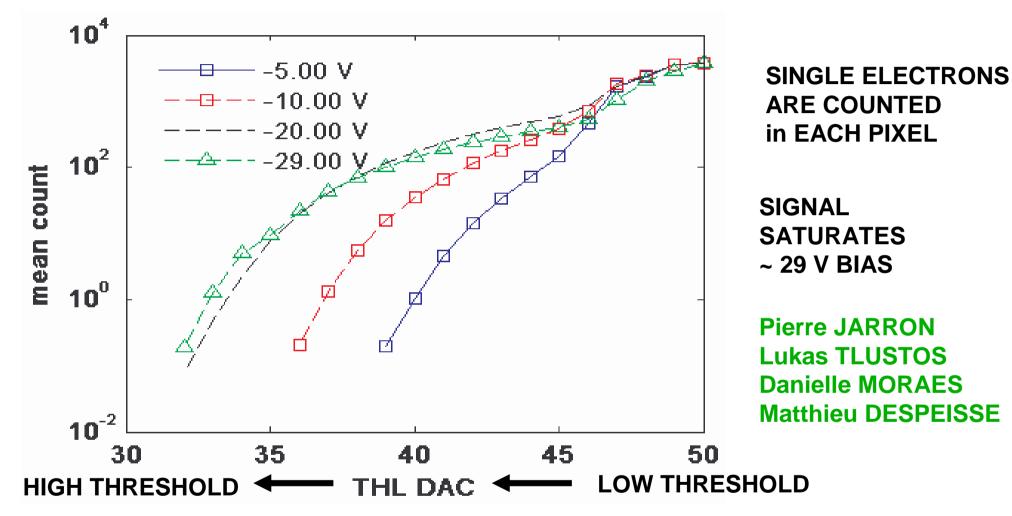

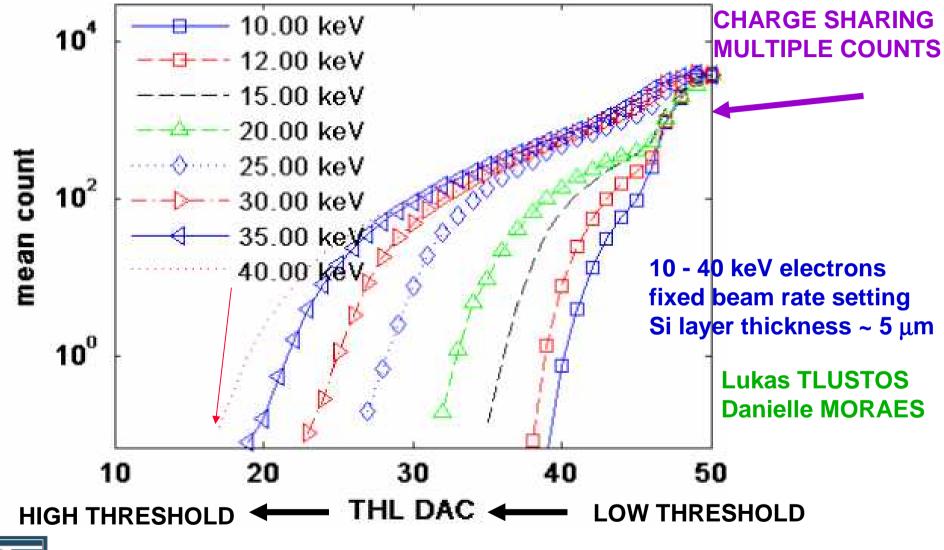

### Threshold scan 20 keV electrons in a - Si

# **ELECTRON SIGNAL a- Si vs keV ENERGY**

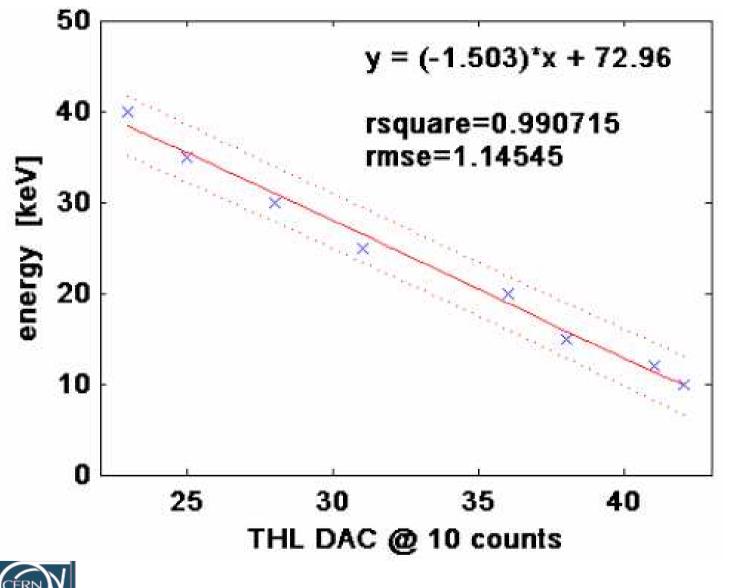

## **ENERGY vs THRESHOLD a - Si**

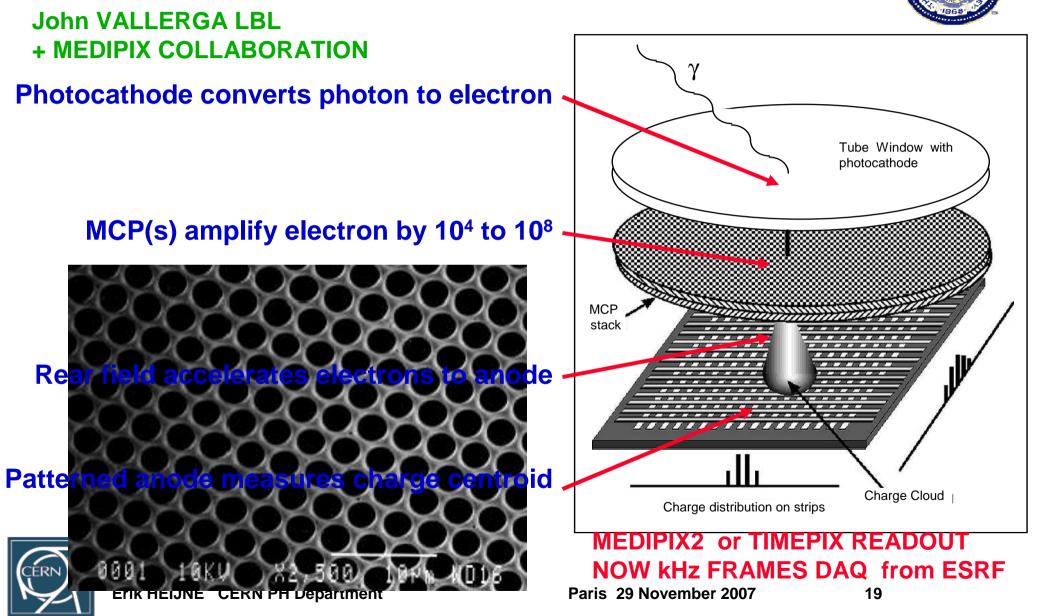

# **VISIBLE PHOTONS**

Erik HEIJNE CERN PH Department

# **Visible Photon Imaging**

# GAS MULTIPLICATION ABOVE PIXEL CHIP

# TIMEPIX

Erik HEIJNE CERN PH Department

# **Timepix with 3-GEM detector**

MPXR CHIP MODIFICATION Xavier LLOPART (CERN), idea J. VISSCHERS (NIKHEF)

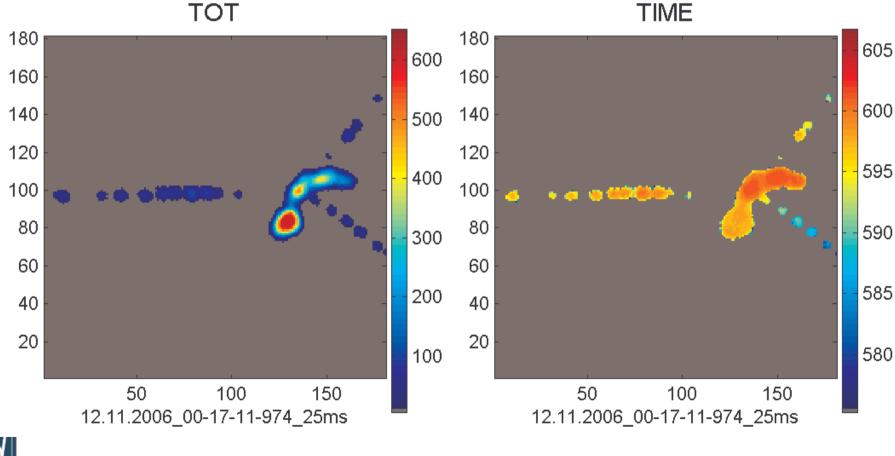

#### DESY testbeam in November 2006 (A.Bamberger, U. Renz, M.Titov)

Erik HEIJNE CERN PH Department

# **Timepix with Micromegas**

January 2007 Nikhef + Saclay Jan Timmermans Harry van de Graaf

TIME of ARRIVAL on CHIP of ELECTRON in GAS

### TIMEPIX QUAD Si Arrival Time electrons <sup>90</sup>Sr

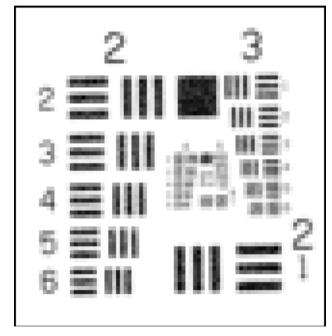

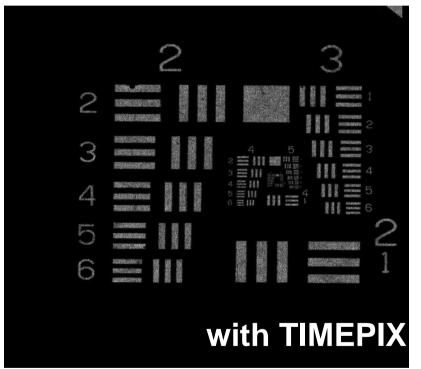

# **Visible imaging - Sub-Pixel Resolution**

#### John VALLERGA LBL **sub-pixel resolution with** + MEDIPIX COLLABORATION **analog cluster centroiding algorithm**

Theoretical pixel resolution 9 lp/mm (55 μm).

Erik HEIJNE CERN PH Department

# AirForce 5-6 pattern resolved corresponding to 57 lp/mm (8.8 μm).

# MINIATURIZATION PACKAGING STACKING SYSTEM

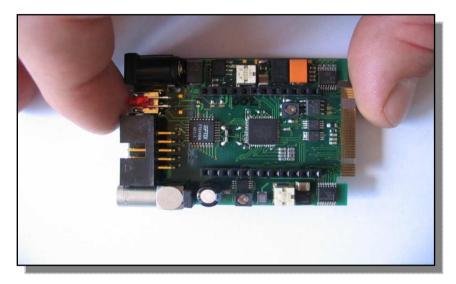

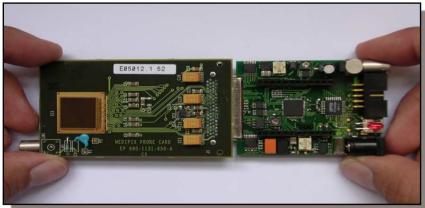

### **USB based Medipix2 Readout System**

USB1 compatible Includes Pixelman readout software Developed by S. Pospisil et al. CTU, Prague

Erik HEIJNE CERN PH Department

# **MEDIPIX USB**

#### with hybrid, bonded bare chip/

APPLY MINIATURIZATION in PHYSICS !!!!!

#### **CTU Prag**

Erik HEIJNE CERN PH Department

# STACKING THIN CELLS

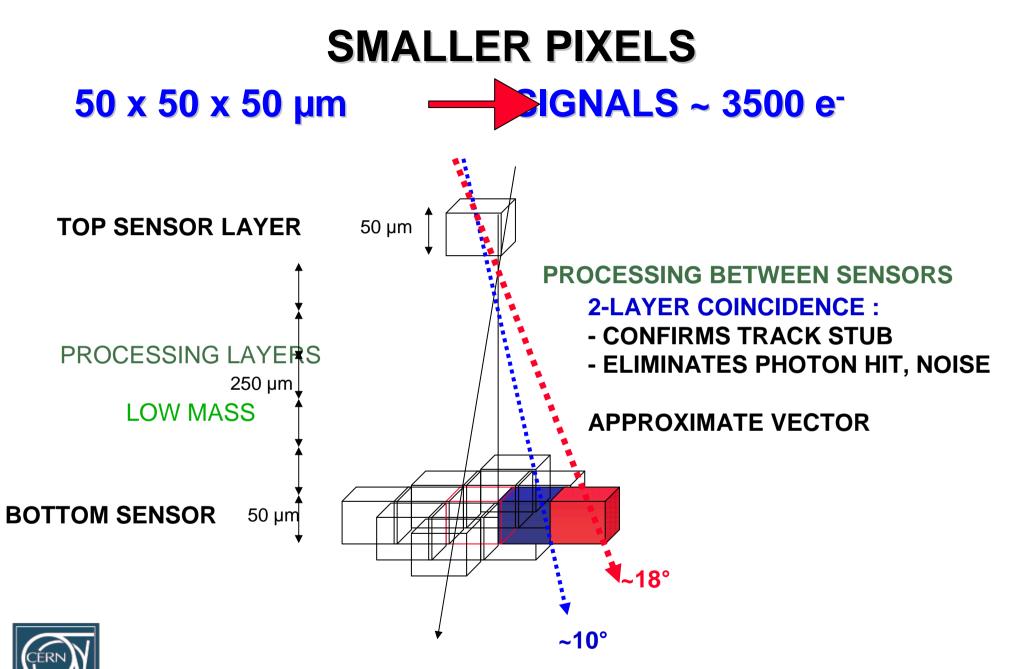

# **50 um CUBES**

Erik HEIJNE CERN PH Department

Erik HEIJNE CERN PH Department

# **TRACK VECTOR DETECTOR**

### **3D MULTILAYER ASSEMBLY**

Erik HEIJNE CERN PH Department

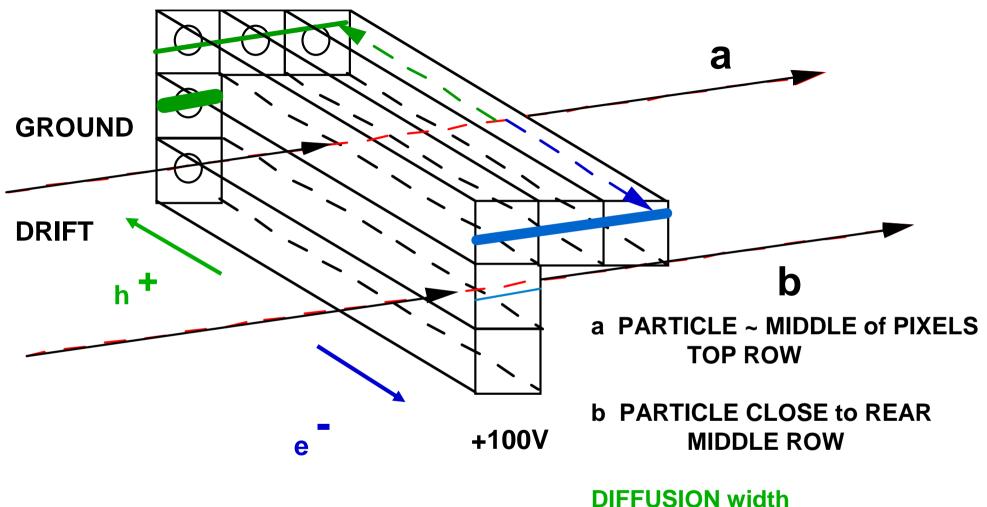

#### **CHARGE COLLECTION & LATERAL DIFFUSION**

**TRY with Si MEDIPIX**

Erik HEIJNE CERN PH Department

shown EXAGGERATED

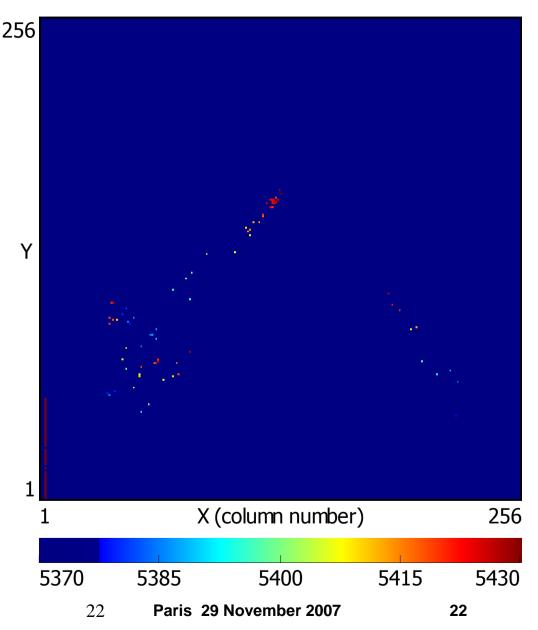

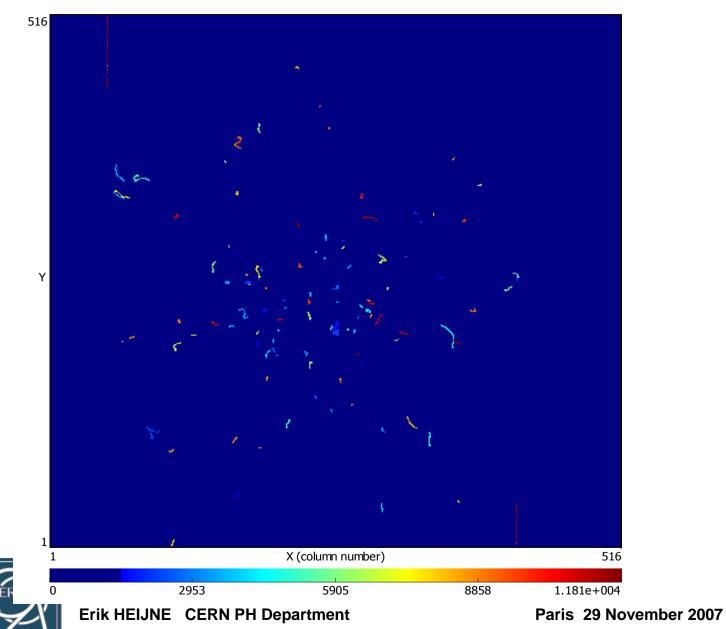

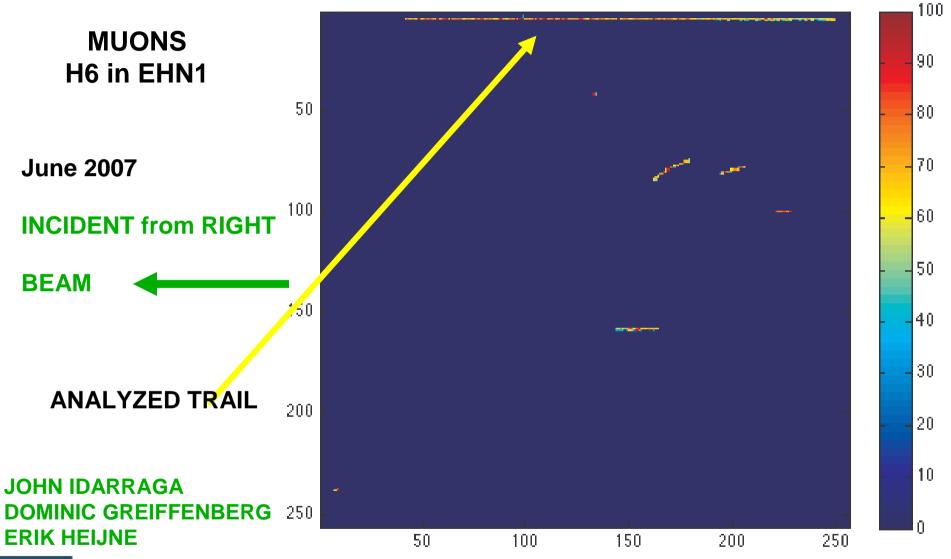

### **TIMEPIX as SILICON 'EMULSION'**

256 'STACKED' Si CELLS

H6 PION BEAM 2007

**INCIDENT** from **RIGHT**

BEAM

QuickTime<sup>™</sup> and a TIFF (Uncompressed) decompressor are needed to see this picture.

Erik HEIJNE Dominic GREIFFENBERG John IDARRAGA - ANALYSIS

Erik HEIJNE CERN PH Departm

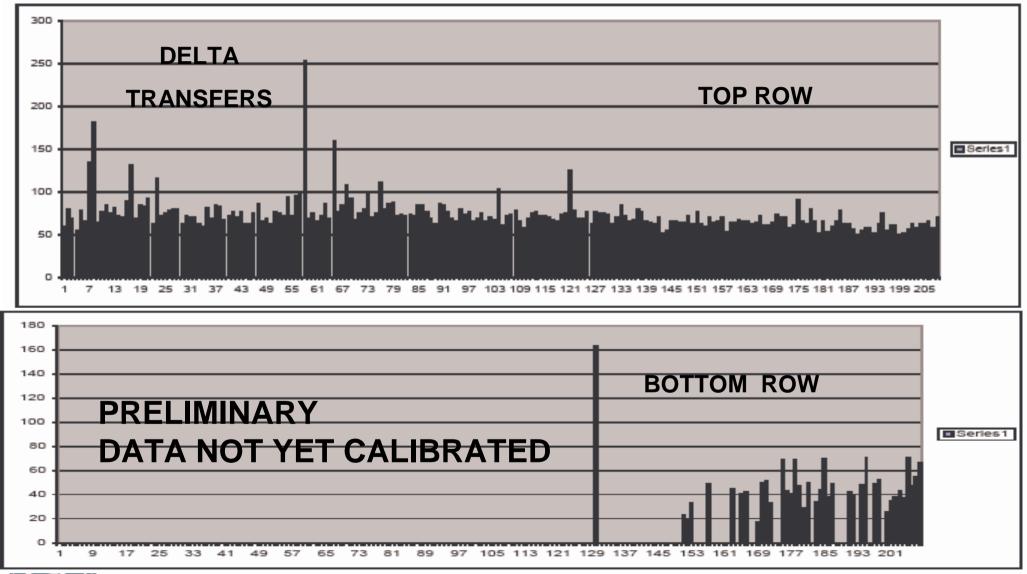

### **MEASUREMENTS with MIPs in Si TIMEPIX (2007)**

Erik HEIJNE CERN PH Department

### **TRAIL ANALYSIS FRAME 29853**

## **MAJOR OPPORTUNITIES**

### THIN SILICON for CMOS and for SENSORS

LOW NOISE NEEDED < 80 e<sup>-</sup> rms

THIN SENSORS MORE RADHARD ?

**3D SPACE POINTS** 50 or 40 um cubes ?

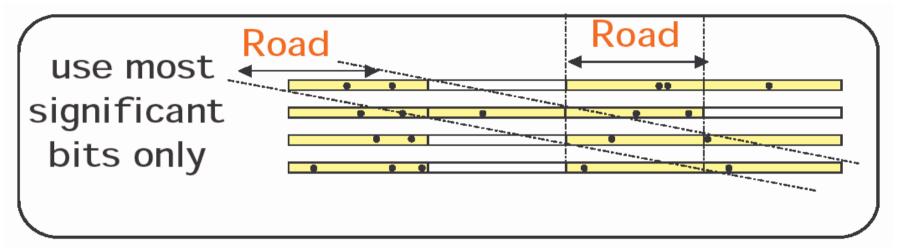

### **TRIGGER FUNCTIONS with STACKED LAYERS**

#### ENHANCED FUNCTIONALITY on SMALL AREA TRACK VECTORS + SELECTIVITY on STIFF TRACKS

Erik HEIJNE CERN PH Department

### WHICH NEW PHYSICS CAN BE DONE WITH THIS ?

#### INTRODUCTION of Si MICROSTRIP TECHNOLOGY ALLOWED STUDY of CHARM and BEAUTY

Erik HEIJNE CERN PH Department

# THE END

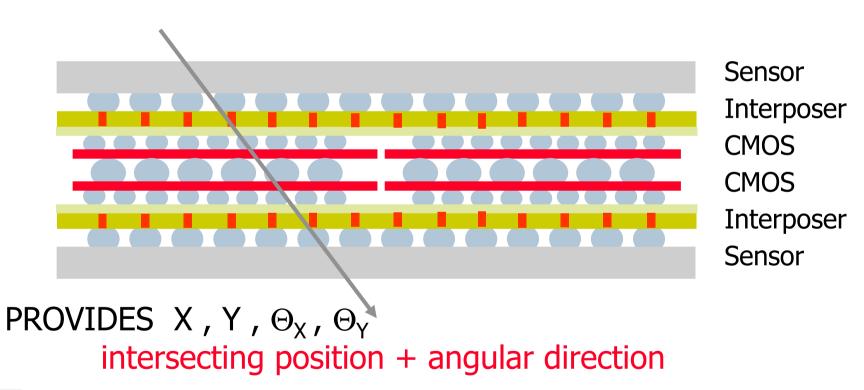

# **AMBITIOUS MULTI-LAYER STRUCTURE**

# **ADDITIONAL SLIDES**

Erik HEIJNE CERN PH Department

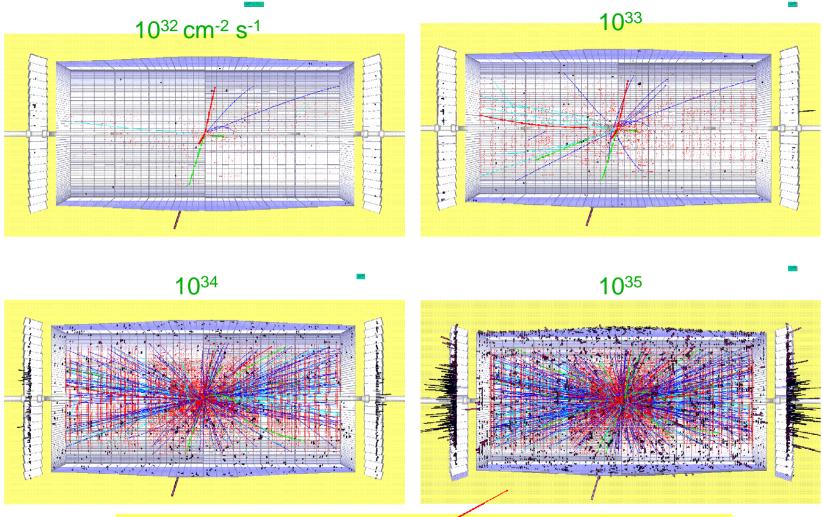

# **CMS from LHC to SLHC**

# The tracker is the key detector which will require upgrading for SLHC

Erik HEIJNE CERN PH Department

Paris 29 November 2007

41

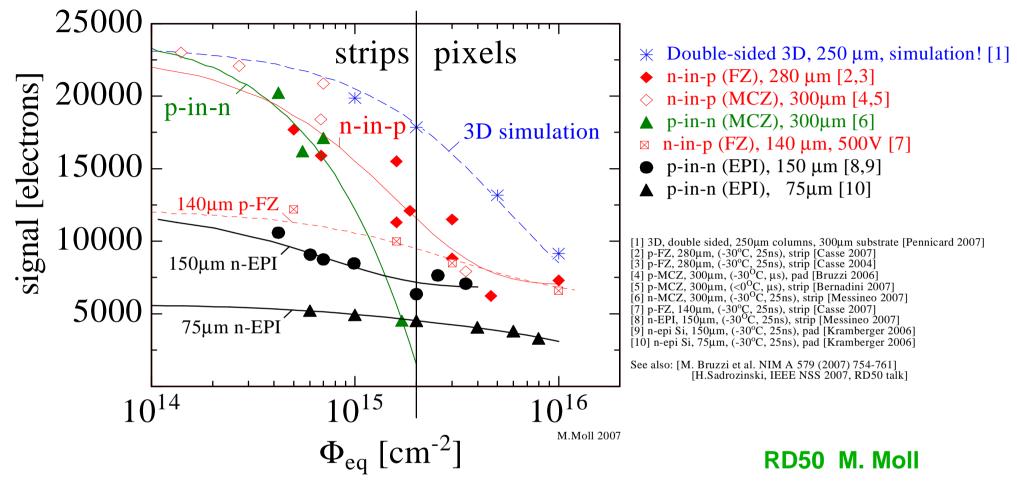

# **COMPARISON VARIOUS SI SENSORS**

~ 10<sup>15</sup> n<sub>eq</sub>/cm<sup>2</sup> all planar sensors loose sensitivity: trapping No obvious material for innermost pixel layers : OPTIONS ? COLUMN '3-D' sensors ? THIN sensors ? replace inner layers ?

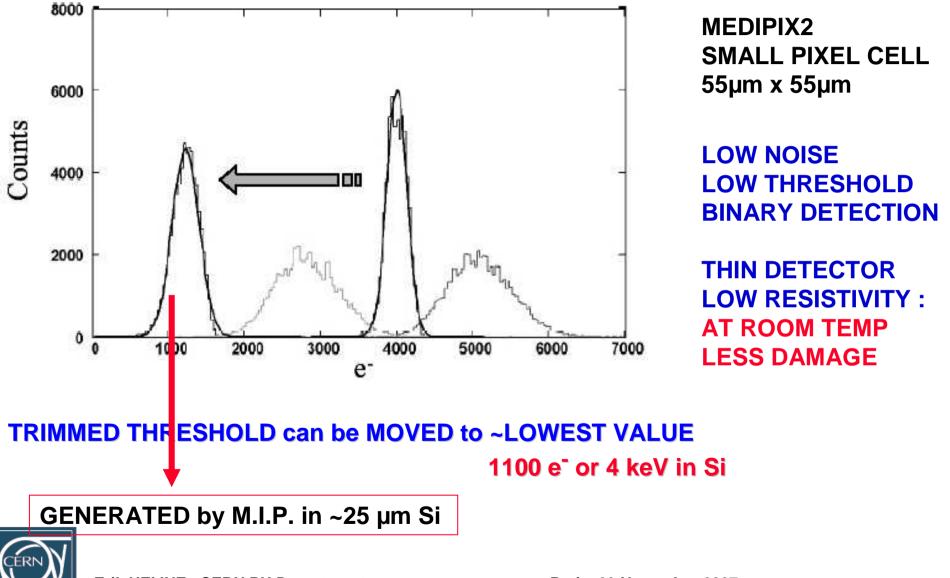

# LOW SIGNALS CAN BE EMPLOYED

Erik HEIJNE CERN PH Department

Erik HEIJNE CERN PH Department

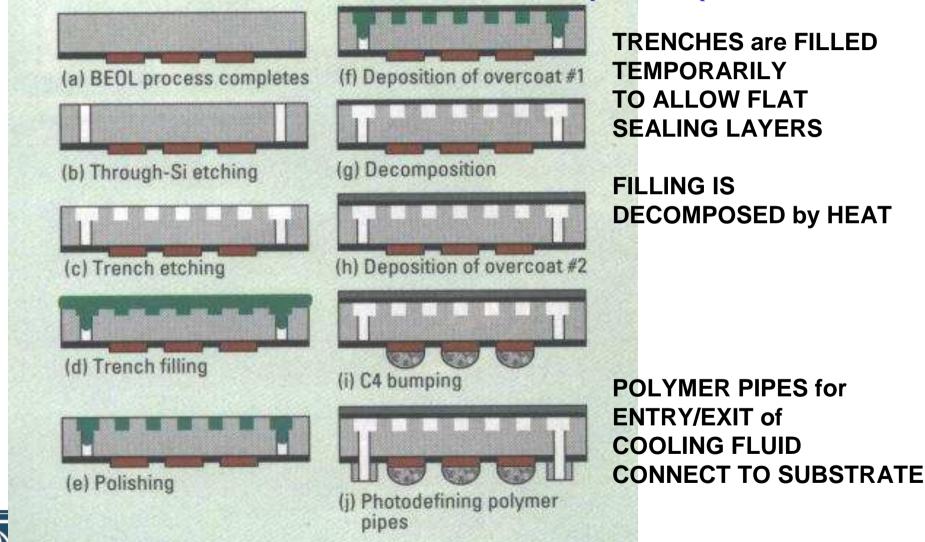

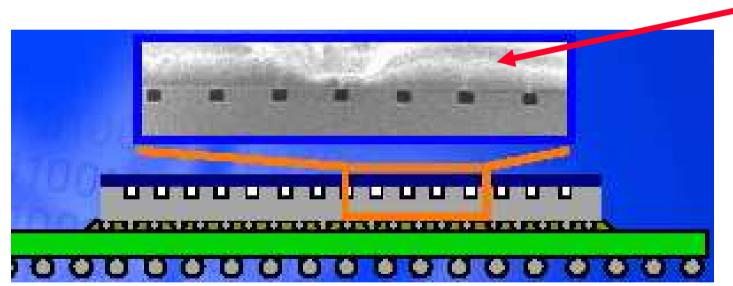

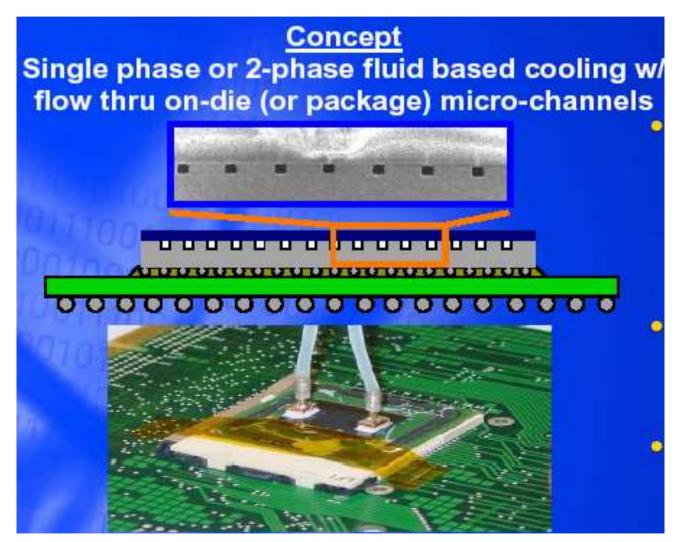

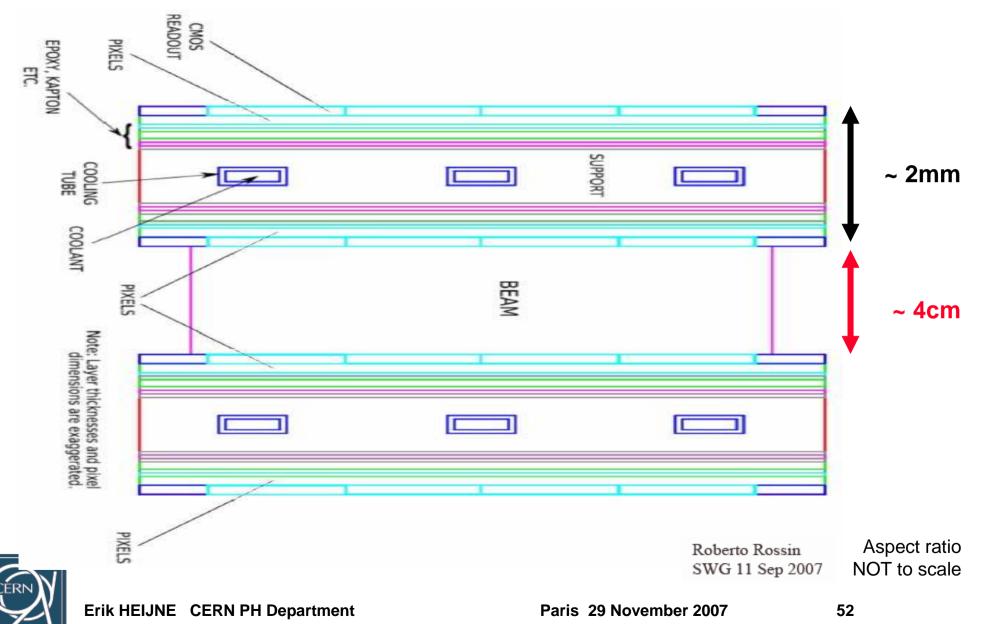

# **SYSTEM INTEGRATION : COOLING**

#### **COOLING inside the CHIPS** 100 W per cm2 possible

# **INTEGRATED CHIP COOLING**

#### **BRING COOLING CLOSE to HEAT SOURCE**

#### 'NORMAL' CMOS WAFER

Erik HEIJNE CERN PH Department

# **INTEGRATED CHIP COOLING**

#### WAFERS are FUSED after ETCHING CHANNEL

# STACKING

# INTERCONNECTS

# WIREBONDING STILL WIDELY APPLIED MULTILAYER now OFTEN USED for SENSORS (IR)

#### **BUMP BONDING for**

HIGH RELIABILITY HIGH DENSITY THIN PACKAGE

#### FUTURE 'BUMP-LESS BUILDUP' maybe THINNER

Erik HEIJNE CERN PH Department

# **NEW DETECTORS ?**

# SILICON submicron CMOS ALLOWS PIXEL FUNCTIONS SELECTIVITY CAN BE BUILT-IN

#### VERY LOW NOISE with SMALL PIXELS ~40 e<sup>-</sup> rms

# **3D FUNCTIONS with HYBRID PACKAGING** TRACK VECTORS + SELECTIVITY

#### THIN DEVICES ARE RADHARD

Erik HEIJNE CERN PH Department

# IDEAS for VECTOR DETECTOR in CMS

CMS SLHC TENTATIVE TRACKER 'Straw Man' LAYOUT

## CMS TENTATIVE TRACKER DESIGN SLHC

#### CMS STUDIES are ONGOING

•Hit Pair Pt Resolution

•Track Stub Pt Resolution

•Fake Rate & Efficiency if require •Single Hit Efficiency: 95%~99.5% •4/4 hits in sensor pair •1/3 vs 2/3 Track Stubs

•Min radius at which scheme works effectively

•All the above varying the design parameters over the plausible range •Eg. Effect of cell geometry on resolution, occupancy and resulting effect on fake rate & efficiency

# **SOFTWARE or also HARDWARE ?**

FAST-TRACK COLLABORATION

## **USE MICROPROCESSORS for FAST TRIGGER**

#### MULTI-LAYER-DETECTOR with LOCAL PROCESSING :

## **SPACE-POINT + VECTOR**

**VERTEX SELECTION, BACKGROUND SUPPRESSION, ..**

Erik HEIJNE CERN PH Department