## 3D DRIE Activities & plans of Alcatel

Michel PUECH 3 DIT Workshop Palaiseau Nov. 29<sup>th</sup> 2007

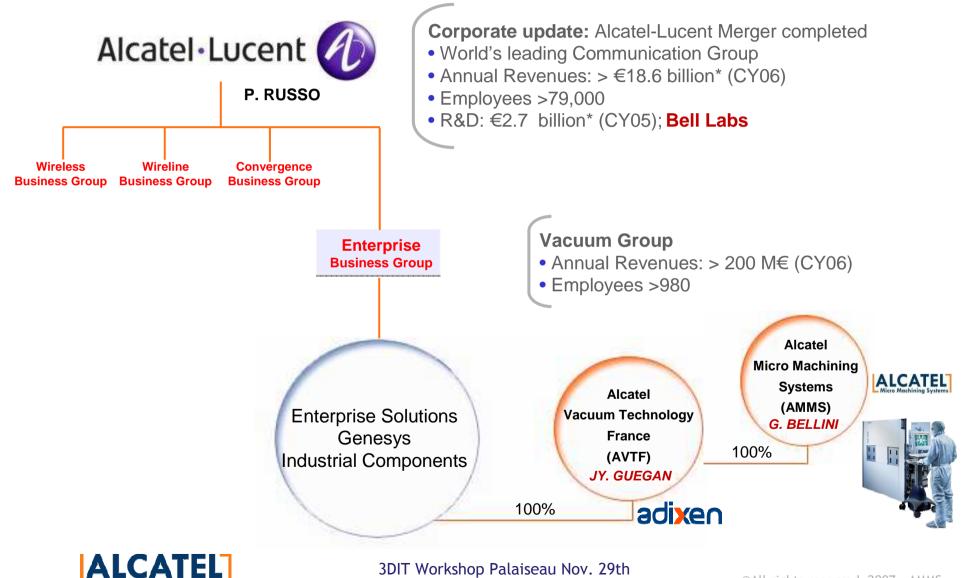

#### Part of a Worldwide Leader, High Tech, Multinational Corporation

2007

## Outline

- Introduction

- DRIE: Semiconductors and Microsystems

- Majors Achievements

- Trends & perspectives

- Conclusion

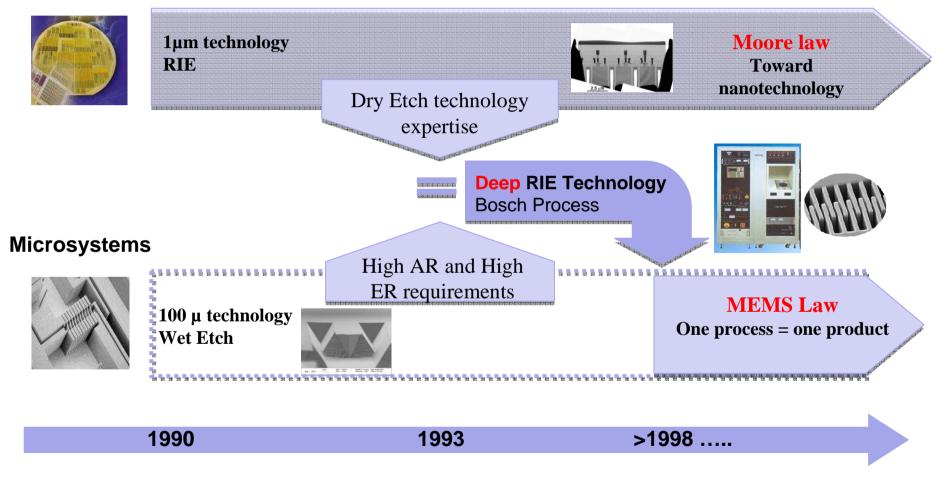

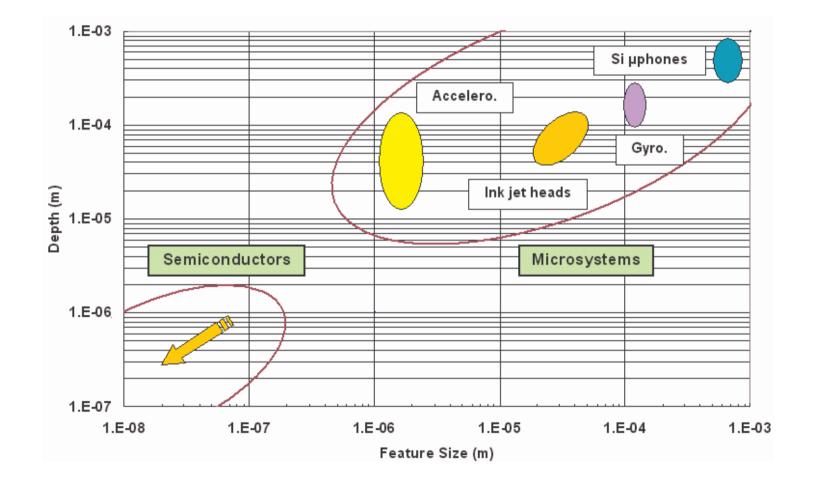

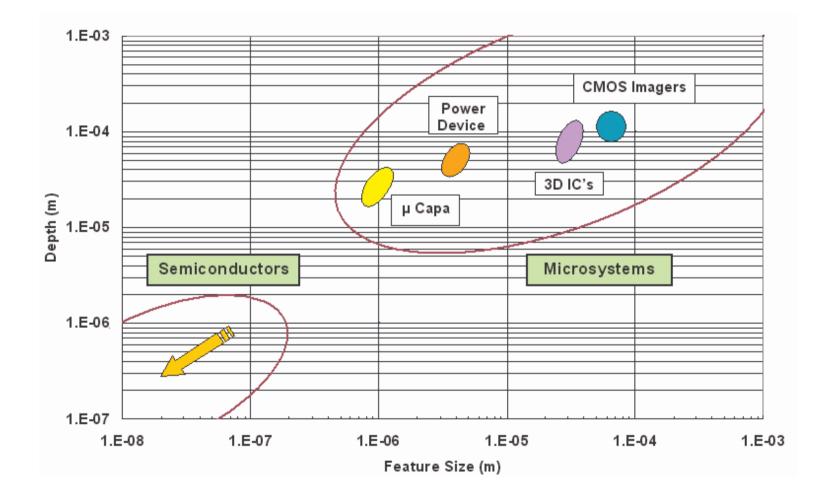

## S.C. Etching tools & Microsystems

#### Semiconductor

#### Microsystems & Semiconductors

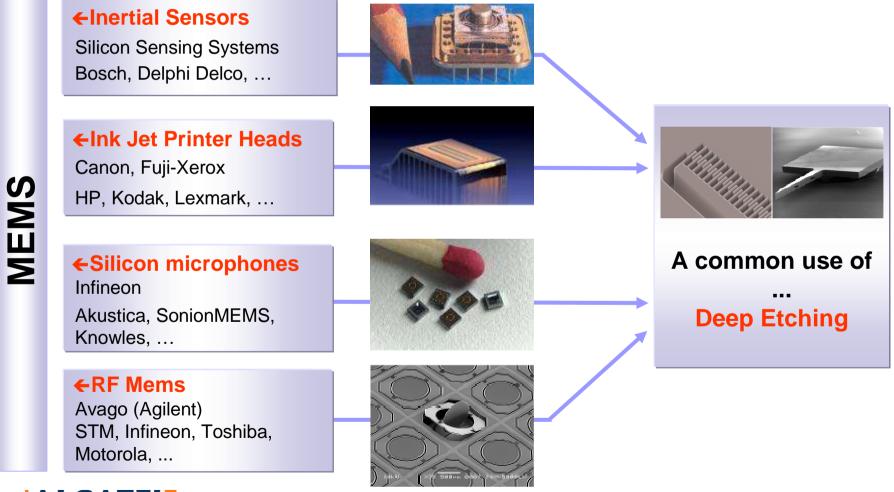

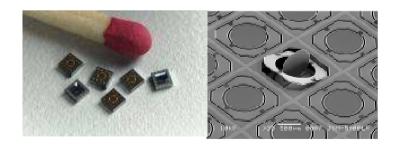

• Microsystems: a wide range of size & depth !

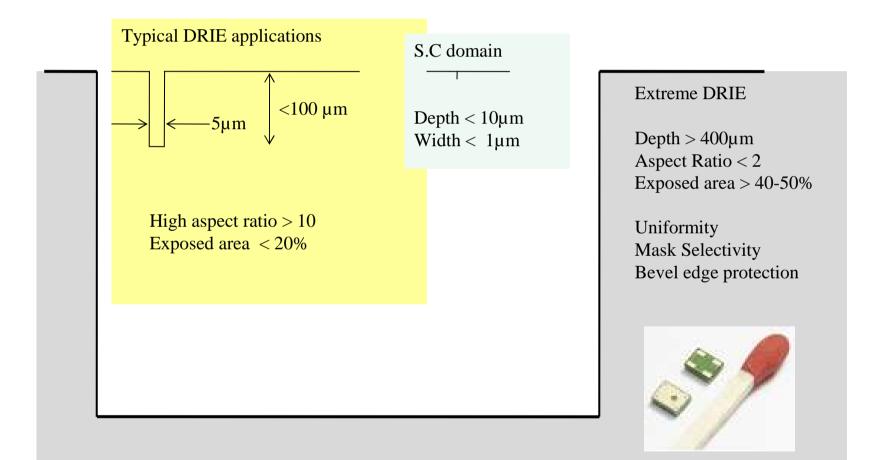

#### **DRIE requirements for MEMS**

#### Microsystems: a huge volume of Si to remove !

#### **DRIE requirements for MEMS**

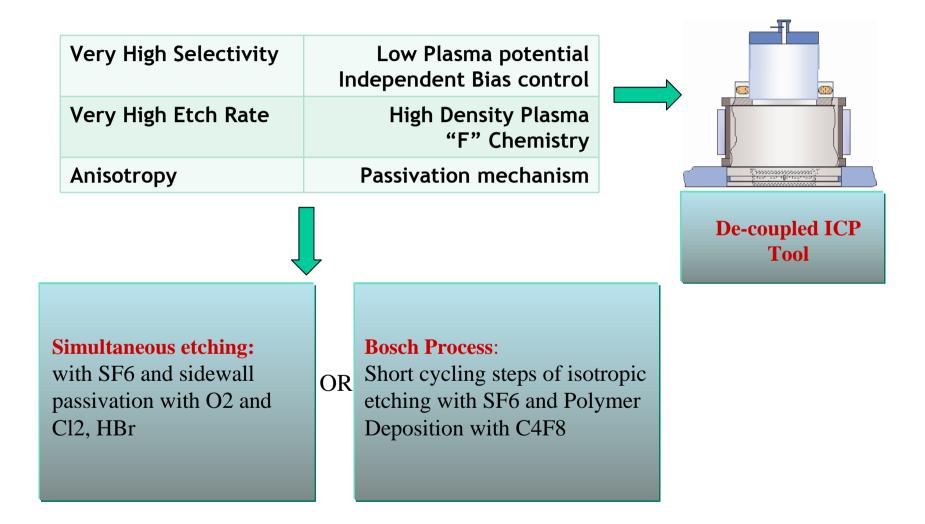

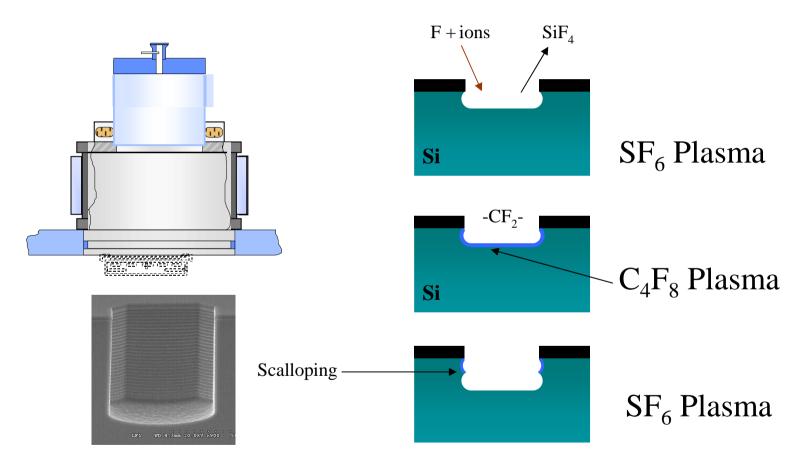

# The "Bosch\*" Process

• A time multiplexed process between Etch & Passivation

\*US pat. 5,501,593 Publi. Mar. 26, 1996

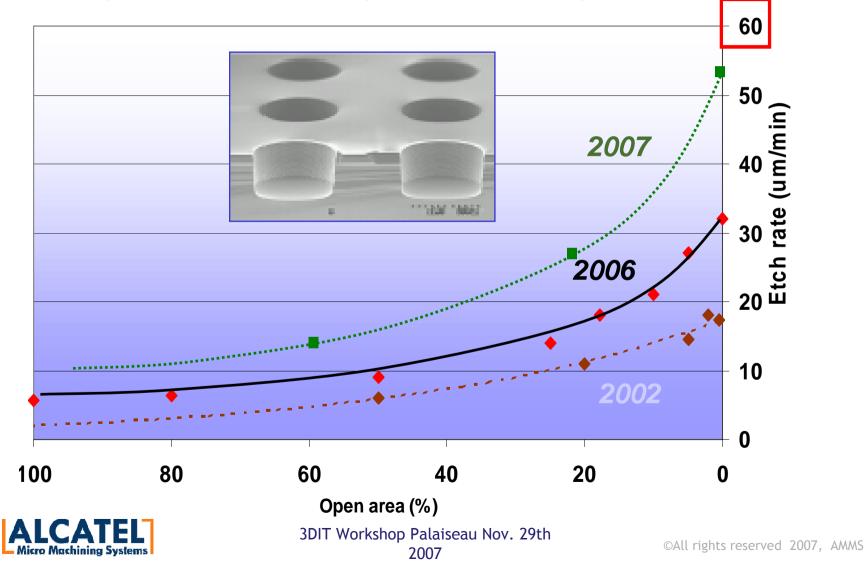

#### The Race Toward Higher Etch Rate

• Si Etching by "F" : a chemical process w/ loading effect

#### The Race Toward Higher Etch Rate

- Higher gas flow / pressure, Better gas utilization

- Higher RF Power

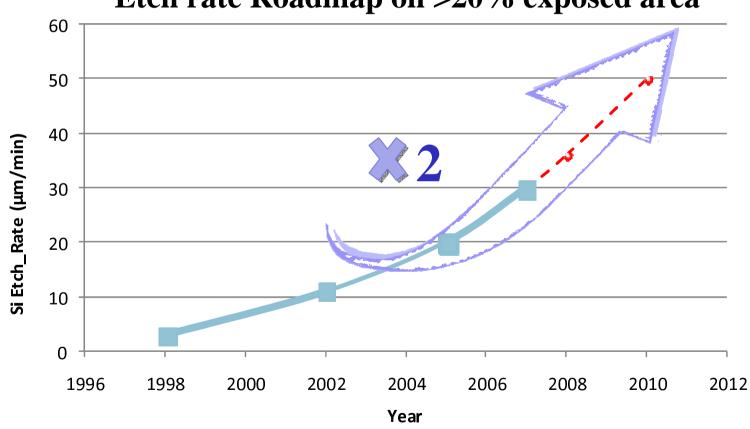

#### Etch rate Roadmap on >20% exposed area

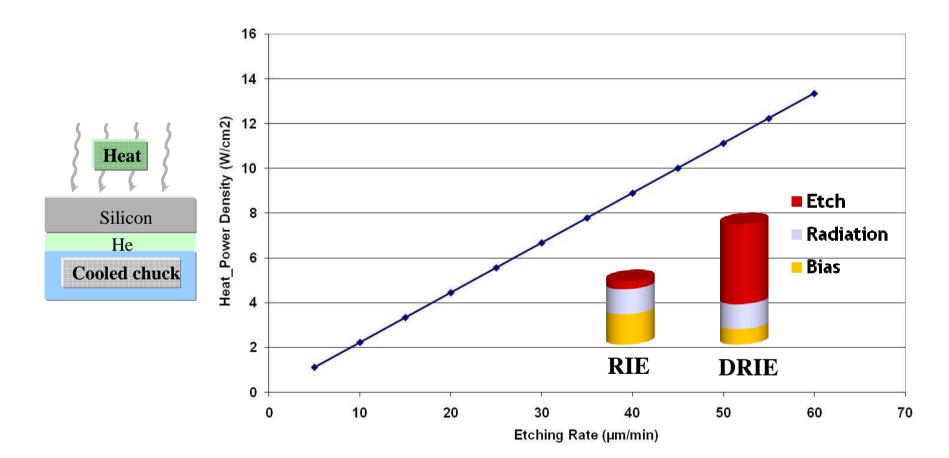

## Thermal Budget issues

• But :  $Si_{(s)} + 4F_{(g)} \longrightarrow SiF_{4(g)} + 385 \text{ kcal/mol }!!$

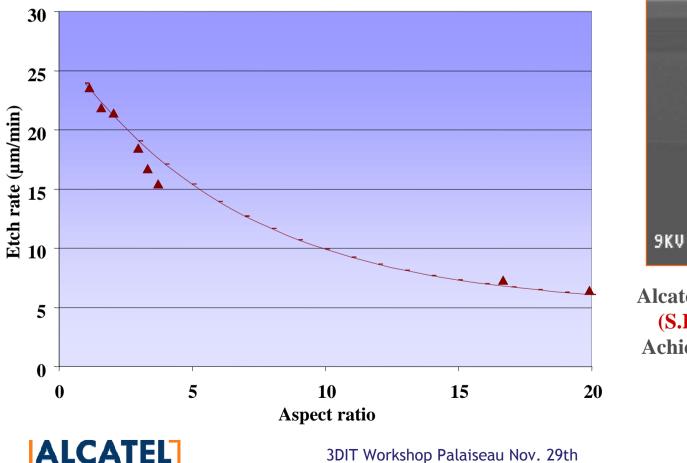

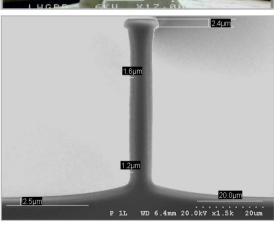

#### Aspect Ratio Dependent Etching

#### • Silicon Etch rate is sensitive to Aspect ratio (species transport limitation)

Micro Machinina Systems

Etch rate versus the aspect ratio for an exposed area around 25 %

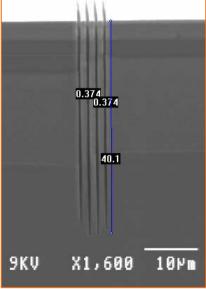

Alcatel Patented process (S.H.A.R.P. process) Achieving Aspect Ratio > 110

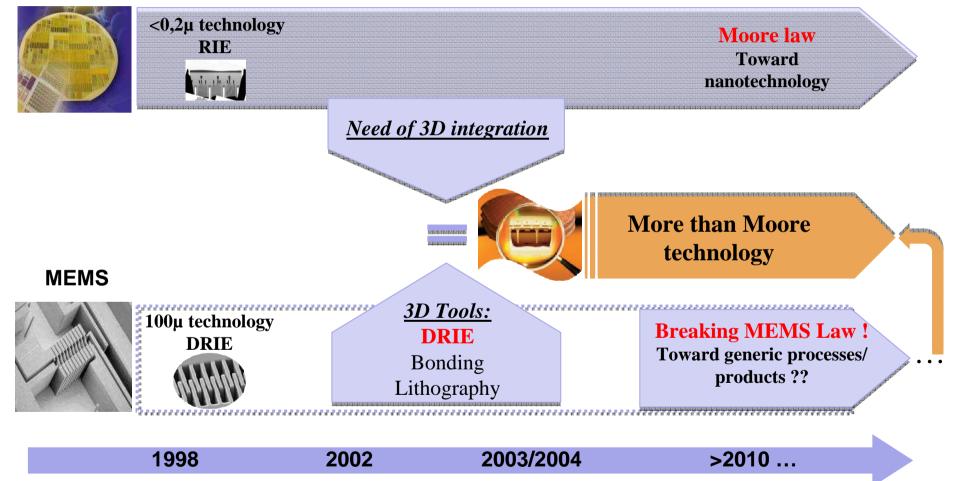

#### New perspectives for the DRIE

• DRIE: a key technology to address the 3<sup>rd</sup> dimension

## Interest from S.C

#### Semiconductor

## Interest from S.C

• Common need of Deep etching and LT-PECVD :

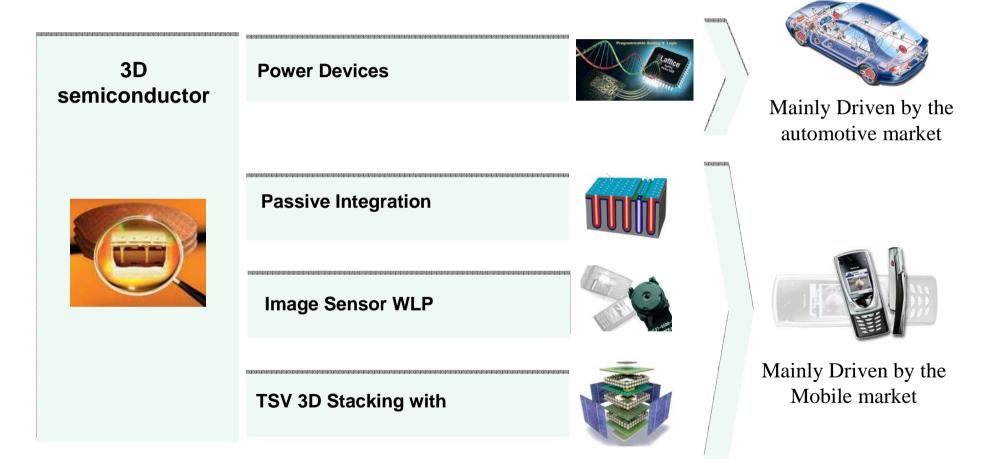

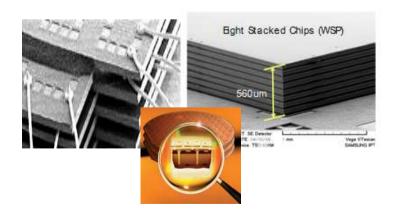

## 3D SC within the scope of DRIE

3D S.C fall into the micro-systems domain !

#### **Process Range**

... addressing 3D integration applications

#### **Silicon Via etch Thick SiO2 Etch** en SiN ICP) 0.374 40.1 X1,600 X330 50Mm 0000 12/DEC/05 30um x 25um x 175um 190um 22 µm Si 1.5 µm SiO<sub>2</sub>

WD 4.3mm

3DIT Workshop Palaiseau Nov. 29th 2007

Process *T*°< 150℃ Conformity in High Aspect Ratio features >60%

## Transition to 300 mm

• 300 mm transition driven by mobile applications

MEMSPower DevicesPassives integration

•WLP CMOS image sensors•3D integration/ Device Stacking

## Conclusion

- DRIE of silicon became a key enabling technology for MEMS.

- Within a decade, DRIE increased productivity by almost a factor of 10.

- New process challenges have been quickly addressed.

- Semiconductor supply chain is looking to DRIE for the emerging 3D semiconductor applications

- Microsystems should take benefits from those new applications

# www.alcatelmicromachining.com