## Status and plans in 3D Technologies; summary - EMC-3D

**Paul Siblerud**

EMC<sup>3D</sup> Program Manager

**V.P. Electrochemical Deposition**

Semitool, Inc.

www.emc3d.org

Semiconductor 3-D Equipment and Materials Consortium

Ecole Polytechnique Paris - 3D Technical Symposium; November 2007<sub>Page1</sub>

# Contents

- EMC<sup>3D</sup> Introduction (Brief)

- Packaging and Interconnects Common Challenges/ Interests

- Challenges of Interconnects

- Direction of Packaging

- 'Fusion' Era

- Enabling Technologies

- 3D CoO The ultimate driver

- Summary

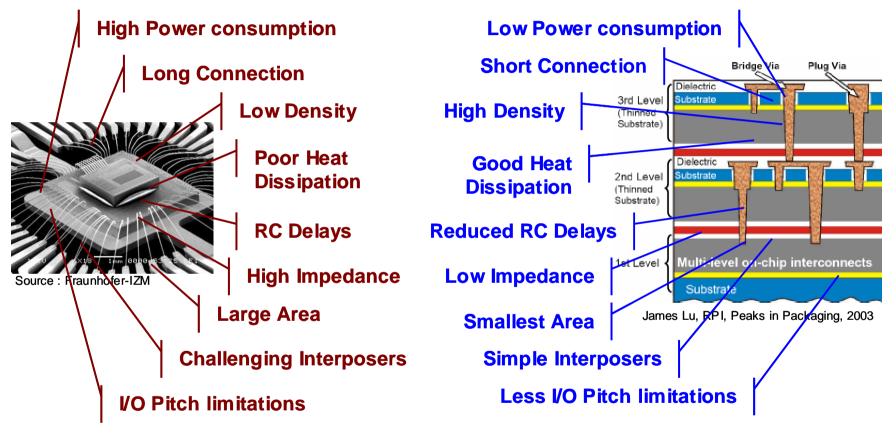

TSV (Through-Silicon-Via) electrodes can provide vertical connections that are both the shortest and the most plentiful.

TSV interconnects provide solutions to many limitations of current SiP and Chip Stacking methods.

# Announcement ; Oct. 11th, 2006

#### EMC-3D consortium created for the development of cost-effective 3D Thru-Silicon-Via interconnect

# Equipment providers, materials companies and researchers join in an international consortium to address complex integration of TSV 3D chip interconnect.

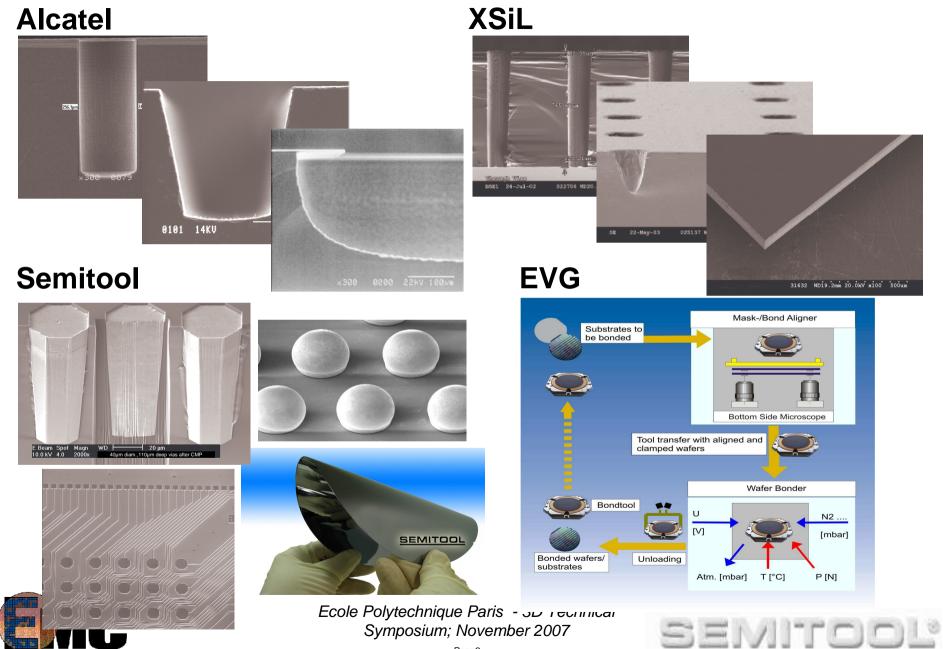

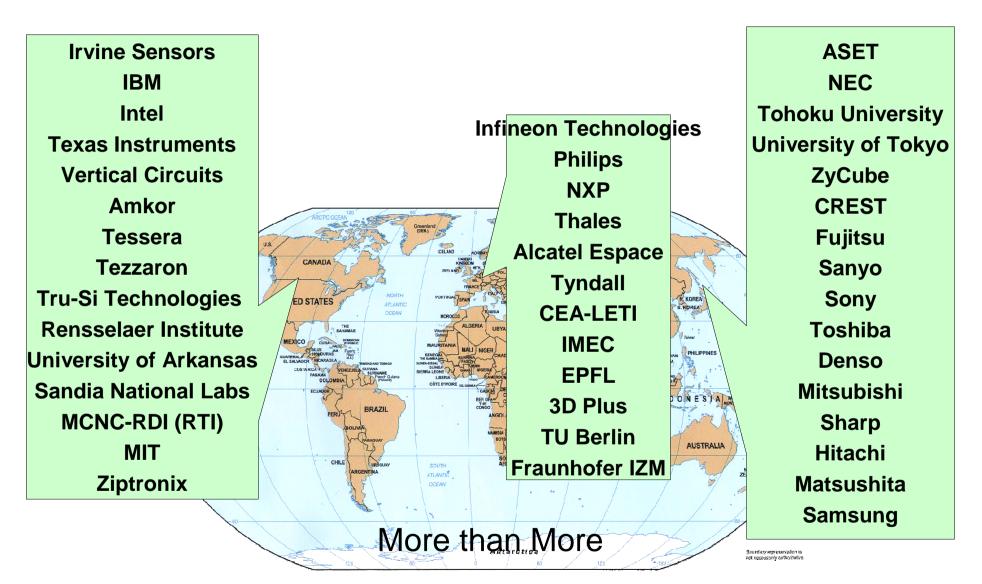

SALZBURG, Austria, October 11<sup>th</sup>, 2006. EMC-3D is a new consortium created to address the technical and cost issues of creating 3D interconnects using TSV technology for chip stacking and MEMS/sensors packaging. Several major equipment manufactures have joined with material companies to work with key research groups to address the issues of cost-effective manufacturing and integration. Equipment companies initiating the consortium are Alcatel, EV Group, Semitool and XSiL.

Associate research members include Fraunhofer IZM, SAIT (Samsung Advanced Institute of Technology), KAIST (Korea Advanced Institute of Science and Technology) and TAMU (Texas A&M University). Material members include Rohm and Haas, Honeywell, Enthone, and AZ with wafer service support from Isonics.

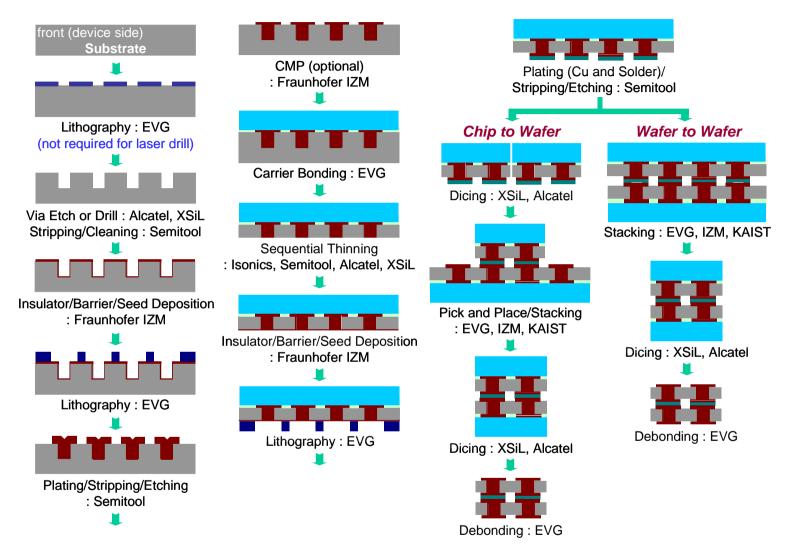

The consortium will develop processes for creating micro vias between 5 and 30um on thinned 50um 300mm wafers using both via-first and via-last techniques. Major processes being integrated into the EMC-3D program are via etch and laser drill, insulator/barrier/seed deposition, micro via patterning with RDL capabilities, high aspect ratio Cu plating, carrier bonding, sequential wafer thinning, backside insulator/barrier/seed deposition, backside lithography, backside contact metal plating, chip-to-wafer placement and attach, and dicing. In addition, wafer-to-wafer attach, dicing and de-bonding will also be demonstrated. Cost of ownership goal for the integrated 3D process is \$200usd per wafer.

#### EMC3D (or EMC<sup>3D</sup>)

Semiconductor 3-D Equipment and Materials Consortium

#### Mission

Develop/demonstrate a cost-effective TSV interconnect technology (unit processes + integration) and provide manufacturable processes, equipment, and materials.

Micro Machining Systems

### **Materials**

enthone

able

**Board Members**

brewer science

wafer service Ecole Polytechnique Paris - 3D Technical Symposium; November 2007

### Technology

Fraunhofer Institut Zuverlässigkeit und Mikrointegration

SAMSUNG ADVANCED INSTITUTE OF TECHNOLOGY

#### Board Members' Technologies

Page8

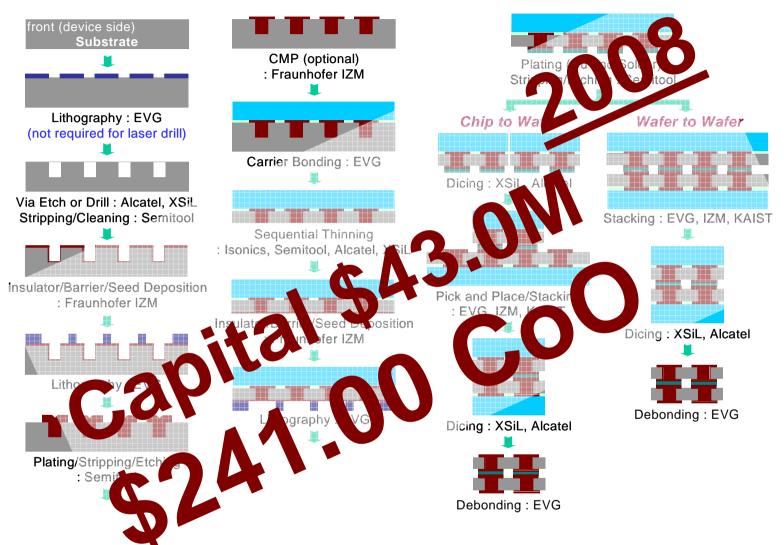

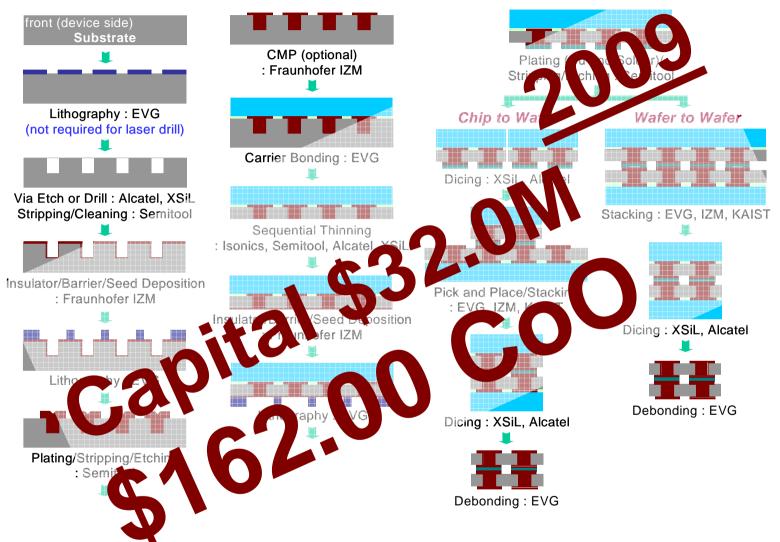

#### EMC-3D Process and Equipment Flow

We are considering both via-first and via-last approaches (start with via-first approach). This process flow is not for licensing, but is an example of process and equipment flow for demonstrating chip integration with consortium members' technologies.

#### **First Year**

Develop unit processes and demonstrate integration (or stackability) of via-first TSV technology on 200mm wafers with CoO  $\approx$  400-500usd per wafer.

#### **Second Year**

Demonstrate integration and reliability of TSV technology (via-first or via-last depending upon technology trends) on 200mm wafers with CoO  $\leq$  300usd per wafer.

#### **Third Year**

Demonstrate seamless integration and reliability of TSV technology (via-first or via-last depending upon technology trends) on 300mm wafers with CoO  $\leq$  200usd per wafer.

# Contents

- EMC<sup>3D</sup> Introduction (Brief)

- Packaging and Interconnects

Common Challenges/ Interests

- Challenges of Interconnects

- Direction of Packaging

- 'Fusion' Era

- Enabling Technologies

- 3D CoO The ultimate driver

- Summary

### **Global Activities in 3D Integration**

### Is TSV 3D-IC Manufacturable?

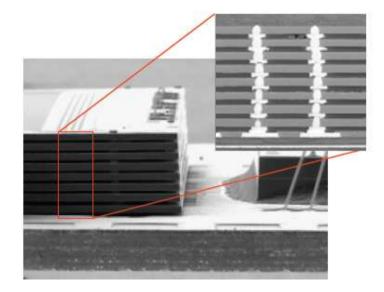

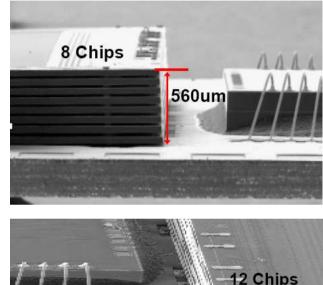

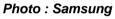

#### Samsung's WSP

Source : Samsung Electronics

# 12 Chips 840um

#### Announced on April 2006

WSP (wafer-level processed stack package) with TSV interconnects

Semiconnuctor 3-D Equipment and Materiais Consortium

# Contents

- EMC<sup>3D</sup> Introduction (Brief)

- Packaging and Interconnects Common Challenges/ Interests

- Challenges of Interconnects

- Direction of Packaging

- 'Fusion' Era

- Enabling Technologies

- 3D CoO The ultimate driver

- Summary

### **Challenges of advanced interconnects**

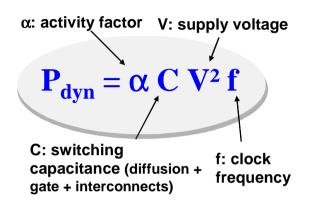

• Today, More than 50% of dynamic power consumption is due to interconnects. This rate is projected to increase.

[Nir Magen et al, Proc. of the 2004 international workshop on System level interconnect prediction, France, pp 7-13, 2004]

• Global Interconnect length doesn't scale with transistors and local wires. Because of functionality increase, chip size remains relatively constant.

[Havemann et al., IEEE, Vol. 89 (5), May 2001]

• RC delay is increasing exponentially. For 65nm node, RC delay in 1mm global wire at minimum pitch is ~100 times higher than NMOSFET intrinsic delay [ITRS07].

[ITRS 2007]

### Logic (Processor with cache memory)

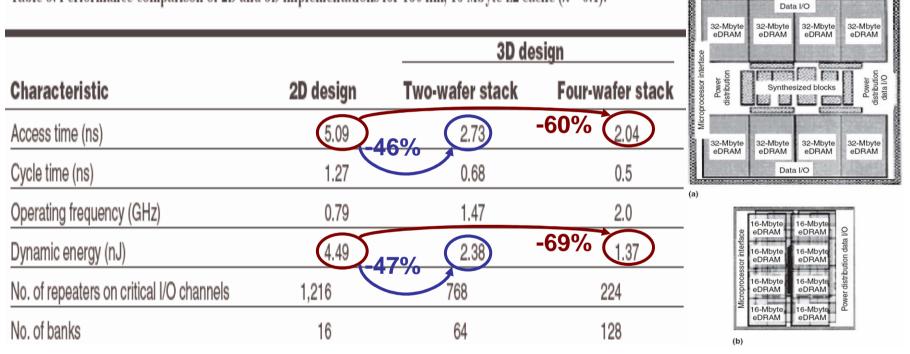

Processor with cache memory : Example of 16-Mbyte SRAM cache design (*Rensselaer Polytechnic Institute*)

Table 5. Performance comparison of 2D and 3D implementations for 130-nm, 16-Mbyte L2 cache ( $\lambda = 0.1$ ).

A. Zeng, J. Lü, K. Rose, and R. Gutmann (Rensselaer Polytechnic Institute), IEEE Design & Test of Computers, 2005, pp. 548-555

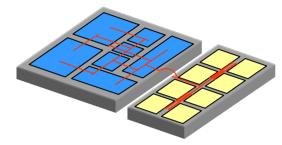

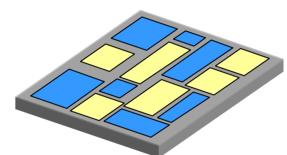

Ecole Polytechnique Paris - 3D Technical Symposium; November 2007 IC floorplan of graphics rendering processor with 256-Mbit eDRAM: 2D (a) and 3D (b).

#### **2D interconnect:**

- Large form factor

- Long lines / shared bus

#### 3.8mm X 2.9mm

#### SOC solution:

- Reduced system size

- Increased performance

- Increased device cost

#### 3D stack:

- Reduced system size

- Short interconnects

- Reduced packaging cost

| 15%       | Size Reduction |

|-----------|----------------|

| 30%       | Power/signal   |

|           | Improvement    |

| <b>5%</b> | Cost Increase  |

Why 3-D?

"More than MOORE"

35% Size Reduction

40% Power/signal Improvement

45% Cost Reduction

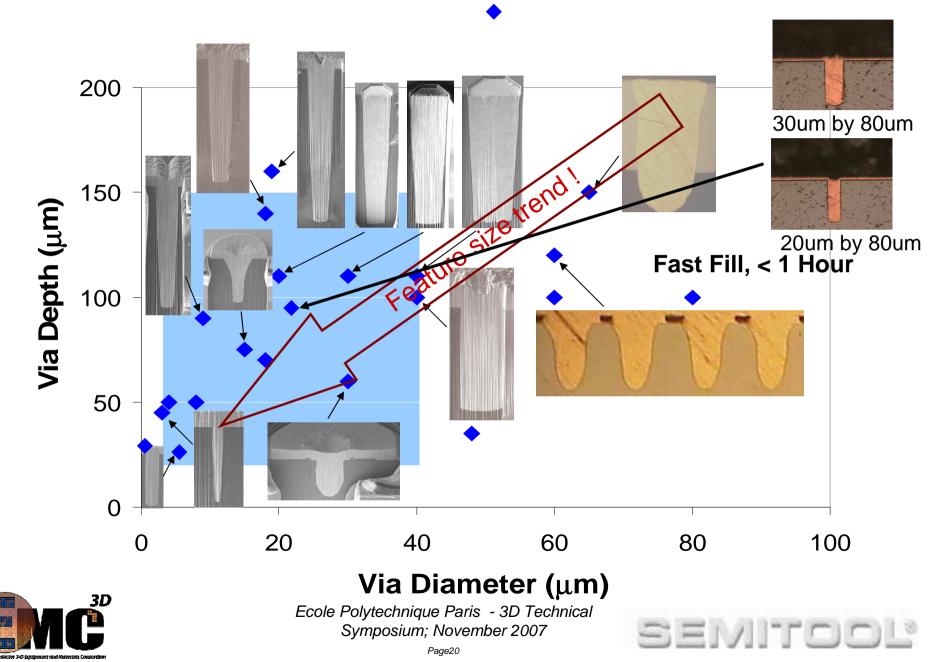

#### **Void-free Filling at Optimized Conditions**

# "Fusion Era"

- "We are at the doorstep of the largest shift in the semiconductor industry ever, one that will dwarf the PC and even the consumer electronics eras"

- "The core element needed to usher in the new age will be a complex integration of different types of devices such as memory, logic, sensor, processor and software, together with new materials, and advanced die stack technologies, ... all based on 3D silicon technology"

Dr. Chang-Gyu Hwang, president-CEO, Samsung Semiconductor, IEDM conference, Dec. 2006

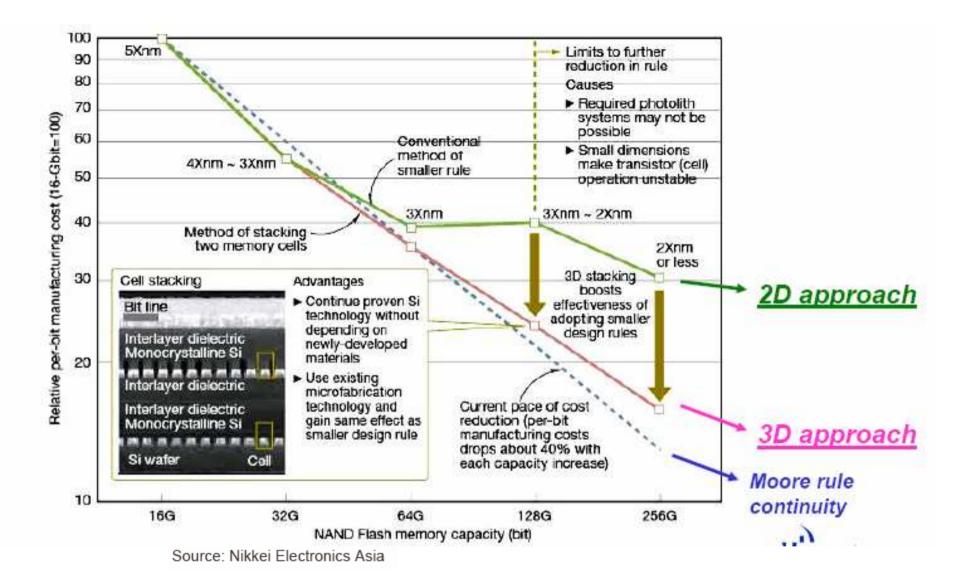

#### At flash capacity >64 Gb, expect to see a big cost differential between 2D and 3D

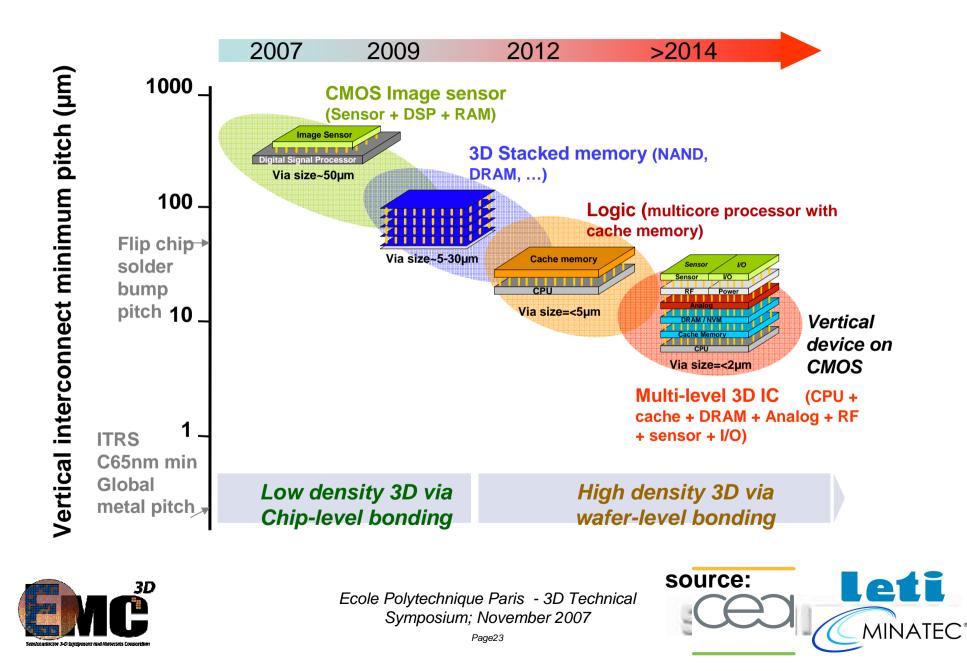

### **Applications of 3D Si integration**

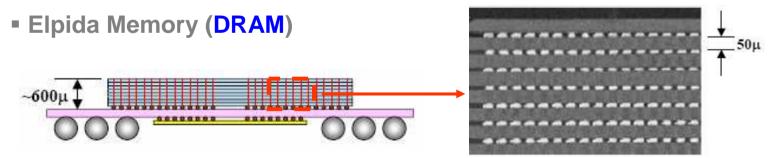

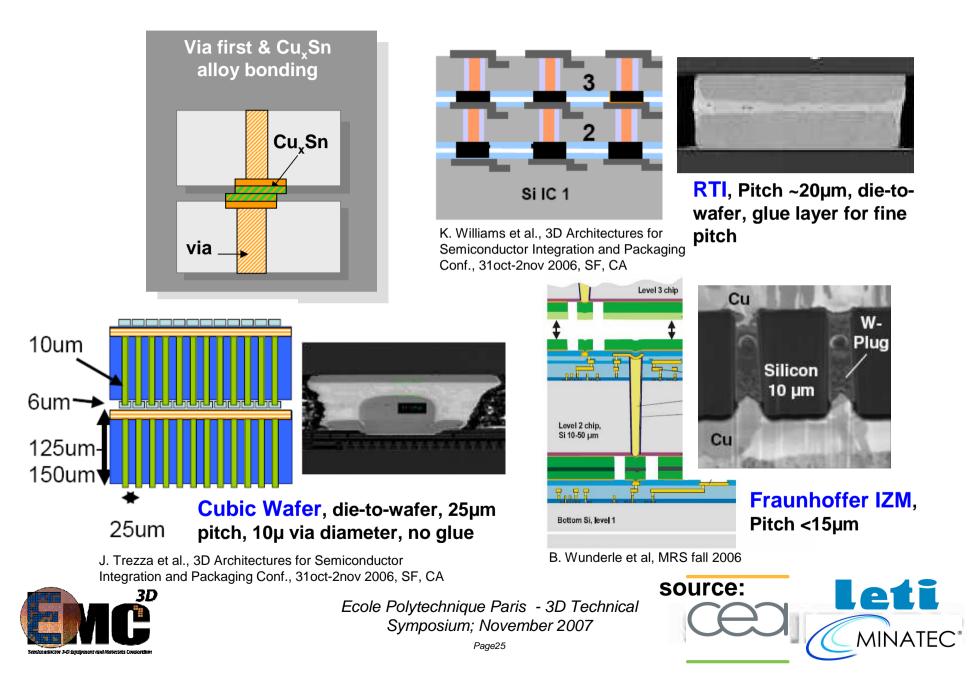

# **Memories (Flash and DRAM)**

Samsung (NAND)

K. Lee (Samsung), Conference on 3D Architectures for Semiconductor Integration and Packaging, 31oct-2nov 2006, SF, CA

Photo : Samsung

- Through Silicon Via Formation (~ 30µm diameter) : Laser Drill, Electroplating Via Filling

- Die-to-die bonding : micro-bump bonding

- Wafer Thinning : ~ 50µm

Photo: Elpida memory

H. Ikeda (Elpida Memory, Inc.); Conference on 3D Architectures for Semiconductor Integration and Packaging, 31oct-2nov 2006, SF, CA

### Via first & CuxSn bonding (w/ or w/o glue)

### Via first & Cu thermo-compression (w/ or w/o glue)

Page26

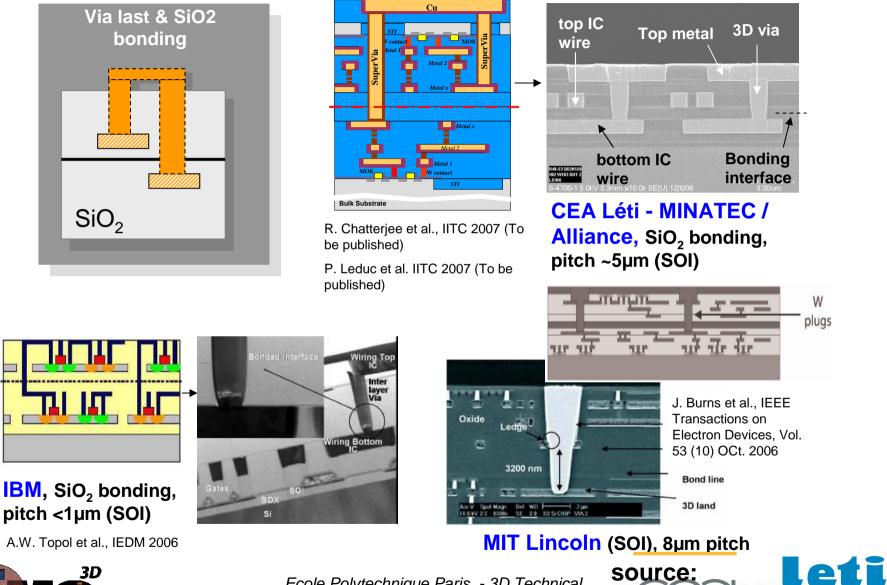

### SiO2 bonding & via last

**MINATEC®**

Ecole Polytechnique Paris - 3D Technical Symposium; November 2007

Page27

# Contents

- EMC<sup>3D</sup> Introduction (Brief)

- Packaging and Interconnects Common Challenges/ Interests

- Challenges of Interconnects

- Direction of Packaging

- 'Fusion' Era

- Enabling Technologies

- 3D CoO The ultimate driver

- Summary

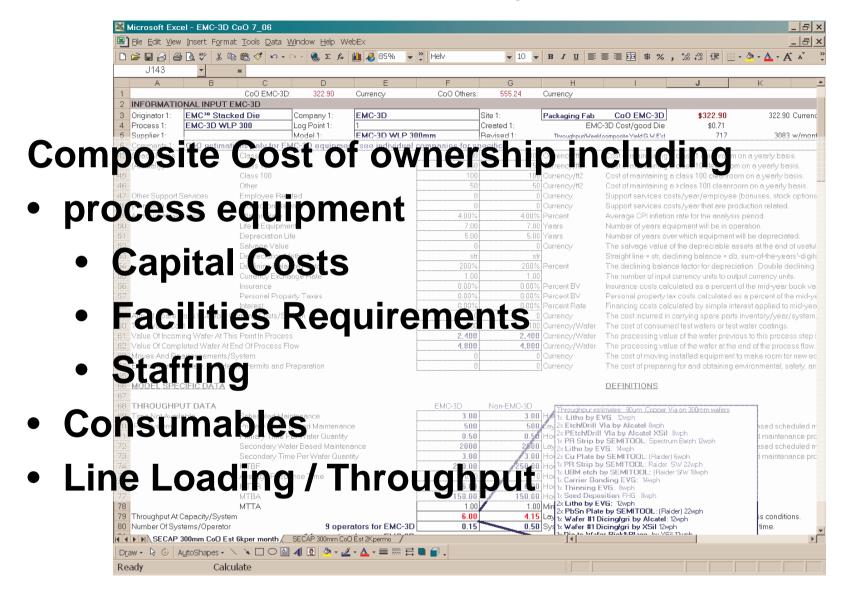

### CoO by SEMATECH's Model

### **2007 CoO Expectation**

#### <u>3,500 wafers/month – 200mm</u>

### **2008 CoO Expectation**

#### <u>3,500 wafers/month – 200mm</u>

### **2009 CoO Expectation**

#### <u>3,500 wafers/month – 300mm</u>

# **CLEAR Objective :**

# Integrated and Cost-Effective Cu TSV for < \$200/wafer by Year 2009

www.emc3d.org

Ecole Polytechnique Paris - 3D Technical Symposium; November 2007

Page33

# Acknowledgements

- Barbara Charlet, Mark Scannell & David Henry CEA/LETI Juergen Wolf, Peter Ramm Fraunhofer IZM • Dr. Christo Bojkov & Dr. Manuel Soriaga Texas A&M • Michel Puech and Hind Beaujon Alcatel • Tom Ritzdorf, Charles Sharbono & Rozalia Beica SEMITOOL • Markus Wimplinger and Paul Kettner EV Group Delphine Perrottet, Dr Aleksej M. Rodin XSII Suk-Jin Ham, Yoon-Chul Sohn SAMSUNG • Dr. Kyung W. Paik KAIST • Dr. Vaidyanathan Kripesh; IME, Singapore Dr. Fred Roozeboom and Eric van Grunsven NXP • Stephen Christian, Bob Forman Rohm & Haas • Yun Zhang, Bioh Kim Enthone Georg Pawlowski, C. Chen **AZ** Electronic

- Paul Harris

- Wilfried Bair

- Jean-Christophe

**Brewer Science** Ziptronix Yole Développement

# Working together to enable low cost thru-silicon-via interconnection.