# Void-Free Cu Filling within High Aspect Ratio TSVs

Tom Ritzdorf and Charles Sharbono Semitool, Inc.

EMC-3D Japan/Korea Technical Symposium April 23-27, 2007

#### **Outlines**

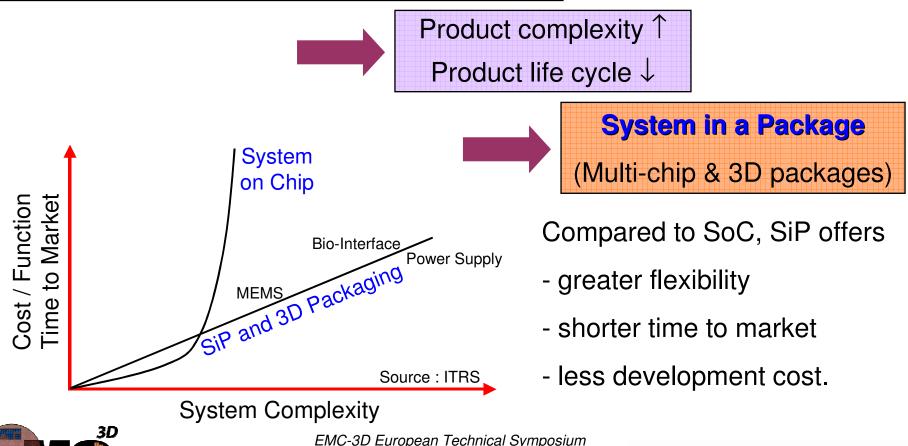

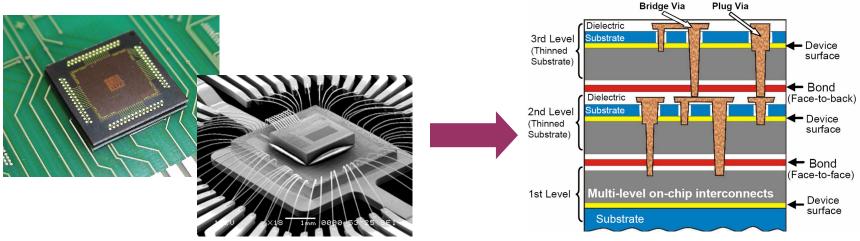

SiP and 3D Packaging

Through-Silicon-Via (TSV) Chip Integration

**TSV Copper Filling**

ECD fill mechanism

Factors affecting filling profiles

Void-free filling at optimized conditions

Conclusions

#### **Demands from Consumer Electronics Market**

Size, Weight, Cost, and Power ↓

Features and Functionality ↑

Incorporation of other circuit elements (MEMS, opto-electronics, and bio-electronics)

# **SIP Technologies**

| Chip / Component<br>Configuration | Technology Source : ITRS                                                                                                                                              |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Side by Side<br>Placement         | Substrate: organic laminate, ceramic, glass, silicon, leadframe Chip Interconnection: wire bond and/or flip chip + passive components — integrated into the substrate |

|                                   | discrete (CSP, SMD)                                                                                                                                                   |

| Stacked<br>Structure              | Stacked Die — wire bond, WB+FC Chip to Chip / Wafer — flip chip, face to face through silicon WL 3D stack wafer to wafer (W2W)                                        |

| Embedded<br>Structure             | Chip in PCB / Polymer — single layer  multi-layer 3D stack  WL Thin Chip Integration — single layer  stacked functional layers                                        |

Need strategies and solutions for test, yield, and rework.

#### **Benefits of TSV Integration**

TSV electrodes can provide vertical connections that are both the shortest and the most plentiful.

Connection length ≈ chip thickness

High density, high aspect ratio, and small pitch connections

RC delays and power consumption are reduced

Therefore, TSV interconnection can overcome the limitations of typical SiP methods.

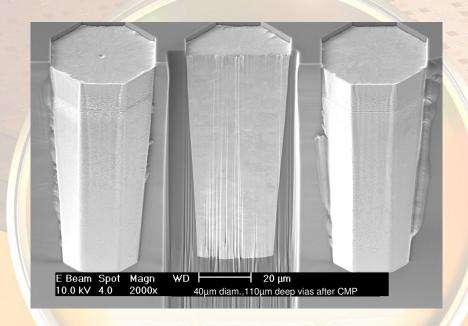

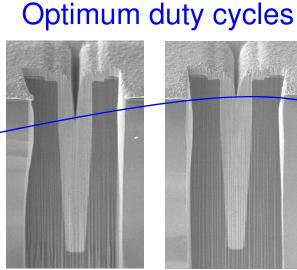

# **Void-free Filling at Optimized Conditions**

EMC-3D European Technical Symposium June 25-29, 2007

#### **Requirements for TSV Integration**

Robust and precise thinning process flow

Handling concepts for a thin wafer

Electrical interconnects through a thinned wafer

Via etch: shape, angle, and scallop control

Insulator/Barrier/Seed: conformality and adhesion control

Copper fill: fill robustness and speed control

Metal removal: surface smoothness and over-polish control

Suitable bonding process: alignment, bonding, and dicing

Need cooperation with industrial leaders in equipment, materials, and technology.

Semiconductor 3-D Equipment and Materials Consortium

#### **Various TSV Filling Methodologies**

Source: Fraunhofer-IZM

CVD W, Cu, or Poly-Si

Source: IMEC

Conductive Polymer or Conformal Cu/Polymer

High purity

Low resistivity

No size/shape limitation

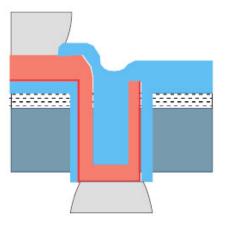

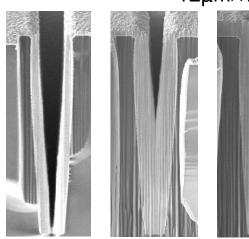

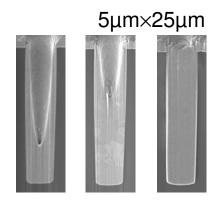

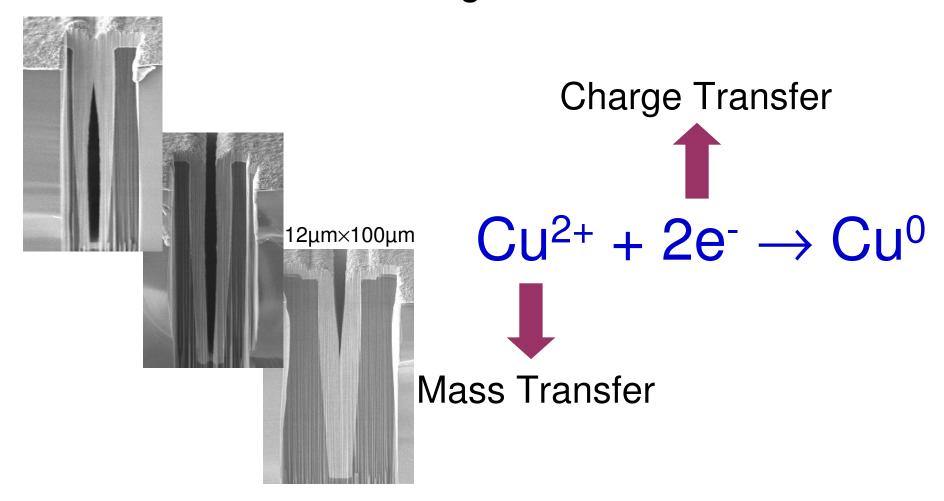

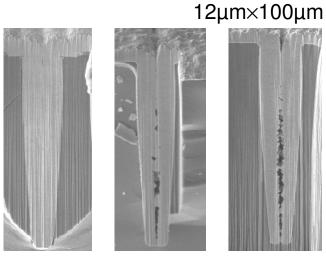

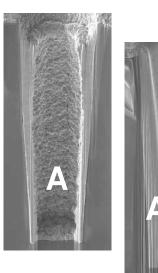

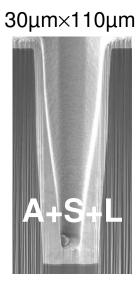

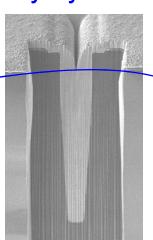

## **Void-free Filling with Various Dimensions**

$40\mu m\!\!\times\!\!100\mu m$

$12\mu m{\times}100\mu m$

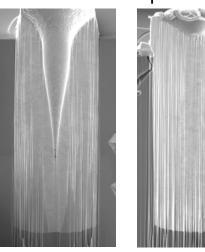

## **Prerequisites**

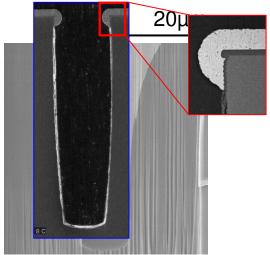

## **Seed Continuity**

#### **Surface Wetting**

$50\mu m{\times}225\mu m$

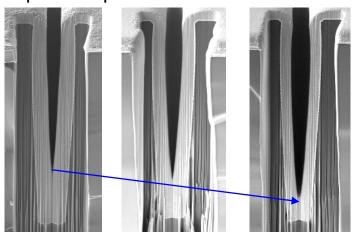

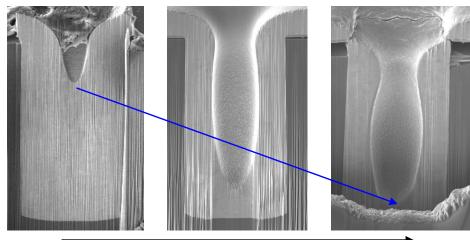

#### **Via Filling Profiles**

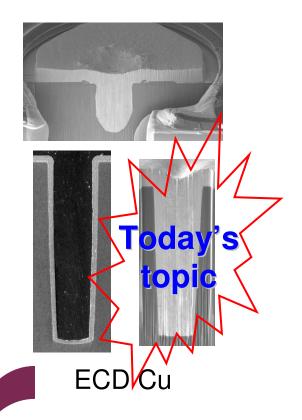

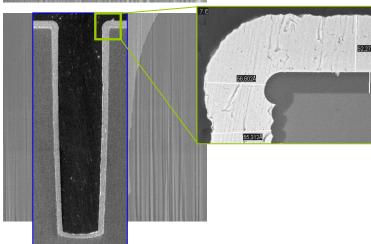

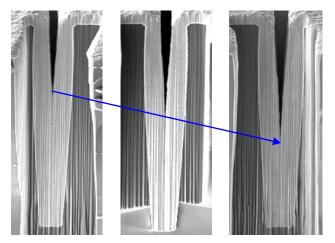

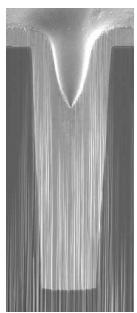

Void formation mechanism: Higher deposition rate near the via mouth due to faster charge and mass transfer, causing pinch-off

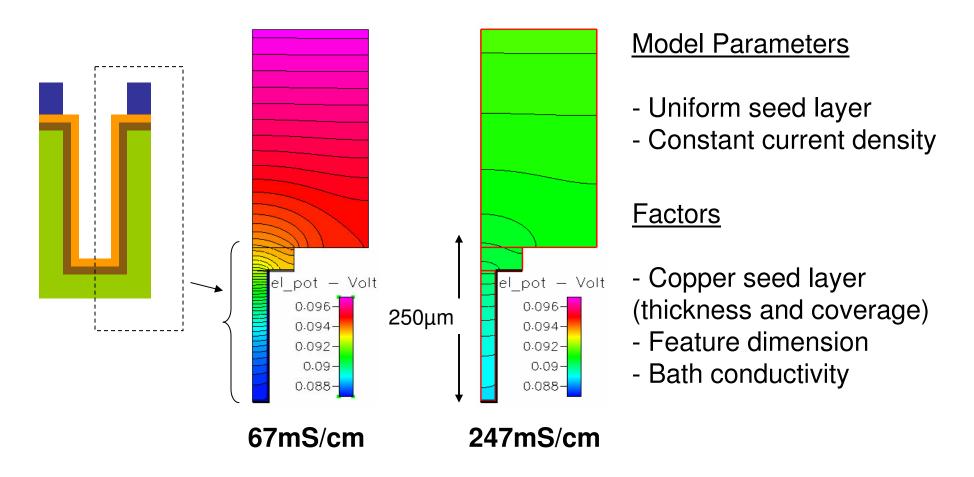

#### Potential Variation through a High AR Via

Additive adsorption/desorption behavior is also dependent on local potential.

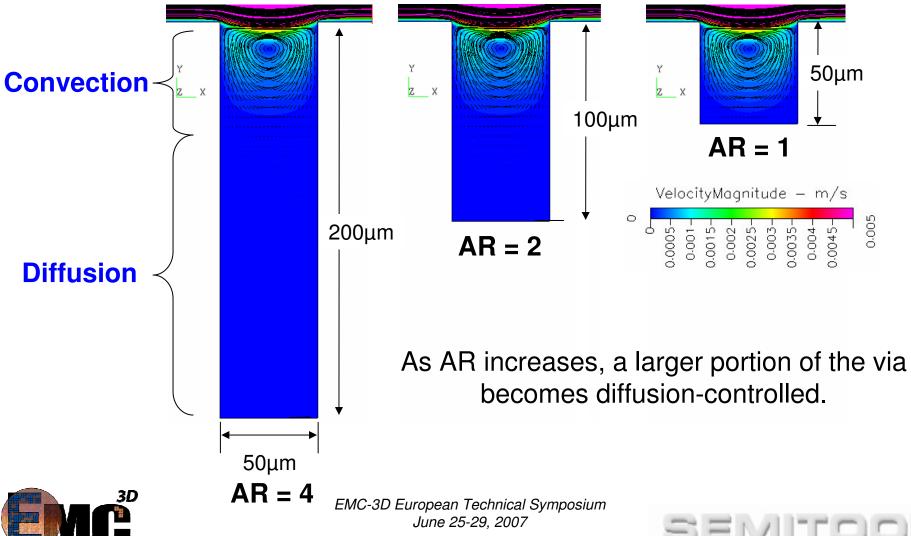

#### Mass Transfer in a High AR Via

Model Conditions: Steady state model fluid velocity, 50µm via diameter Constant fluid velocity across feature top

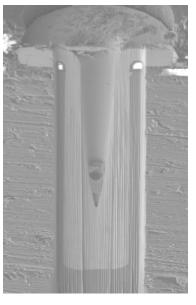

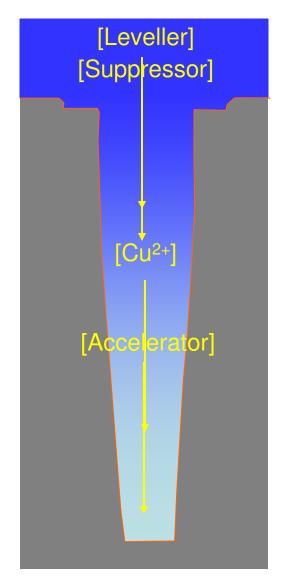

#### Via Filling Mechanism

#### How to Achieve Void-free Filling?

#### **Prerequisites**

Seed conformality for uniform charge transfer

Surface wetting for proper mass transfer

Reduce current crowding at the via mouth

Waveform

Bath composition

Reduce mass transfer limitation at the via bottom

Bath LCD

Flow mechanism

Impact of

current density?

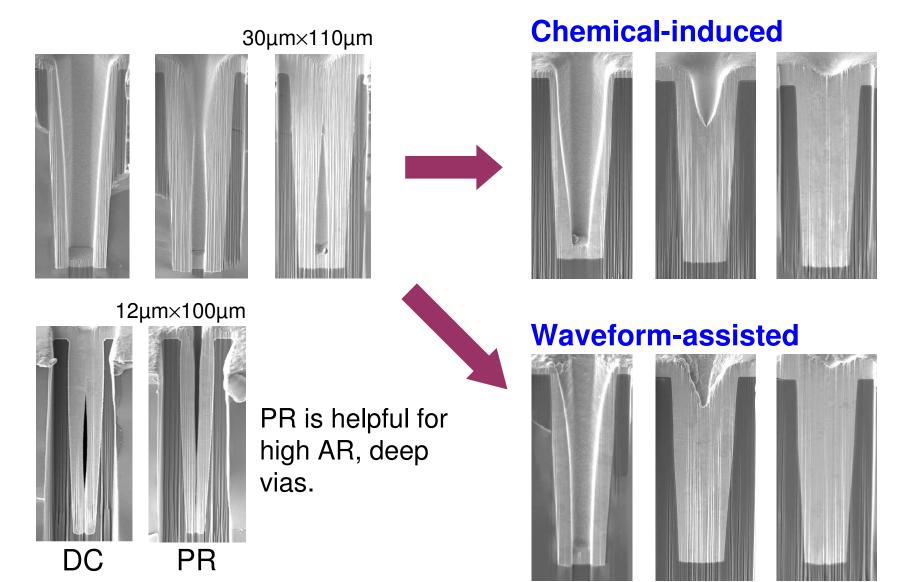

#### **Reduce Current Crowding at Via Mouth**

EMC-3D European Technical Symposium June 25-29, 2007

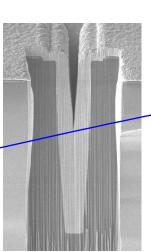

#### Reduced Current Crowding at Via Mouth: Chemical-induced

Increasing accelerator conc.

Increasing suppressor conc.

EMC-3D European Technical Symposium June 25-29, 2007

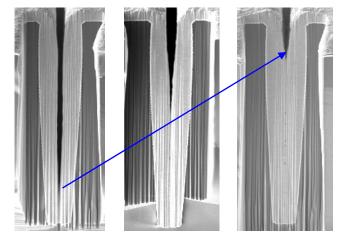

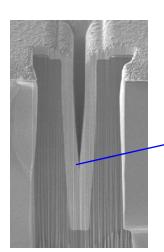

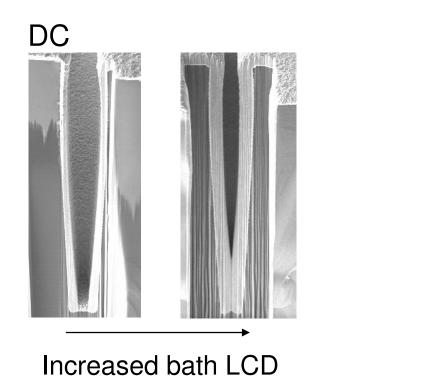

#### Reduced Current Crowding at Via Mouth: Waveform-assisted

DC

At a fixed amp-time and bath composition

PR

PR cycle time

#### Reduced Mass Transfer Limitation at Via Bottom

Bath LCD: A higher LCD bath is preferred.

Flow Mechanism: The ion transport within deep vias may not be substantially enhanced by the increased convection. But, a strong flow mechanism is still required for better transfer of organic components.

#### **Current Density Effect**

$12\mu m \times 100\mu m$

$40\mu m{\times}100\mu m$

Increasing Current Density

Increases current crowding at the via mouth

Approaches mass transfer limit at the via bottom

Reduces deposit within the via

**Current Density**

EMC-3D European Technical Symposium June 25-29, 2007

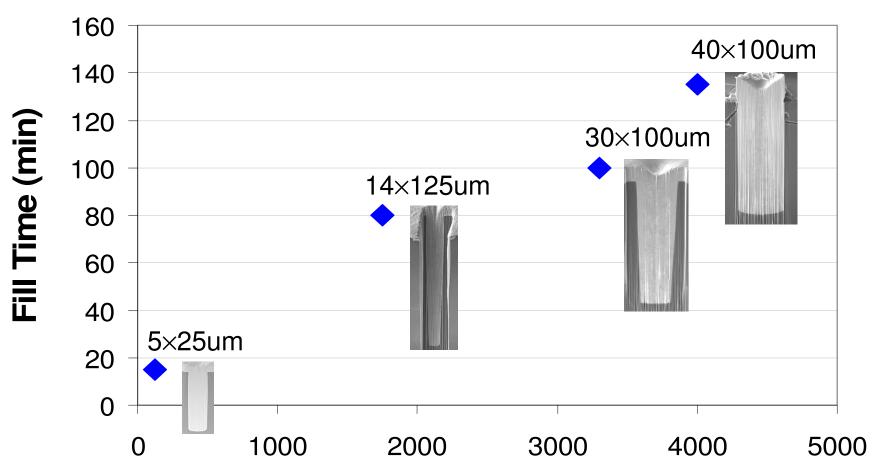

#### **Feature Dimension vs. Filling Time**

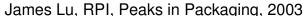

#### Why is Smaller Feature Dimension preferred?

# Feature Cross-Sectional Area (µm²)

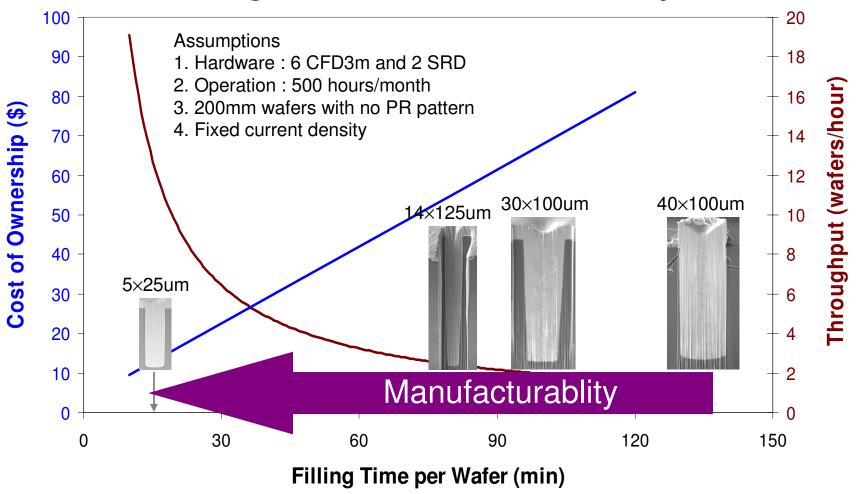

## Filling Time vs. Manufacturability

Actual throughput & CoO varies with tool configuration and process conditions. Resist pattern plating will have better overall cost of ownership.

#### **Summary**

Copper filling process with robustness and speed is among the most important to make TSV interconnection manufacturable.

Surface wettability Prerequisites for proper mass transfer Seed conformality and current distribution

Bath composition

Waveform and current density

Flow conditions

Reduce current crowding at the via mouth

Void-free Bottom-up Filling