## DRD7 activities

-few selected topics-

November 27<sup>th</sup>, 2025

Marlon Barbero, CPPM (with many slides borrowed from: <a href="https://indico.cern.ch/event/1556239">https://indico.cern.ch/event/1556239</a>)

5<sup>th</sup> FCC / DRD France workshop

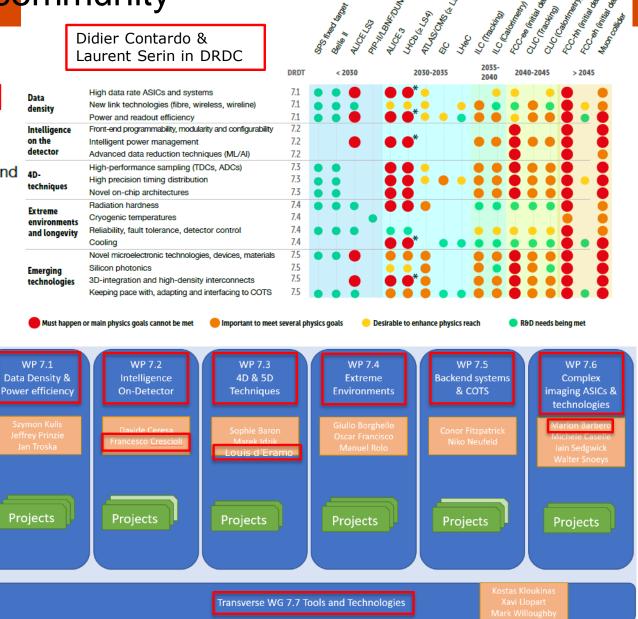

## DRD 7 goals & french community

## DRD7: Electronique

Electronics

DRDT 7.1 Advance technologies to deal with greatly increased data density

**DRDT 7.2** Develop technologies for increased intelligence on the detector

**DRDT 7.3** Develop technologies in support of 4D- and 5D-techniques

DRDT 7.4 Develop novel technologies to cope with extreme environments and required longevity

DRDT 7.5 Evaluate and adapt to emerging electronics and data processing technologies

Goals: Follow strategic R&Ds in electronics, support access to technologies, tools and knowledge, and aim for the DRDT.

DRD7 is transverse by design, supports to other DRDs → Can sometime be at the interface to other DRDs.

DRD7 proposal 2024 → DRD7 approval June 5th 2024

Last workshop: Sept 2025

https://indico.cern.ch/event/1556239

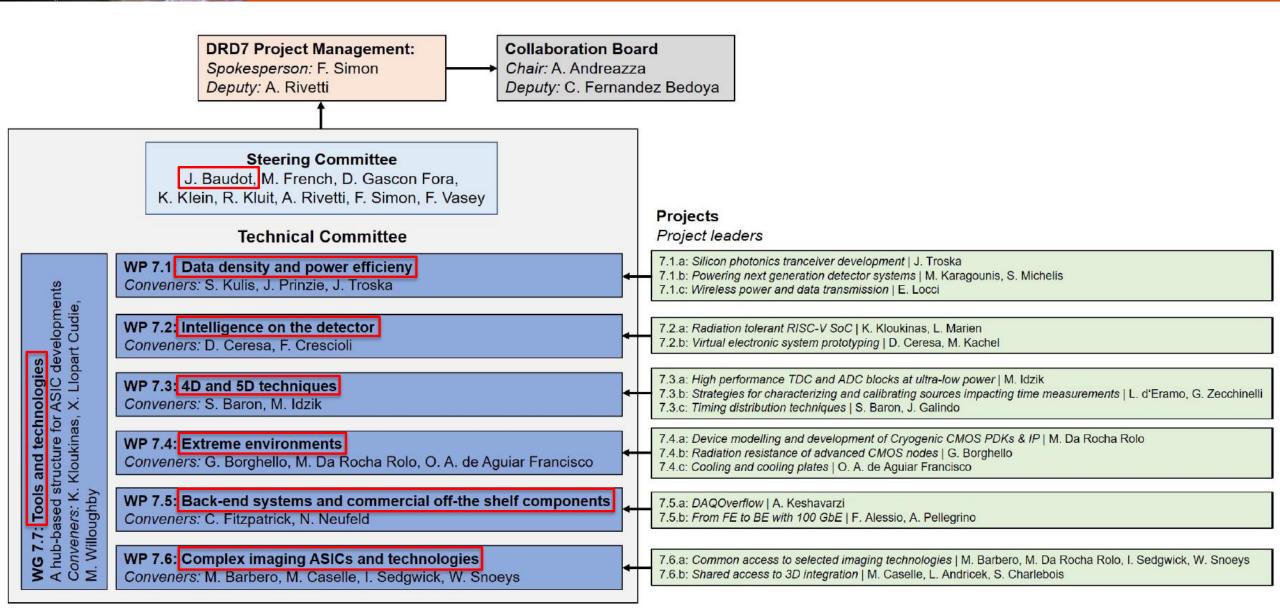

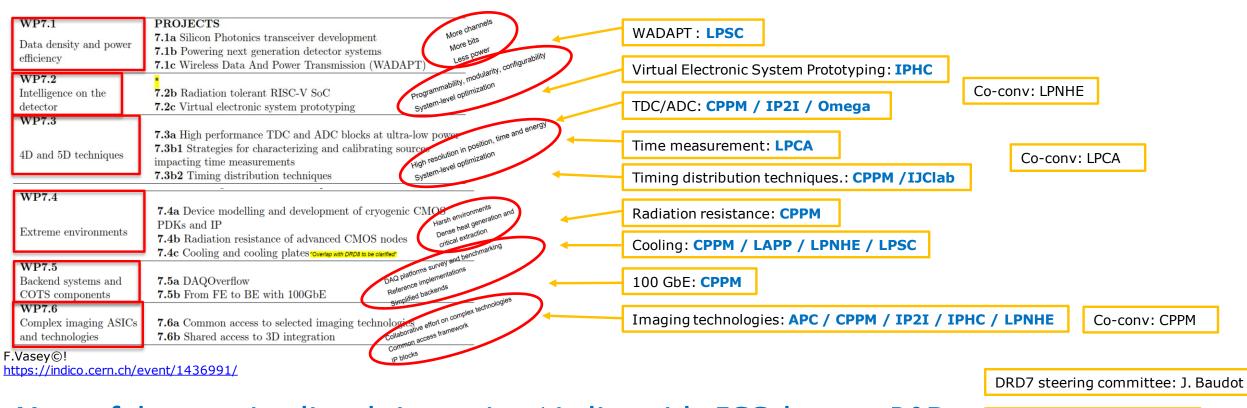

## DRD 7: WP organisation

## DRD 7: WP1 -> Data Density and Power Efficiency

# 7.1.a: Silicon Photonics Transceiver Development

Develop high-speed optical transceivers based on Silicon Photonics technology for use in a wide range of future particle physics applications from low-temperature neutrino detectors to high-radiation environment HL-HLC pixel detectors.

Project Leader: Jan Troska, CERN

# 7.1.b: Powering Next Generation Detector Systems

Develop power distribution schemes and their voltage/current regulators and converters for use in a wide range of future particle physics applications, from low-temperature neutrino detectors to high-radiation environment HL-HLC pixel detectors and beyond.

Project Leaders: Michael Karagounis, FH Dortmund and Stefano Michelis, CERN

# 7.1.c: WADAPT Wireless links and free-space optics

Develop wireless technology based on a millimeter wave transceiver IC as well as on Free Space Optics to connect neighboring detector layers, providing increased data rates, high power efficiency and high density of data links, with the aim of reducing mass and power consumption.

Project Leader: Elizabeth Locci, DGIST

> WP convenors: Szymon Kulis, CERN Jeffrey Prinzie, KUL Jan Troska, CERN

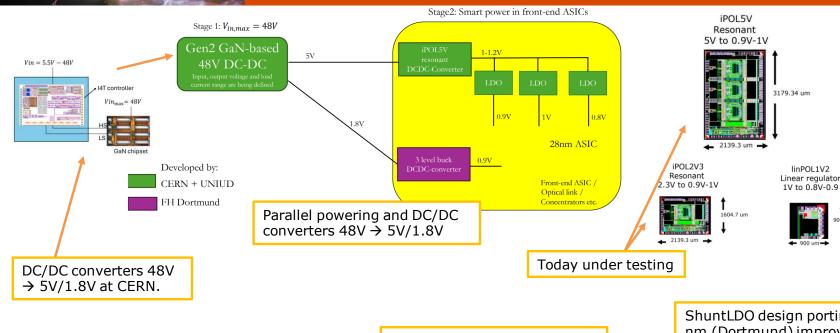

## DRD 7: WP1b Powering

#### DC/DC Conversion

- GaN converter 48V -> 5V conversion (CERN)

- GaN converter 48V -> 2.5V conversion (Taltech)

- Fully integrated resonant 28nm 5V -> 0.9V (CERN)

- FCML with external air coil 28nm 5V -> 0.9V (FH Dortmund)

- GaN converter characterization (RWTH Aachen)

#### **Serial Powering**

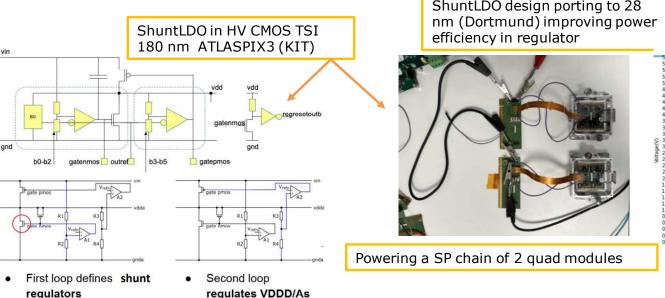

- 28 nm porting of SLDO (FH Dortmund)

- High-Efficiency switch-mode SLDO (FH Dortmund)

- GaN Constant Current Source (ITANNOVA)

- Serial Power Pixel Modules (MILANO)

CERN – Stefano Michelis, Marta Macaluso, Antonio Ocarino, Sokratis Koseoglou

FH Dortmund - Jeremias Kampkötter, Hossein Tavakoli, Michael Karagounis

ITANNOVA - Fernando Arteche, Alvaro Pradas

University of Milano and INFN - Attilio Andreazza, Attilio Andreazza, Massimo Lazzaroni, Fabrizio Sabatini, Riccardo Zanzottera

RTWH Aachen - Lutz Feld, Katja Klein, Martin Lipinski, Joëlle Savelberg

TALTECH - Abdul Majid Bhat, Dr. Andrii Chub, Prof. Dmitri Vinnikov

## DRD 7: WP1b Powering many activities

M.Karagounis©!

Pass-Device

**Shunt Tranistor**

Input Voltage

1,0

0,5

starts regulating

1,5

1,0

0,5

- VDDA W6\_40

→ VDDD W6\_40 - VDDA W6\_28

- VDDD W6 28 - VDDA W6\_29

VDDD W6 29

**Output Voltage**

2-chip module

starts regulating

Input Current [A]

ShuntLDO design porting to 28 nm (Dortmund) improving power efficiency in regulator

Version ATLASPix3.1 has possibility for serial powering through two shunt/low dropout regulators

- digital and analog (VDDD/A)

- 3 bits to tune threshold of shunt regulator

- 3 bits to tune VDD

- gatenmos, outref, gatepmos are for monitoring

- o regresetoutb can be used as power on reset

Possibility to use a single power supply for all the 6 alimentation needed to operate the chips

DRD7 activities 5th FCC / DRD France ws

Very active DC/DC serial powering activites within 7.1b

## DRD 7 : WP2 → Intelligence on Detector

Two projects and one group of interest:

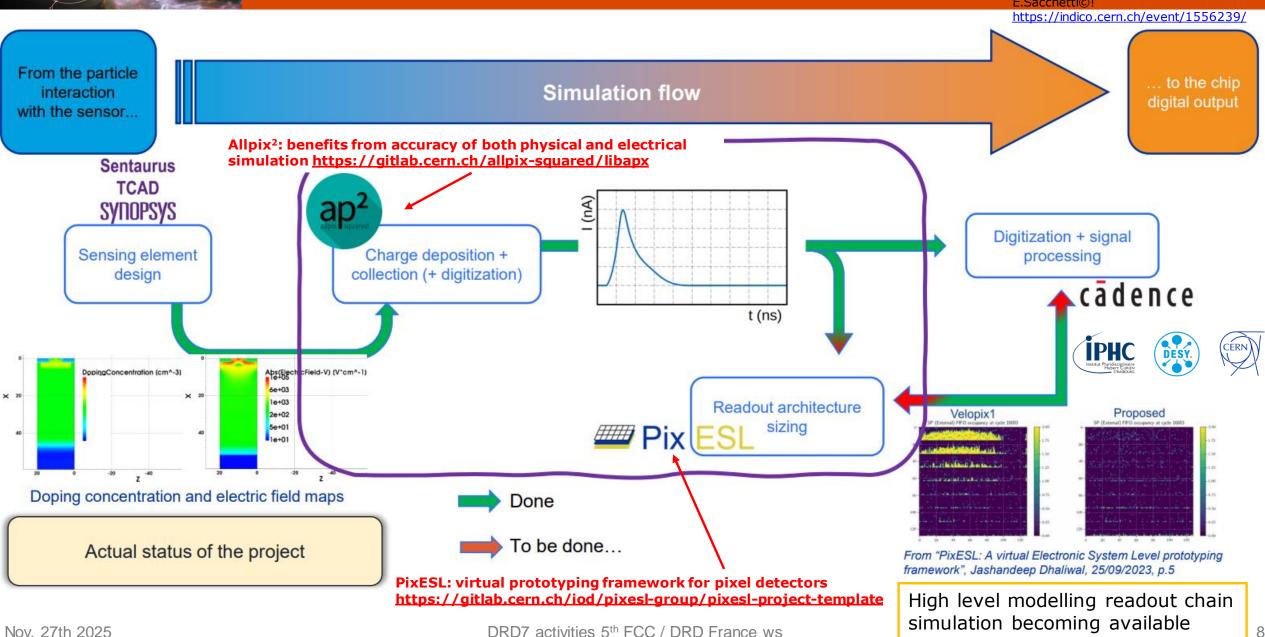

7.2ca: Virtual Electronic System Prototyping

Project Leaders: Davide Ceresa, CERN and Maciej Kachel, IPHC

7.2b: Radiation Tolerant RISC-V System-On-Chip

Project Leaders: Kostas Kloukinas, CERN and Levi Marien, KU Leuven

Conveners: Davide Ceresa and Francesco Crescioli

7.2c (not started and not in MoU): Radiation Tolerant Embedded FPGA (eFPGA)

####

The project aims to develop a simulation of the readout chain of a particle detector at a high level modelling the essential components and processes that occur from the moment particles interact with the detector to the digital readout of the collected data.

## DRD 7: WP2a -> Virtual Electronic System Prototyping

DRD7 activities 5th FCC / DRD France ws

## DRD 7 : WP3 → 4D & 5D techniques

| Number | Title                                                                                         | Description                                                                                                                                      | Start date | End date |

|--------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------|

| D7.3a  | High performance<br>TDC and ADC<br>blocks at ultra-low<br>power                               | Develop ultra-low power high performance TDC and ADC blocks for use in future particle physics experiments.                                      | Sep.24     | Jun.27   |

| D7.3b  | Strategies for<br>characterizing and<br>calibrating sources<br>impacting time<br>measurements | Study and propose generic data-<br>driven calibration strategies for<br>the time measurements in<br>detectors requiring high<br>precision timing | Nov.24     | Jun.27   |

| D7.3c  | Timing Distribution<br>Techniques                                                             | Study and propose strategies to optimize and assess ultimate precision and determinism of timing distribution systems for future detectors.      | Mar.24     | Jun.27   |

- Many designs ongoing

- Various technologies

- Very promising results

- Progress on understanding impact of timing instabilities

- Portfolio of effects identified

- Practical tests started

- Better understanding on FPGAs performances

- Implementation of White Rabbit techniques on various platforms progressing

- First measurements with ASICs and PCs of generic solutions

#### https://indico.cem.ch/event/1556239/

#### DRD 7: WP3a $\rightarrow$ ADC & TDC

Slow control

PA +discri TOA TDC

A 8b 40M

#### EICROC0

- Preamp, discri taken from ATLAS ALTIROC

- I2C slow control taken from CMS HGCROC

- TOA TDC adapted by IRFU Saclay

- ADC adapted to 8bits by AGH Krakow

Digital readout : FIFO depth 8 (200 ns)

#### EICROC1: 32x32

- Goal test full scale analog performance

- Tests with sensor

Omega has been coordinating development of several readout ASICs:

CEA-IRFU 12b TDC assisted

- HGCROC collaboration with AGH, CEA, CERN, Imperial

- ALTIROC collaboration with AGH, CERN, LPCF, SLAC

SAR ADC

• HKROC - collaboration with AGH, CEA, CERN, Imperial

OMEGA: EICROC

# Pixel array SET RO-TID devices Ro-TID Ro-T

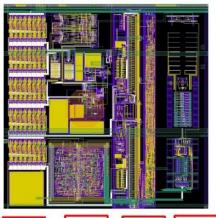

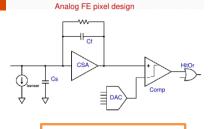

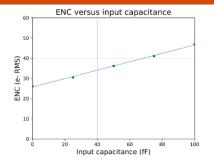

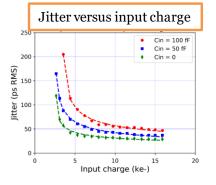

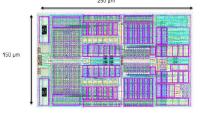

CPPM dvp in 28 nm

- Analog matrix in 28 nm technology:

- Pixel pitch 25 µm

- Gain charge/voltage: 95 mV / ke-

- 8 μW / analog pixel

- Threshold dispersion 130 e- RMS

- Noise 47 e- ENC (for Cdet = 100 fF)

- jitter < 50 ps rms for  $C_{in}$  = 100 fF (and approx. 37 ps when  $C_{in}$  = 50 fF)

- TDC to be added in next proto (2026)

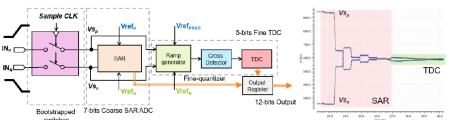

#### **SAR-TDC ADC**

#### Architecture of 12-bit ADC:

Differential split switching (fast dynamic comparator settling time) Asynchronous logic — no clock tree (low power)

ADC core layout :

s 10 μm Fine timing is needed for FCC-ee tracking and PID, as well as for Belle II and the LHCb UT, with a requirement of about 1 ns.

☐ To achieve this, we propose integrating a Time-to-Digital Converter (TDC) at the column level.  $\hfill\square$  The technology is a good candidate to achieve both spatial and time precision

☐ The main challenge is to find an acceptable compromise between

- tolerable power consumption (tbd),

- timing precision of the whole chain including: Sensor, Front End & Discriminator, column logic and TDC at the bottom of column (RefCLK also),

- and affordable area.

#### TDC concepts/candidates

FCCee trk & PID

≲ 100 ps

no

tbd

low

- TDC developed by SLAC: Vernier Delay Line (see Ariel Gustavo Schwartzman & Bojan Markovic 7.3a)

- Possible variants of TDCs developed by IP2I

- · Vernier Ring Oscillator with a Single Phase Detector

- Vernier R.O with a Multi-Phase Detector

- Vernier R.O with a Multi-Phase Detector

TDL (Tapped Delay Line) TDC

Submission of IP blocks in TPSCo65nm

MPR2, possibly ER3

☐ The target of our contribution to DRD7-3 is to provide a TDC with a time resolution of ≤ 20 ps RMS

- Not a stringent constraint to achieve a global timing resolution of ≤100 ps.

- The 20 ps resolution could be further improved depending on the sensor, FE, digital architecture, and clock precision).

IP2I plans for TDC in TPSCo 65 nm (part of MANTA project)

Lots of activities, joint ASIC designs ...

Nov. 27th 2025

## DRD 7: WP4 -> Extreme environnements & longevity

## Modelisation & developments of CMOS PDKs & IPs for cryogeny

Fermilab (US)

## Radiation hardness of advanced CMOS processes

Cooling

| Project Name                         | Device modelling and Development of Cryogenic CMOS PDKs                                                                                                                                                                                                                                                                                                                                                                                                       | Project Name                   | Radiation Resistance of Advanced CMOS Nodes (WP7.4b)                                                                                                                                                                                                                                                                                                                                       | Project Name                           | Cooling and cooling plates (WP7.4c)                                                                                                                                                                                                                                                                                                                                       |  |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Project Description                  | and IP (WP7.4a)  Device modelling from selected CMOS technology nodes, development of "cold" Process Design Kits (PDKs), design and characterisation of mixed-signal CMOS IP blocks and demonstrator chips for photon detection in (LAr, LXe) noble                                                                                                                                                                                                           | Project Description            | This project aims to evaluate the radiation response (total ionizing dose TID, single event effects SEE, and displacement damage DD) of commercial CMOS technologies more advanced than the 65nm node for use in the next generations of ASICs for particle detectors. Duration 4-5 years.                                                                                                 | Project Description                    | Development of the general purpose next generation of microchannels cooling structures to deliver excellent cooling performance, minimal material budget, and better electronics integration. Duration about 2+ years.  Better integration of electronics features to the cooling plates                                                                                  |  |

| Innovative/strategic                 | liquid experiments, quantum computing interface and sensing.  The aggregation of the international research teams will create the critical mass needed for the construction of infrastructures and tools, needed for device characterisation and modelling, towards the development of cold PDKs and cold-IP blocks.  These will be made available to a wider community working towards the construction of frontier particle and photon cryogenic detectors. | Innovative/strategic vision    | Understanding the effects of radiation on CMOS technologies is essential for the design of ASICs used in particle detectors. This project represents a first and crucial step in evaluating the performance of advanced CMOS nodes for the unique environment of particle detectors.                                                                                                       | Innovative/strategic vision            | especially in dense electronics applications. Better scalability considering alternative manufacturing techniques (more cost-effective). Thermal performance numerical simulation tools for new applications.  Different topics will explore different following parameters: page 100 DRD8 (y/cm²), material by the cost. Different topics will explore different topics. |  |

| Vision                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Performance Target             | Deepen the knowledge of the radiation response of 40nm and 28nm technologies and begin to study finFETs technologies.  D7.4b.1 (M12) Deliver a 28nm CMOS front-end (FE) circuits                                                                                                                                                                                                           | -<br>-                                 |                                                                                                                                                                                                                                                                                                                                                                           |  |

| Performance Target                   | cold PDK for a deep sub-micron CMOS technology, with<br>temperature corners at 165-87-77-4K, cold IP blocks<br>demonstrated on board of a multi-channel mixed-mode<br>demonstrator chip.                                                                                                                                                                                                                                                                      | Milestones and<br>Deliverables | for pixel sensors prototype; TID test of IP-blocks in 28nm node D7.4b.2 (M18) Deliver a chip in 28nm CMOS including matrices of FE channels for readout of pixel sensors M7.4b.3 (M24) Radiation test of FE structures; Design and testing of rad-hard memory elements in 28nm node D7.4b.4 (M36) Deliver a prototype in FinFET technology including IP blocks for pixel readout circuits. | Performance Target                     | experiments of their final application. The progress will be cracked via public reports in the form of presentations, public notes and/or papers.  D7.4c.3 (M15) Deliver a feasibility public note or paper (topic 3)  M7.4c.6 (M24) 3D printing public note or paper (topic 4) D7.4c.5 (M27) Deliver a report summarising fluidic and thermal                            |  |

| Milestones and Deliverables          | D7.4a.1 (M9) Deliever a specification and requirements document for a full-chip demonstrator. M7.4a.2 (M18) Cold-PDK for TSMC28nm complete M7.4a.3 (M26) Tapeout of full-demonstrator chip                                                                                                                                                                                                                                                                    | Denverables                    |                                                                                                                                                                                                                                                                                                                                                                                            | - Milestones and                       |                                                                                                                                                                                                                                                                                                                                                                           |  |

|                                      | D7.4a.4 (M38) Deliver a report of full-demonstrator silicon chip characterisation.  The availability of reliable device models and PDKs for                                                                                                                                                                                                                                                                                                                   | Multi-disciplinary,            | In order to ensure the success of projects involving ASIC design<br>for particle detectors, it is imperative to consider the radiation<br>resistance of the technologies used. On the other hand, the<br>definition of radiation qualification would greatly benefit from                                                                                                                  | Deliverables                           | tests of demonstrators public note or paper (topic 1) M7.4c.7 (M36) Bi-phase CO2 Thermo-fluidic models developed for microchannel, nuclear and annular flows, and thermal heat                                                                                                                                                                                            |  |

| Multi-disciplinary, cross-WP content | advanced CMOS technology nodes, qualified for operation at cryogenic temperatures, will pave the way for the development of cryo-qualified CMOS IP blocks suitable for integration on complex mixed-signal ASICs for DRD2 and DRD5.                                                                                                                                                                                                                           | cross-WP content               | the input of the designer. For example, ASICs developed in WP7.3a must be radiation tolerant and could also serve as valuable test vehicles to evaluate radiation effects.  CERN                                                                                                                                                                                                           | Multi-disciplinary, - cross-WP content | exchanger characterization and interconnection (topic 2).  Communication with DRD8 (Mechanics) and DRD3 (Semiconductor detectors) via liaisons and workshops (e. g.: Forum on tracking mechanics) and 7.6b project (common access                                                                                                                                         |  |

| Contributors                         | Graz University of Technology (Austria) University of Sherbrooke (Canada) Forschungszentrum Jülich (Germany) INFN (Italy) KEK (Japan) ICCUB, University of Barcelona (Spain) EPFL (Switzerland) RHUL (UK) University of Oxford (UK)                                                                                                                                                                                                                           | Contributors                   | AT: TU Graz<br>IT: INFN Pavia, Uni. Bergamo, Uni. Padova, Uni. Pavia<br>FR: CPPM                                                                                                                                                                                                                                                                                                           | Contributors                           | 3D and advanced integration) within the DRD7.  CA: Sherbrooke CERN DE: DESY                                                                                                                                                                                                                                                                                               |  |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                |                                                                                                                                                                                                                                                                                                                                                                                            |                                        | ES: IMB-CNM, IFIC-Valencia UK: Manchester FR: CPPM, LAPP, LEGI, LPNHE, LPSC                                                                                                                                                                                                                                                                                               |  |

|                                      | University of Oxford (UK)                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                |                                                                                                                                                                                                                                                                                                                                                                                            |                                        |                                                                                                                                                                                                                                                                                                                                                                           |  |

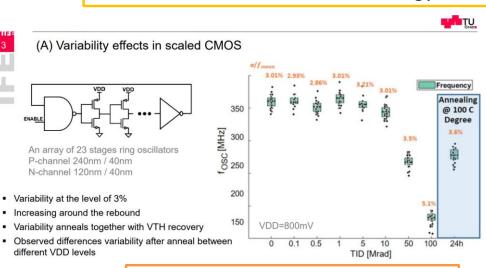

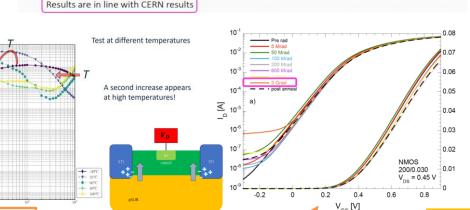

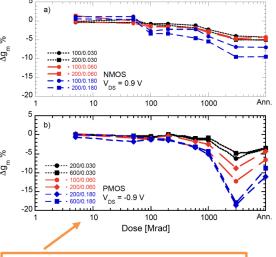

## DRD 7: WP4b -> Radiation Hardness

G. Borghello@!

Very active domain, some studies on 40 nm but main focus on 28 nm technology

Ring-Oscillator studies on 40 nm technology

### TID test results

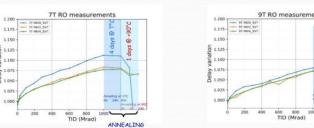

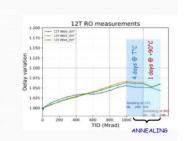

28 nm ring oscillator studies (HDR):

max 15% increase at 1 GRad

TID measurements have been done in close collaboration with Alicja from Graz institute - Austria

ANNEALING

- X-ray source for 1 week to reach 1 Grad

- Several days @room T°C

- At high temperature +90°C

Results show very good dose tolerance even at ambient temperature

Better tolerance than 65nm or 130nm

TID tests at room temperature show a delay increase of less than 15% up to 1 Grad

Max delay increase of ~15 % measured on 7T-NORO cells (min strength drive)

12T and 9T more tolerant than 7T

INV2 and INV4 have similar variation → same size for transistors are used

Results are in line with CERN results

Transconductance vs. Dose: short channel more resistant! (Pavia)

Practical question: methodology

at ultra high dose?

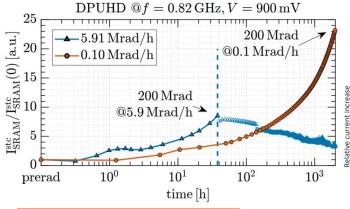

TID-induced leakage in pn junctions seen in 28nm DC-DC conv (CERN)

Nov. 27th 2025

28 nm: dose rate effect (CERN)

G. Traversi et al., Ionizing Radiation Effects of 3 Grad TID on Analog and Noise Performance of 28nm CMOS Technology, IEEE Transactions on Nuclear Science, 10.1109/TNS.2025.3542231

Id vs Vgs to 3 Grad (Pavia)

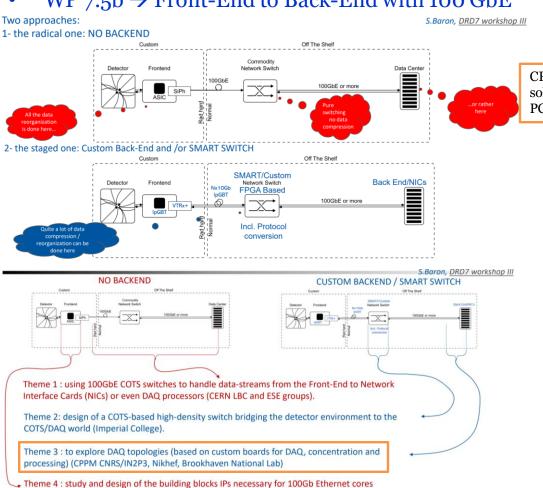

## DRD 7: WP5 -> Back End systems & COTS

#### WP 7.5a → common TDAQ developments with COTS

- Main focus on triggering with various hardware platforms (FPGA, CPU, GPU...)

- Sharing technological knowledge: soft/firmware framework, hardware devices, open-access git repository...

- WP 7.5b → Front-End to Back-End with 100 GbE

implementation in future FE ASICs. (Rutherford Lab)

CPPM uses existing BE board solution adaptation  $\rightarrow$  uses PCIe400 with 100 GbE links.

Develop «classical» approach with Back-End custom FPGA-based card (Intel version) – PCIe400

Two prototype boards received in December 2024

- 23 power rails satisfy DC level and ripple noise requirements

- Power supply sequence to power-up FPGA is OK

- Both FPGA programming paths, from JTAG and flash memory, are validated

- Low level control of board : over-heat protection, FPGA power cycle, reconfiguration is OK

- Access and configuration of all external peripherals has been validated

- PCIe interface slow control works on a PCIe Gen 3 server

A functional test suite performing over 400 measures using pytest developed and running

#### **Progress Report – BackEnd FPGA-based**

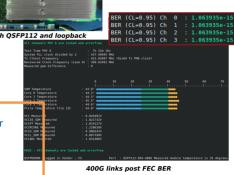

Agilex 7 F-tile transceiver has FHT interface with up to 116 Gbits/s PAM 4 links + 400GbE Hard IP provides physical and data link layer (PHY, MAC, FEC)

Challenging implementation between the FPGA and a QSFP112 cage over ~50 mm

Using Altera's PHY FEC RS(544,514) PRBS-31 external loopback

Error free post FEC during 7h BER of < 1e-15 with pre-corrected FEC BER < 2e-10

Opens the possibility to integrate a Network interface within the readout board Interface with a switch using 400GbE UDP

#### Next steps

- PCIe interface slow control and DMA access on Gen 4 and Gen 5 server

- Performance of the cooling solution

- Power supply ripple and transient noise at high FPGA logic occupation

- Front-end serial links at 10 and 25 Gbits/s

- Serial links at 100 Gbits/s

- Performance of the phase determinism of the Agilex 7 (synergies with DRD7.3)

- December 2026: Report on performance of lpGBT and phase determinism on PCle400 prototypes

- July 2028 : Delivery of a ~100 PCIe400 cards

## DRD 7: WP6a -> Access to selected imaging technologies

#### DRD 7.6a Goals:

Provide framework to facilitate access to complex imaging technologies / modified process through standard MPWs Support access to monolithic CMOS technologies

- TPSCo 65 / TJ 180 → Single pt of interface to foundries

- PDK support, design flow...

- MPW / ER organization

- Thinning & cutting

- Support IP development:

- Many IPs available or in development...

- Implication of French community mainly on 2 technologies:

- TJ 180nm, TPSco 65nm

#### Access through IPHC

IP dvps + link to DRD3 projects

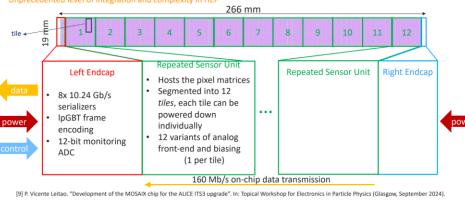

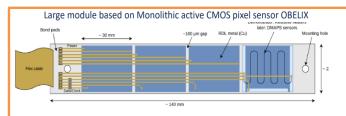

MOSAIX is the full-size, full-functionality, stitched sensor prototype for ALICE ITS3. 22.8 x 20.8 µm pixels. 9.97 Mpixels. MOSAIX inherits some of its features from MOSS (synchronous read-out, conservative layout) and MOST (power segmentation, data transmission on chip), but it includes many more complex functionalities. Attention to YIELD Unprecedented level of integration and complexity in HEP

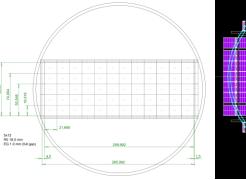

In ER2: MOSAIX stitched sensor for ALICE ITS3

MLR1 (Multy-Layer Reticle, Dec 2020):

Learn about the technology, characterize pixels, transistors and building blocks

1.5 x 1.5 mm<sup>2</sup> test chips >50 chiplets from: DESY, IPHC, RAL, NIKHEF, CPPM, Yonsei, **CERN**

ER1 (Engineering Run, Dec. 2022):

Prove we can design wafer-scale stitched sensors

MOSS (1.4 x 25.9 cm)

MOST (0.25 x 25.9 cm)

Hybrid-To-Monolithic (H2M)

51 chiplets from: DESY, IPHC, RAL, NIKHEF, SLAC, INFN, CERN

https://indico.cern.ch/event/1556239/

Shared engineering run

MPR2

ER2 (August 2025) Full-scale stitched sensor prototype for ALICE ITS3

W.Snoeys©!

MOSAIX (1.9 x 26.6 cm)

~30 chiplets from: IPHC, SLAC, CPPM, BNL, INFN, Universität Heidelberg, CERN

ER3 (2026): Stitched sensor production for ITS3 (ALICE-specific)

In ER3 ALICEdriven, of order 6-7 chiplets 1.5 mm<sup>2</sup> available to community

259 mm

Organization of ER3 / MPR2 timing / process to access IPs in discussion with users.

DRD7 activities 5th FCC / DRD France ws

In ER1: MOSS

## DRD 7: WP6b -> Shared access to 3D integration

1.Caselle©!

https://indico.cern.ch/event/1556239/

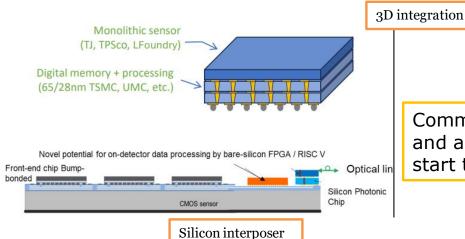

#### DRD 7.6b Goals:

Shared access to 3D integration.

- 2.5D chiplet architectures and 3D W2W

- Key enablers for future detectors

#### **Collaboration Update**

Community is developing and ambitious projects start to shape in DRD7.6b!

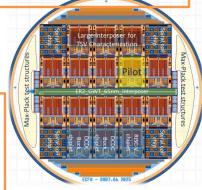

#### Detector packaging technologies for large-area detector modules

Advanced packaging is vital to achieve ultra-low mass, precise assembly, and robust high-speed power/data links required for large-area detectors in future experiments

- From DRD 7.6a: Fabrication of wafer-level dummy interposer structures, emulating state-of-the-art monolithic pixelated detectors

- Featuring only the top metal layer, enabling interconnection testing, including of SiPh chip Integration

- All-Silicon Ladder Concept: Single silicon piece with 4 sensors cut from one wafer

- Post-Processing: Addition of redistribution metal layers for data and power

#### Pilot Project to validate and implement distributed workflow (ECFA-DRD7.6b-2025)

The Pilot Project is a full-wafer engineering run, entirely developed and fabricated in-house by DRD 7.6b contributors

#### Key Features:

- Simple enough to efficiently validate the distributed workflow

- Sufficiently complex to assess chiplet integration, providing insights toward the development of TSVs and RDL capabilities

#### Approach:

- Design test structures suitable for multi-site fabrication

- Coordinate process steps across institutes, including TSV formation, RDL fabrication, and interposer assembly

- Collect performance and yield data to refine distributed production protocols

6-inch wafer size

15

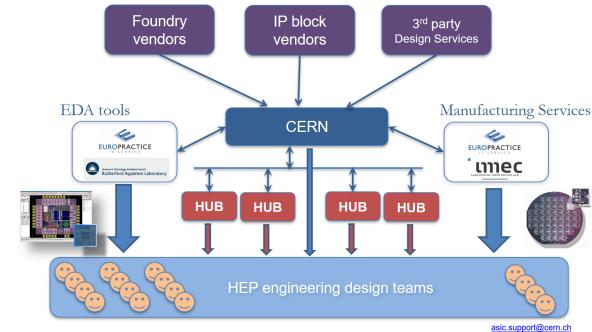

## DRD 7 : WP7 → Hub-based support

K.Kloukinas©! https://indico.cern.ch/event/1556239/

In response to the DRD7 projects and in order to manage ASIC-related design risks in our distributed community, the Steering Committee invites Conveners of WG7.7 to create and steer a task force that will propose an implementation solution for a hub-based structure for ASICs developments

- WG7.7 Conveners

- Xavi Llopart (CERN)

- Mark Willoughby (STFC, UK)

- Kostas Kloukinas (CERN)

- WG7.7 Task Force members by Geographical Location

- Mark Prydderch, UKRI STFC, RAL, UK

- Frederic Morel, CNRS/CEA, IPHC Strasburg site, FR

- Gianni Mazza, INFN (Torino), IT

- Ruud Kluit & Arseniy Vitkovskiy, NIKEF, NL

- David Gascon, University of Barcelona, ES

- Regional HUB operations:

- **ASIC Design** service

- **ASIC Verification** service

- Foundry Design Kit support (PDKs, IP blocks, Design Methodologies)

- Foundry access services (legal frameworks, commercial contracts)

- Administrative, financial and logistics services

- Flexible and scalable model

- HUBs to be classified by the number of services they offer (Tiered Model)

- Design services

- Verification services

- Foundry Design Kit support and IP block sharing services

- Foundry access services

- HUBs can scale up the type of services they offer as necessary

- Sharing of engineering resources between design projects and services

- Funding

- Advocate to funding agencies on the critical importance of such infrastructure

- Introducing a *levy system* where a portion of each project's budget contributes to funding the shared services

- A mix of both funding models

Kostas Kloukinas (CERN) Xavi Llopart (CERN) Mark Willoughby (STFC, UK)

#### Conclusion

# Good participation of IN2P3 teams in particular in this DRD with relatively transverse vocation, sign of the dynamism of our community!

Many of these topics directly impacting / in line with FCC detector R&D

DRDC: L. Serin, D. Contardo