# Coffret DAQ PEPITES

Franck Gastaldi / Rémi Duhamel / Remi. Guillaumat / Lorenzo Bernardi / François Joubert ... et bien d'autres avant

Journée des groupes techniques du LLR – 3 juillet 2025

## Sommaire

**Contexte**

Le système DAQ

**Architecture du firmwre**

Conclusion

### Contexte

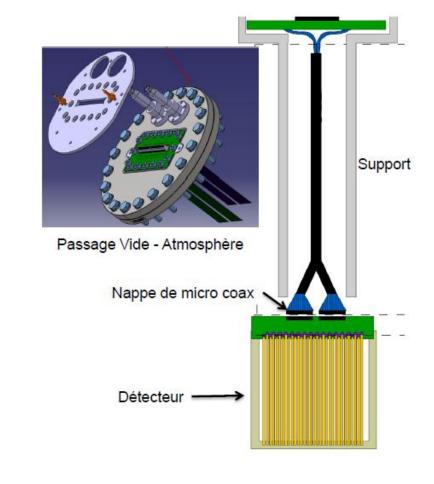

Acheminer des faibles courants (pA) depuis le détecteur situé dans la ligne faisceau à l'ASIC situé hors du

tube faisceau

Petits courants

configuration Triax

- Câblage environ 30 cm de long basse capacité

- Translation du détecter faisceau / hors faisceau

- Passage vide/Atmosphère ambiant

### Solution : câbles micro coax basse capacité logés dans le support détecteur

- Coax + support Triax

- Logés dans le support Pas de problème avec la translation du détecteur (tout se déplace ensemble)

- Passage de vide via un PCB traversant

### Le système DAQ

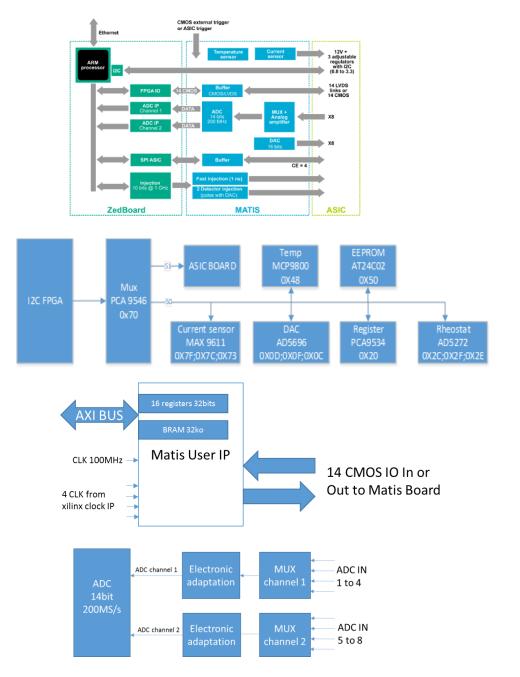

### Coffret constitué de 3 cartes : ZedBoard + Matis + PEPITA

- Cœur du control/readout PEPITAS

- FGPA Zynq (processeur embarqué)

- Lecture/contrôle par RJ45

- Interface logiciel PETALINUX

- Firmware téléchargé sur carte SD

- Interconnexion Zedboard/Matis Connecteur FMC

### Spécifications Matis

- Translateur/driver de niveaux

- Régulateurs de tensions pour **PEPITAS**

- Interconnexion Trigger/Sync/Signal externe

- ADC 2 voies 200Mbs/14bits

- Interconnexion ZedBoard FMC

- Interconnexion PEPITAS Samtec

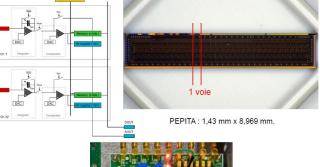

#### Spécifications PEPITA

- Lecture 2 x 32 voies courant

- 2 ASICs PEPITAS (32 voies) de lecture

- Développé par le CEA-DEDIP

- Grande gamme dynamique (pA à 10 nA par voie)

- Technologie XFAB 180 nm 1 voie = Intégrateur et 2 comparateurs (seuil haut, seuil bas)

- Placé en dehors du tube faisceau pour diminuer la dose reçue

### Architecture du firmware

#### **Contrôle/Commande**

Effectué par liaison série I2C et divisée en 2 canaux Un canal est utilisé pour contrôler les composants I2C sur la carte MATIS L'autre canal est utilisé pour PEPITA

#### Configuration de l'ASIC

Chaque Asic sont configurés par 320 bits dans la même transaction. Le firmware (FPGA Zedboard) dispose de 20 registres de 32 bits chacun

### Régalage des HV

Le firmware permet de régler les valeurs de HV sur les plans de PEPITES

### Générateur de signaux

- 1. Mode TDC

- 2. Mode Multiplexé

#### Lecture des données

L'ADC dispose de 2 canaux connectés à un multiplexeur 4 canaux en un. Le multiplexeur est contrôlé par le firmware

### Conclusion

- 1. Système semi-opérationnel (un mode de fonctionnement de l'ASIC à debugger)

- 2. Réaliser une automatisation des tests

- 1. Slow control

- 2. Control/commande I2C

- 3. Pilotage ADC

- 3. Mener une réflexion sur l'avenir de ce coffret et les solutions envisagées