**IN2P3**

Les deux infinis

# La microélectronique dans les expériences

Damien Thienpont

École du détecteur à la mesure 2025

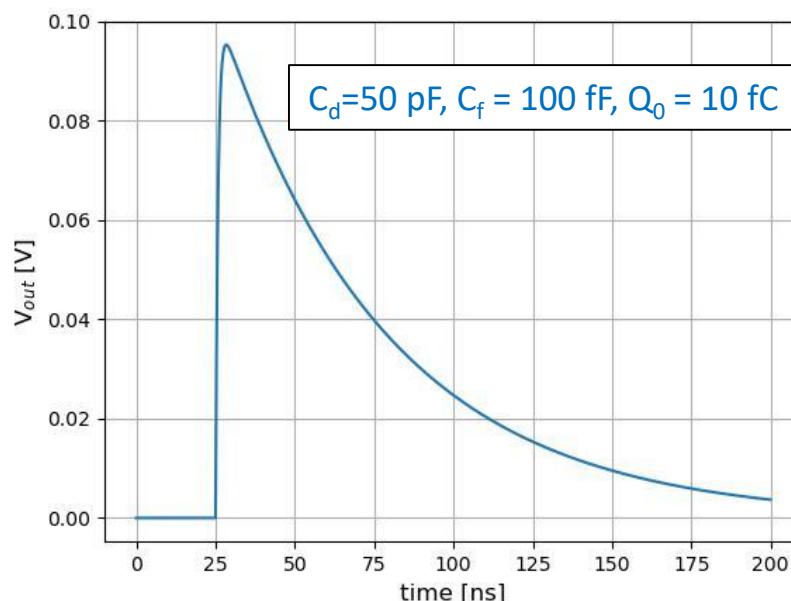

# Rappel

$$V_{out}(t) = -\frac{Q_0}{C_f} \cdot \frac{1}{\left(1 + \frac{C_d}{G_0 \cdot C_f}\right)} \left(1 - e^{-t/\tau}\right) \quad \text{avec } \tau = \frac{C_d}{G_0 \omega_0 C_f}$$

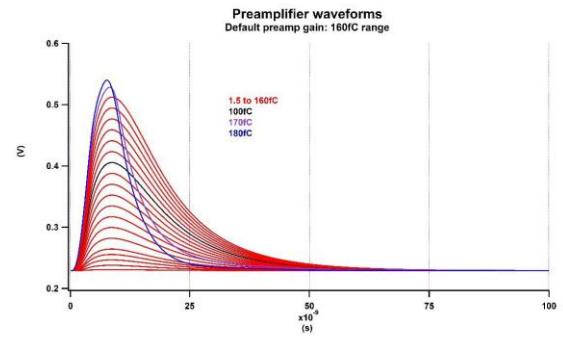

# Besoin d'un étage de filtrage/shaper

- **Filtrage:** optimiser le rapport signal sur bruit et/ou le jitter (~noise/pente)

- Filtrer contribution du bruit hors fréquence du signal: passe-haut (CR), passe-bas (RC)

- **Shaper:** mettre en forme le signal pour permettre la mesure de la charge

- Rendre le signal plus « court »

- Ajuster le peaking time → échantillonnage de l'ADC au maximum du signal

- Shaper bipolaire → intégrale du signal nulle

$$ENC = \sqrt{A_t \cdot Si \tau + A_v \cdot Sv \cdot \frac{C_{in}^2}{\tau}}$$

# Le bruit électronique

# Plan du cours

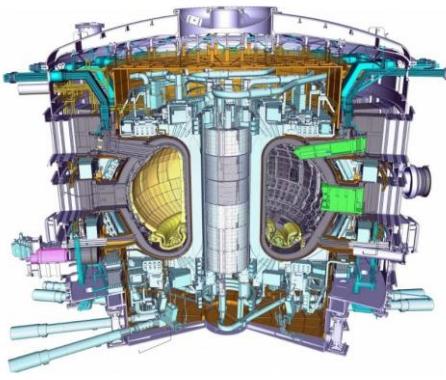

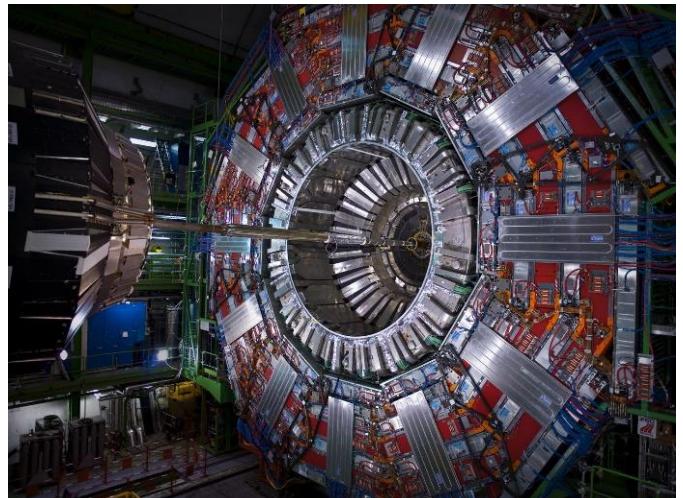

- Introduction: de l'électronique partout dans nos détecteurs

- Fondamentaux de l'électronique

- Rappel général des bases de l'électronique

- Détecteur et préamplificateur

- Conversion Analogique/Numérique

- Numérique

- Le langage HDL (VHDL ou Verilog), synthèse, vérification

- De plus en plus de numérique dans les ASICs

- Design Flow: Analog-on-Top ou Digital-on-Top

- **Bruit électronique**

- **Fondamentaux**

- **Filtrage, shaping**

- **Techniques de mesure**

- Effets des radiations sur l'électronique

- TID et SEE

- Campagnes d'irradiation, performances, cross-section

- Extrême importance des tests: sur table, radiation, beam, système

- La mesure de temps

- Généralité

- Les TDCs

# Qu'en est-il avec du bruit?

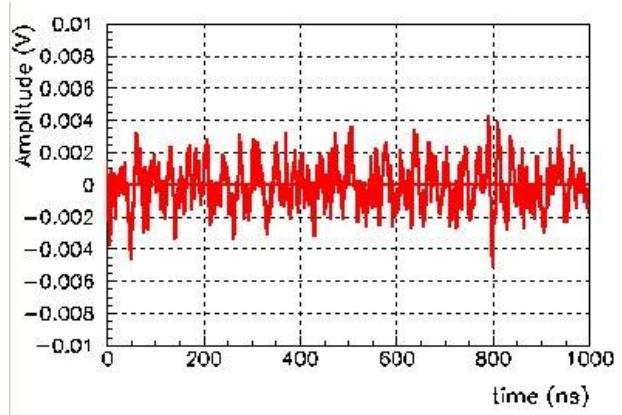

- Définition du bruit

- Fluctuation aléatoire superposée au signal

- Traitement statistique: somme quadratique, **module au carré des impédances et des fonctions de transfert**

- 3 types de bruit

- Bruit fondamental (thermal noise, shot noise)

- Excess noise ( $1/f$ , ...)

- Parasitiques: EMC/EMI (pickup noise, ground loops...)

# Le bruit électronique

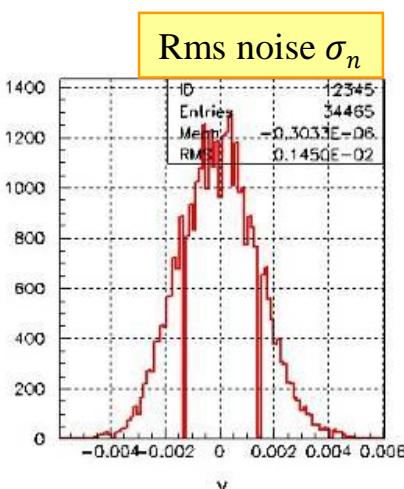

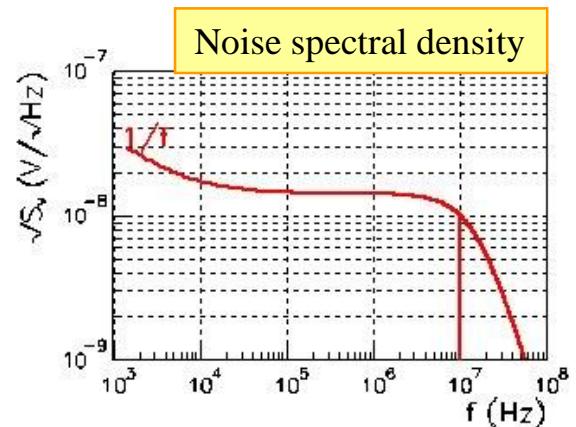

- Le bruit électronique provient de la superposition d'un grand nombre de petits événements électriques aléatoires qui s'ajoutent au signal de tension ou de courant souhaité.

- On peut calculer l'autocorrélation d'un signal  $s(t)$  telle que  $R_n(\tau) = \langle n(t) \cdot n(t + \tau) \rangle$ , c'est la valeur moyenne du produit du signal avec lui-même retardé de  $\tau$

- De l'autocorrélation, on calcule la **densité spectrale de bruit** comme la transformée de Fourier de  $R_n(\tau)$

$$S_n(f) = \int_0^{+\infty} R_n(\tau) e^{-j\omega\tau} d\tau$$

- La densité spectrale de bruit est la **distribution en fréquence de la puissance du bruit**

- Contient plus d'information que la simple déviation standard  $\sigma_n$ .

- On obtient la **déviation standard** en intégrant la densité spectrale de bruit

$$\sigma_n^2 = \int_0^{+\infty} S_n(f) df = \int_0^{+\infty} e_n^2(t) dt$$

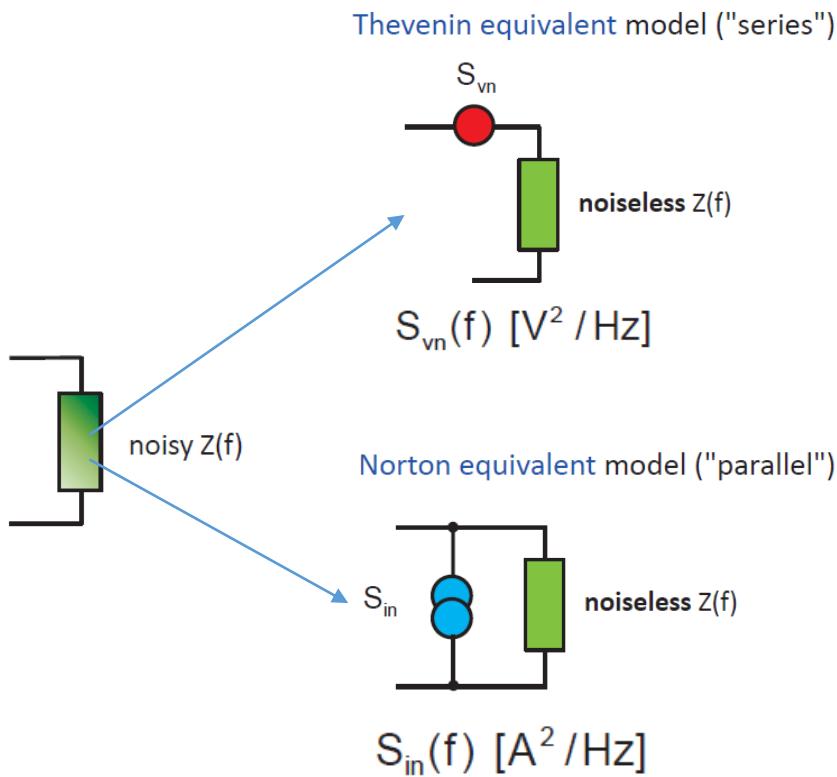

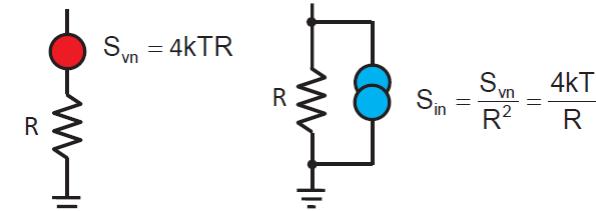

# Modélisation du bruit électronique dans les circuits

$$S_{vn} = S_{in} \cdot |Z(f)|^2$$

- Thermal noise (R)

- $S_{vn}(f) = 4kTR = e_n^2$        $S_{in}(f) = \frac{S_{vn}}{R^2} = \frac{4kT}{R} = i_n^2$

- $K$  = constante de Boltzmann,  $T$  = Température en Kelvin

- Shot noise (junctions)

- $S_i(f) = 2qi = i_n^2$

- $q$  = charge de l'électron,  $i$  = courant DC dans la jonction

- Capa?

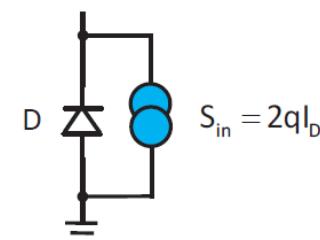

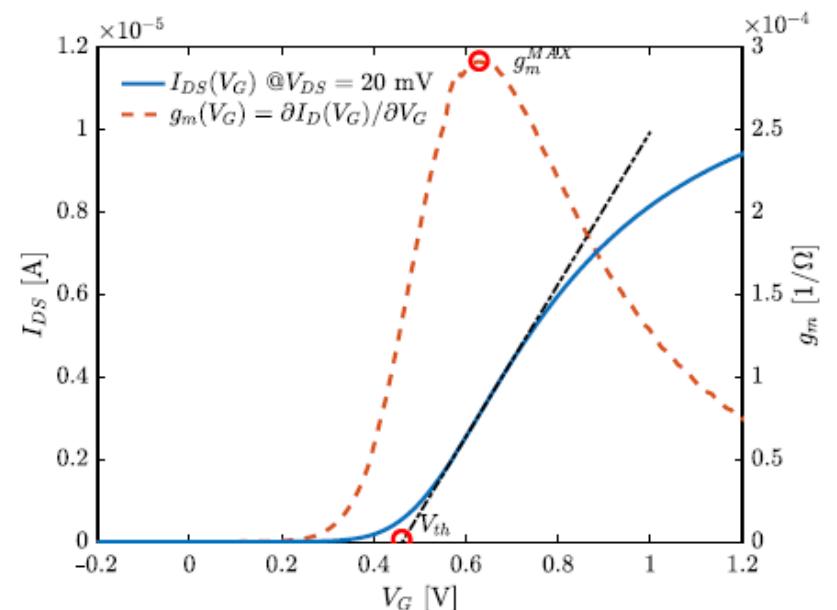

# Bruit dans un transistor

- Le bruit dans un MOSFET provient principalement des effets aléatoires associés aux porteurs circulant dans le canal pendant le fonctionnement, c'est-à-dire des fluctuations aléatoires du courant Drain-Source  $I_{DS}$ .

- Deux sources de bruit indépendantes sont associées à  $I_{DS}$  :

- **Agitation thermique** semblable au bruit thermique d'une résistance : elle engendre un **bruit blanc** dont la puissance est proportionnelle à la transconductance  $g_m = \frac{\partial I_{ds}}{\partial V_{gs}}$

- **Fluctuations du nombre ou de la mobilité des porteurs** : génère un **bruit de basse fréquence (bruit 1/f)** dont la puissance est proportionnelle à la surface de grille  $L^*W$  et au carré de la fréquence de coupure  $f_T$ .

- Le bruit peut être modélisé par une **unique source de bruit équivalente en série  $S_{vn}$**  appliquée à la grille.

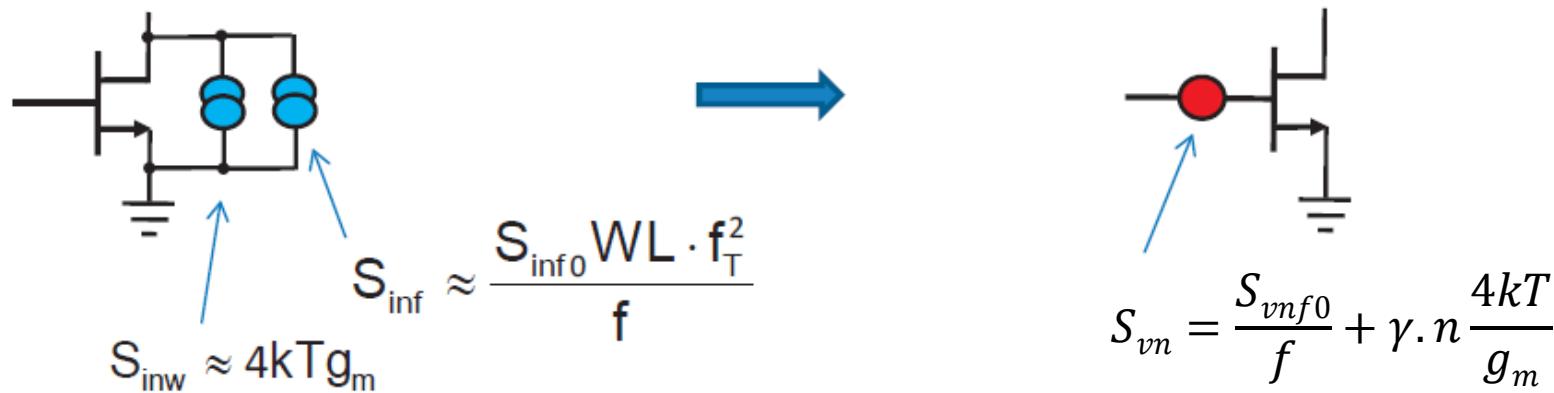

# Modélisation du bruit dans un circuit

- On peut utiliser 2 générateurs de bruit

- Bruit parallèle:  $S_{in} = i_n^2$  (courant de fuite) modélisé par un générateur en courant

- Bruit série:  $S_{vn} = e_n^2$  (préamp) modélisé par un générateur en tension

- Le bruit est référencé à l'entrée

- Deux générateurs, série et parallèle, pas plus, pas moins:  $e_n^2$  et  $i_n^2$

- Un générateur de bruit n'a pas de polarité (quadratique)

- L'impédance d'entrée est à gauche dans ce modèle

- Règle d'or:

- Toujours calculer le signal avant le bruit

- Ce qui compte est le rapport signal sur bruit

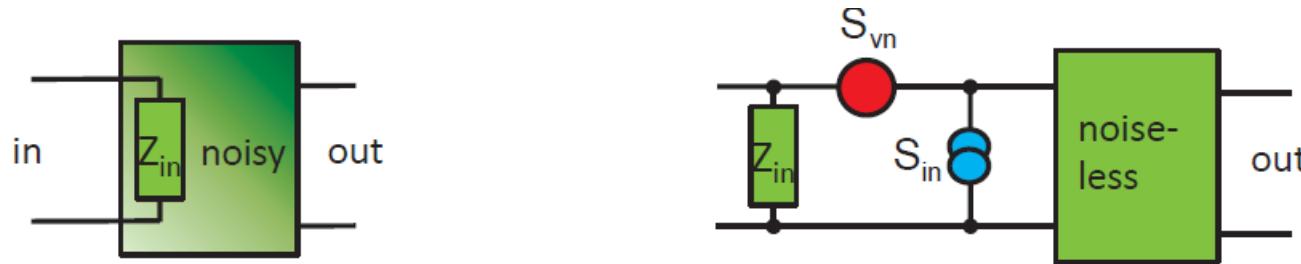

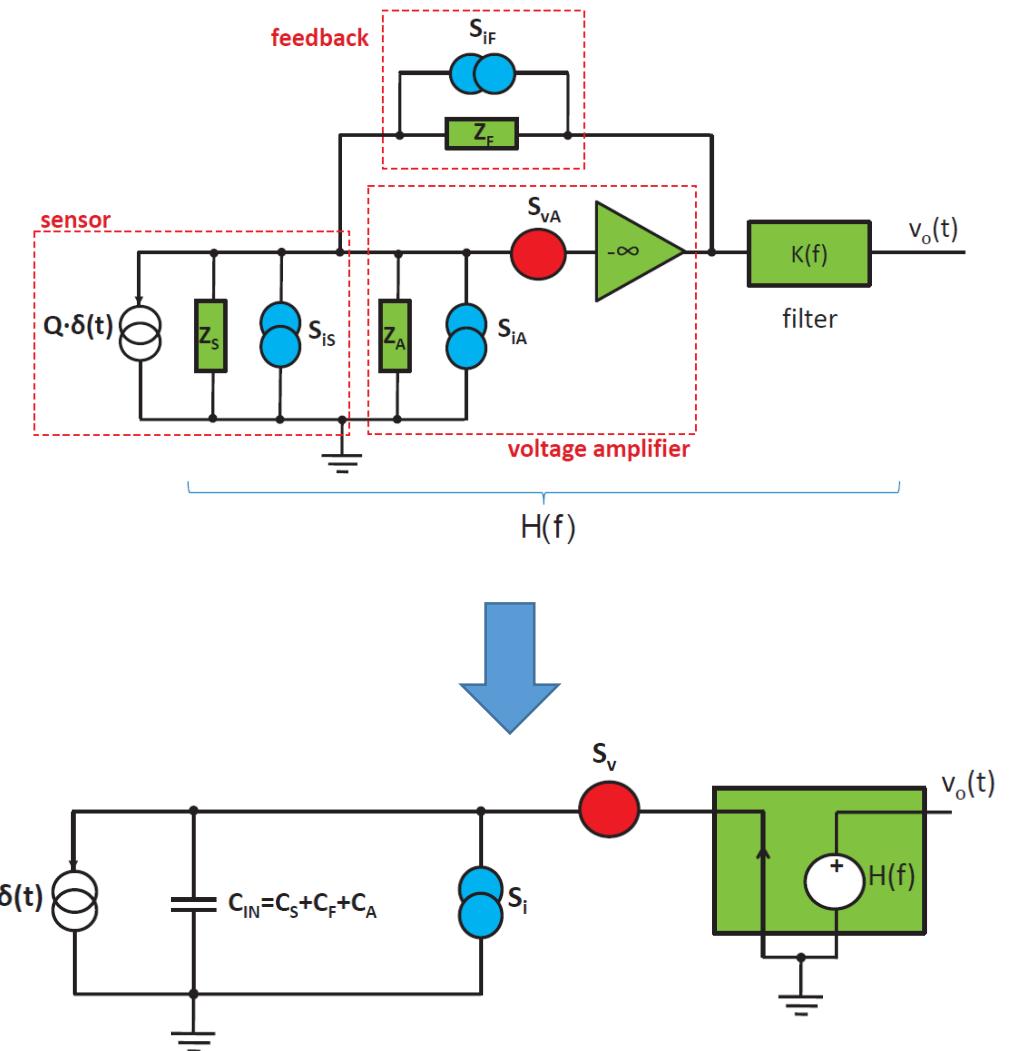

# Calcul du bruit dans un circuit

$$S_i = Si_{leak} + Si_S + Si_A + Si_F = 2qi + (4kT\omega Cin * LossFactor)$$

$$S_v = \sim \frac{S_{vnf0}}{WL.f} + \gamma n \frac{4kT}{g_m}$$

Avec  $i = 1nA$ ,  $\sqrt{S_i} = i_n = \sim 17 fA/\sqrt{Hz}$

Avec  $gm = 50m\frac{A}{V}$ ,  $T = 300 K$ ,  $\sqrt{S_v} = e_n = \sim 0.6 nV/\sqrt{Hz}$

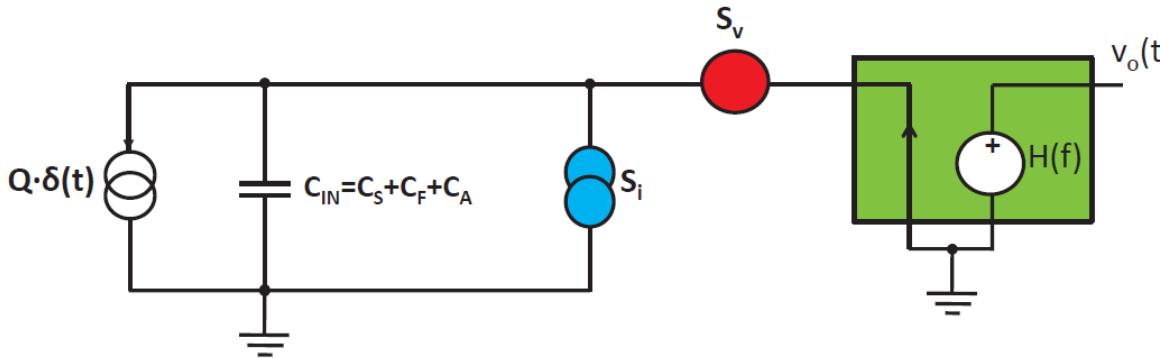

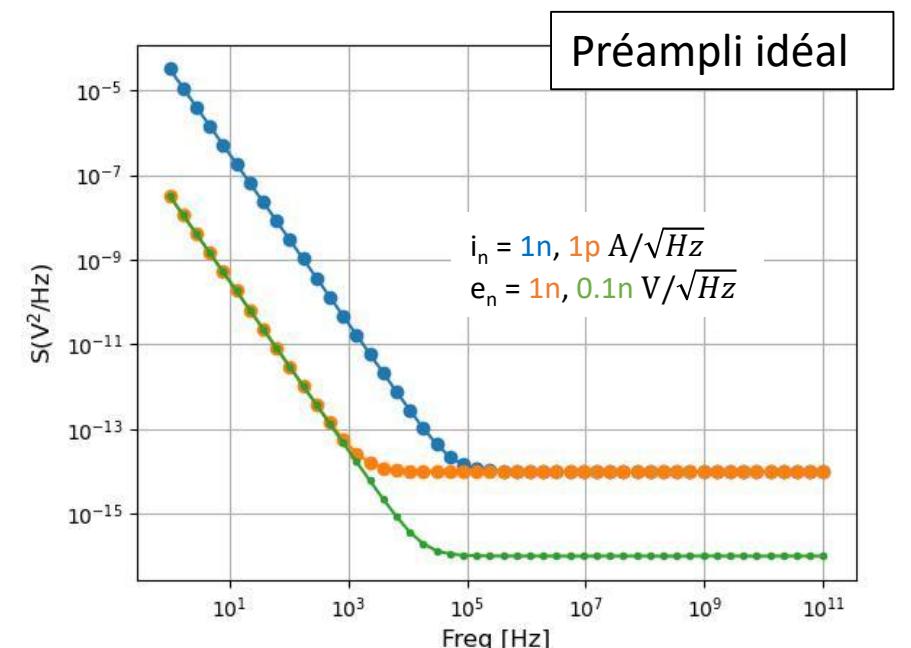

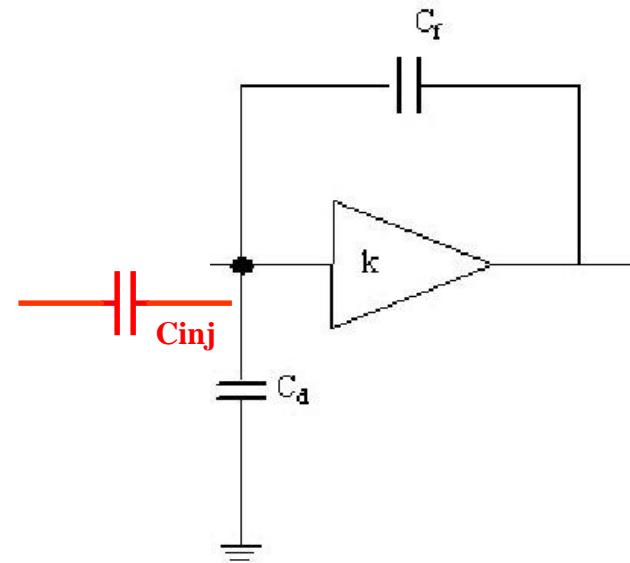

# Calcul du bruit dans un circuit

Le signal en sortie est  $V_o(t) = Q \cdot h(t) = \int_{-\infty}^{+\infty} Q \cdot H(f) \cdot e^{j2\pi f t} df$  avec un maximum  $V_{o, max} = Q \cdot h(t_{max}) = Q \cdot h_{max}$

$$\text{La densité spectrale de bruit en sortie est } S(f) = \left( S_i + \frac{S_v}{|Z_{in}|^2} \right) * |H_f|^2$$

$$\text{Pour un préamplificateur de charge idéal: } S(f) = \frac{S_i}{\omega^2 C_f^2} + \frac{S_v C_d^2}{C_f^2}$$

- Le bruit parallèle est en  $1/f^2$

- Le bruit série est plat avec un **noise gain**  $C_d/C_f$

Et donc la variance :

$$\sigma_{V_o}^2 = \overline{V_{no}^2(t)} = \int_0^{\infty} S_i |H(f)|^2 df + \int_0^{\infty} S_v \omega^2 C_d^2 |H(f)|^2 df$$

# Bruit d'un préampli de charge idéal

- Le bruit rms  $\sigma_{V_0}$  s'écrit pour un préampli idéal (gain infini,  $R_f$  infini) avec  $H(f) = \frac{1}{j2\pi f C_f}$  :

$$\sigma_{V_o}^2 = \overline{V_{no}^2(t)} = \frac{S_i}{4\pi^2 C_f^2} \int_0^\infty \frac{1}{f^2} df + \frac{S_v C_d^2}{C_f^2} \int_0^\infty df$$

- La contribution du bruit parallèle diverge: le préampli intègre le bruit du pulse durant un temps infini (en pratique limité par  $R_f$ )

- La contribution du bruit série diverge: bande passante infinie, donc temps de montée infiniment court (en pratique limité par la bande passante)

- Il s'avère nécessaire de filtrer le signal du préampli pour optimiser S/N

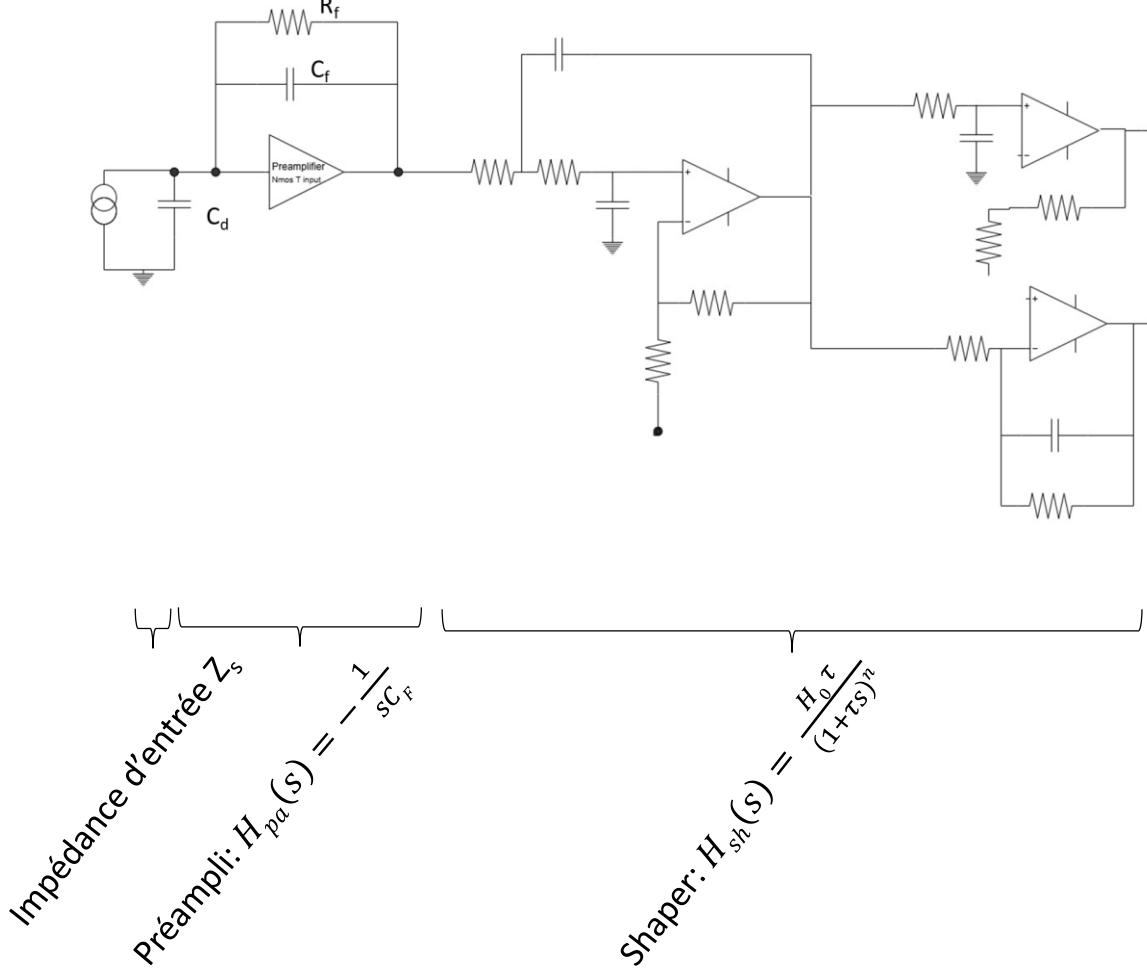

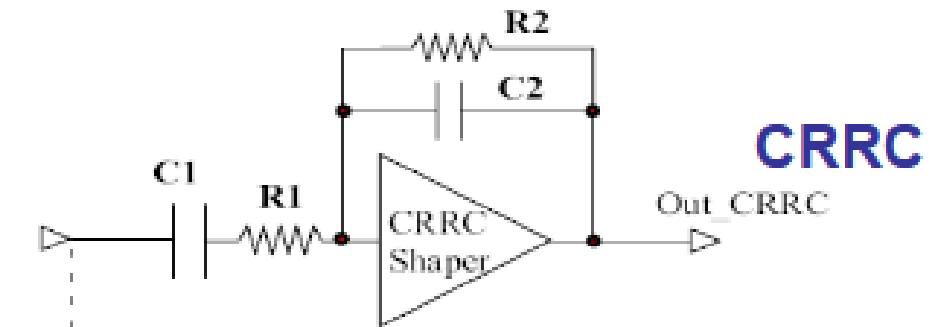

# Nécessité du filtrage

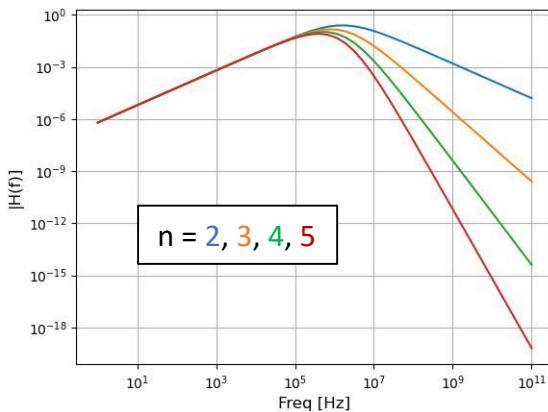

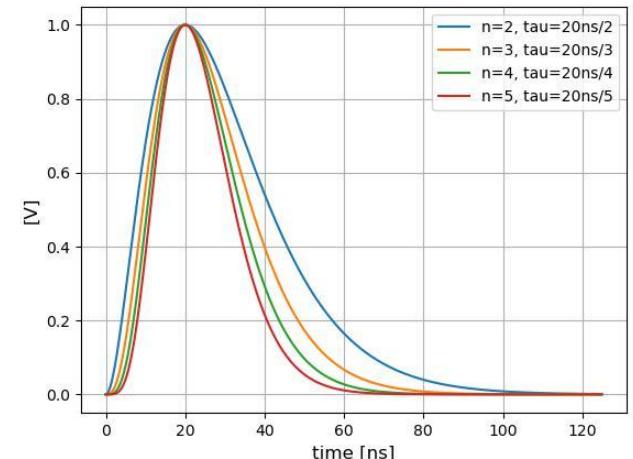

- Pour un préampli idéal, on a  $H(p) = \frac{1}{pC_f}$

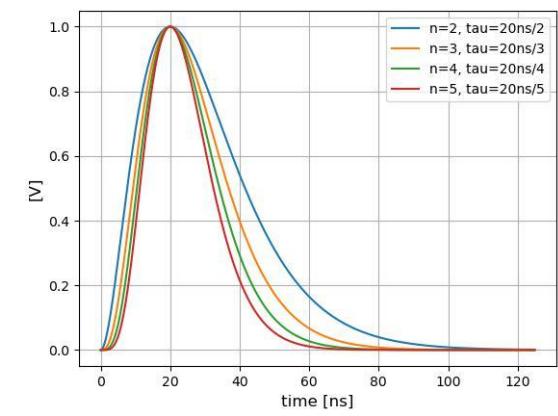

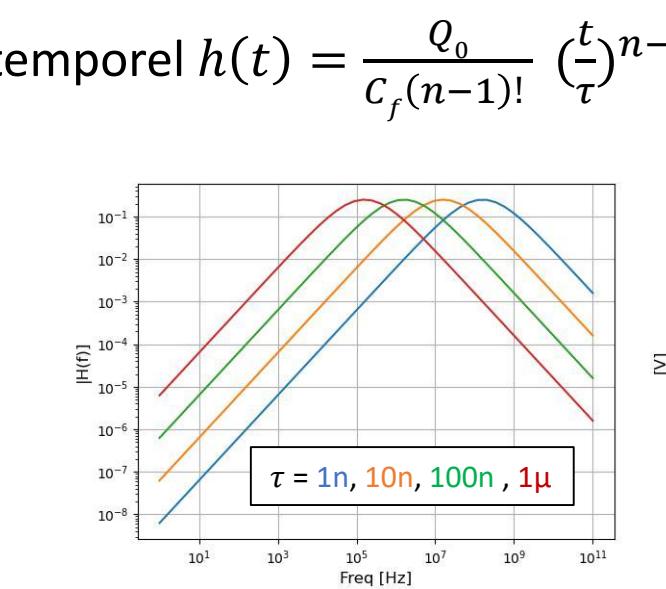

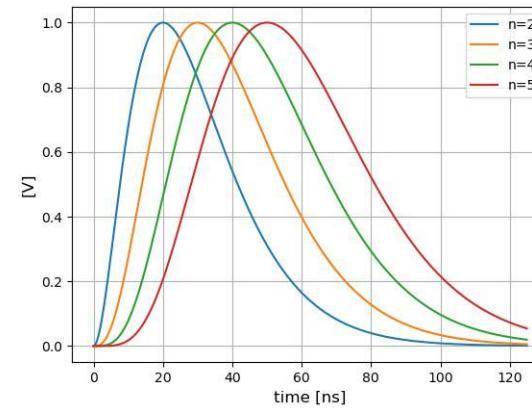

- Pour un filtre CR-RC<sup>n-1</sup>, on a  $H(p) = \frac{\tau p}{(1+\tau p)^n}$ ,

- Un filtre passe-bas pour couper le bruit haute fréquence

- Un filtre passe-haut pour couper le bruit parallèle

- Ensemble, on a donc  $H(p) = \frac{Q_0\tau}{C_f} \cdot \frac{1}{(1+\tau p)^n}$  et en temporel  $h(t) = \frac{Q_0}{C_f(n-1)!} \left(\frac{t}{\tau}\right)^{n-1} e^{-\frac{t}{\tau}}$

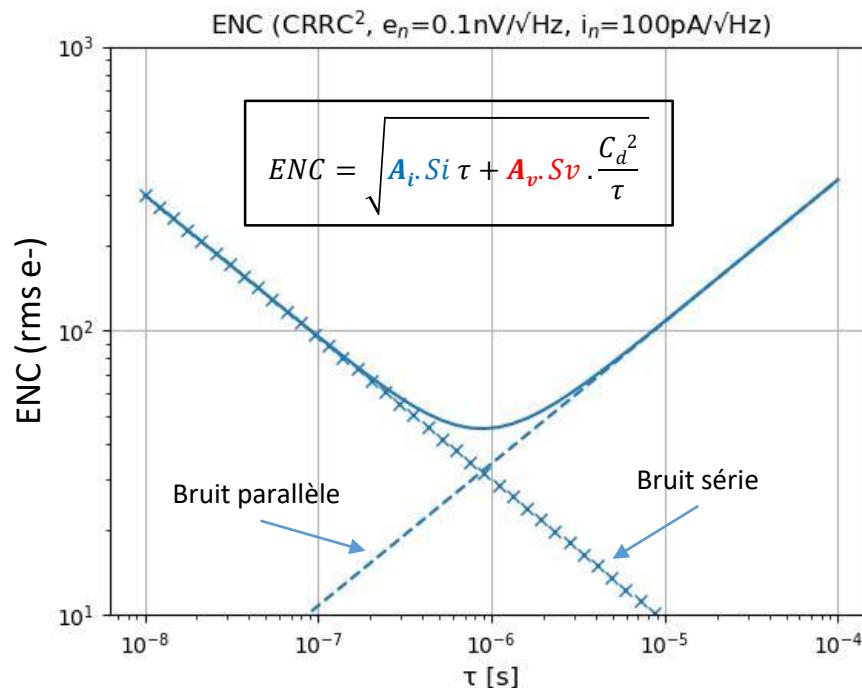

# Bruit après un filtre CR-RC<sup>n</sup>

- Le bruit rms est

$$\sigma_{V_o}^2 = \overline{V_{no}^2(t)} = \int_0^\infty S_i \cdot |H(f)|^2 df + \int_0^\infty S_v \cdot \omega^2 C_d^2 \cdot |H(f)|^2 df$$

- Ce qui donne

$$\begin{aligned} \sigma_{V_o}^2 &= \frac{Q_0 S_i}{C_f^2} \int_0^\infty \frac{\tau^2}{(1 + \tau^2 \omega^2)^n} df + S_v \cdot C_d^2 \frac{Q_0}{C_f^2} \int_0^\infty \omega^2 \cdot \frac{\tau^2}{(1 + \tau^2 \omega^2)^n} df \\ &= Q_0 \frac{\tau S_i}{2\pi C_f^2} \int_0^\infty \frac{1}{(1+X^2)^n} dX + Q_0 S_v \cdot \frac{C_d^2}{2\pi \tau C_f^2} \int_0^\infty \frac{X^2}{(1+X^2)^n} dX \end{aligned}$$

- L'ENC est la charge qu'il faut injectée en entrée telle que S/N = 1

$$ENC^2 = \frac{\sigma_{V_o}^2}{\frac{Q_0^2}{C_f^2} h_{max}} = A_i \cdot S_i \tau + A_v \cdot S_v \cdot \frac{C_d^2}{\tau}$$

$$h_{max, CRRCn} = \frac{(n-1)^{n-1}}{(n-1)!} e^{-(n-1)} \text{ à } t = \tau(n-1)$$

$$A_{iw} = \frac{\int_0^\infty \frac{1}{(1+x^2)^n} dx}{2\pi \left[ \frac{(n-1)^{n-1}}{(n-1)!} e^{-(n-1)} \right]^2}$$

$$A_{vw} = \frac{\int_0^\infty \frac{x^2}{(1+x^2)^n} dx}{2\pi \left[ \frac{(n-1)^{n-1}}{(n-1)!} e^{-(n-1)} \right]^2}$$

|                       | <b>n=2</b> | <b>3</b> | <b>4</b> | <b>5</b> |

|-----------------------|------------|----------|----------|----------|

| <b>A<sub>iw</sub></b> | 0.924      | 1.280    | 1.556    | 1.791    |

| <b>A<sub>vw</sub></b> | 0.924      | 0.425    | 0.311    | 0.256    |

- La contribution parallèle va avec  $\sqrt{\tau}$

- La contribution série va avec  $1/\sqrt{\tau}$  et  $C_d$

# Les intégrales de bruit...

*CRRCn*:

$$H(s) = \frac{\tau s}{(1+\tau s)^{n+1}}$$

Réponse indicielle (= à un step):

$$h(t) = \frac{1}{n!} \left(\frac{t}{\tau}\right)^n e^{-\frac{t}{\tau}}$$

$$\text{Maximum pour } t_m = n\tau : h\left(\frac{t_m}{\tau}\right) = \frac{1}{n!} n^n e^{-n}$$

Intégrales de bruit :

$$I_a = \int_0^\infty |H(j\omega)|^2 \frac{d(\omega\tau)}{2\pi} = \int_0^\infty \frac{\omega^2 \tau^2}{(1+\omega^2 \tau^2)^{n+1}} \frac{d(\omega\tau)}{2\pi} = \frac{1}{2n} \frac{2n-3}{2n-2} \dots \frac{1}{2} \frac{\pi}{2\pi} = \frac{1}{4} \frac{1}{2n-1} \frac{(2n)!}{n^2 2^{2n}}$$

$$I_b = \int_0^\infty \frac{|H(j\omega)|^2}{(\omega\tau)^2} \frac{d(\omega\tau)}{2\pi} = \int_0^\infty \frac{1}{(1+\omega^2 \tau^2)^{n+1}} \frac{d(\omega\tau)}{2\pi} = \frac{2n-1}{2n} \frac{2n-3}{2n-2} \dots \frac{1}{2} \frac{\pi}{2\pi} = \frac{1}{4} \frac{(2n)!}{n^2 2^{2n}}$$

$$I_c = \int_0^\infty \frac{|H(j\omega)|^2}{(\omega\tau)} \frac{d(\omega\tau)}{2\pi} = \int_0^\infty \frac{\omega\tau}{(1+\omega^2 \tau^2)^{n+1}} \frac{d(\omega\tau)}{2\pi} = \frac{1}{2n} \frac{1}{2\pi}$$

*CRRC2*:

$$H(s) = \frac{\tau s}{(1+\tau s)^3}$$

Réponse indicielle (= à un step):

$$h(t) = \frac{1}{2} \left(\frac{t}{\tau}\right)^2 e^{-\frac{t}{\tau}}$$

$$\text{Maximum pour } t_m = 2\tau : h\left(\frac{t_m}{\tau}\right) = 2e^{-2}$$

Intégrales de bruit :

$$I_a = \frac{1}{4} \frac{1}{2n-1} \frac{(2n)!}{n^2 2^{2n}} = \frac{1}{4} \frac{1}{3} \frac{24}{64} = \frac{1}{32}$$

$$I_b = \frac{1}{4} \frac{(2n)!}{n^2 2^{2n}} = \frac{1}{4} \frac{24}{64} = \frac{3}{32}$$

$$I_c = \frac{1}{2n} \frac{1}{2\pi} = \frac{1}{8\pi}$$

$$Ia = \int_0^\infty |H(j\omega)|^2 \frac{d\omega}{2\pi} \quad Ia = \int_0^\infty \frac{x^{2m}}{(1+x^2)^{m+n}} \frac{dx}{2\pi} \quad Ib = \int_0^\infty \frac{x^{2m-2}}{(1+x^2)^{m+n}} \frac{dx}{2\pi} \quad Ic = \int_0^\infty \frac{x^{2m-1}}{(1+x^2)^{m+n}} \frac{dx}{2\pi}$$

For CR<sup>m</sup>RC<sup>n</sup>, central frequency :  $f = \frac{1}{2\pi\tau} \sqrt{\frac{m}{n}}$

$$Vn = \Gamma \frac{e_n}{\sqrt{\tau}} \quad \Gamma = \frac{\sqrt{I_a}}{V_{\max}}$$

$$ENC_s = \alpha_1 \frac{enC_t}{\sqrt{\tau}}$$

$$ENC_p = \beta_1 m \sqrt{\tau}$$

|                                 | tm    | Max      | I <sup>2</sup> <sub>a</sub> | I <sup>2</sup> <sub>b</sub> | $\Gamma$ | $\alpha_1$ | $\beta_1$ | tp <sub>5%-max</sub> /τ |

|---------------------------------|-------|----------|-----------------------------|-----------------------------|----------|------------|-----------|-------------------------|

| CR RC                           | 1     | 0.36788  | 1/8                         | 1/8                         | 0.961    | 190        | 190       | 0,981                   |

| CR RC <sup>2</sup>              | 2     | 0.27067  | 1/32                        | 3/32                        | 0.653    | 129.1      | 223.6     | 1,820                   |

| CR RC <sup>3</sup>              | 3     | 0.22404  | 1/64                        | 5/64                        | 0.558    | 110.3      | 246.6     | 2,523                   |

| CR RC <sup>4</sup>              | 4     | 0.19537  | 5/512                       | 35/512                      | 0.506    | 100.       | 264.5     | 3,136                   |

| CR RC <sup>5</sup>              | 5     | 0.17547  | 7/1024                      | 63/1024                     | 0.471    | 93.1       | 279.4     | 3,686                   |

| CR RC <sup>6</sup>              | 6     | 0.16062  | 21/4096                     | 231/4096                    | 0.446    | 88.1       | 292.2     | 4,188                   |

| CR <sup>2</sup> RC              | 0,586 | 0.23058  | 3/32                        | 1/32                        | 1.328    | 262.5      | 151.5     | 0,574                   |

| CR <sup>2</sup> RC <sup>2</sup> | 1.268 | 0.13060  | 1/64                        | 1/64                        | 0.957    | 189.2      | 189.2     | 1,144                   |

| CR <sup>2</sup> RC <sup>3</sup> | 2     | 0.09022  | 3/512                       | 5/512                       | 0.848    | 167.6      | 216.5     | 1,653                   |

| CR <sup>2</sup> RC <sup>4</sup> | 2.764 | 0.068557 | 3/1024                      | 7/1024                      | 0.790    | 156.01     | 238.4     | 2,111                   |

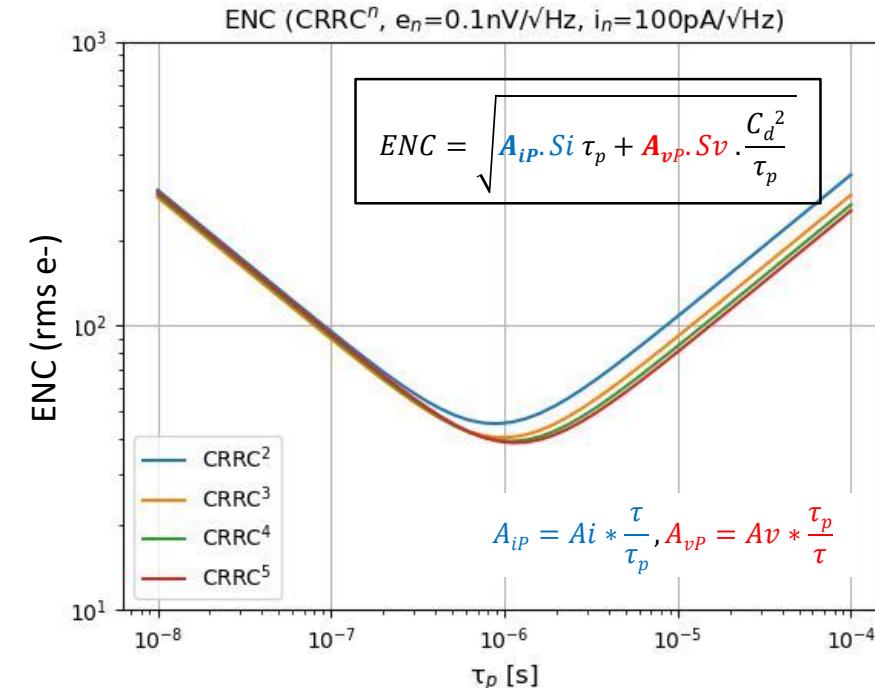

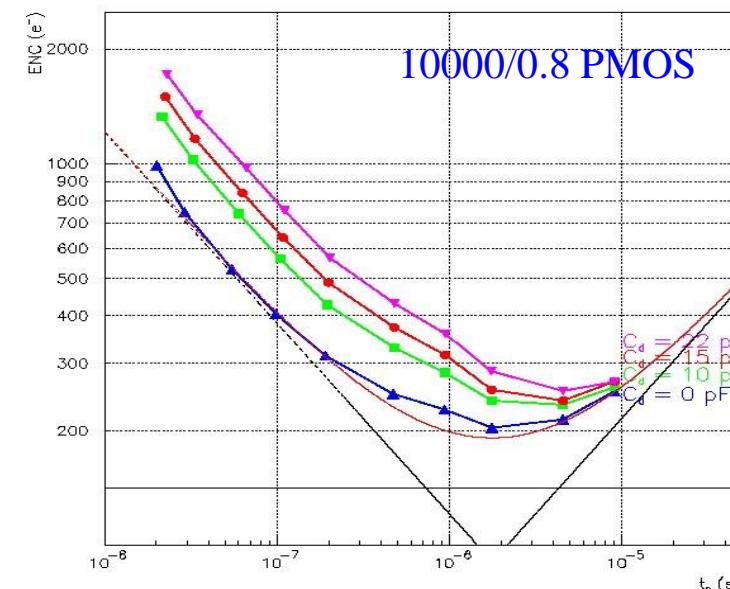

# ENC vs. $\tau_p$ pour différent ordres $n$ de shaper

- Plutôt que la constante de temps  $\tau$ , nous pouvons utiliser un paramètre plus « visible ». Le temps de montée  $\tau_p$  (peaking time)

- défini comme le temps nécessaire pour atteindre 10 % à 90 % de l'amplitude de l'impulsion

- Nous pouvons comparer les performances de filtres d'ordres différents à peaking time égal

- Un peaking time égal signifie une contribution du bruit blanc quasi égale

- Le minimum ne s'améliore guère au-delà de l'ordre 5

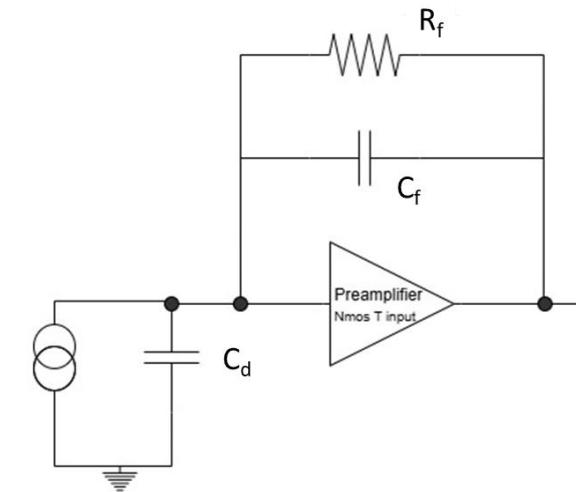

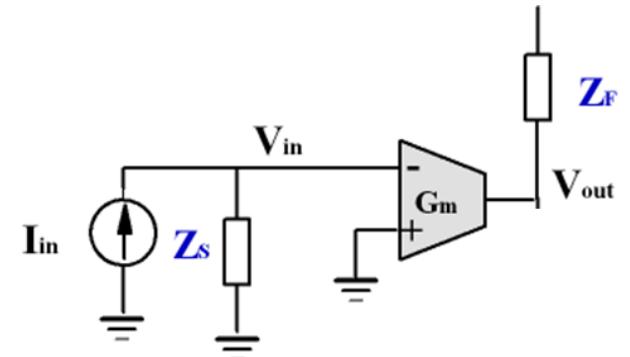

# Comment concevoir un préampli bas bruit?

- Schéma simplifié

- Optimisation des composants

- Quel transistor d'entrée (PMOS, NPN ?)

- Quel courant de bias?

- Quelle taille de transistor?

- Quelle est la contribution en bruit de chaque composant?  $e_n$  et  $i_n$  et  $1/f$ ? Deuxième étage?

- Comment le minimiser?

- Quels paramètres déterminent la stabilité?

- Quel est le comportement en saturation?

- Comment varie le signal et le bruit avec la capa d'entrée?

- Comment optimiser la dynamique de sortie (gamme et linéarité)?

- Quelle est la sensibilité aux tensions d'alimentation, température?

- Effets des voisins, bias? Crosstalk?

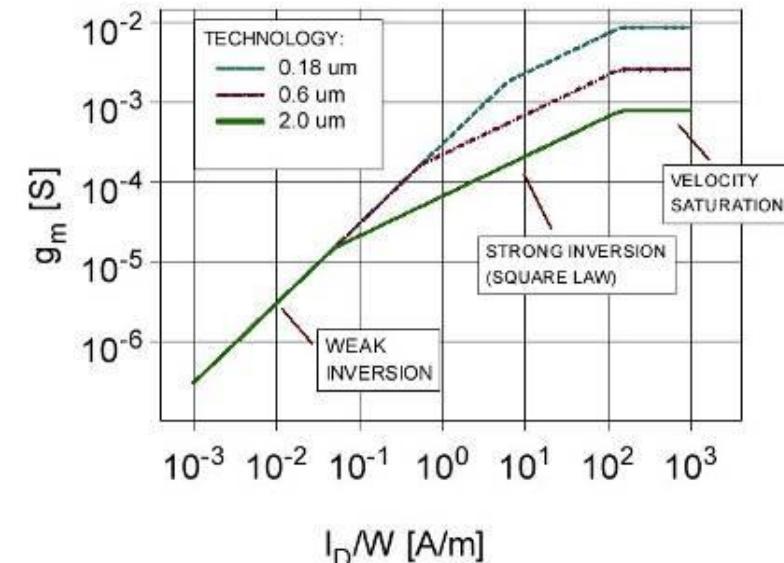

# MOS input transistor sizing

- Strong inversion:** capacitive matching

- $g_m$  proportionnal to  $W/L \sqrt{I_D}$

- $C_{GS}$  proportionnal to  $W*L$

- ENC proportionnal to  $(C_{det} + C_{GS}) / \sqrt{gm}$

- Optimum  $W/L : C_{GS} = 1/3 C_{det}$

- Large transistors are easily in moderate or weak inversion at small current

- Weak inversion**

- $g_m$  proportionnal to  $I_D$  (indep of  $W,L$ )

- ENC minimal for  $C_{GS}$  minimal, provided the transistor remains in weak inversion

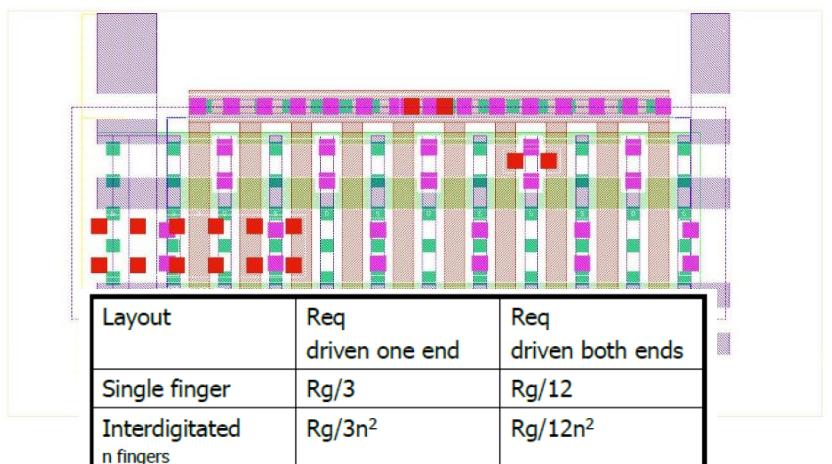

- Transistor gate resistance (add  $4kTR$  in serie noise)**

- 1 gros transistor:  $R_g = \sim 4200 \text{ Ohm} (\sim 8 \text{ nV}/\sqrt{\text{Hz}})$

- A partir de 15 plus petits transistor:  $R_g = 280 \text{ Ohm}$

- With 20 gates  $\rightarrow 14 \text{ ohm}$

- Connected both sides  $\rightarrow < 7 \text{ Ohm}$

- 15 transistors in //  $\rightarrow < 0.5 \text{ Ohm} (\sim 90 \text{ pV}/\sqrt{\text{Hz}})$

- Attention de bien connecté le substrat pour minimiser  $g_{mb}$  (bulk noise)

$$ENC^2 = 2\pi A_{vfp} \frac{K_F}{c_{ox}L_{min}} \frac{(C_S + c_{ox}WL_{min})^2}{W} + \begin{cases} \frac{A_{vwP}}{\tau_p} \frac{4kT\gamma n}{2\mu c_{ox}} \sqrt{\frac{L_{min}}{I_{D0}}} \frac{1}{\sqrt{W}} \frac{(C_S + c_{ox}WL_{min})^2}{\sqrt{W}} \\ \frac{A_{vwP}}{\tau_p} \frac{4kT\gamma n^2 V_T}{I_{D0}} \frac{1}{L_{D0}} (C_S + c_{ox}WL_{min})^2 \end{cases}$$

SI

WI

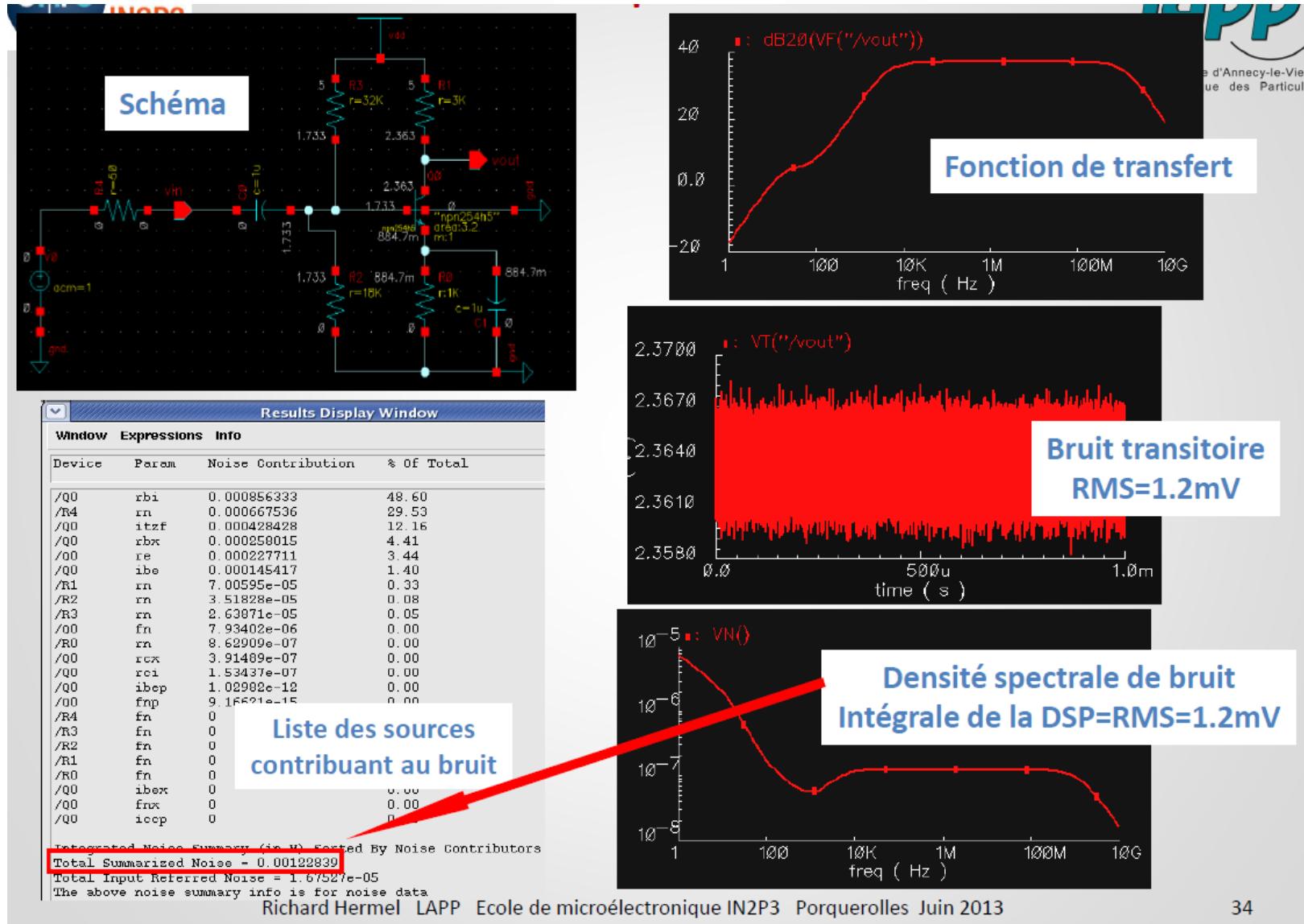

# Simulation du bruit

# Attention aux simulations

## 8.3 Noise Model Flag

A model flag, `noiMod`, is used to select different combination of flicker and thermal noise models discussed above with possible optoins described in Table 8-2.

| noimod flag | Flicker noise model | Thermal noise model |

|-------------|---------------------|---------------------|

| 1           | SPICE2              | SPICE2              |

| 2           | BSIM3v3             | BSIM3v3             |

| 3           | BSIM3v3             | SPICE2              |

| 4           | SPICE2              | BSIM3v3             |

Table 8-2. `noiMod` flag for differnet noise models.

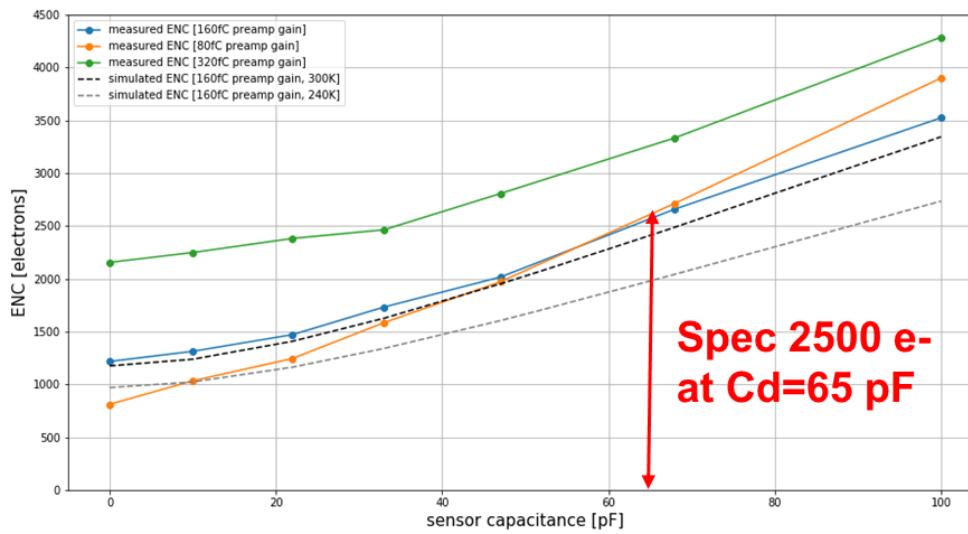

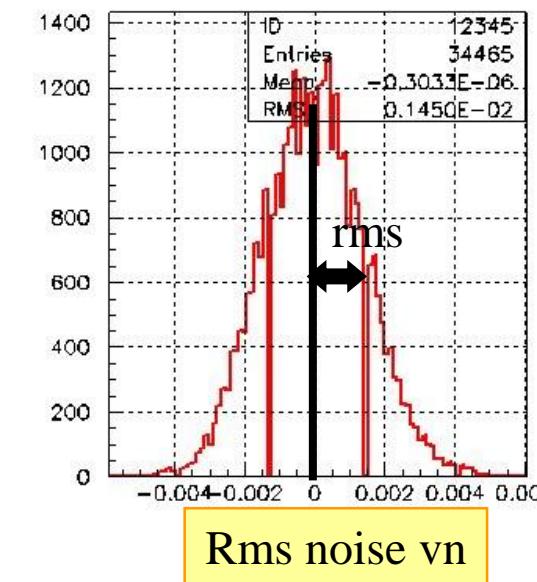

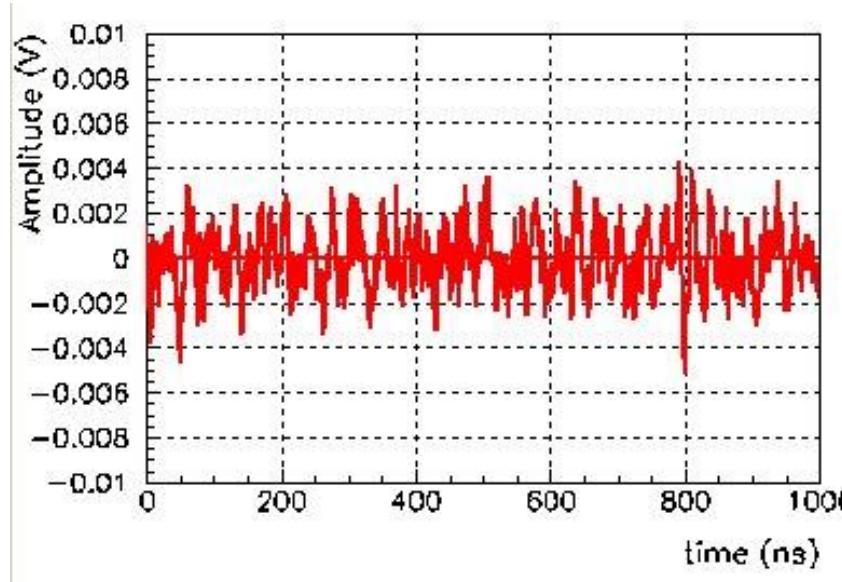

# Mesure de la charge équivalente de bruit (1)

- Mesure du bruit rms :  $v_n$

- Voltmètre rms ou histogrammation de la ligne de base sur oscilloscope

- Bruit gaussien : écart type =  $v_n$  (+ contrôle du bruit cohérent)

- Vérifier que le système de mesure (filtre, oscillo) a une contribution négligeable (éteindre le préampli et remesurer, au besoin soustraire quadratiquement le bruit de 2ème étage)

- Il est important de mesurer le bruit dans les mêmes conditions que le signal

# Mesure de la charge équivalente de bruit (2)

- Mesure du signal :  $V_{\max}(\delta)$

- On injecte une charge connue (impulse)  $Q_0\delta(t)$ ,

- En sortie :  $V_{\max}(\delta) = C_{\text{inj}} V_0 / C_f$

- on mesure aussi le peaking time 5-100% :  $t_p(\delta)$  pour tenir compte du temps de montée du préampli

- Equivalent Noise Charge : ENC

- $\text{ENC} = V_{\text{rms}} / V_{\max}(\delta)$

- Exprimé en général en électrons rms

- On varie le shaping time réglable du shaper CRRC<sup>2</sup>

- On varie la capacité détecteur  $C_d$  ajoutée sur l'entrée

- On fit le bruit série  $A/\sqrt{\tau_p}$ , le bruit parallèle  $B\sqrt{\tau_p}$  et le 1/f : C

- On trace A en fonction de  $C_d$  : droite  $A = 181 \cdot e_n C_d$

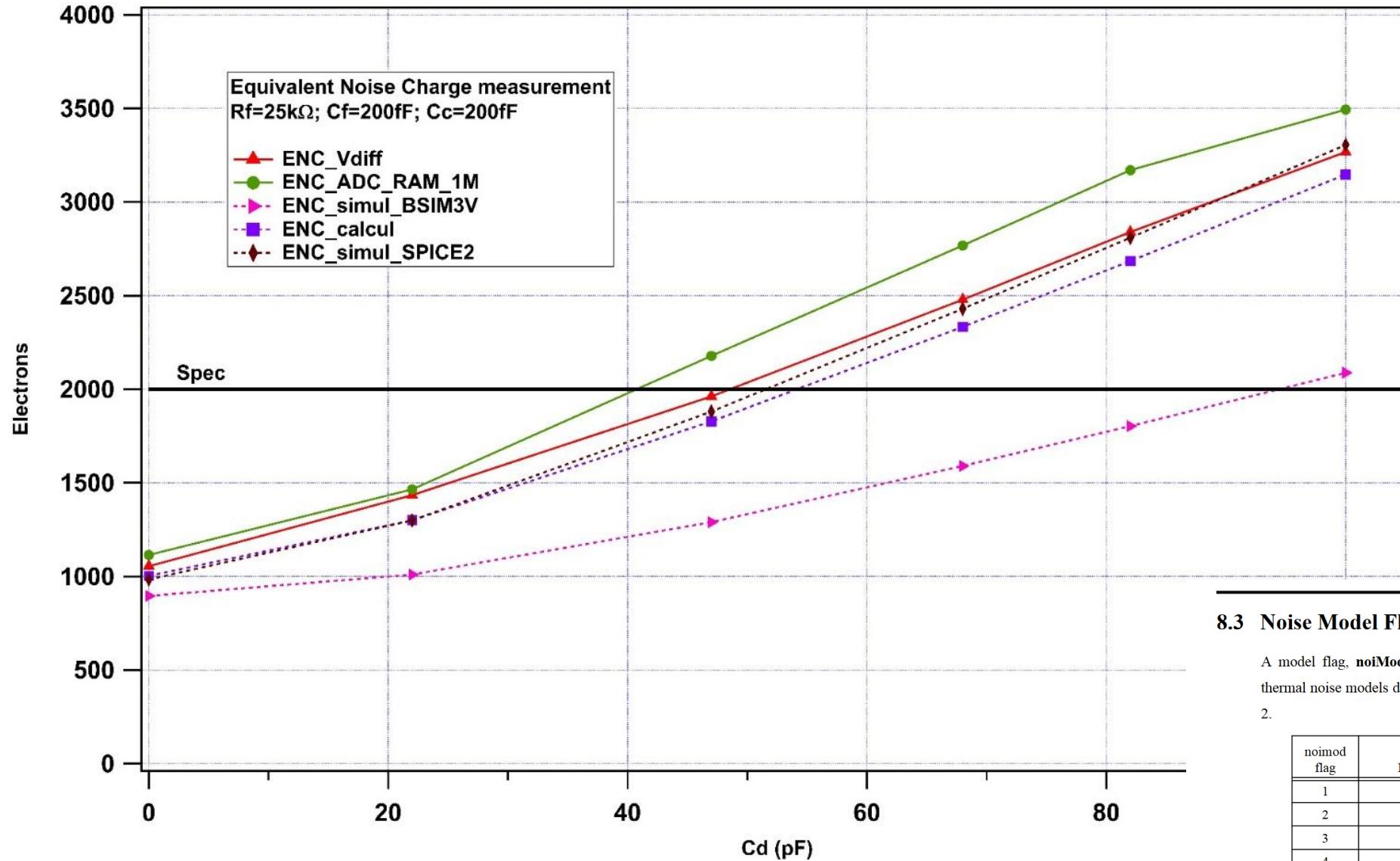

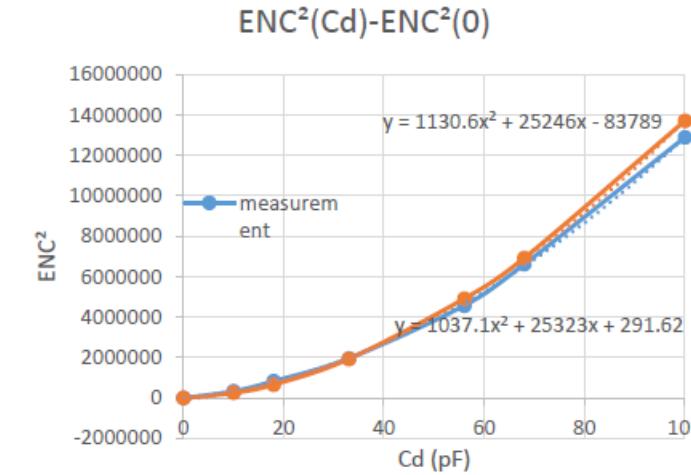

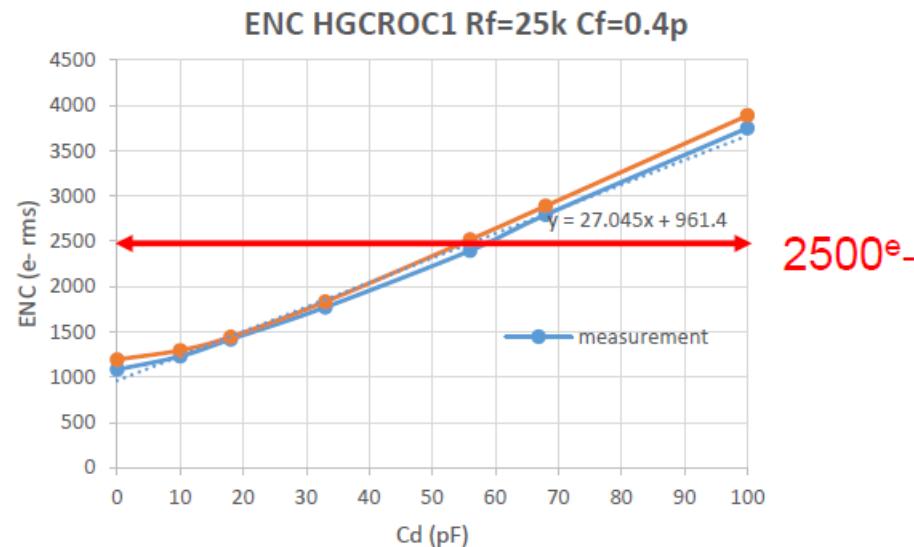

# Extraction du bruit série et de la capa d'entrée du préamp

- Mesure de ENC après un filtre CRRC<sup>2</sup> variable

- On varie la capacité détecteur  $C_d$  ajoutée sur l'entrée

- Quadratique fit de ENC<sup>2</sup> donne  $e_n$  et  $C_{pa}$

- $ENC^2(C_d) - ENC^2(0) = A \frac{e_n^2}{\tau_p} (C_d^2 + 2C_d C_{pa}) = \alpha C_d^2 + \beta C_d$

- $\rightarrow e_n = \sqrt{\frac{\alpha \tau_p}{A}}$  et  $C_{pa} = \frac{\beta}{2\alpha}$

- Ici on a  $e_n = 0.79 \text{ nV}/\sqrt{\text{Hz}}$  et  $C_{pa} = 12.5 \text{ pF}$  en mesure ( $e_n = 0.75 \text{ nV}/\sqrt{\text{Hz}}$  en simulation)

- Le préamp contribue à 75% du bruit total

$$ENC^2 = A_i \cdot Si \tau + A_v \cdot Sv \cdot \frac{C_d^2}{\tau} + SecondStage$$

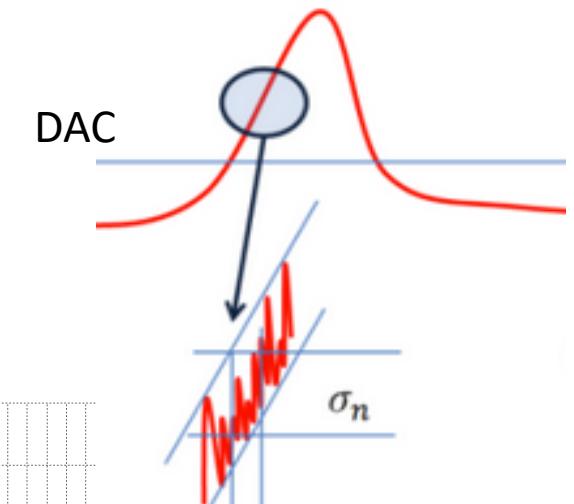

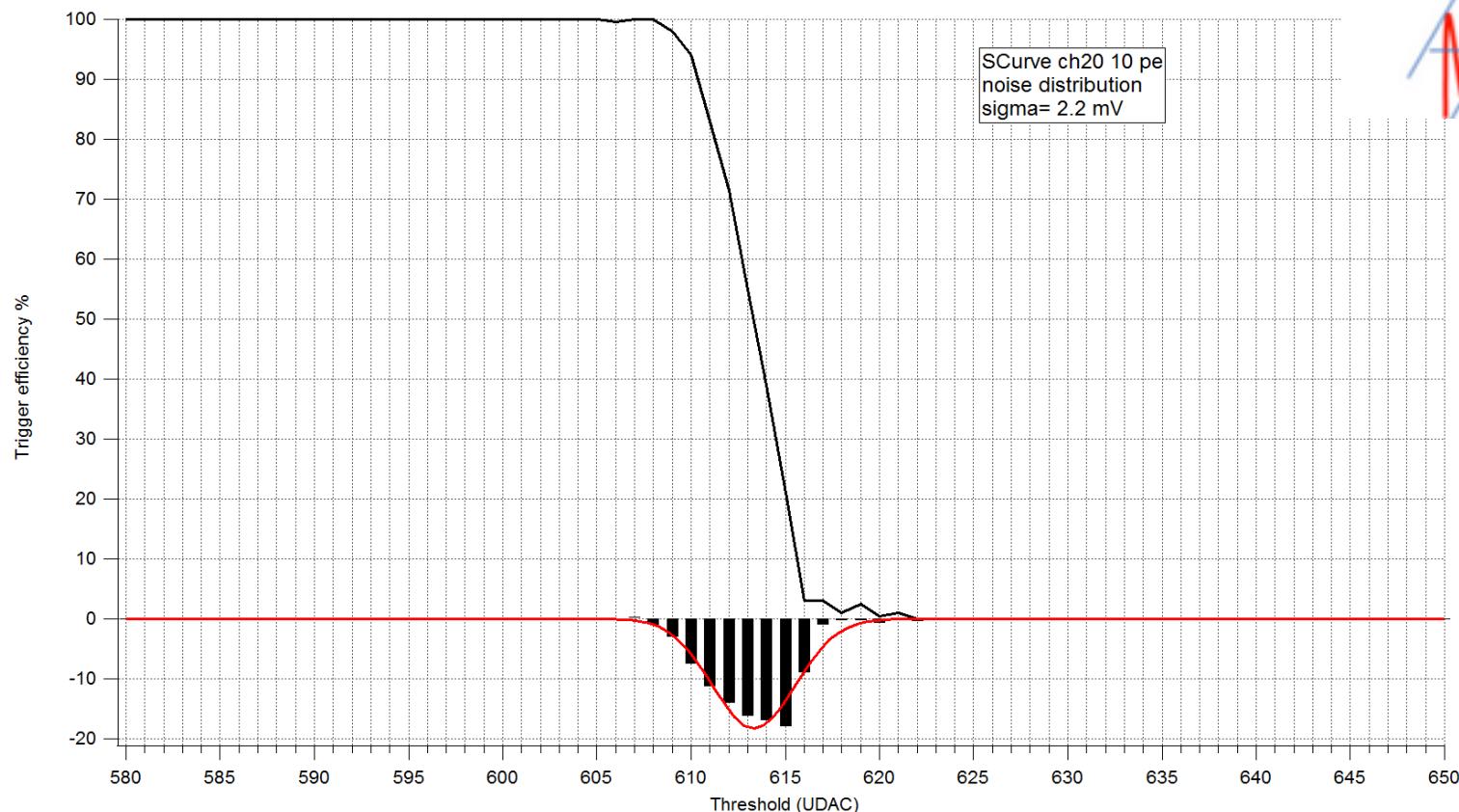

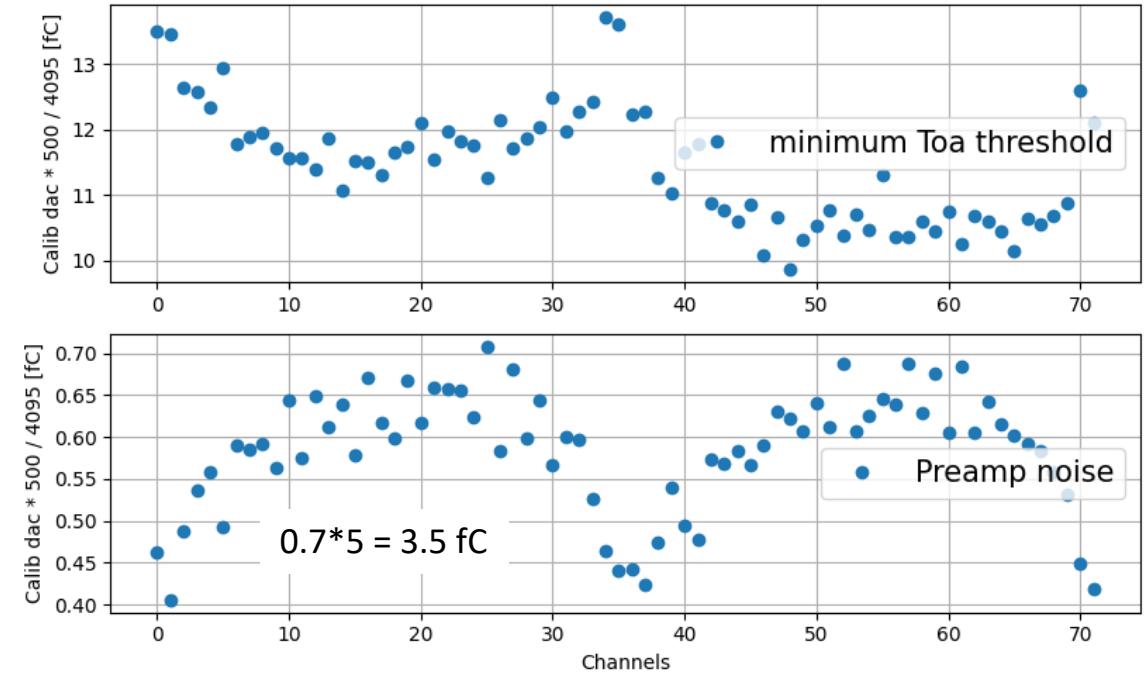

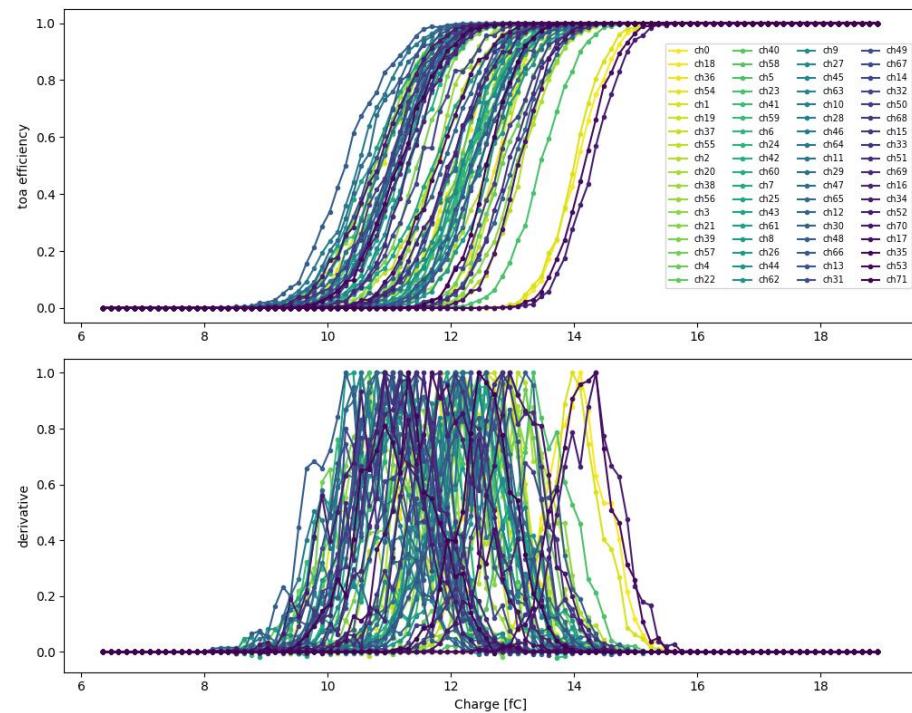

# Trigger efficiency

- Préamp + discriminateur = tracker electronics

- Scan du DAC produit une « S-Curve »

- La dérivée donne l'enveloppe du bruit

# Mesure du bruit en sortie de preamp

Sans shaper et sans ADC, on peut mesurer le bruit avec un discri

- En scannant le seuil autour du pedestal, on peut déterminer le seuil minimal de déclenchement

- En variant l'injection à un seuil fixe, on peut évaluer le gain en sortie du préamp

- La pente des S-curve nous donne aussi la mesure de l'enveloppe du bruit

Bruit numérique puisque seuil minimum > 5\*bruit

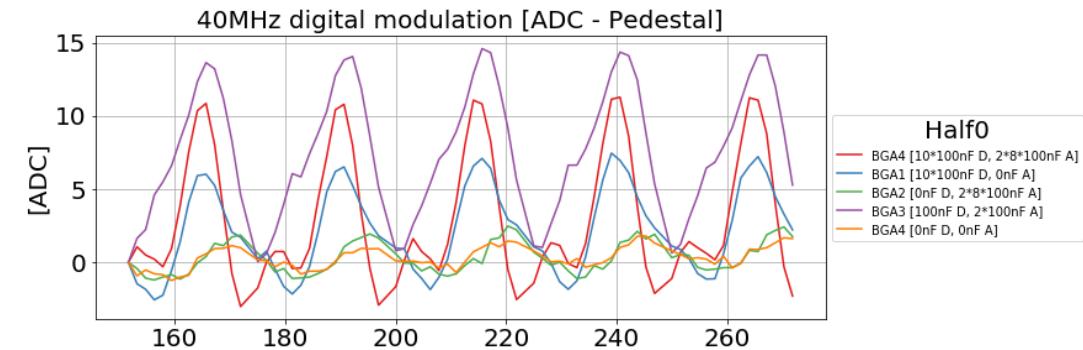

# Bruit numérique

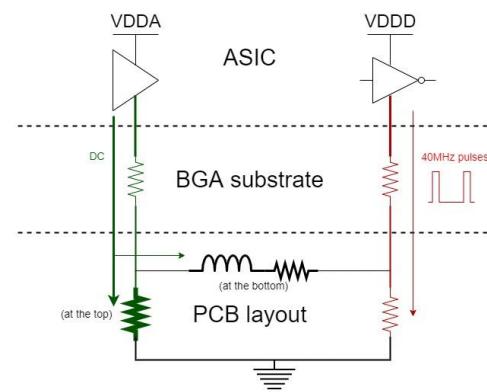

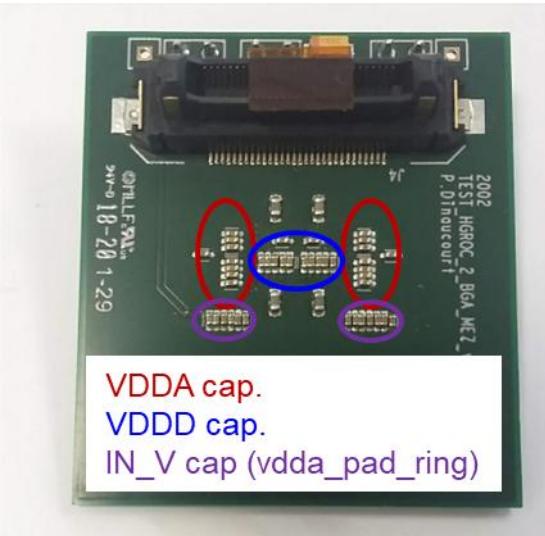

- Le front-end analogique est très sensible à la masse et à la tension de Bias du sensor

- Gain =  $C_{\text{det}}/C_{f,\text{pa}} > 100$ ,  $10 \mu\text{V}$  sur la masse →  $1 \text{ mV}$  en sortie du préamp

- Masse doit être très basse impédance → plans de masse au-dessus et en-dessous des entrées

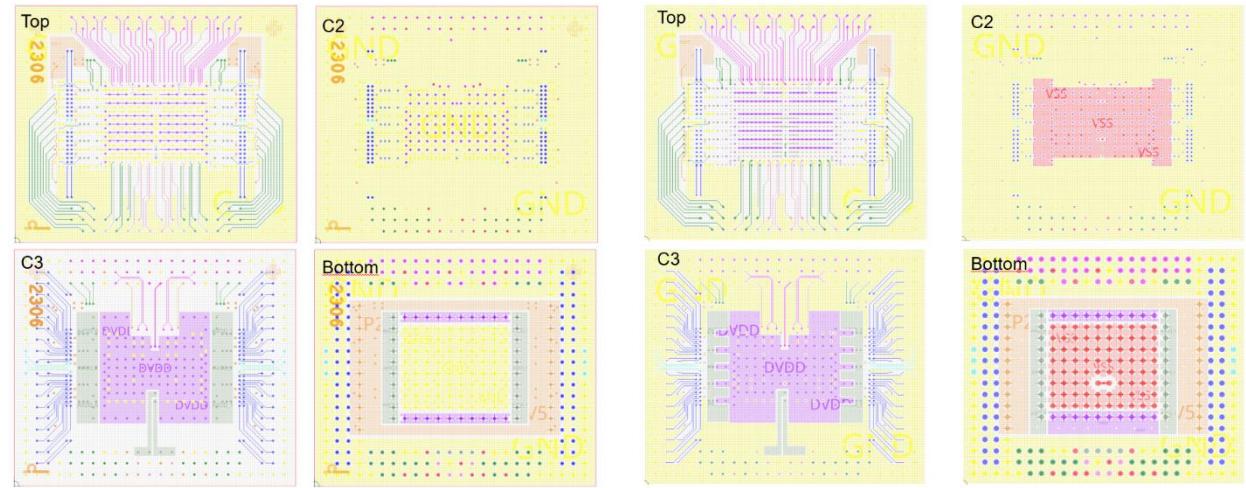

Half0

— BGA1 [10\*100nF D, 2\*8\*100nF A]

— BGA1 [10\*100nF D, 0nF A]

— BGA2 [0nF D, 2\*8\*100nF A]

— BGA3 [100nF D, 2\*100nF A]

— BGA4 [0nF D, 0nF A]

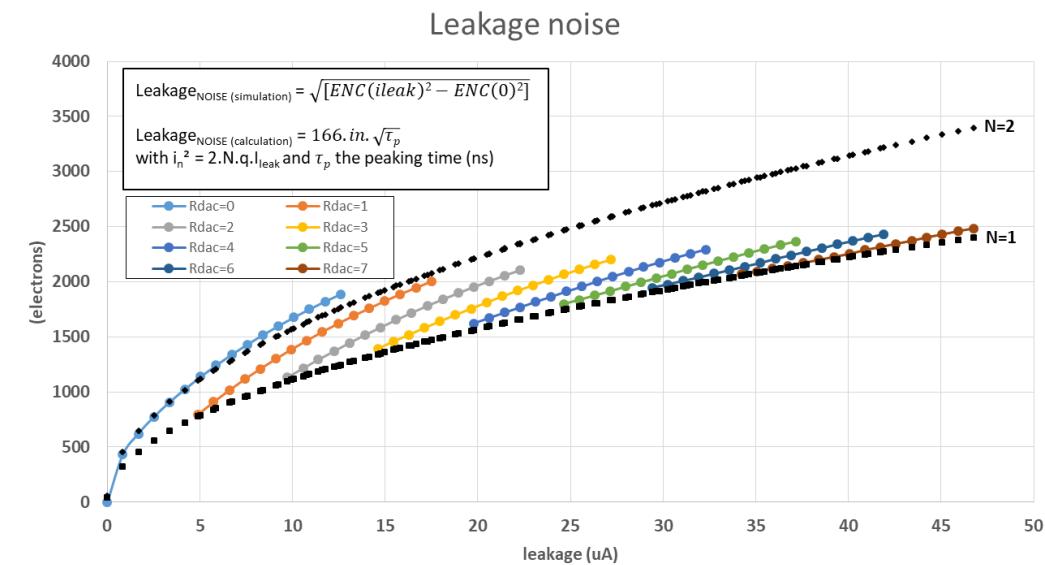

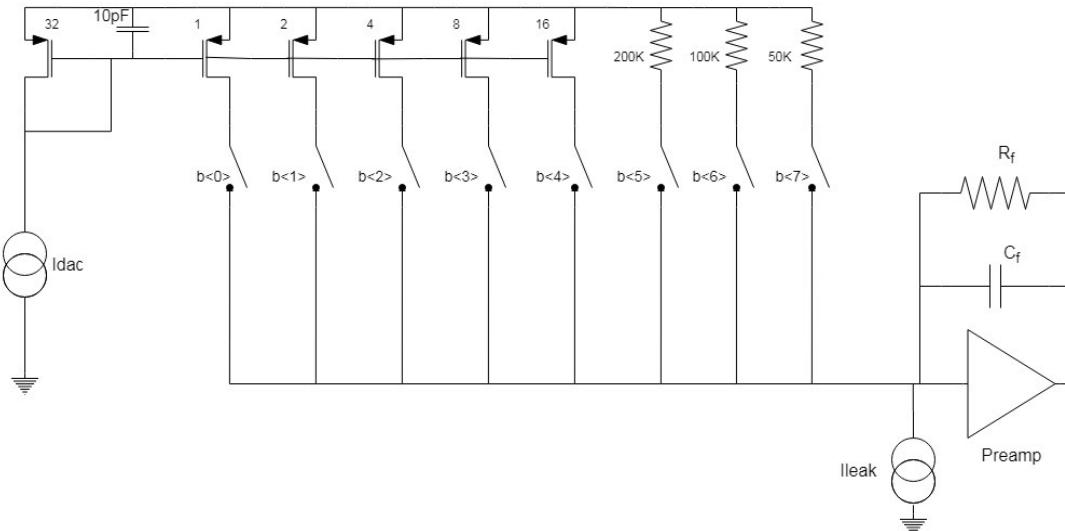

# DAC d'entrée pour compenser le courant de fuite du détecteur

- Le sensor peut avoir un courant de fuite qui contribue principalement au bruit parallèle

- Augmente avec les irradiations

- Nécessité de le compenser en ajoutant un courant opposé

- Le courant de fuite et le courant du DAC contribue au bruit parallèle

- Réglage fin effectué avec un DAC de courant basé sur des miroirs de courant

- $i_n^2 = 2qi$

- Ajouter des capas de découplage ( $> 10 \text{ pF}$ ) pour filtrer la contribution des étages amonts du DAC

- Pour de plus grands courant à compenser, on peut utiliser des résistances

- $\frac{4kT}{R} > 2qi$

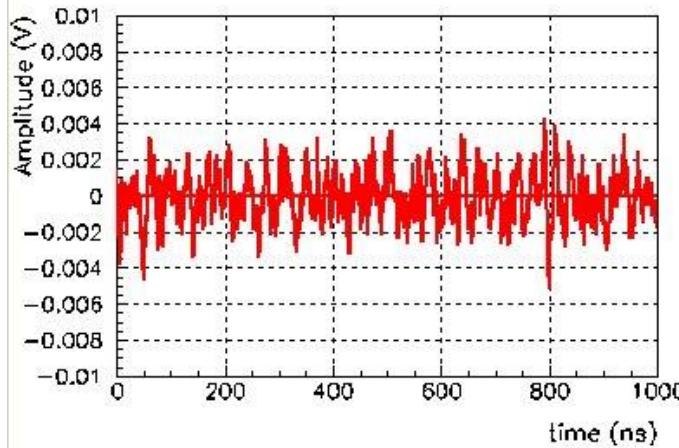

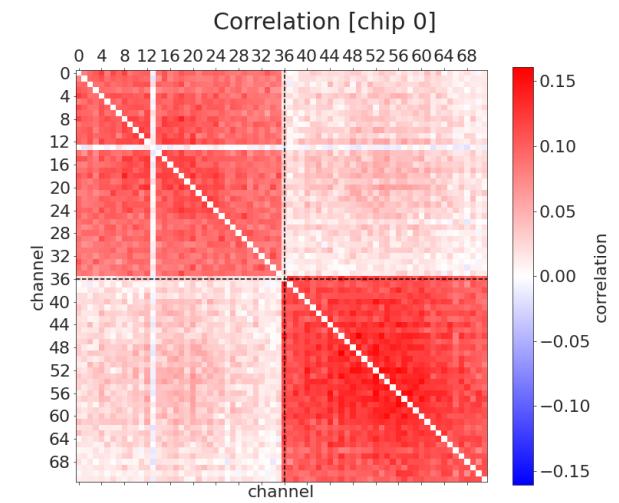

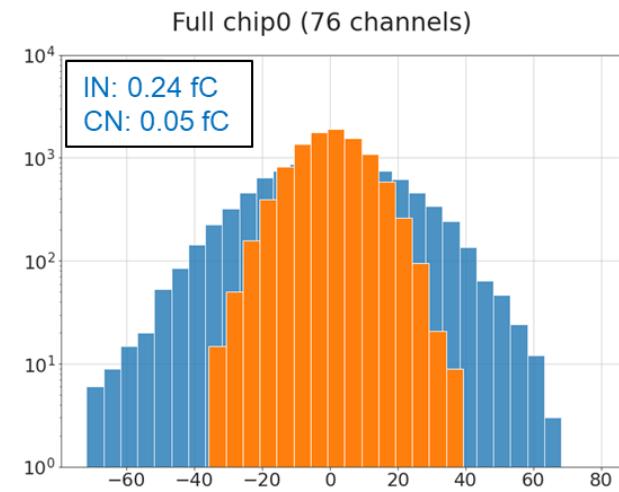

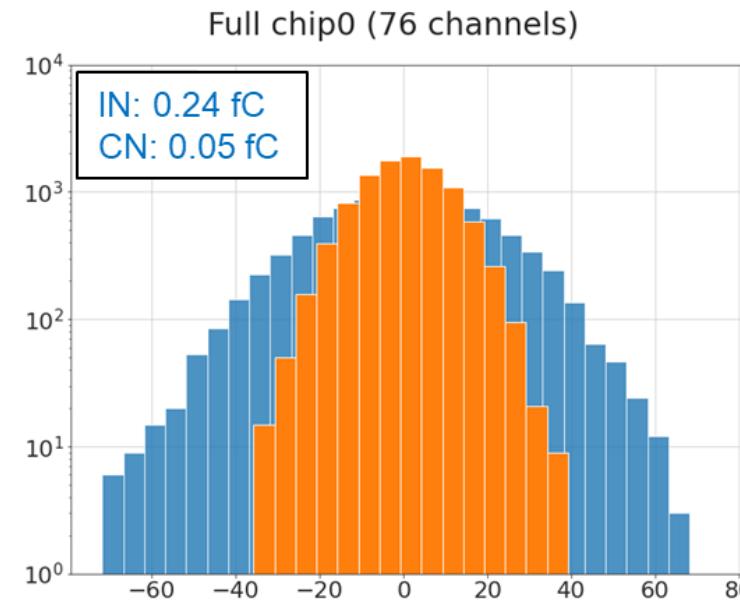

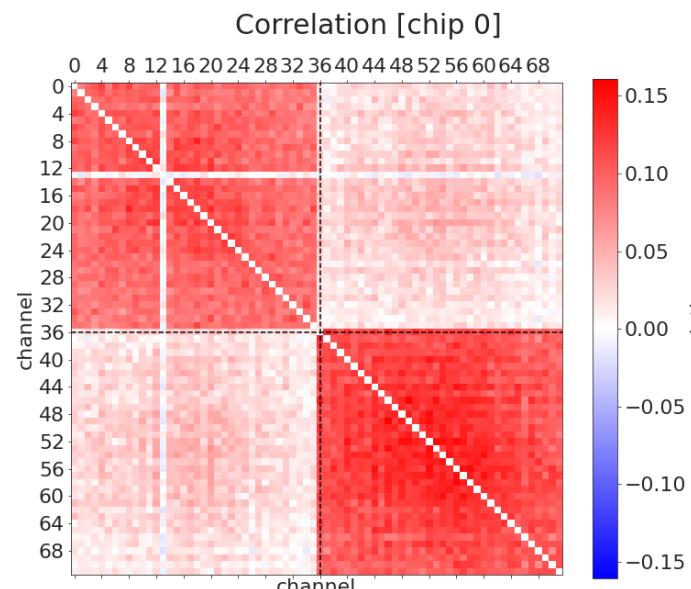

# Bruit corrélé

- Il peut y avoir une source de bruit cohérente, qui se retrouve sur toutes les voies

- Plusieurs techniques permettent de l'évaluer

- La matrice de correlation: coefficient de correlation entre voies du circuit

- Bruit coherent extrait à partir des sommes directes et alternées de N (pair) voies

$DS = \sum ped[i]$ ;  $AS = \sum (-1^i)ped[i]$

- Le bruit coherent est égal à  $CN = \sqrt{var(DS) - var(AS)}/n$

- Le bruit incoherent est égal à  $IN = rms(AS)/\sqrt{n}$

- L'autocorrélation permet aussi de voir si un bruit cohérent (clock) est présent

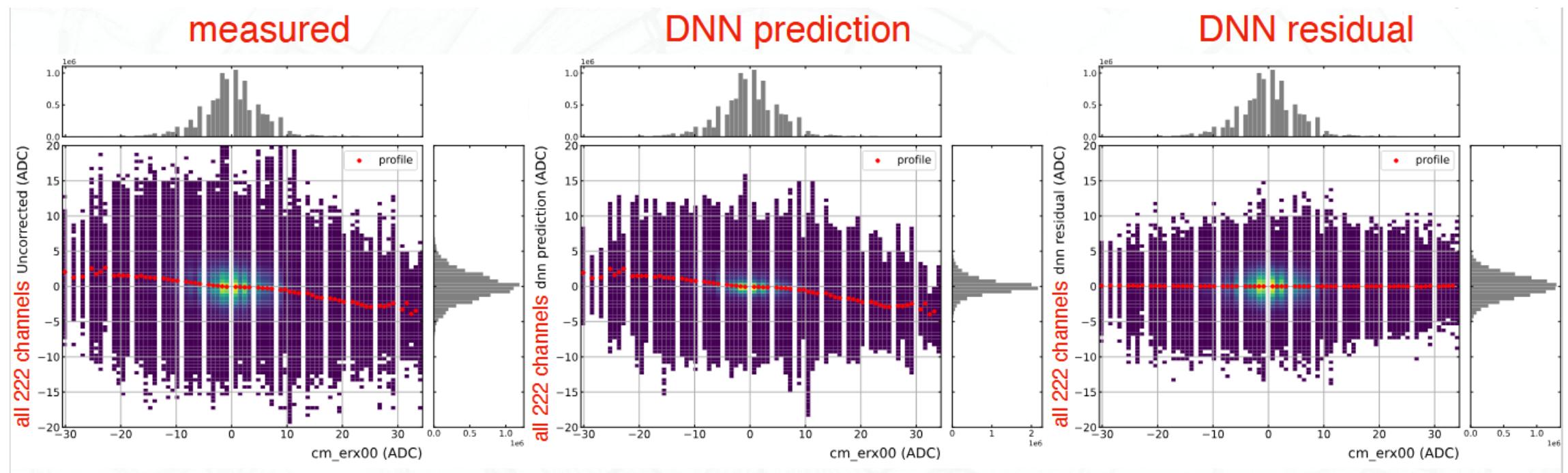

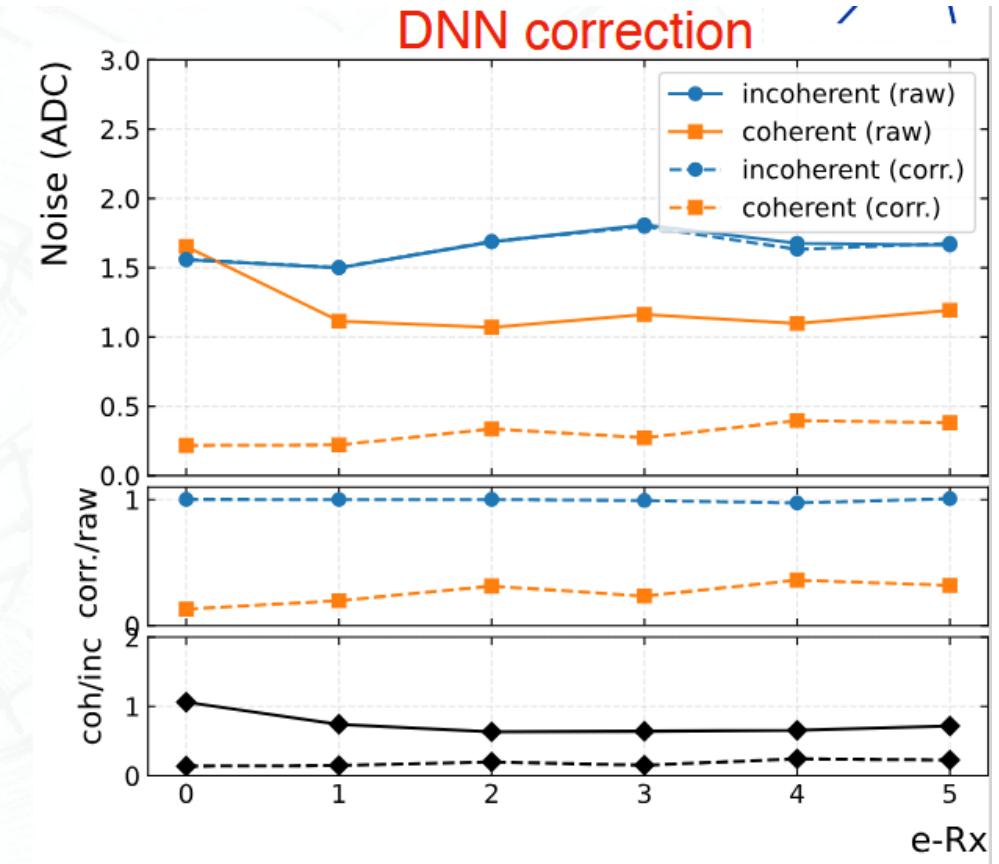

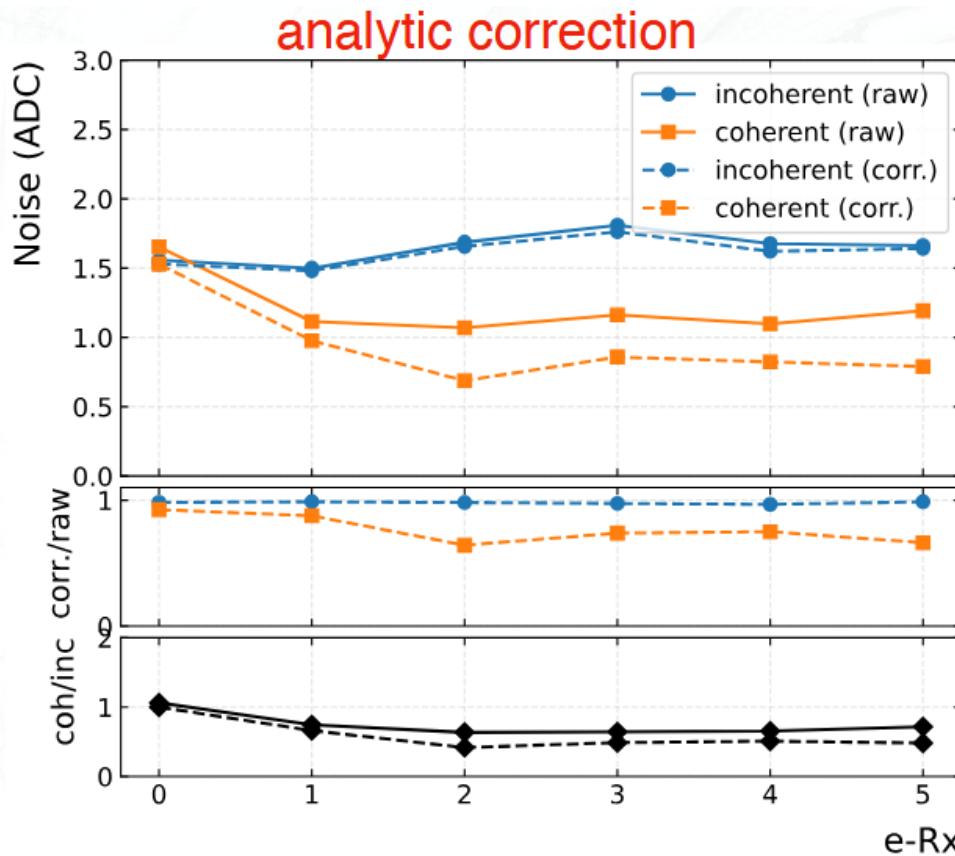

# Bruit corrélé dans les systèmes plus complexes

- On utilise des voies spéciales, CM, qui suivent le bruit de mode commun mais qui ne reçoivent jamais de signal

- On peut utiliser les réseaux de neurone pour évaluer le bruit cohérent et le soustraire du bruit pour améliorer la mesure

- Meilleurs résultats que la simple méthode analytique:  $ADC_i \rightarrow ADC_i - \rho_i (ADC_{CM} - \langle ADC_{CM} \rangle)$

# Bruit corrélé dans les systèmes plus complexes

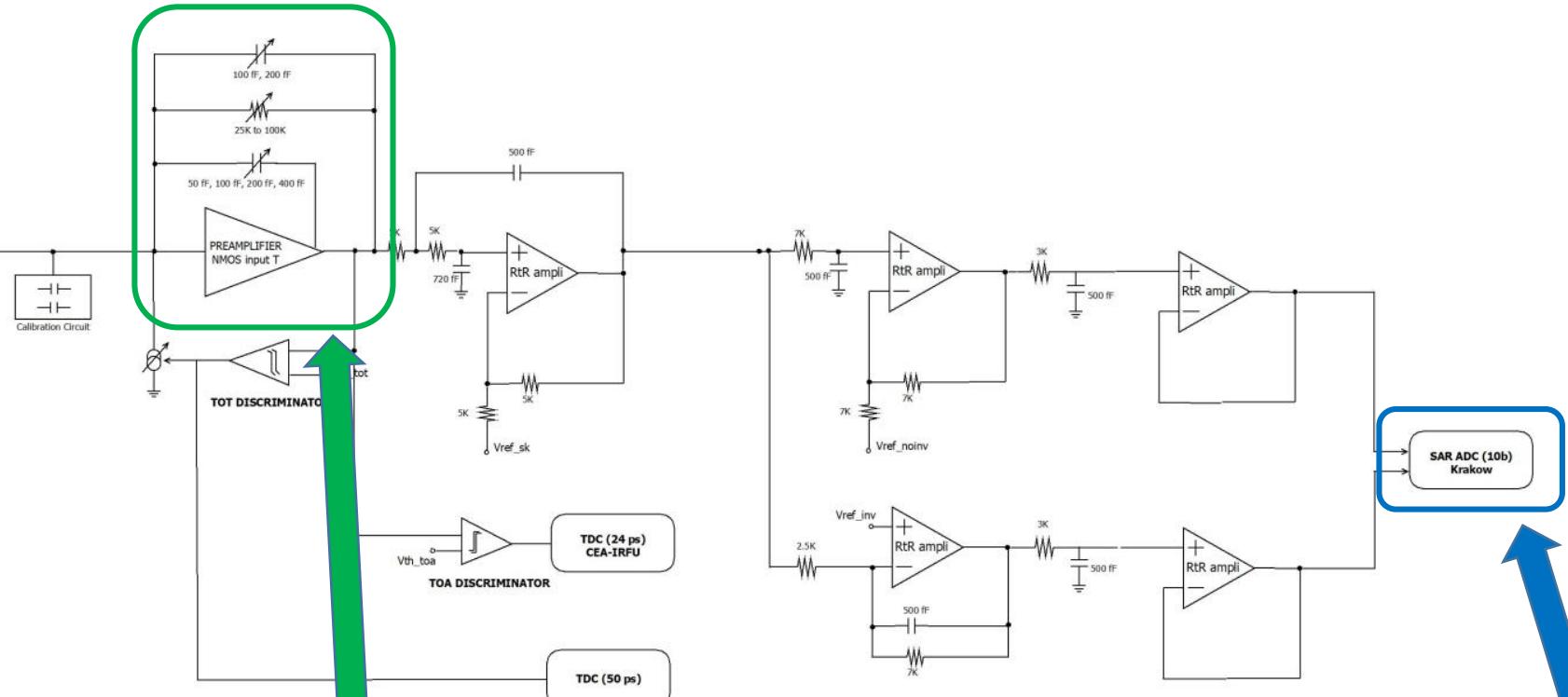

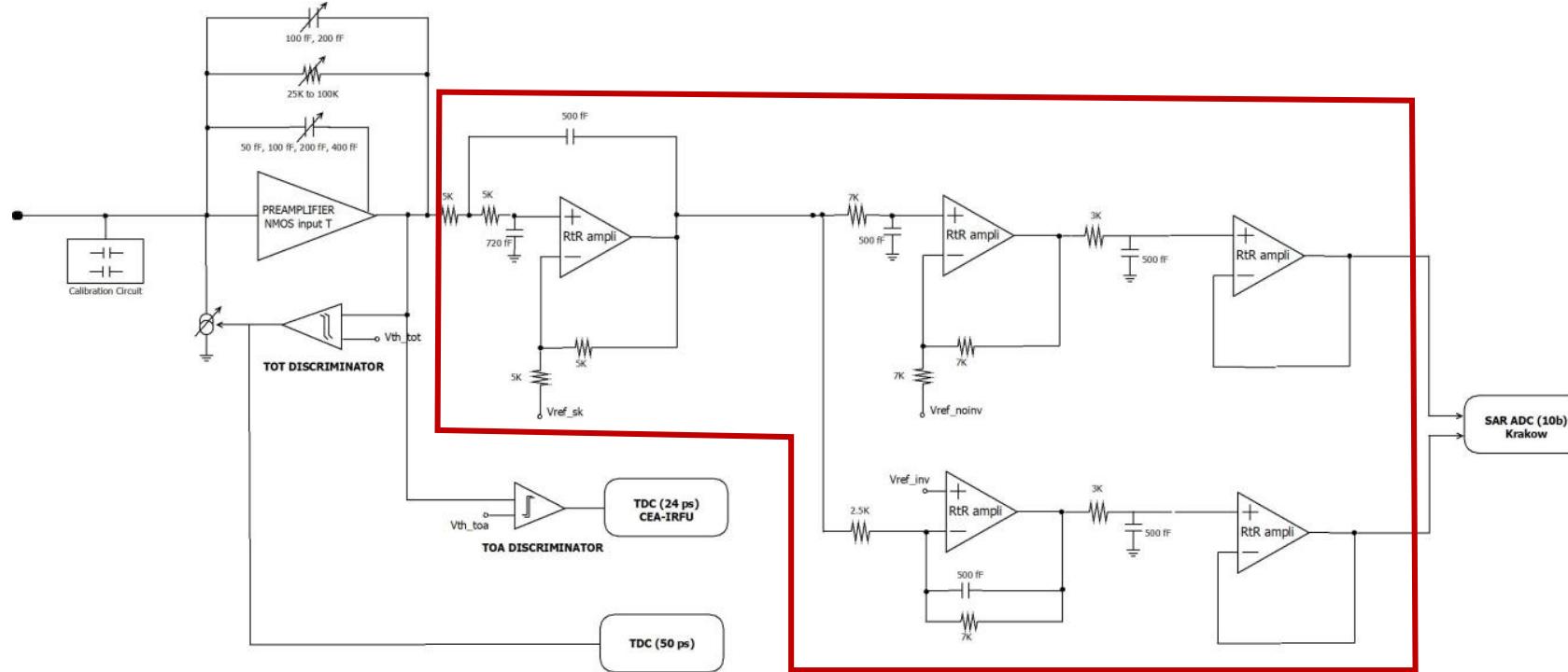

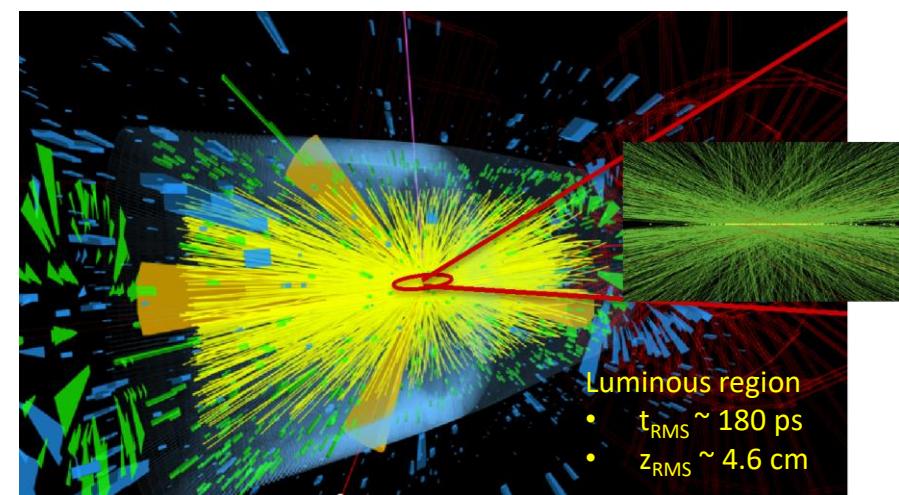

# Besoin de la mesure de temps

- Time resolution <50ps required by many experiments/applications keeping low power, large dynamic range ....

- **PET/ Time of Flight measurements (SiPM)**

- Dynamic range : 1 pe (100fC) up to 3000 pe (300 pC)

- Time resolution <100ps

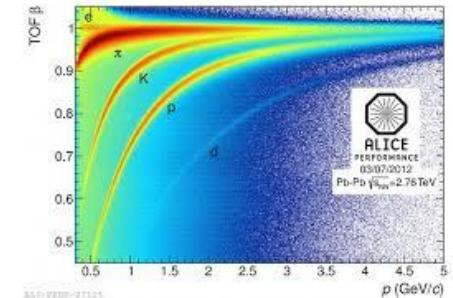

- **ALICE TOF (Time of Flight)**

- MRPCs

- Particle identification with S PTR  $\sim$  100-300 ps

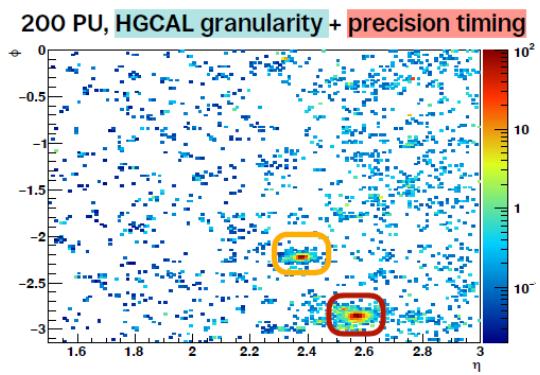

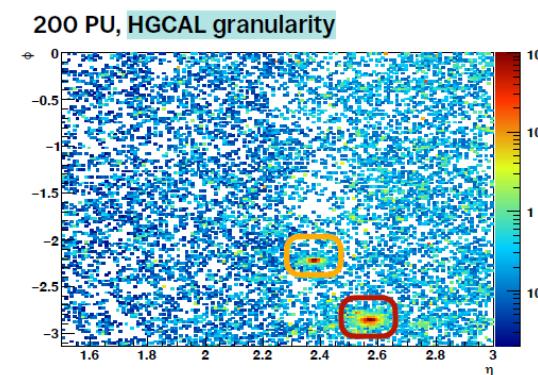

- **CMS High Granularity CALorimeter: (Si pin diodes)**

- Large dynamic range : few fC up to  $\sim$ 10 pC

- Calorimetry => Precision /linearity  $<$  1%

- Fast timing ability  $\sim$ 50ps (for  $>$  10 mips desirable)

- Peaking time 15-20 ns (minimize noise, minimise Out of Time pileup)

- Power on detector  $<$   $\sim$ 10 mW/channel all included

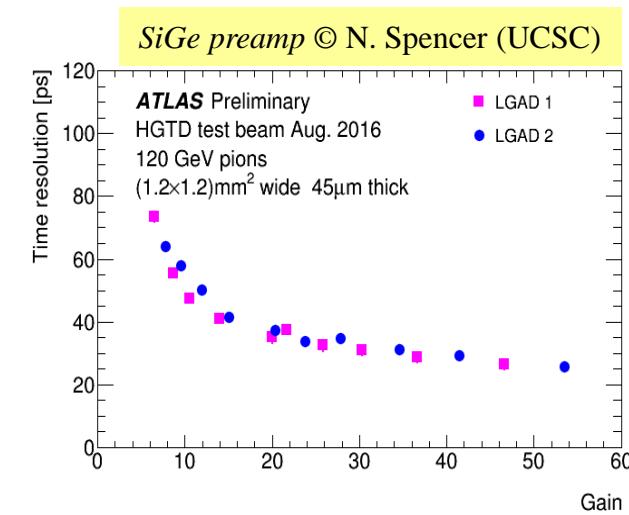

- **Timing Detector (LGAD)**

- ATLAS et CMS

- Time performance  $\sim$ 30 ps : To reject Time Pile up events => better particle identification

Target for timing performance: resolution of 30ps

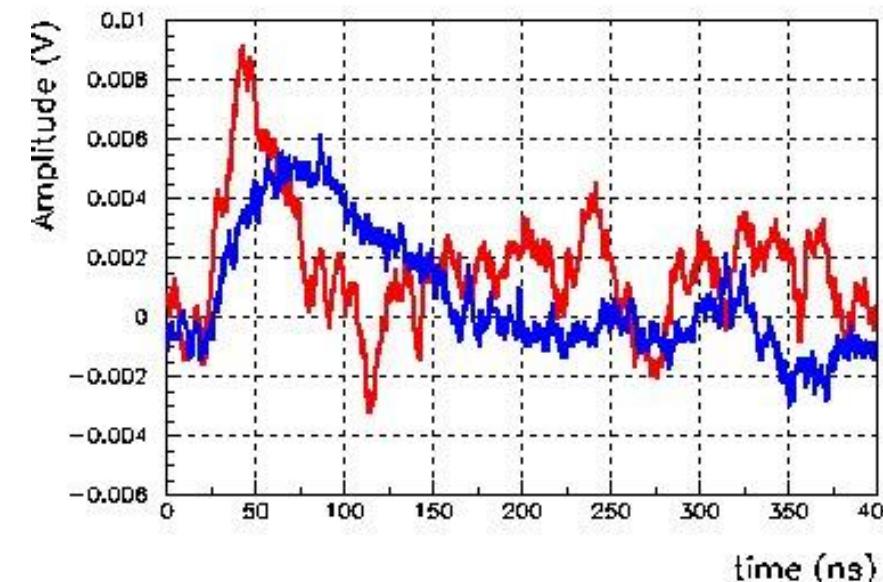

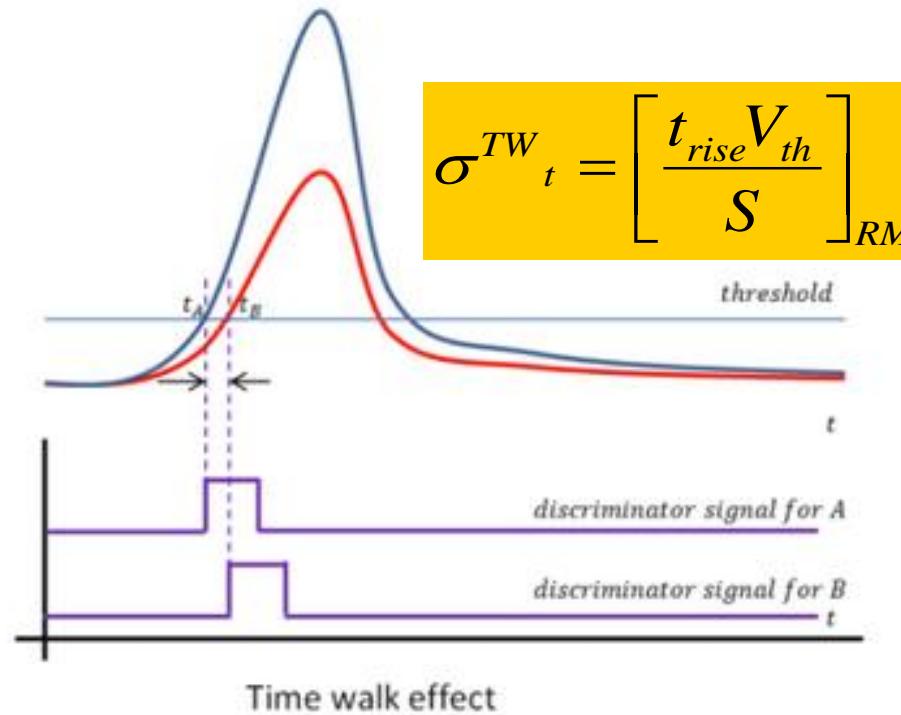

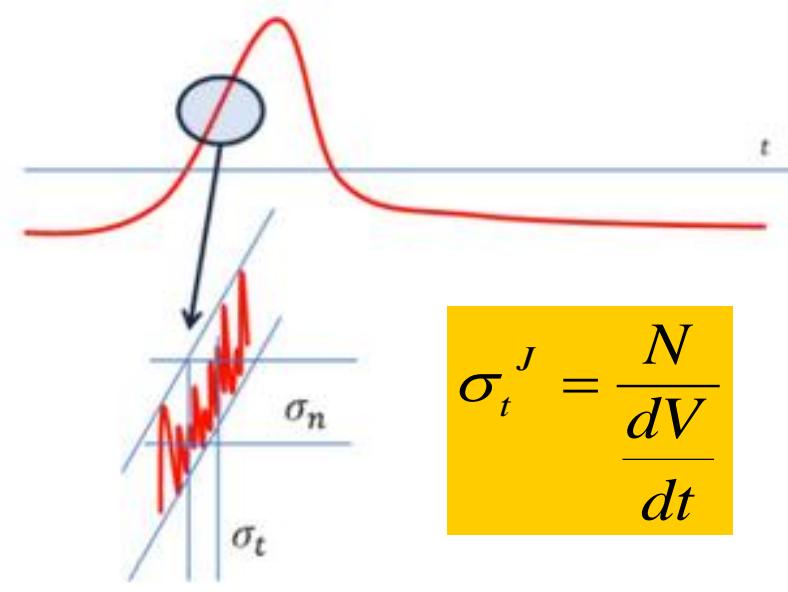

# Time walk and time jitter

**Time walk:** the voltage value  $V_0$  is reached at different time for signal of different amplitudes

Time walk effect

**Jitter:** the noise is summed to the signal, causing amplitude variations

$$\sigma_t = \frac{N}{dV} \frac{dt}{\sqrt{12}}$$

Jitter effect

Due to the physics of signal formation

$$\sigma_t^2 = \left( \frac{t_{rise}}{S/N} \right)^2 + \left( \left[ \frac{t_{rise} V_{th}}{S} \right]_{RMS} \right)^2 + \left( \frac{TDC_{bin}}{\sqrt{12}} \right)^2$$

**Jitter** **Time Walk** **TDC**

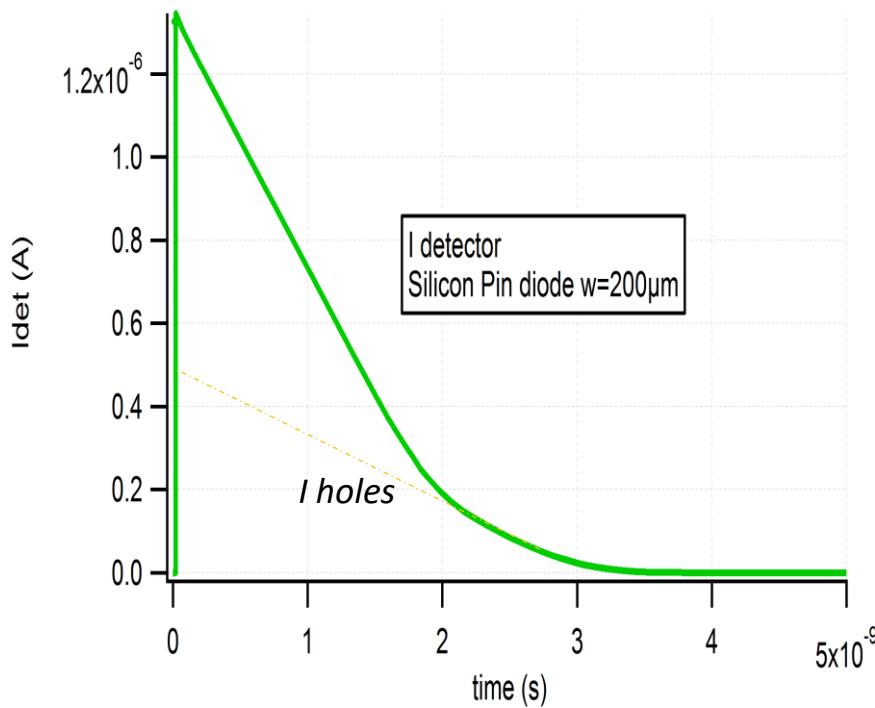

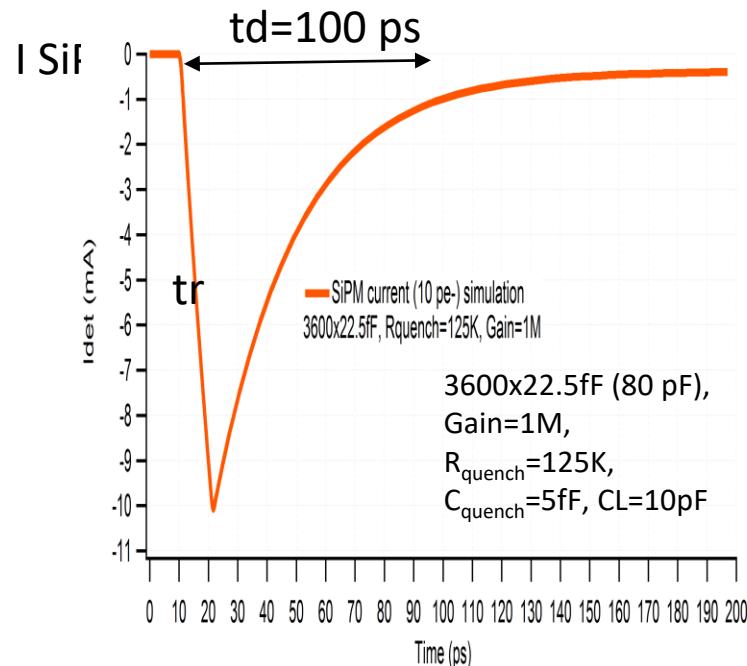

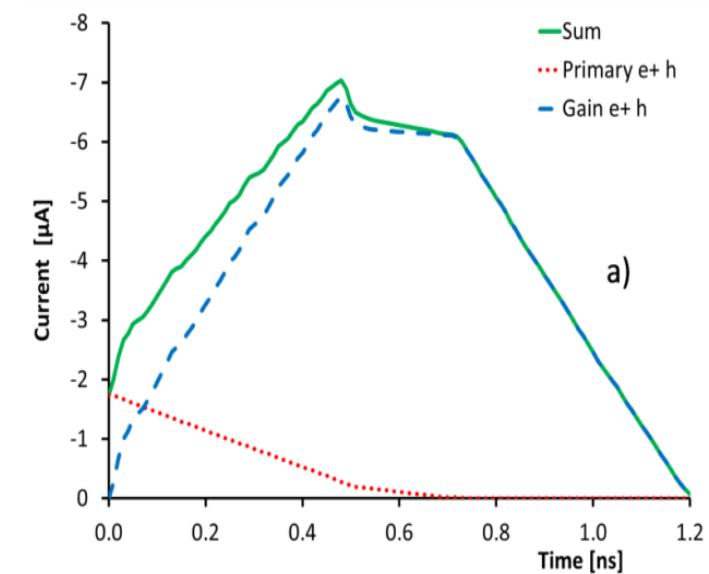

# Detector current

- PN diode  $w = 200 \mu\text{m}$

- Very short rise time :  $t_r \sim 10 \text{ ps}$

- Relatively long «drift time» :  $t_d \sim 2 \text{ ns}$

- SiPM detector (10 pe-)

- very short rise time :  $t_r \sim 10 \text{ ps}$

- Short duration :  $t_d \sim 100 \text{ ps}$

- LGAD sensor  $w = 50\mu\text{m}$

- rise time :  $t_r \sim 500\text{ps}$

- Decay time» :  $t_d \sim 700\text{ps}$

# Signal et bruit dans un Broadband amplifier

- Broadband amplifiers: amplificateur en boucle ouverte (source commune)

- Durée du signal  $t_d$  à travers la capa  $C_d$  avec un broadband d'impédance d'entrée  $R_0$

- Signal va avec  $1/ C_d$  si  $R_0 C_d \gg t_d$  and  $C_{PA} \ll C_d$

$$S = V_{OUT} = G \frac{Q_{IN}}{C_d}$$

- Le temps de montée est la convolution de  $t_d$  et du temps de montée de l'ampli  $t_{10-90\_PA}$

$$\frac{dV}{dt} = \frac{G \cdot Q_{in}}{C_d \sqrt{t_{10-90\_PA}^2 + t_d^2}}$$

- Bruit indépendant de  $C_d$  (entrée en tension)

$$N = G \cdot e_n \sqrt{\frac{\pi}{2} BW} = G \cdot e_n \sqrt{\frac{\pi}{2} \frac{0.35}{t_{10-90\_PA}}} = \frac{G \cdot e_n}{\sqrt{2t_{10-90\_PA}}}$$

$$t_r = t_{10-90\%} = 2.2\tau$$

$$f_{-3dB} = \frac{1}{2\pi\tau} = \frac{0.35}{t_{10-90\%}}$$

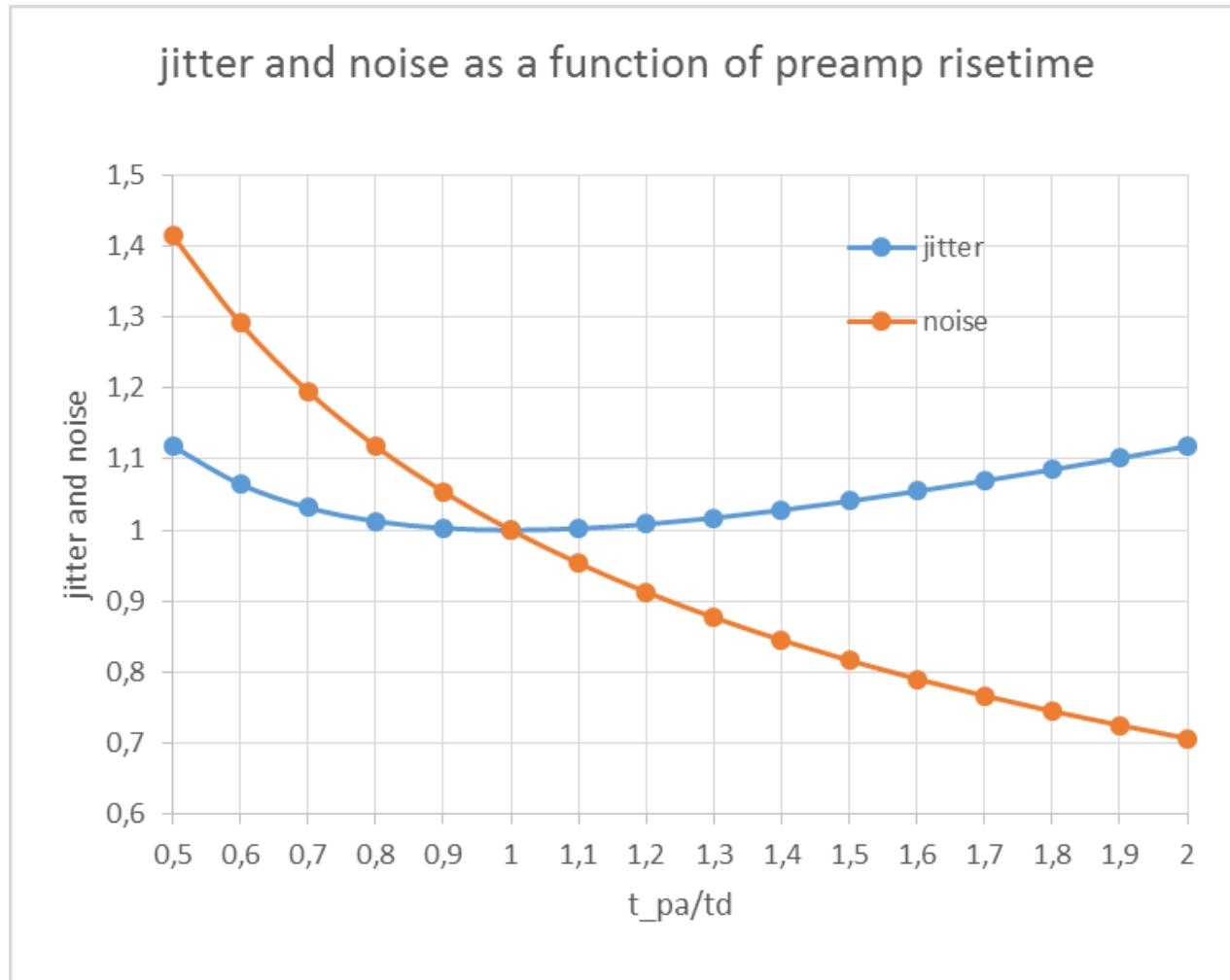

# Jitter et seuil minimum de détection

- Jitter n'est pas trop dégradé si tpa jusqu'à  $2 \times \text{td}$

- Par contre le bruit augmente vite avec un préamp trop rapide

- Seuil minimum

$$\sigma_t = \frac{e_n C_d}{Q_{in}} \sqrt{\frac{t_{10-90\_PA}^2 + t_d^2}{2t_{10-90\_PA}}}$$

$$N = \frac{G \cdot e_n}{\sqrt{2t_{10-90\_PA}}}$$

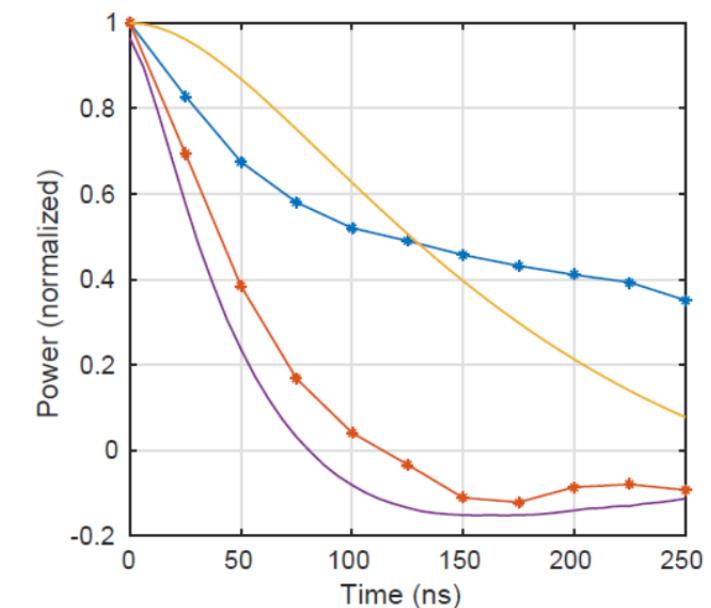

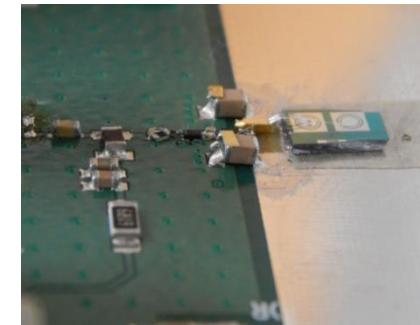

# Examples (obtenus en test beam)

- NA62 tracker : PIN diode thickness 300  $\mu\text{m}$  A=0.09  $\text{mm}^2$

- $C_d = 0.1 \text{ pF}$   $e_n = 11 \text{ nV}/\sqrt{\text{Hz}}$   $t_d = 3 \text{ ns}$   $\sigma = 60 \text{ ps}/\text{Q(fC)}$

- 1 MIP = 3 fC =>  $\sigma = 20 \text{ ps}/\#\text{MIP}$  (~60-200 ps measured)

- CMS HGCAL : PIN diode thickness 300  $\mu\text{m}$  A=25  $\text{mm}^2$

- $C_d = 8 \text{ pF}$   $e_n = 1 \text{ nV}/\sqrt{\text{Hz}}$   $t_d = 3 \text{ ns}$   $\sigma = 420 \text{ ps}/\text{Q(fC)}$

- 1 MIP = 3.8 fC =>  $\sigma = 110 \text{ ps}/\#\text{MIP}$  (~200 ps measured)

- ATLAS HGTD : LGAD diode thickness 50  $\mu\text{m}$  A= 2  $\text{mm}^2$  G = 10

- $C_d = 2 \text{ pF}$   $e_n = 2 \text{ nV}/\sqrt{\text{Hz}}$   $t_d = 0.5 \text{ ns}$   $\sigma = 50 \text{ ps}/\text{Q(fC)}$

- 1 MIP = 5 fC (G=10) =>  $\sigma = 10 \text{ ps}/\#\text{MIP}$  (~40 ps measured)

- SiPM G = 1<sup>E</sup>6

- $C_d = 300 \text{ pF}$   $e_n = 1 \text{ nV}/\sqrt{\text{Hz}}$   $t_d = 100 \text{ ps}$   $\sigma = 3 \text{ ns}/\text{Q(fC)}$

- 1 pe = 160 fC =>  $\sigma = 20 \text{ ps}/\#\text{pe}$  (~60 ps measured)

$$\sigma_t^J = \frac{e_n C_d}{Q_{in}} \sqrt{t_d}$$

*Et des TDC....*

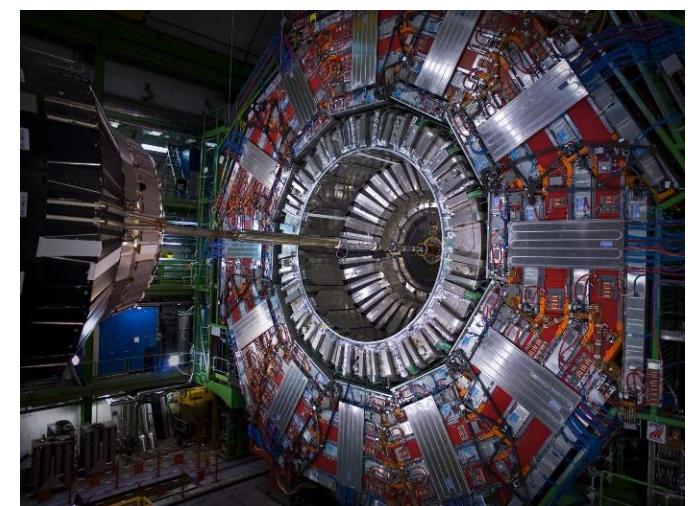

# Designer pour tenir aux radiations

# Plan du cours

- Introduction: de l'électronique partout dans nos détecteurs

- Fondamentaux de l'électronique

- Rappel général des bases de l'électronique

- Détecteur et préamplificateur

- Conversion Analogique/Numérique

- Numérique

- Le langage HDL (VHDL ou Verilog), synthèse, vérification

- De plus en plus de numérique dans les ASICs

- Design Flow: Analog-on-Top ou Digital-on-Top

- Bruit électronique

- Fondamentaux

- Filtrage, shaping

- Techniques de mesure

- **Effets des radiations sur l'électronique**

- **TID et SEE**

- **Campagnes d'irradiation, performances, cross-section**

- Extrême importance des tests: sur table, radiation, beam, système

- La mesure de temps

- Généralité

- Les TDCs

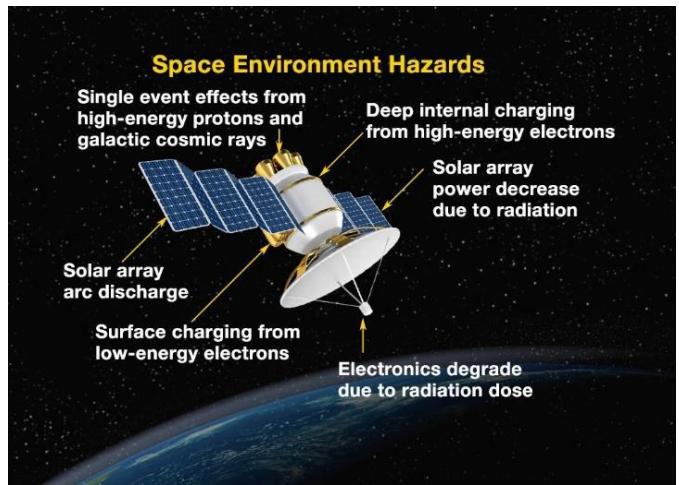

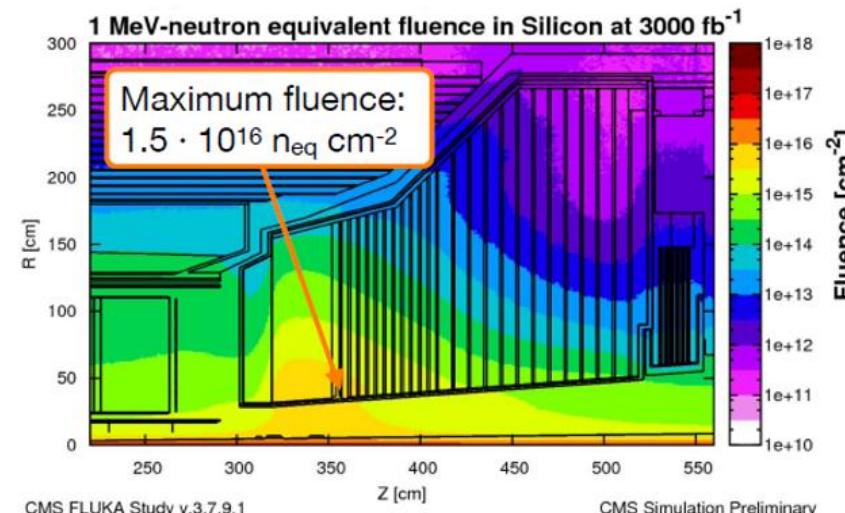

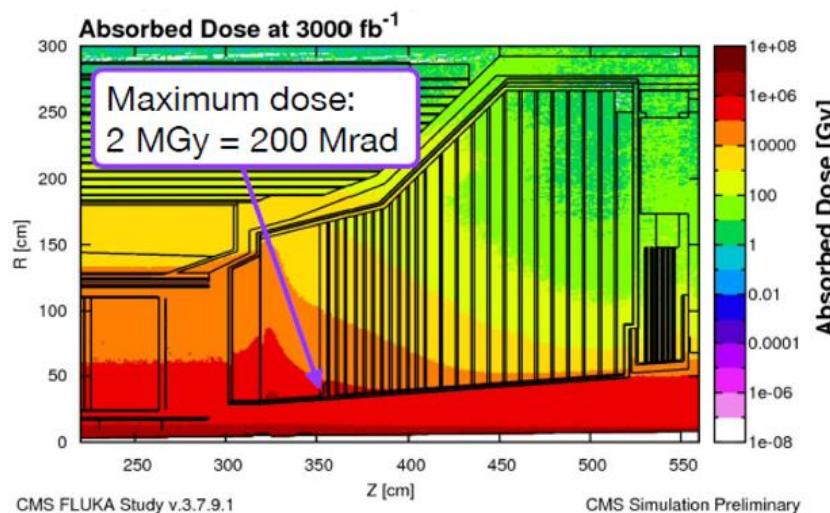

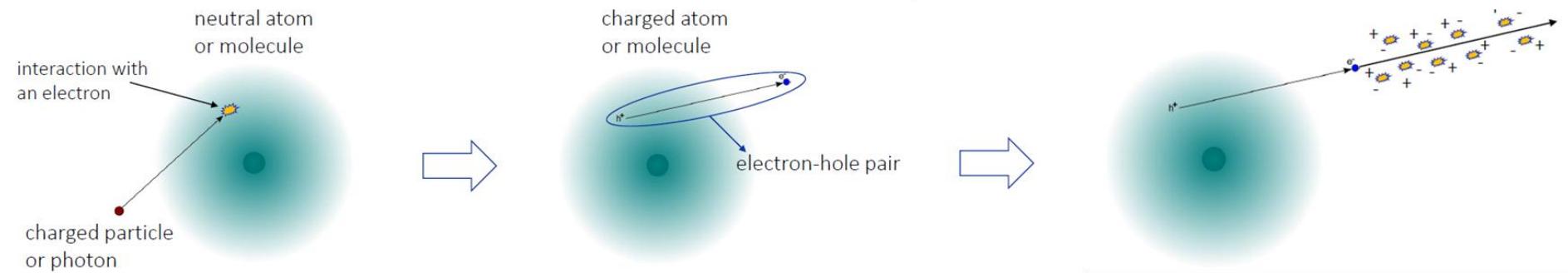

# Différents effets des radiations

- Total Ionizing Dose (TID): accumulation de charge dans l'oxyde d'un composant électronique

- $J/kg = \text{Gray (Gy)}$ ,  $\text{rad} = 100 \text{ Gy}$

- Single-Events Effects: SEU, SET, SEL, etc.

- Displacement Damage: Non Ionizing Energy Loss (NIEL)

- Dommage dans le cristal avec des neutrons

**Total Ionising Dose (TID):** test the cumulative damage of ionising particles

**Single Event Effect (SEE):** test the non-cumulative damage induced by single particles

- Accumulation de charge dans l'oxyde d'un composant électronique

- Effet cumulatif: des pairs e-h sont produites par ionisation et peuvent être piégées à l'interface Si-Oxyde ou dans l'oxyde

- Si le composant continue d'être irradié, les charges s'accumulent

- Il est possible de réduire les dommages en augmentant la température: Annealing

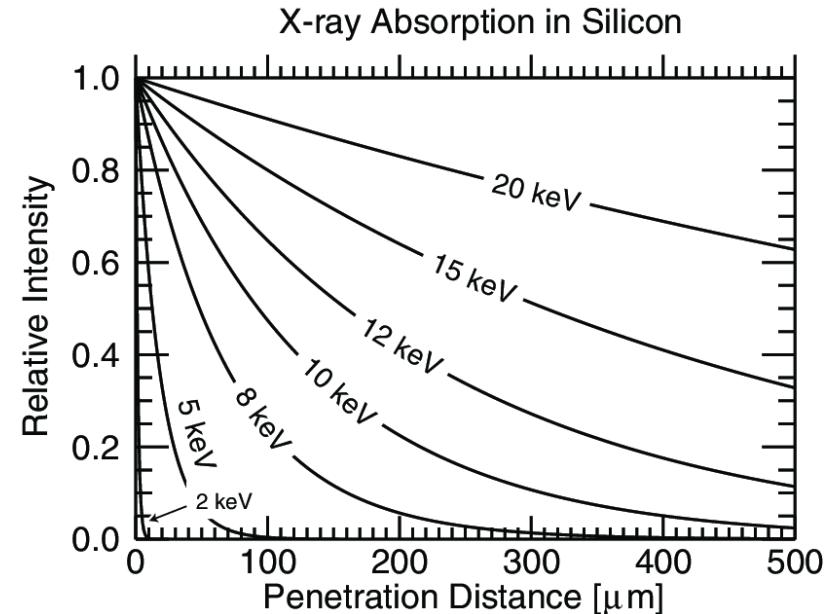

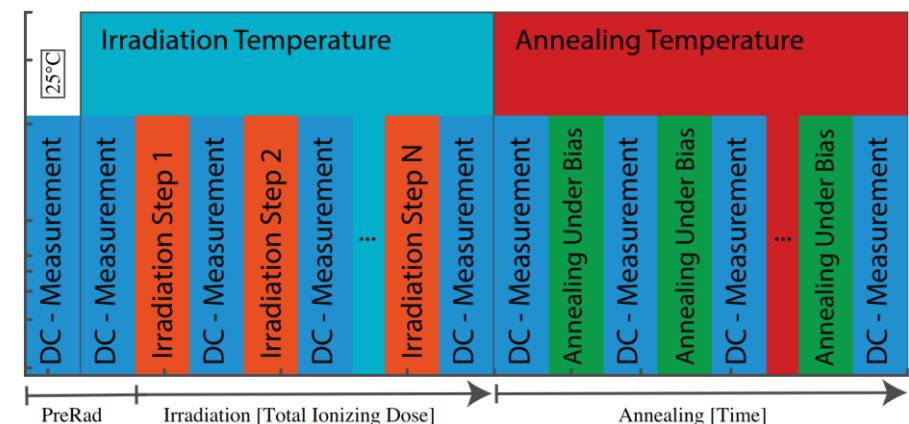

# Tester la robustesse au TID

- Rayons X (10 keV), Protons,  $^{60}\text{CO}$  (rayons  $\gamma$ ), etc

- Les rayons X sont les plus pratiques pour atteindre des doses élevées en peu de temps (5 Mrad/h)

- Mais grande atténuation dans le silicium

- Irradier plus loin que le target: low dose effect

- Bien mesurer le chip avant irradiation!

- Mesurer durant l'irradiation

- Et après! Avec ou sans annealing!

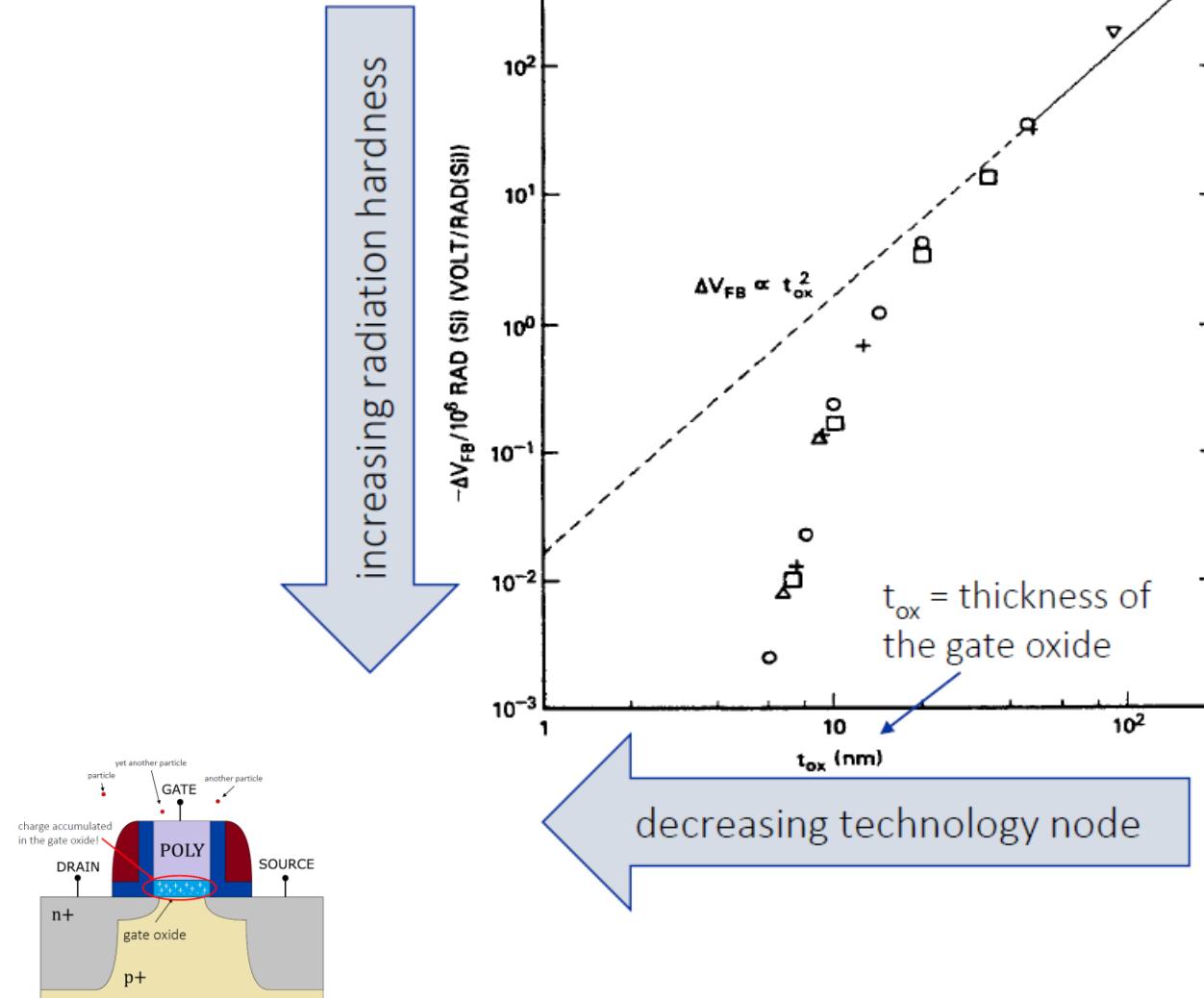

# Quelle dépendance de la techno?

*thin oxides are more rad-hard!!*

threshold voltage      flatband voltage (sensitive to TID)

$$V_{TH} = V_{FB} + \dots$$

average charge density in  $t_{ox}$

$$\Delta V_{TH}(TID) = \Delta V_{FB}(TID) = -\frac{\rho_{ox}(TID)}{\epsilon_{ox}} t_{ox}^2$$

$t_{ox}$  in 65nm node  $\approx 2$  nm

MOSFETs in 65nm CMOS technology should be extremely rad hard!

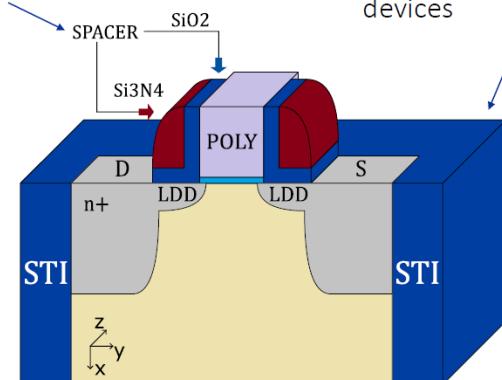

# Mais...

- Beaucoup d'oxyde et d'interface Si/Ox dans les nouvelles techno

- Et oxyde de moins bonne qualité que le gate oxyde

Spacers: needed to create the Lightly Doped Source/Drain (LDD) extensions

Shallow Trench Isolation (STI): useful to isolate adjacent devices

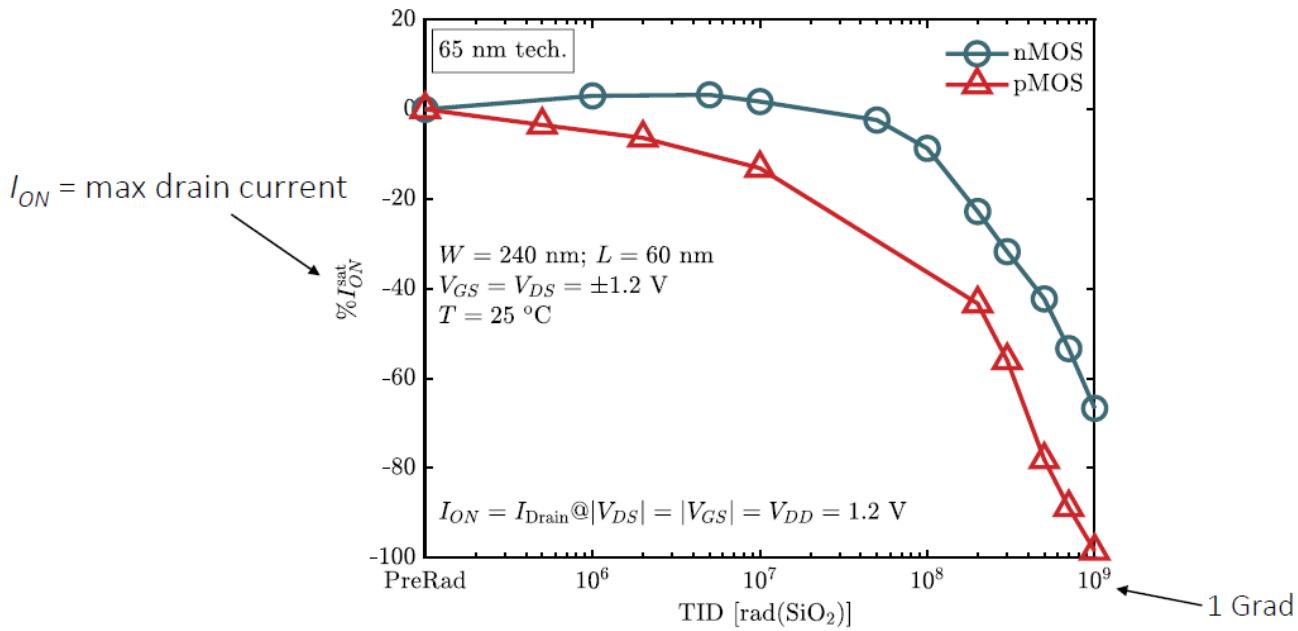

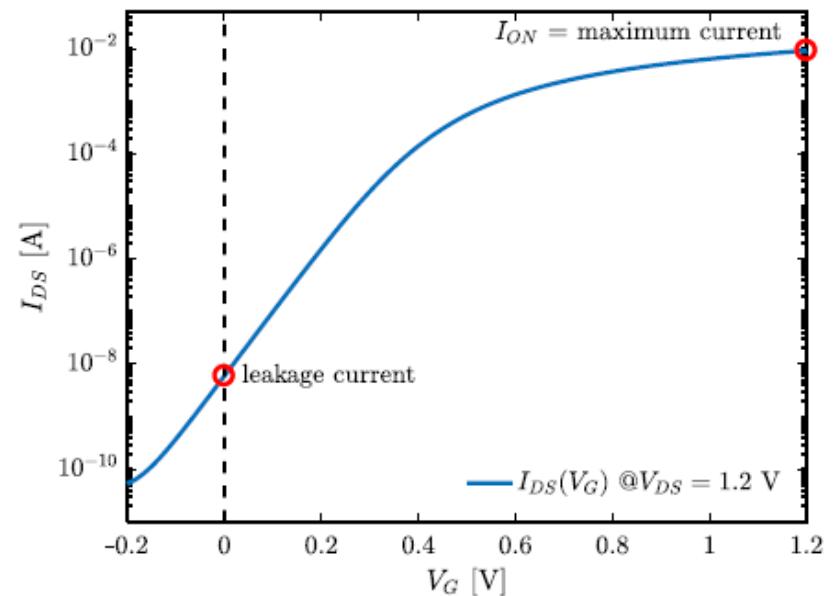

# Qu'est-ce qui est dégradé dans les transistors?

- $I_{on}$ : courant de drain maximal

- $I_{OFF}$  (leakage current): courant de drain @  $V_{DS}=\pm 1.2$  V,  $V_{GS}=0$

- $V_{th}$ : tension de seuil

- $gm_{MAX}$ : pic de la transconductance ( $g_m = \partial I_d / \partial V_g$ )

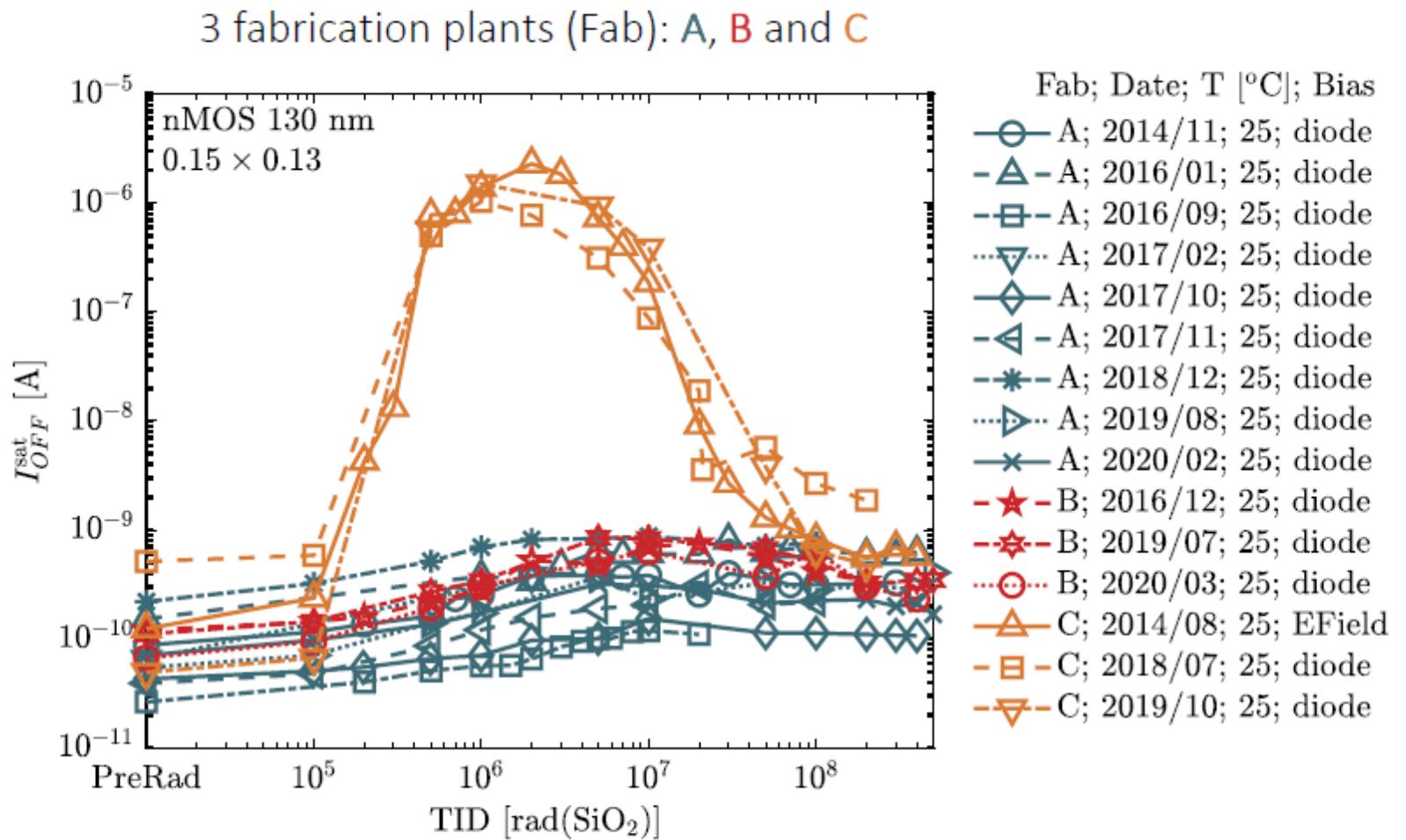

# Quelques résultats: leakage

\*F. T. Brady, J. D. Maimon, and M. J. Hurt. "A scalable, radiation hardened shallow trench isolation." In: IEEE Transactions on Nuclear Science 46.6 (Dec. 1999), pp. 1836–1840.

Z. Hu, Z. Liu, H. Shao, Z. Zhang, B. Ning, M. Chen, D. Bi, and S. Zou. "Impact of within-wafer process variability on radiation response." In: Microelectronics Journal 42.6 (2011), pp. 883–888.

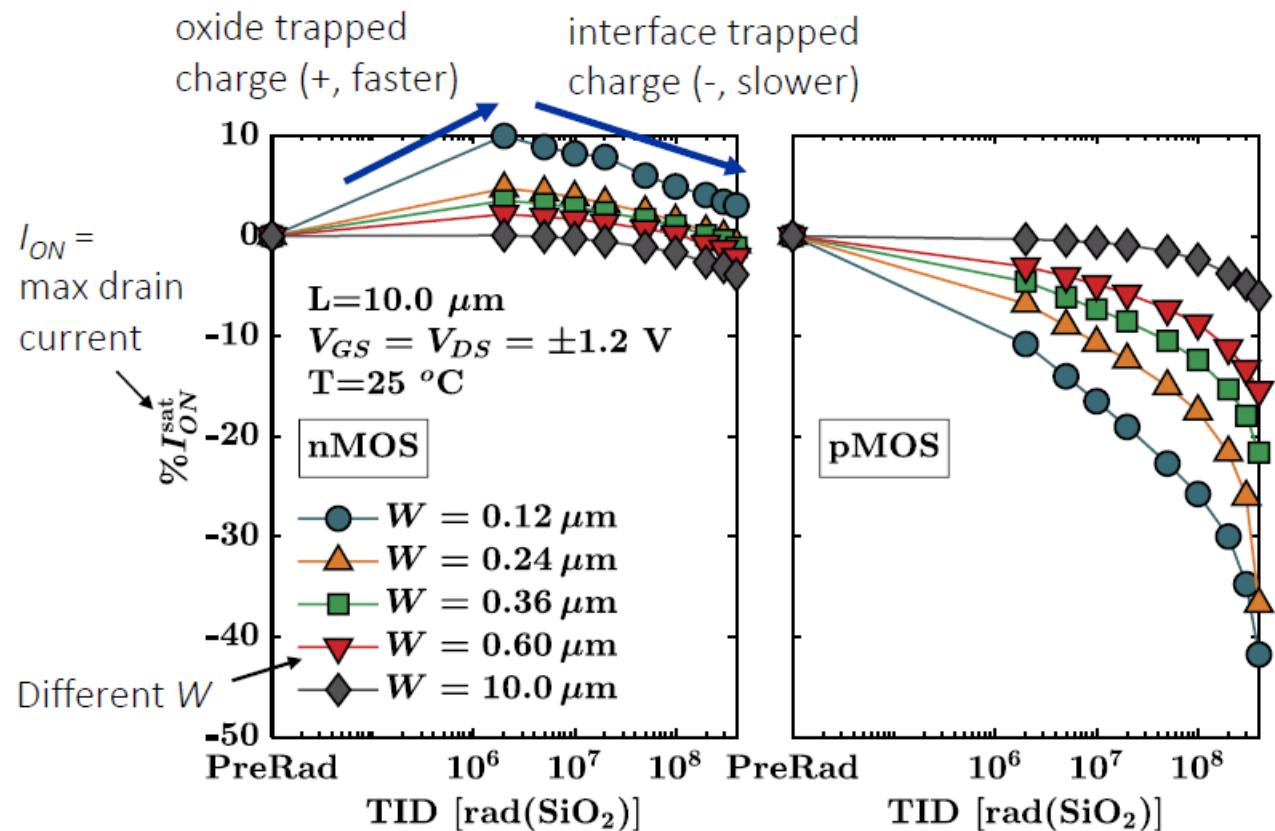

# Quelques résultats: $I_{ON-MAX}$

large performance variation in narrow devices!

smaller W

F. Faccio and G. Cervelli, "Radiation-induced edge effects in deep submicron CMOS transistors," in *IEEE Transactions on Nuclear Science*, vol. 52, no. 6, pp. 2413-2420, Dec. 2005

F. Faccio, S. Michelis, D. Cornale, A. Paccagnella and S. Gerardin, "Radiation-Induced Short Channel (RISCE) and Narrow Channel (RINCE) Effects in 65 and 130 nm MOSFETs," in *IEEE Transactions on Nuclear Science*, vol. 62, no. 6, pp. 2933-2940, Dec. 2015

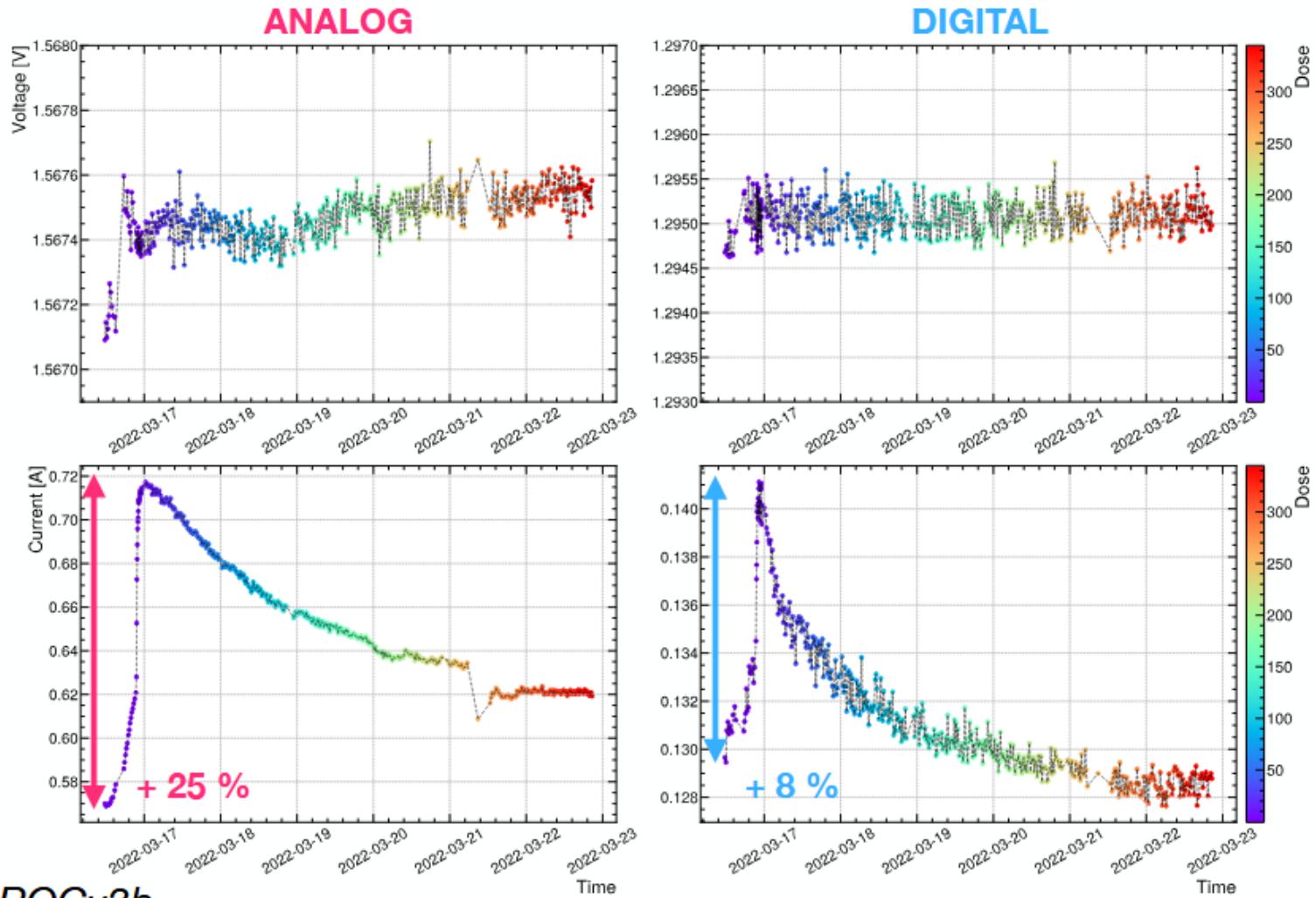

# Total ionising dose (TID)

## Power consumption

- Increase in the analog and digital current in the initial part of irradiation:

- Analog: +25%

- Digital: +8%

- Digital current increase is expected due to leakage current in the transistors (small size)

- compatible with requirements

- Analog current increase was unexpected (large size) and investigated: the cause is related to a floating node in the circuit

- fixed in the next submission *HGCROCv3b*

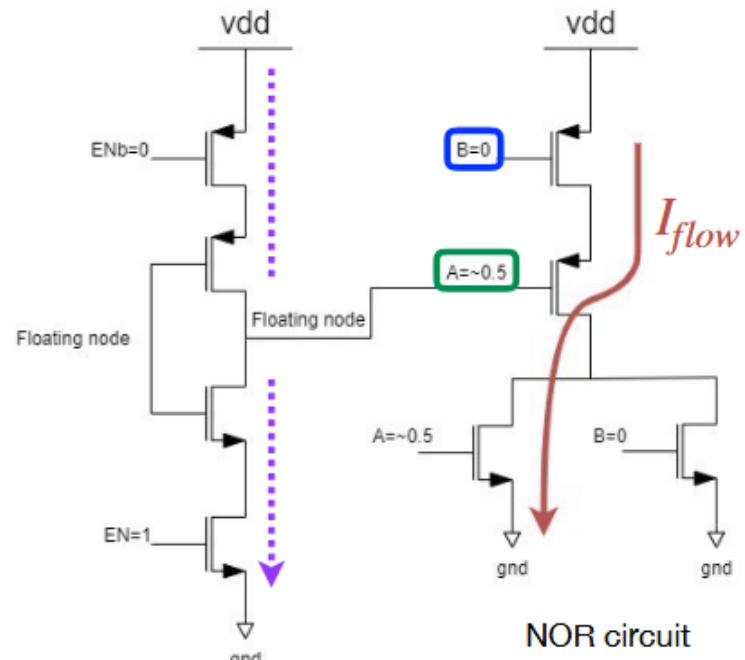

# Total ionising dose (TID)

## Floating node

- A floating input node was spotted in the **TDC circuit**

- Input A** should be **fixed** either to  $V_{\text{gnd}} \sim 0$  or  $V_{\text{dd}} \sim 1 \text{ V}$

- Leakage current** can shift the input value

- When  $A \sim 0.5 \text{ V}$  there is **current** flowing in the circuit

- Simulations** of the circuit can reproduce a current

$$I_{\text{flow}} \simeq 122 \mu\text{A}$$

and the total current in the chip would be

$$I_{\text{chip}} = I_{\text{flow}} \cdot 42 \cdot 2 \cdot 72 \simeq 700 \text{ mA}$$

# of NOR cells in one TDC circuit

ToA + ToT

# of channels

- The simulation **confirms** the presence of a **big current** flowing in the circuit (even higher than the observed one  $\sim 150 \text{ mA}$ )

| NOR circuit |   |   |

|-------------|---|---|

| A \ B       | 0 | 1 |

| 0           | 1 | 0 |

| 1           | 0 | 0 |

[Back to presentation](#)

[Back to list of contents](#)

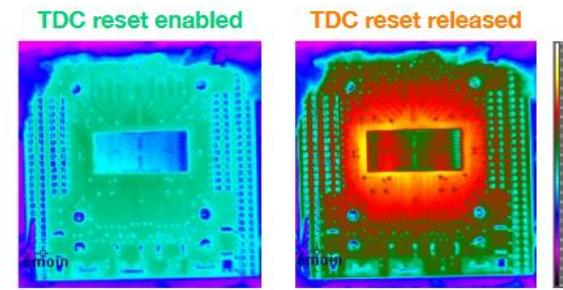

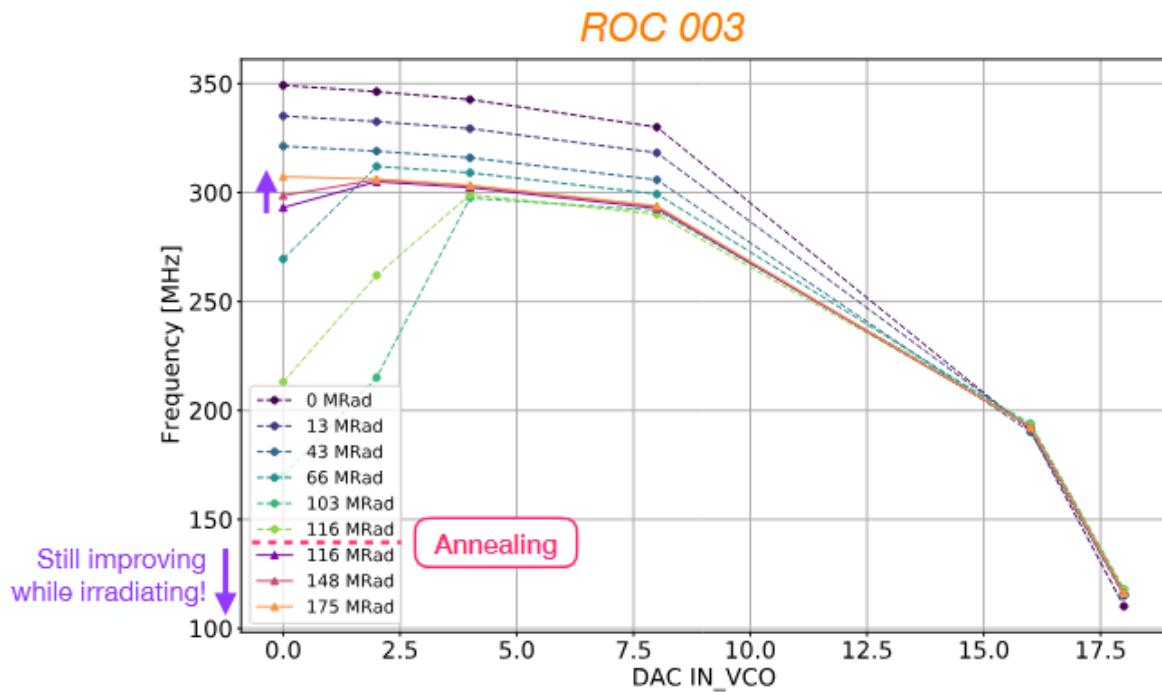

# Total ionising dose (TID)

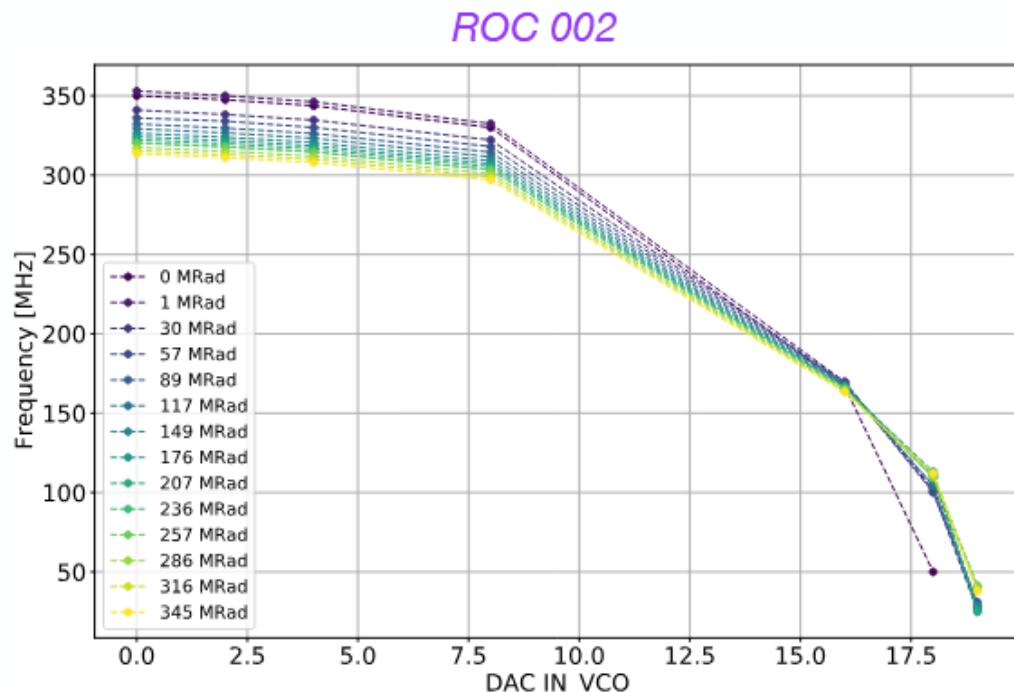

## Low and high temperature irradiation: PLL

- Irradiated 2 chips under different temperature conditions:

- ROC 002* at  $-10^{\circ}\text{C}$  (2.45 Mrad/h) : **345 Mrad**

- ROC 003* at  $+30^{\circ}\text{C}$  (2.45 Mrad/h) : **175 Mrad**

- After 345 Mrad of dose, the PLL is still able to provide frequencies bigger than 160 MHz.

- After  $\sim 48$  hours of annealing, the response still improves under irradiation.

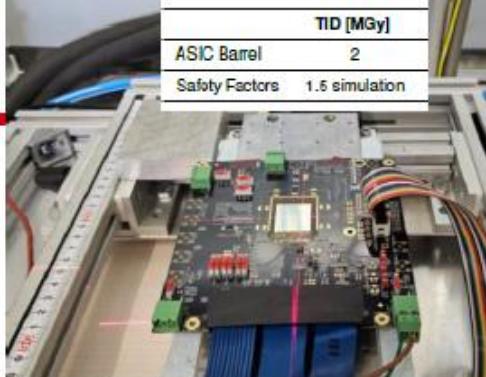

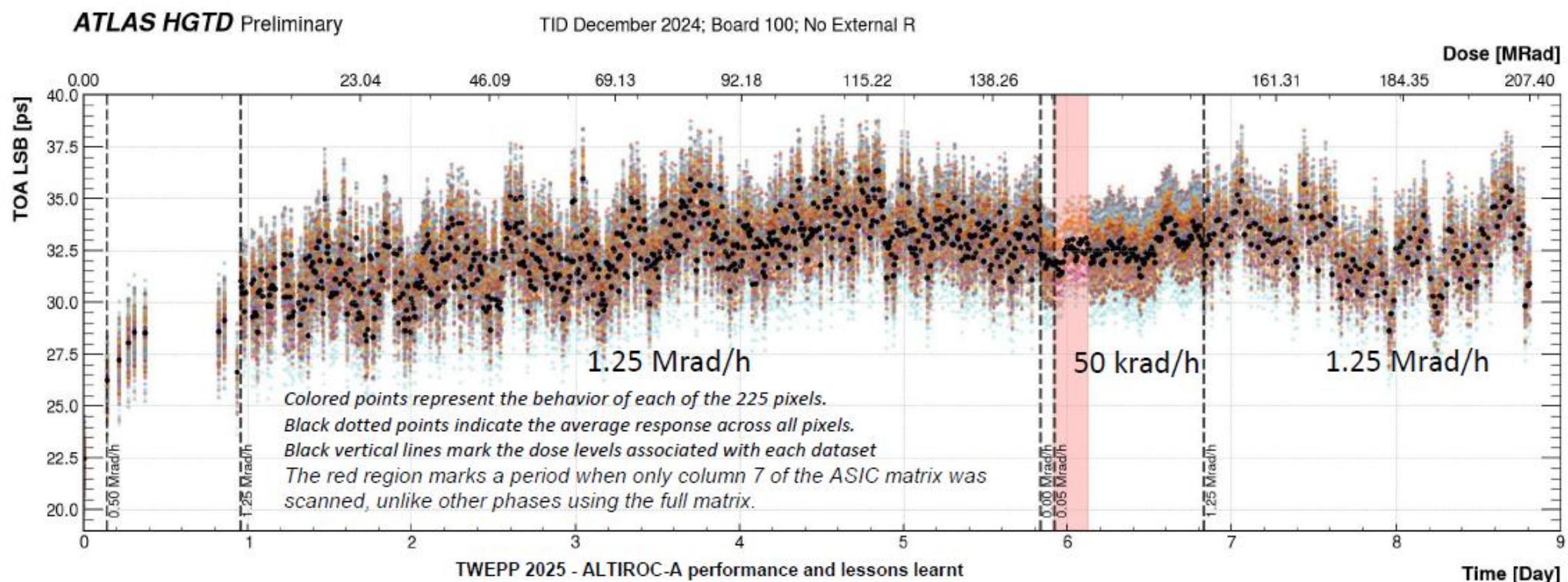

# ALTIROC-A PERFORMANCE: TID irradiation (1)

| TID [MGy]      |                |

|----------------|----------------|

| ASIC Barrel    | 2              |

| Safety Factors | 1.5 simulation |

- **TID conditions**

- Use Obelix facility 10 keV X-rays (Dec 2024, Jan 2025, March 2025) and ATLAS pixel facility (Feb 2025)

- Temp -20°C at Obelix, room temp at ATLAS pixel facility

- Up to 200 Mrad (= 2 MGy) with beam at the max distance to irradiate all the chip => max dose rate ~1.2 Mrad/h, min dose ~ 16 krad/h

- **Continuous measurements during irradiation:**

- DC voltages and power consumptions, Vth & Vthc scan, Charge scans (Qmin), noise, TOA and TOT LSB, Jitter measurements for Qinj = 4 fC and 10 fC

- **No variations** observed for all the measurements **except for the TOA TDC bin** which shows unexpected variations under irradiation: the larger the rate the larger the variations

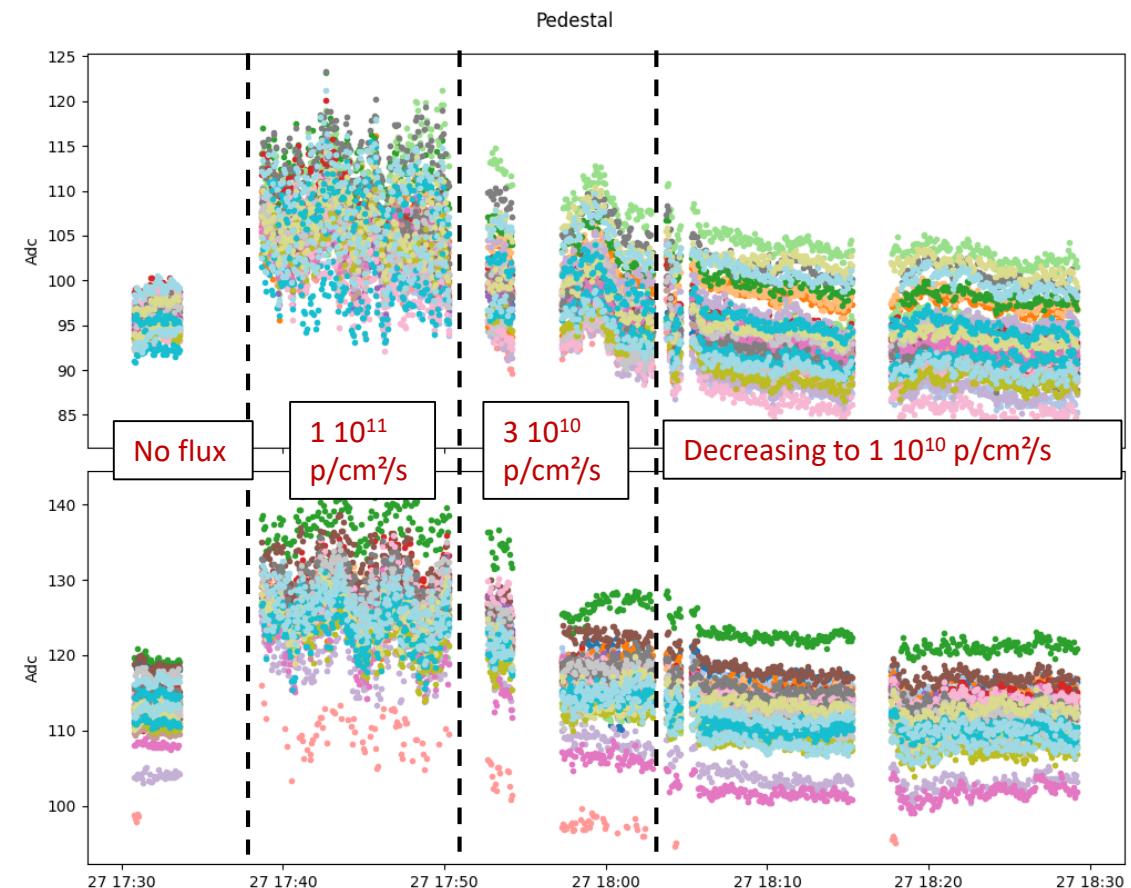

# SEE test: pedestal disturbance

- The pedestal disturbances are observed with protons as well, similar to TID

- It is still a collective effect affecting half of the chip

- The dependence on flux is more visible

- Should be negligible at realistic flux

# TID mitigations

- Choix de la techno quand possible

- Éviter transistor de taille minimale

- Gates interdites dans la synthèse numérique

- à cause de la taille de leur transistor

- À cause de leur architecture

- Éviter thick oxide transistors

- En particulier utilisés comme capa

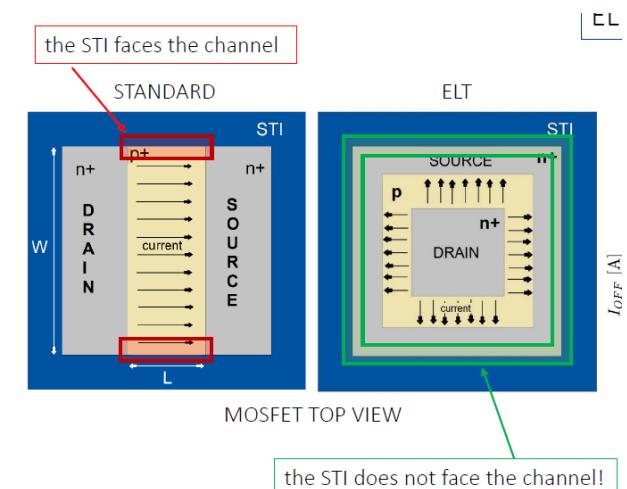

- Enclosed Layout Transistor (ETL)

- Annule les courants de fuites des bords

- Très long à implémenter partout

- Impossible (?) dans les librairies numériques

- Erreur de DRC et LVS

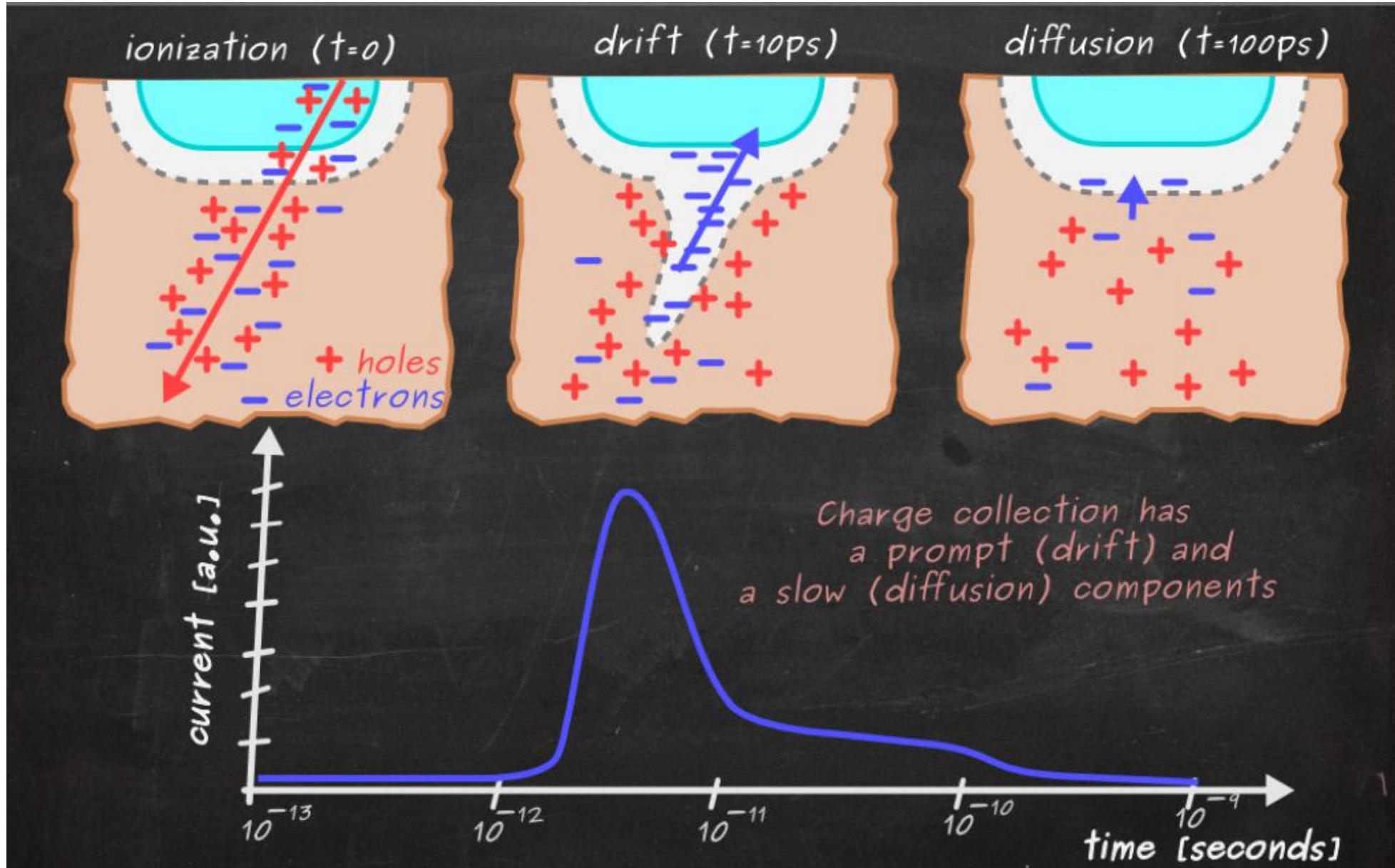

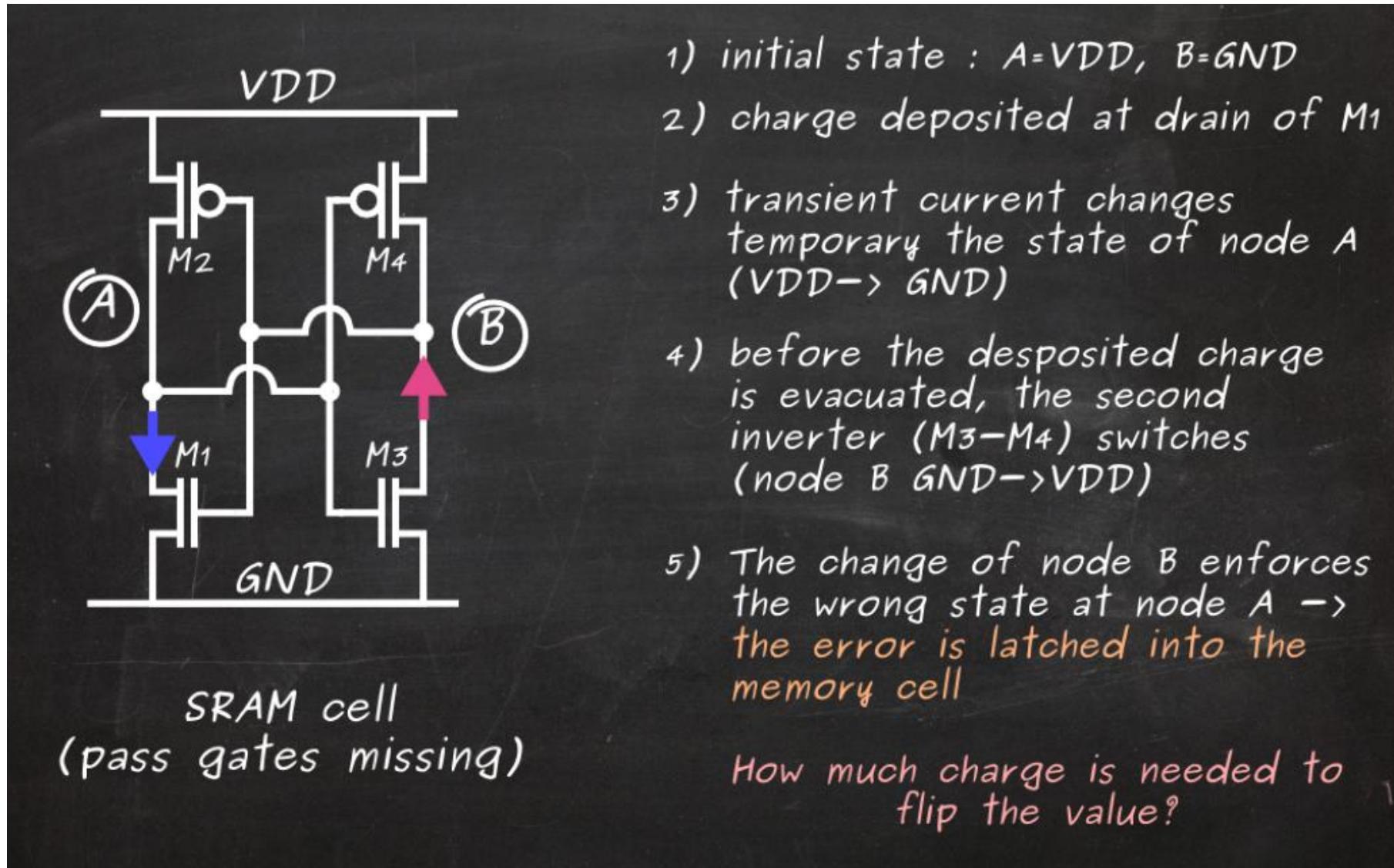

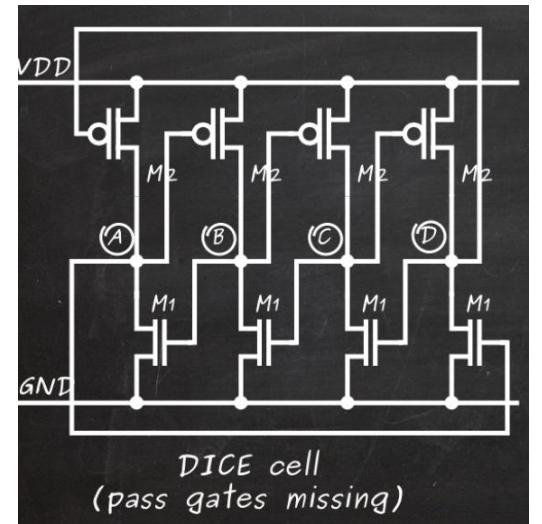

# Mécanisme des SEE

# Mécanisme des SEU

Probabilité de SEU:

Tension d'alim (Q=CV)

Capacité (Q=CV)

Nœud techno (cross-section)

# SEE mitigations

- Au niveau techno

- Minimiser la profondeur sensible: SOI

- Au niveau cellule

- Augmenter la capacité sur les nœuds sensibles (augmente la charge critique)

- Design plus lent

- Information stocké à plusieurs endroits: cellules DICE, Whitaker, SERT

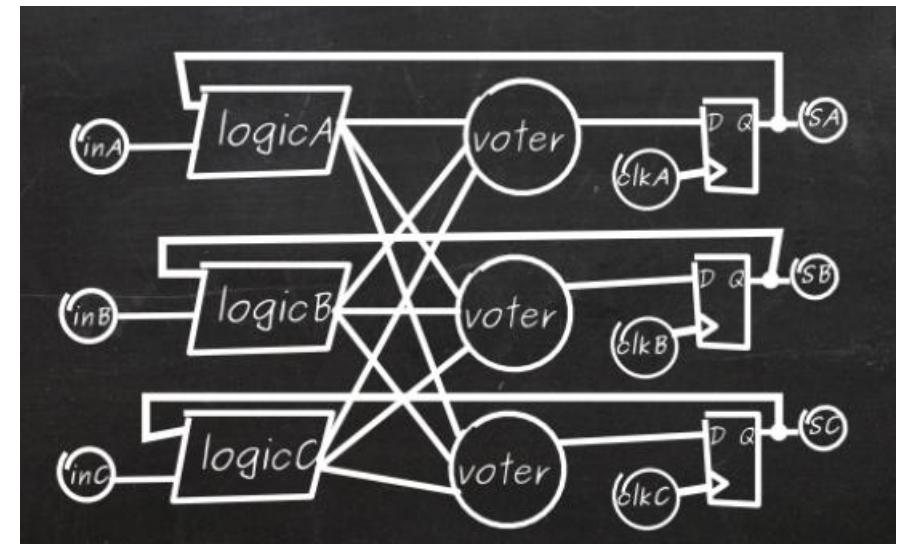

- Au niveau système

- Encodage: Hamming, Reed-Solomon

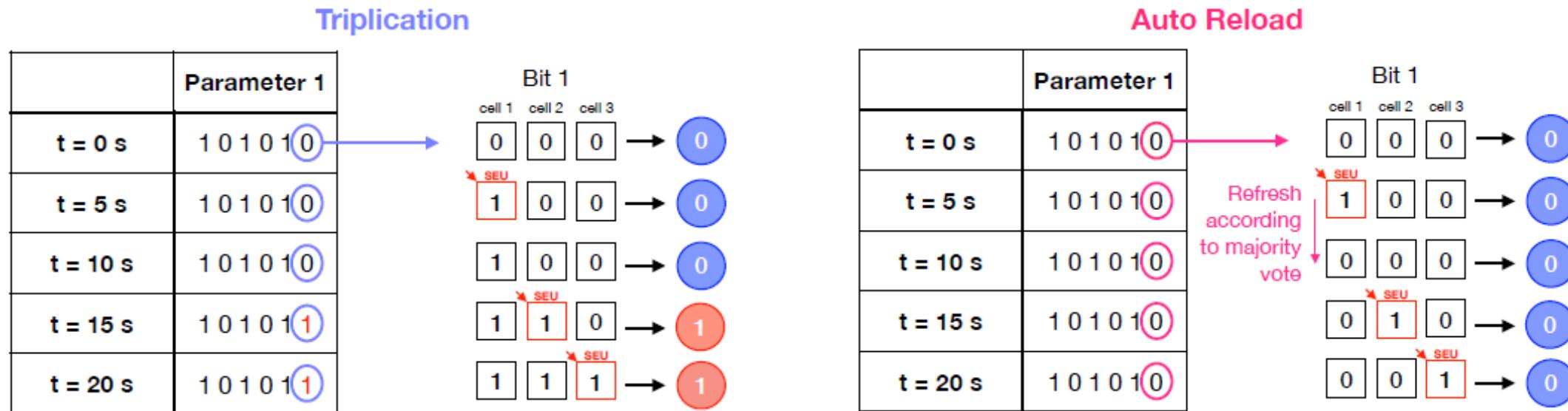

- ***Tripllication: Triple Modular Redundancy (TMR)***

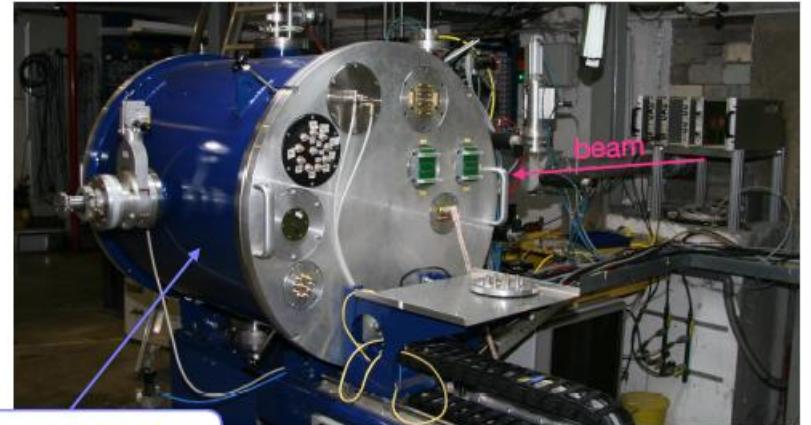

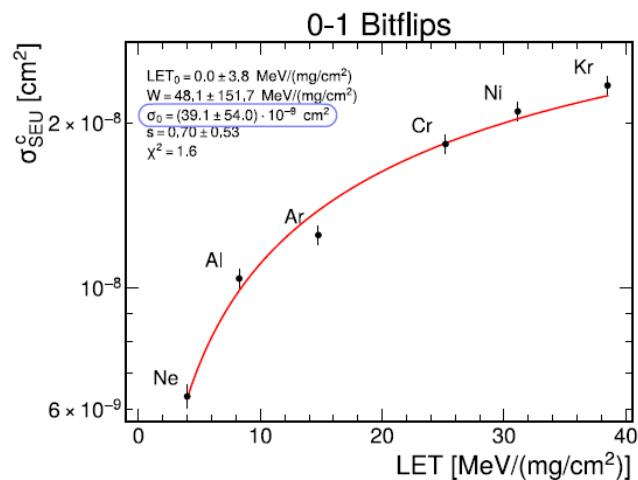

# Comment et où tester les SEE?

- Avec **des ions lourds** (Louvain la Neuve)

- Scan d'ions lourds de différentes énergies: sections efficaces

- Weibull fit permet de trouver la section efficace attendue au LHC

- Très compliqué avec triplication

- En pratique: limite haute pour la configuration et SEL

- **Protons > 60 MeV** (Arronax à Nantes)

- Ou medical center: à Nice avec protons de 200 MeV

- Équivalents aux conditions du LHC

- Plus facile d'extraire des sections efficaces (SEU, SET dans numérique/analogique)

# Single Event Effect (SEE)

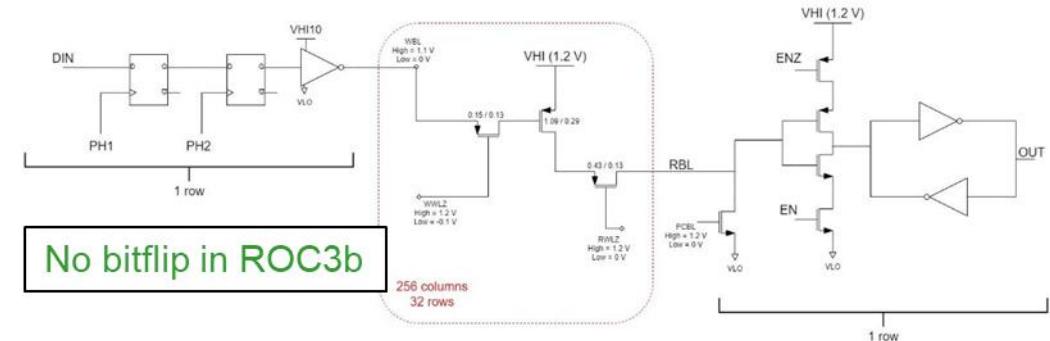

## I<sub>2</sub>C test: results

- The I<sub>2</sub>C is a set of **static registers** to store the chip's configuration (2573 parameters in 8956 bits)

- At the beginning, all the **I<sub>2</sub>C parameters** are **set** to given values

- During the irradiation, the **I<sub>2</sub>C parameters** are read and **compared** to the written ones

- Tripllication* logic and *Auto Reload* are used to protect against SEUs

✓ No bit flips observed with **Auto Reload** enabled

# Single Event Effect (SEE)

## I<sup>2</sup>C test: results

- The I<sup>2</sup>C is a set of **static registers** to store the chip's configuration (2573 parameters in 8956 bits)

- At the beginning, all the **I<sup>2</sup>C parameters** are **set** to given values

- During the irradiation, the **I<sup>2</sup>C parameters** are read and **compared** to the written ones

- Auto Reload* refreshes flipped cells to protect against SEUs (only ~100 ps refresh time)

| Ion | LET<br>[MeV/mg/cm <sup>2</sup> ] | Flux<br>[part/(s·cm <sup>2</sup> )] | Auto Reload mode OFF |                 | Auto Reload mode ON |                 |

|-----|----------------------------------|-------------------------------------|----------------------|-----------------|---------------------|-----------------|

|     |                                  |                                     | Total Time<br>[s]    | Total bit flips | Total Time<br>[s]   | Total bit flips |

| Ne  | 3.3                              | 10 000                              | 490                  | 55              | 1515                | 0               |

| Al  | 5.7                              | 10 000                              | 674                  | 213             | 1291                | 0               |

| Ar  | 9.9                              | 10 000                              | 699                  | 316             | 1184                | 0               |

| Cr  | 16.0                             | 10 000                              | 687                  | 559             | 879                 | 0               |

| Ni  | 20.4                             | 10 000                              | 678                  | 662             | 1289                | 0               |

| Kr  | 32.4                             | 10 000                              | 507                  | 502             | 661                 | 0               |

| Xe  | 62.5                             | 10 000                              | 641                  | 130             | 127                 | 0               |

✓ No bit flips observed with Auto Reload enabled

# Single Event Effect (SEE)

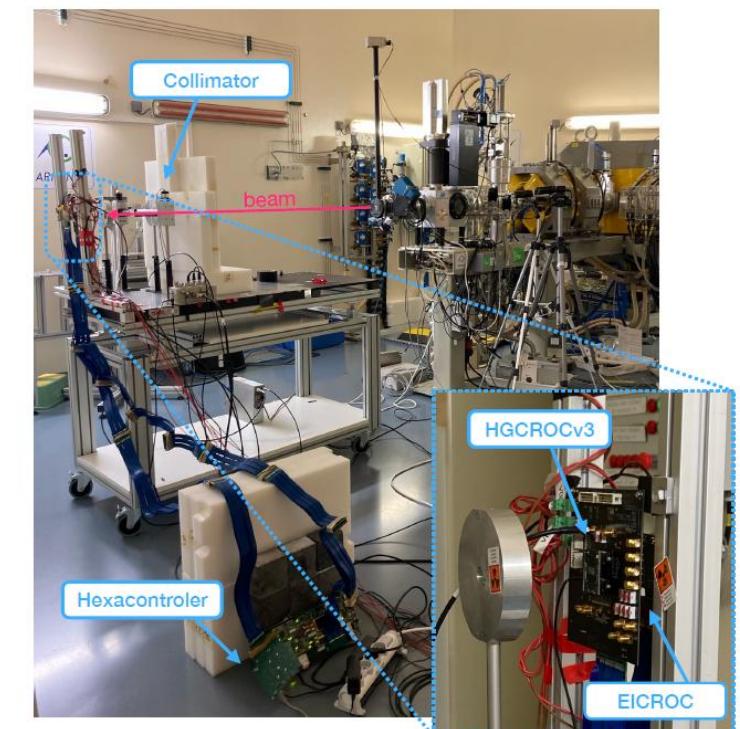

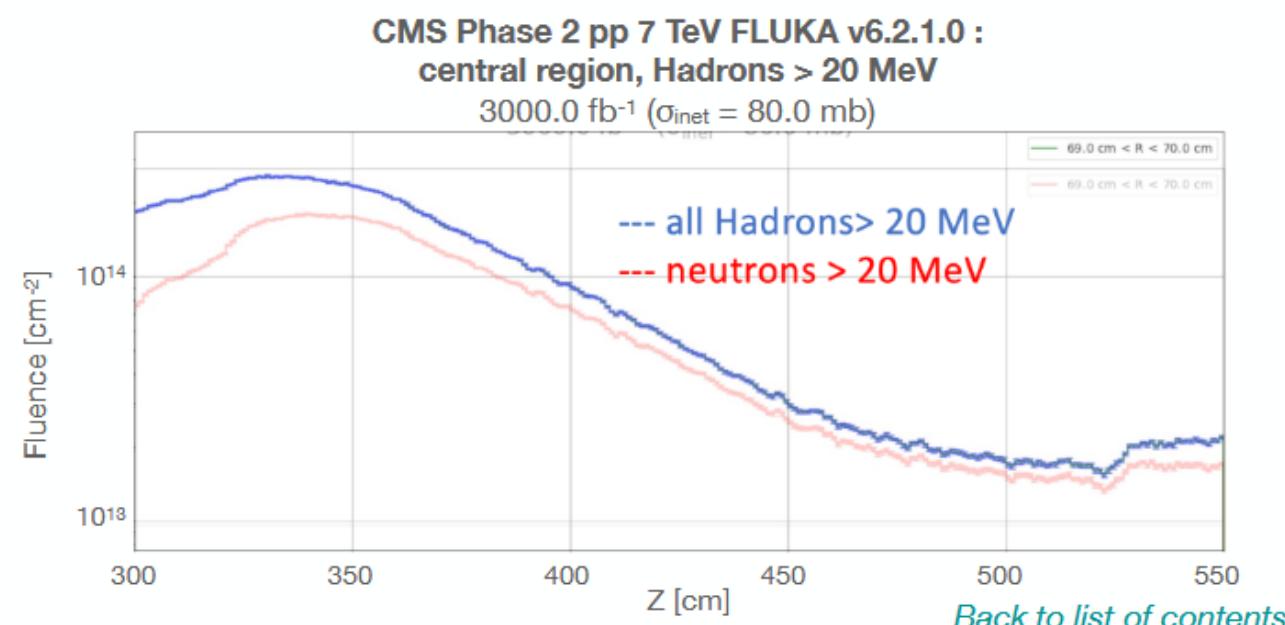

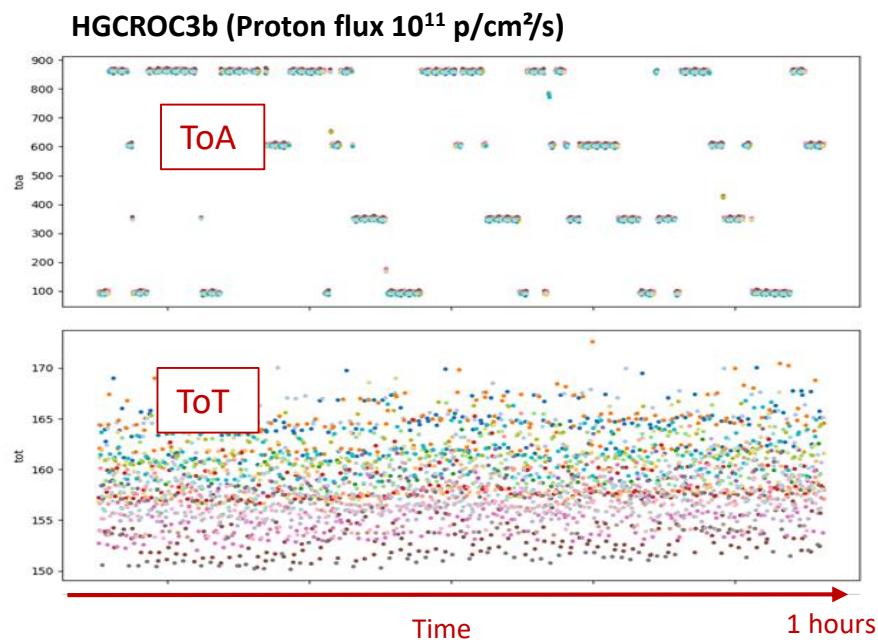

## Proton irradiation

- SEE irradiation test of HGCROC3 with **protons** at Arronax in Nantes

- Beam*: 20 - 63 MeV protons

- Current*: ~10 nA

- Flux*: ~ $10^{10}$  protons/(s·cm<sup>2</sup>)

- Duration*: 12 h

- The goal is to extract

- SEU rate* on the *digital* part

- SET rate* on the *analog* part

- Convert the rate to the HGCAL expected flux

- Flux max hadrons > 20 MeV*:

$2.11 \cdot 10^7$  particles/(s·cm<sup>2</sup>)

- Average flux hadrons > 20 MeV*:

$1.91 \cdot 10^6$  particles/(s·cm<sup>2</sup>)

# SEE results with 70 MeV protons

$$\sigma = \frac{\# \text{ errors}}{\text{Fluence}_{\text{Arronax}}} = \frac{\# \text{ errors}}{\text{DAQ time} * \Phi_{\text{Arronax}}}$$

$$R_{LHC}^{Av} = \Phi_{LHC}^{Av} \cdot \sigma$$

**Table 1.** Summary of SEE test results of HGCROC3. Errors seen at  $2.2 \times 10^{10} / \text{cm}^2/\text{s}$  70 MeV protons flux. The expected rate is computed assuming  $2 \times 10^6 / \text{cm}^2/\text{s}$  average flux at HGCAL and 100 000 chips.

| Category               | Time [s] | # Errors | Cross Section [ $\text{cm}^{-2}$ ] | HGCAL Rate [ $\text{s}^{-1}$ ] |

|------------------------|----------|----------|------------------------------------|--------------------------------|

| I2C configuration      | 108 000  | < 1      | $< 4.2 \times 10^{-16}$            | $< 1.01 \times 10^{-4}$        |

| Tripllicated Logic     | 62 639   | < 1      | $< 7.26 \times 10^{-16}$           | $< 1.74 \times 10^{-4}$        |

| Non-tripllicated logic | 340      | 30       | $4 \times 10^{-12}$                | 0.8                            |

| Trigger data           | 34       | 38       | $5 \times 10^{-11}$                | 10.16                          |

| DAQ memory             | 4 352    | 127      | $1.33 \times 10^{-12}$             | 0.318                          |

# Mesures

# Plan du cours

- Introduction: de l'électronique partout dans nos détecteurs

- Fondamentaux de l'électronique

- Rappel général des bases de l'électronique

- Détecteur et préamplificateur

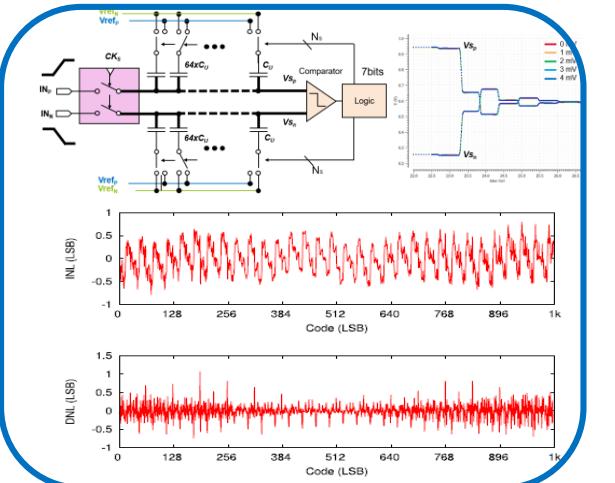

- Conversion Analogique/Numérique

- Numérique

- Le langage HDL (VHDL ou Verilog), synthèse, vérification

- De plus en plus de numérique dans les ASICs

- Design Flow: Analog-on-Top ou Digital-on-Top

- Bruit électronique

- Fondamentaux

- Filtrage, shaping

- Techniques de mesure

- Effets des radiations sur l'électronique

- TID et SEE

- Campagnes d'irradiation, performances, cross-section

- **Extrême importance des tests: sur table, radiation, beam, système**

- La mesure de temps

- Généralité

- Les TDCs

# Importance des tests

- Un chip soumis est toujours vérifié

- Analog/digital simulations

- Design review

- On essaye d'imaginer tous les cas possibles d'échecs

- Et pourtant il n'est pas rare de trouver des bugs

- Même pour des circuits largement utilisés et testée depuis longtemps

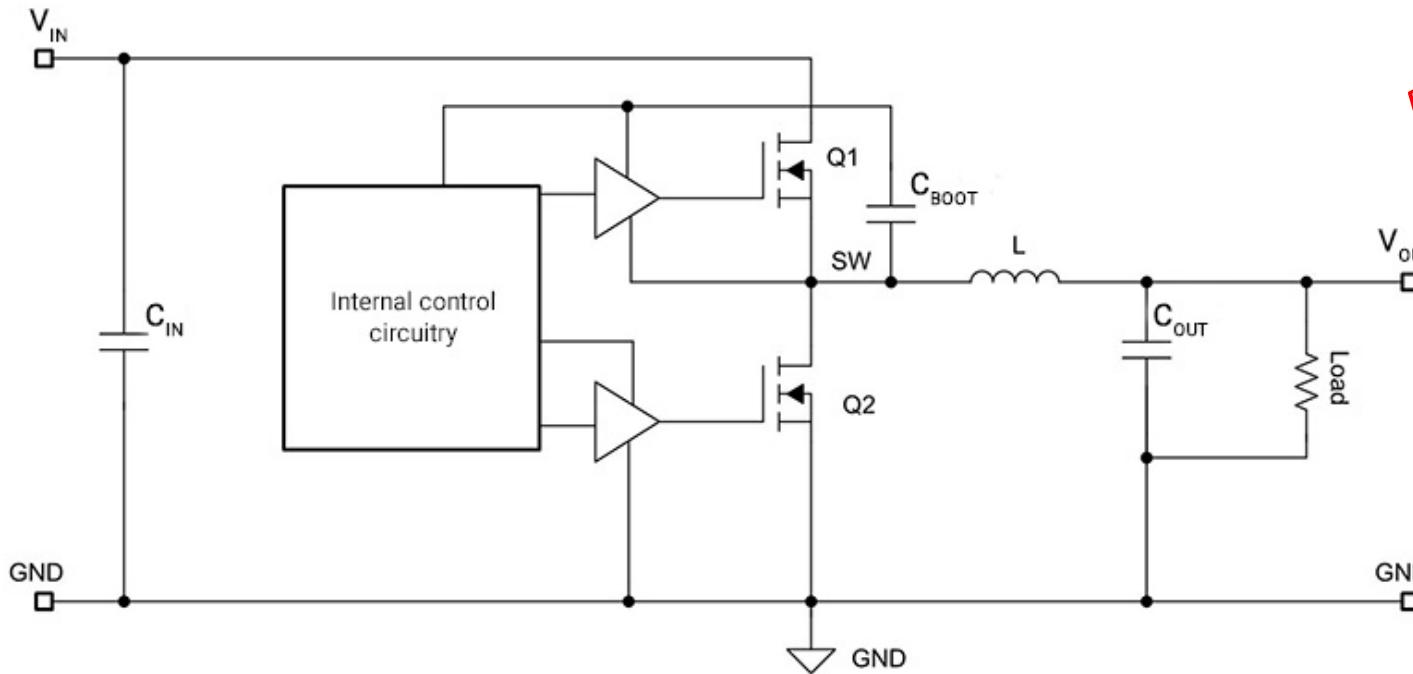

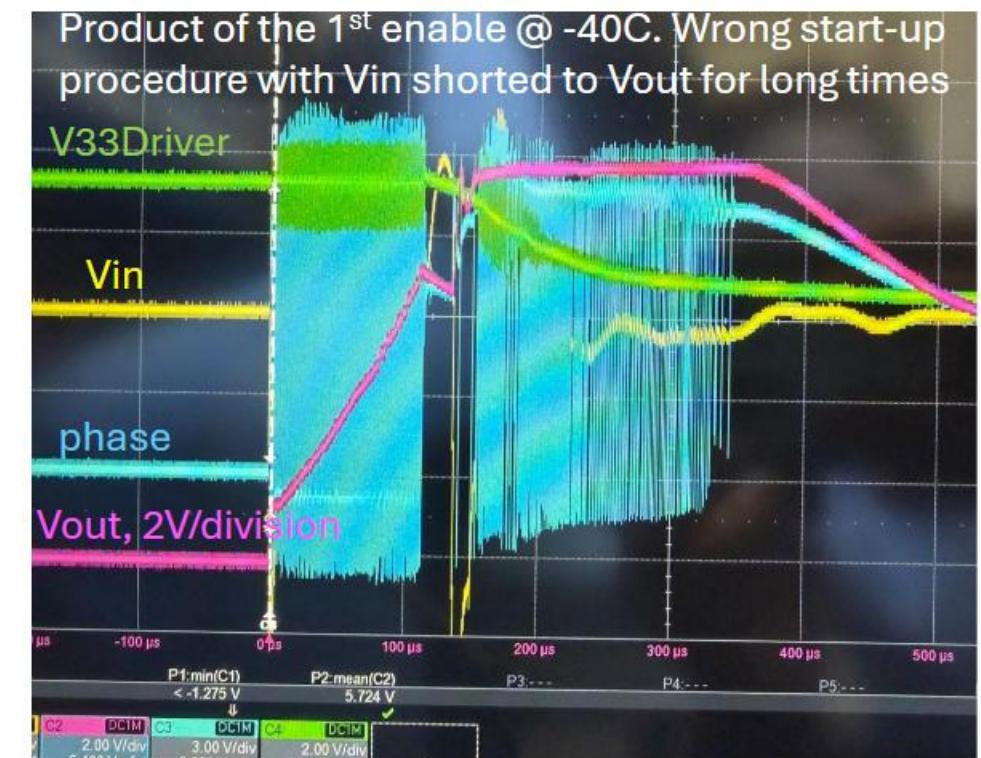

# BPOL12V bug

DC-DC converter

Chip commun à toutes les manip CERN

Des milliers produits et distribués

Découvert par les équipes d'ATLAS!

| # wafers | # of chip from the wafers | # of chip after testing | yield | Year of production | Lot name      |

|----------|---------------------------|-------------------------|-------|--------------------|---------------|

| 18       | 24794                     | 22399                   | 90.3% | 2021               | 21/52 (lot 1) |

| 60       | 145768                    | 138877                  | 95.3% | 2022               | 23/16 (lot 2) |

| 50       | 111397                    | 106511                  | 95.6% | 2023               | 24/16 (lot 3) |

| 50       | 109491                    | 104269                  | 95.2% | 2024               | 25/11 (lot 4) |

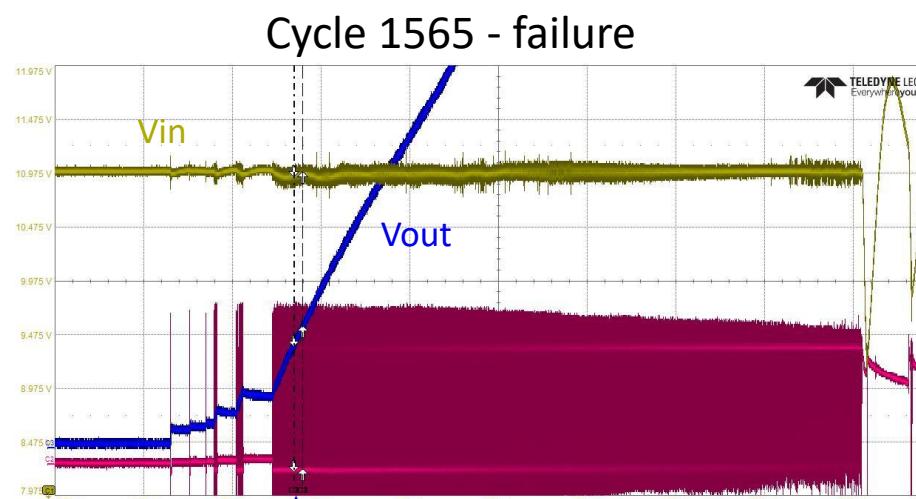

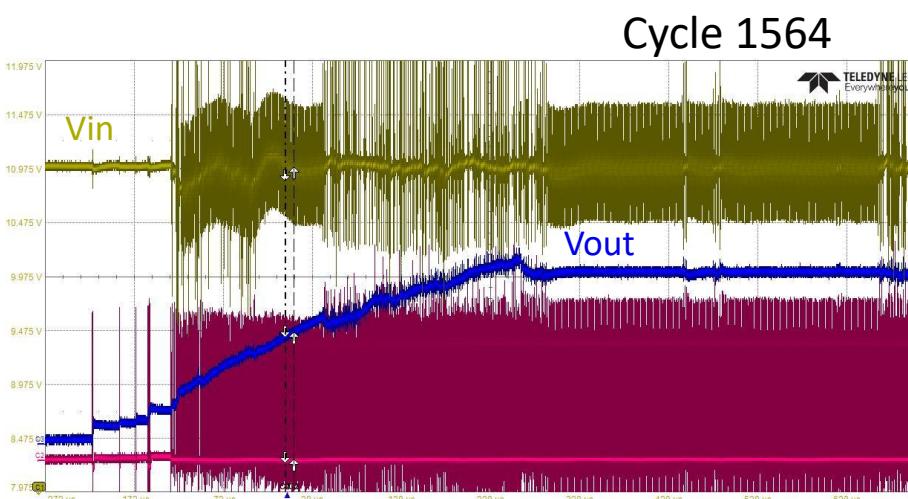

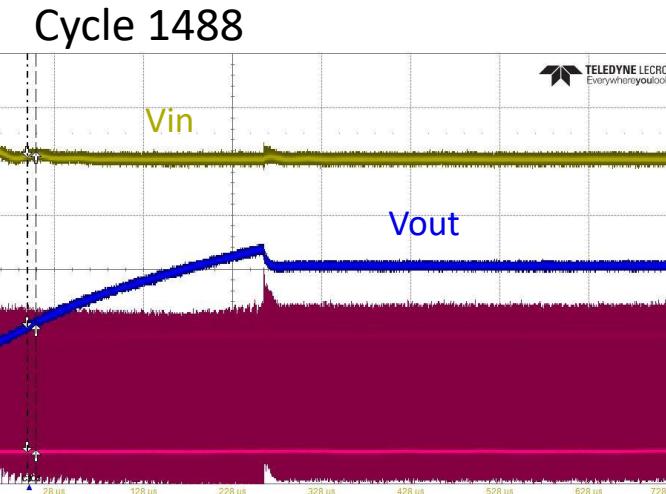

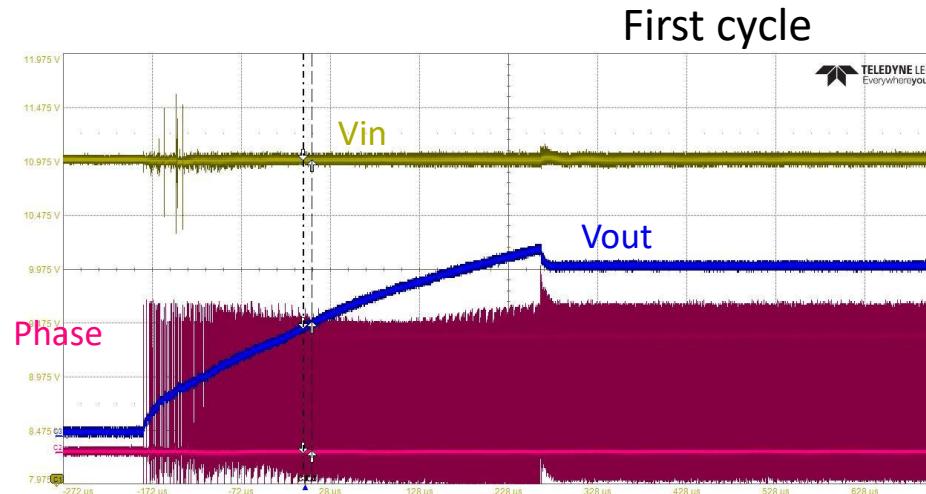

# The problem: example of evolution

Example of a 70 Mrad Xray irradiated bPOL12V, then Enable cycled at -30C at CERN

# Résumé des observations

- bPOL12V exposed to TID are subject to 2 failure mechanisms:

- A “gradual” failure, consequence of the evolution of a defect in the switching during the enable and occurring after hundreds/thousands of enable cycles

- A “sudden” failure, occurring at the first enable if a sequence of conditions is met. The observation of this failure type is still very limited.

- Irradiate to 70Mrad floating

- Cool to -35/-38 °C

- Apply Vin=11V for 30-60 minutes, with bPOL12V disabled

- Enable bPOL12V

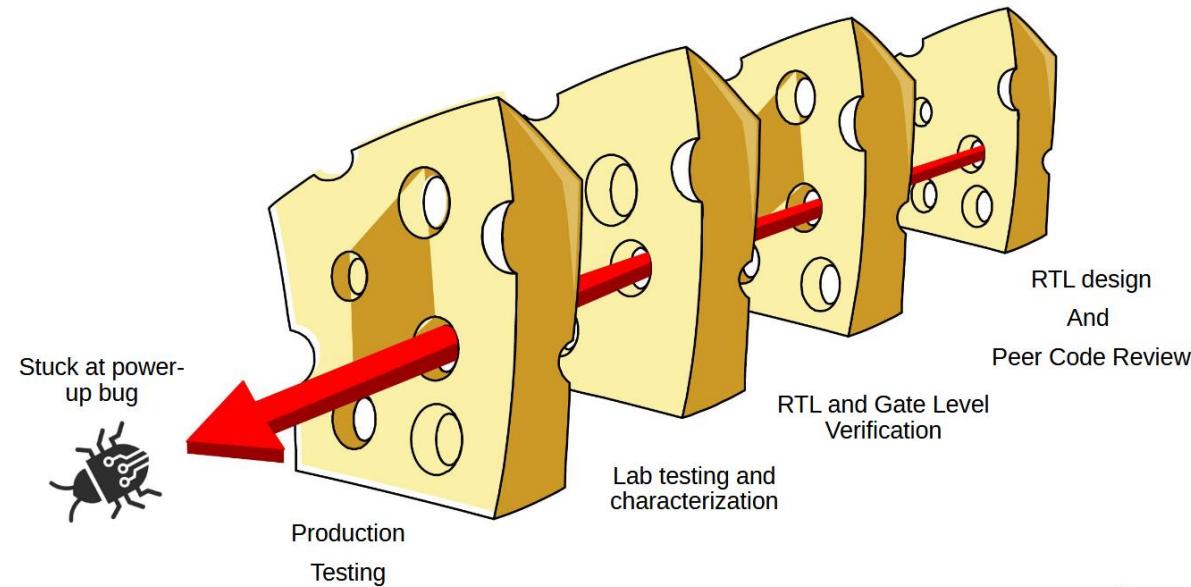

# LpGBT bug

- Stuck at power-up

- À cause de la valeur initiale de DFF au démarrage (reset synchrone)

- Aurait du être vu en simulation. Mais simulation faite dans les mêmes conditions initiales (seed inchangé: même séquence de valeurs aléatoires)

- Finalement reproduit en simulation

- Equalizer attenuation

Découvert par les équipes d'ATLAS!

# Impact d'un bug!!

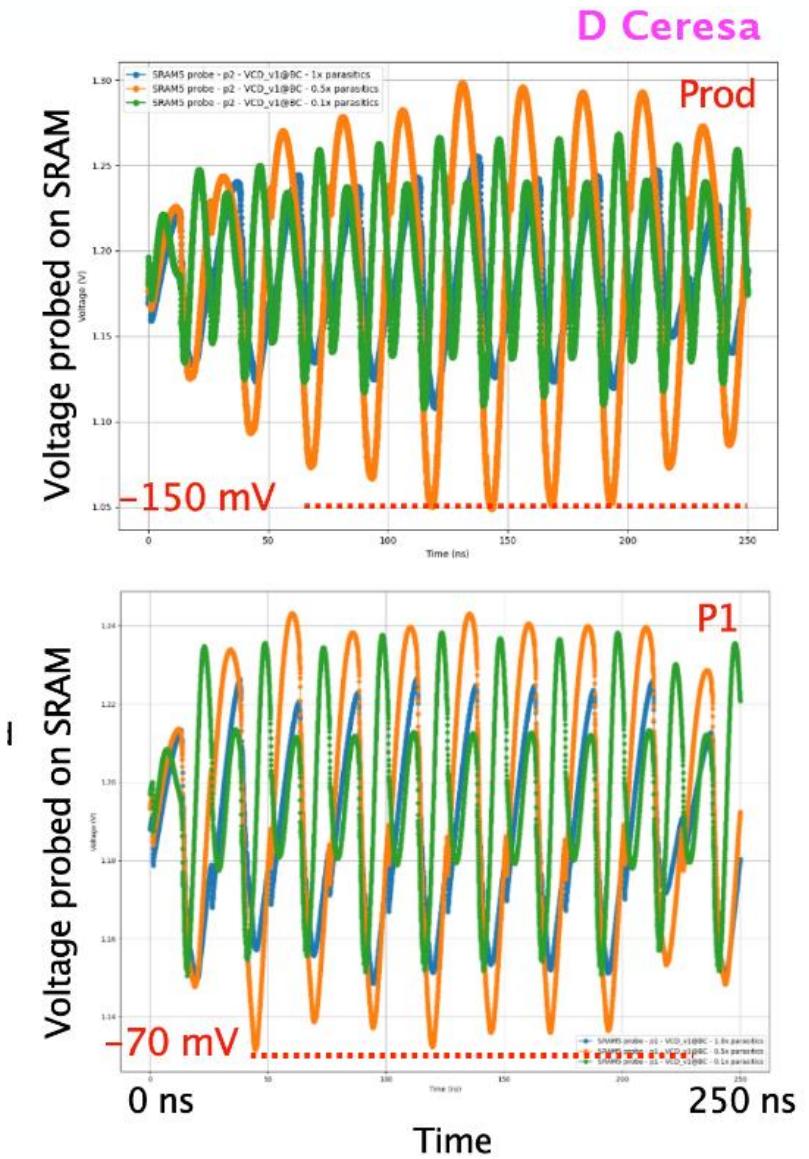

# ECON-D bug

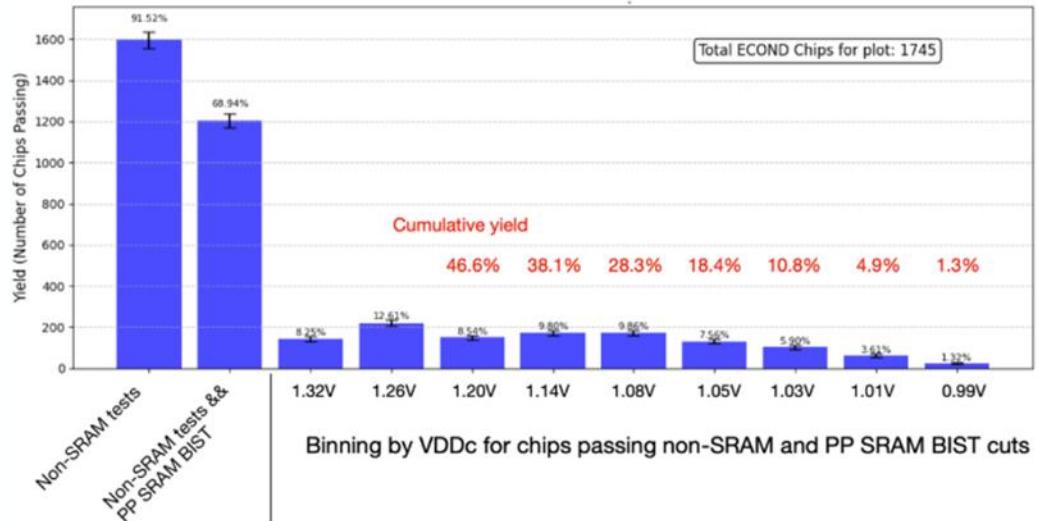

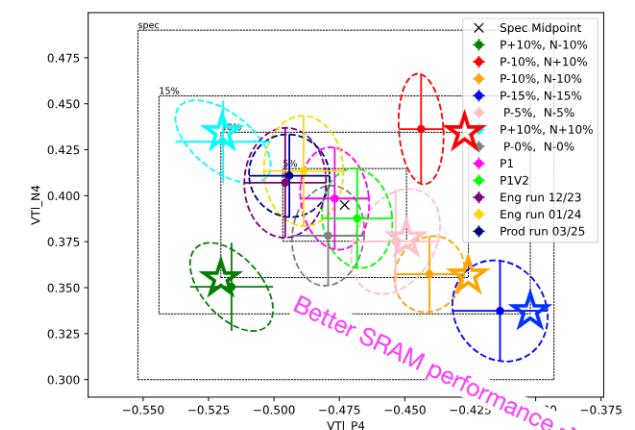

## Reminder : ECON-D SRAM issue

- **Observation** : ECON-D SRAMs give read errors with rate depending on **total ionizing dose** (TID), **supply voltage** (VDD), and **temperature** (T).

- Chip error rates vary due to dependence on internal timing and **transistor threshold voltage** (VTI).

- **Hypothesis** :

- Large current transients cause **internal oscillation of voltage** supplied to SRAM

- TID, temperature, and **CMOS process variations increase VTI** making SRAM more susceptible to oscillation

- **Production (Prod) vs prototype (P1) chips**:

- Error rates are lower in P1

- Prod has tighter timing alignment → larger transients → larger oscillation amplitude

- Prod process has higher VTI → more susceptible to oscillation

# ECON-D bug

## Reminder : ECON-D SRAM issues

### Baseline production strategy : “Treat as yield issue”

- Select ECON-D useful for detector during QC

- Yield = 28% (18%) @ 1.08V (1.05V)

- Bin by TID tolerance for use on detector.

### Mitigation strategies :

- (1) System supply voltage configurable from 1.2 – 1.25 mV bringing VDD margin of 50 mV

- confirmed

- (2) Package bonding optimization : lower package inductance by adopting prototype bonding scheme

- studied with ~40 chips, no improvement

- (3) VTI tuning during wafer fab evaluated with “corner wafer” study

- success

- (4) New : Metal-only design changes to softly isolate SRAM power grid in ECON-D

- design complete, tapeout in progress

5

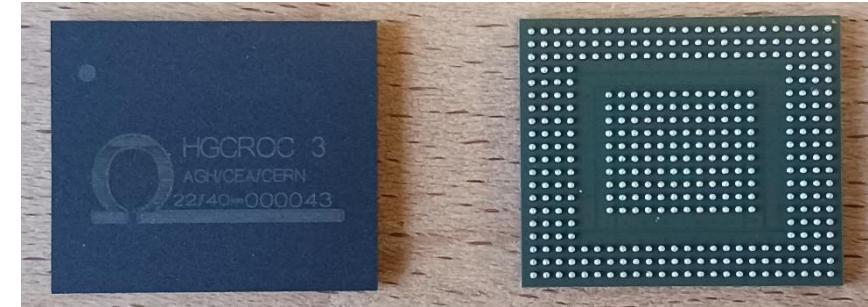

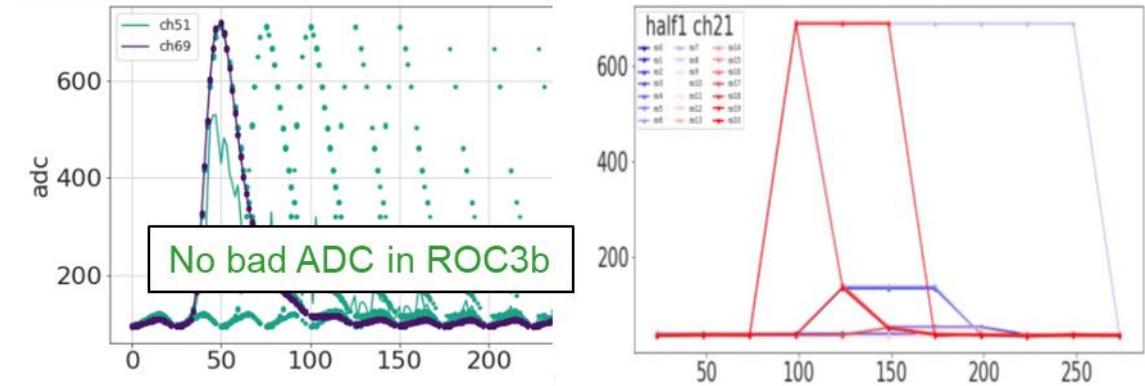

# The HGCROC3 saga

- **HGCROC3** is the final version of the chip

- All final functionalities

- Previous versions were prototypes

- **HGCROC3a (December 2020)**

- Performance generally very good

- Few bugs

- DRAM bitflips 0 > 1 → Need a fix on the board

- Statistically rare ADC conversion error → low yield

- TDC issues: ToA in BX+2, poor start-up sequence → not optimal timing performance

- Used on module assembly, system test and beam test

- **HGCROC3b (May 2023)**

- Bugs confirmed as solved by design

- DRAM, ADC, TDC

- Must be the production version

- Unfortunately, some new issues were seen...

# HGCROC3b bugs → HGCROC3c → HGCROC3d

| Submission date             | May<br>2023 | →                                               |             |                                                                                                                                                                                                                                                                    | July 07<br>2024                                                                           | →                |                        |  |

|-----------------------------|-------------|-------------------------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------|------------------------|--|

|                             | ROC3b       | Issue                                           | Grav<br>ity | Cause                                                                                                                                                                                                                                                              | ROC3c<br>meta fix                                                                         | result           | ROC3d<br>metafix       |  |

| Fixed                       | Bug1        | « ToT hole »                                    | 4           | 3B metastability fix : Synchronisation problem in the TDC control logic occurring at low TOT.                                                                                                                                                                      | adding a delay cell in the TOT synchronisation logic.                                     | fixed            | Unchanged (as 3C)      |  |

|                             | Bug2        | « ToA/ToT outliers »                            | 5           | 3B TID fix : Set up & hold time violation between the TDC latch and register. Seen in some corners. Causing an error on the TOA & TOT measurement.                                                                                                                 | Adding delay in encoder. Introduction of a buffer to break a long RC path.                | fixed            | Unchanged (as 3C)      |  |

| Roc3b unusable for<br>HGCAL | Bug3        | SEE TDC<br>Digital current increase             | 1           | Already in 3A but not observed : Source traced to TDC FIFO.<br>SET can cause Tri-state buffers on the FIFO output bus to go into conflict.                                                                                                                         | None                                                                                      | unchanged        | Unchanged (as 3B & 3C) |  |

|                             | Bug4        | SEE Analog current increase.<br>TDC not working | 3           | Already in 3A but not observed : Increase of Master TDC DLL Control V. Due to an SEU in the control logic of the DLL generating the Control V. Leads to a non functioning master TDC affecting half a chip. Reset by I2C intervention. Can also occur at Start-up. | removing a flip-flop in the Master TDC DLL Control state machine.                         | fixed            | Unchanged (as 3C)      |  |

| Roc3b → Roc3c → Roc3d       | Bug5        | SEE ToA Gray encoder errors                     | 2           | Already in 3A but not observed : SET in TOA gray code data first two MSBs. The counter is triplicated but not its reference clock tree.                                                                                                                            | automatic resynchronization of counter between 40MHz and 160MHz at the end of each cycle. | Now gets blocked | Back to 3B             |  |

|                             | Bug6        | CM ESD sensitivity                              | 2           | Already in 3A but observed with sparks at module assembly                                                                                                                                                                                                          | None                                                                                      | unchanged        | Unchanged (as 3B & 3C) |  |

| Roc3b unusable for<br>HGCAL | Bug7        | I2C bad phase                                   | 2           | Already in 3A but observed with long bus and bi-directional SCL                                                                                                                                                                                                    | Remove 2 synchronizers                                                                    | fixed            | Unchanged (as 3C)      |  |

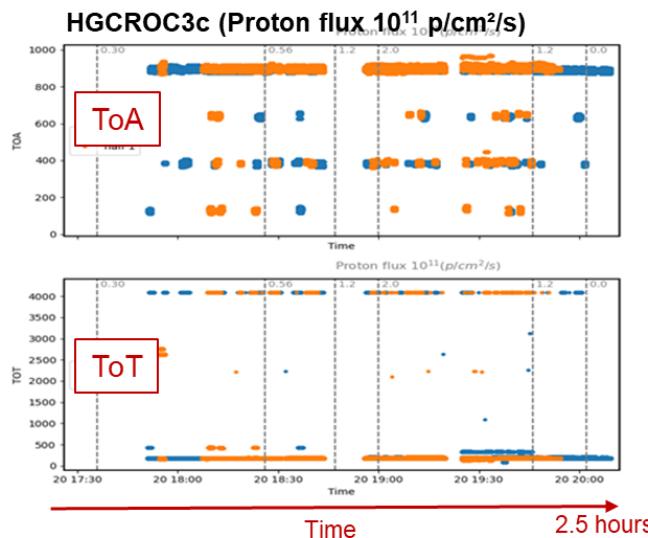

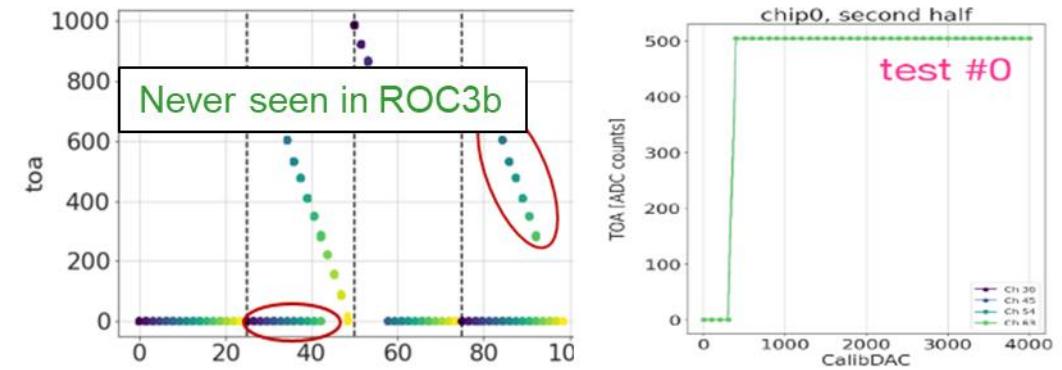

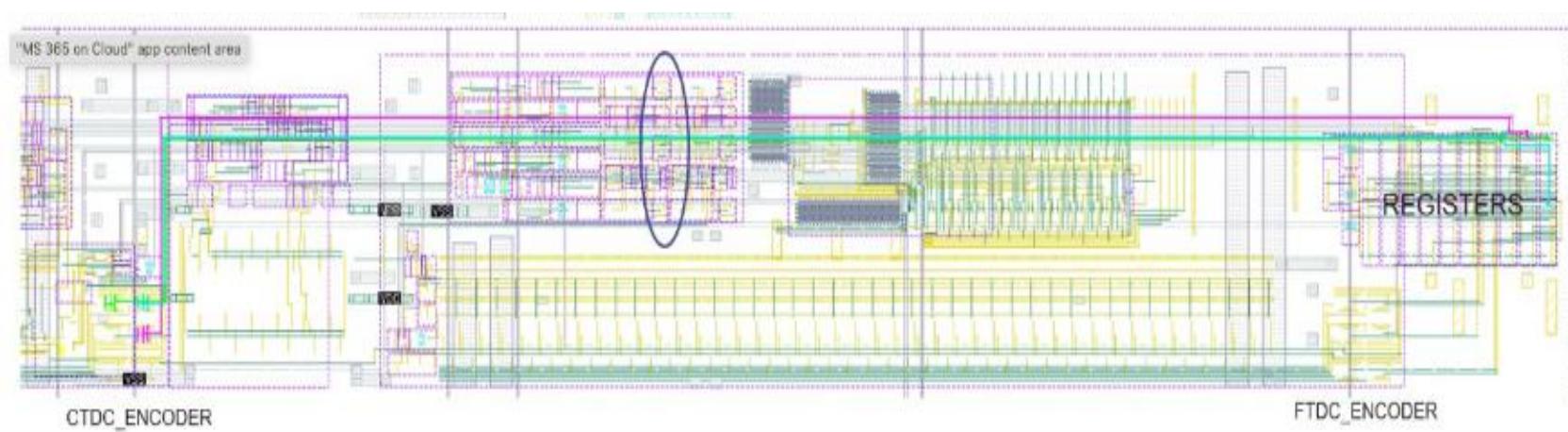

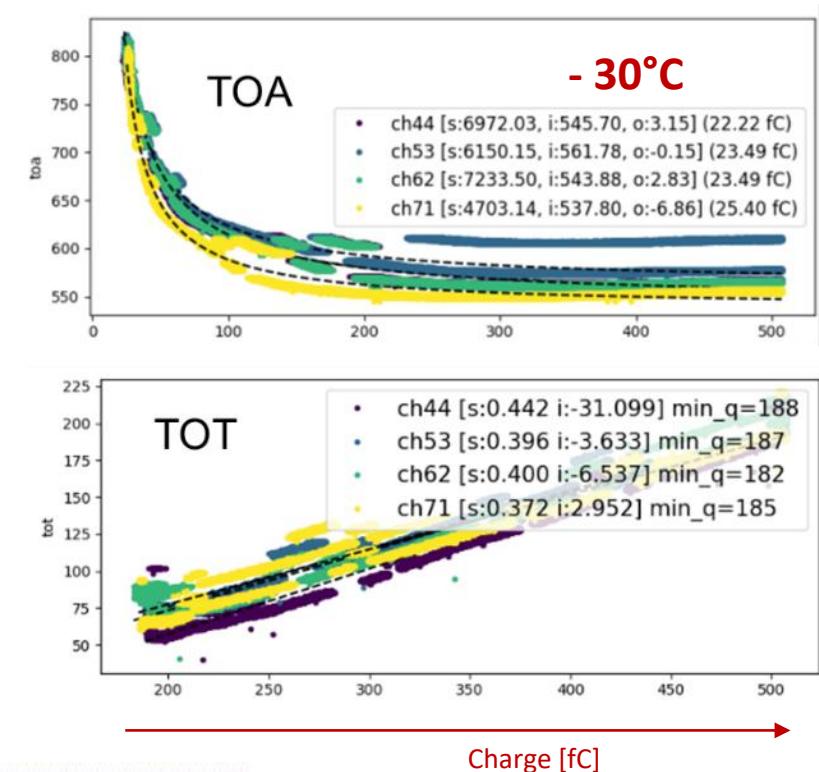

# HGCROC3b bug 2: ToA/ToT outliers

- A fix in roc3a caused this bug and made the TDC unusable

- Jumps in the TDC measurements were observed, both in ToA and ToT

- The magnitude of the jumps pointed to the coarse TDC

- Worse at cold

- Hard to understand and reproduce in simulation

- Required post-layout simulations, under specific corners with a lower supply voltage

- It was necessary to inject closely spaced signals to demonstrate the TDC jumps

- Issue was caused by excessively long routing lines driven by an undersized buffer

- By simply modifying the internal routing of the TDC, we were able to reuse nearby components to extend encoder duration and insert a buffer

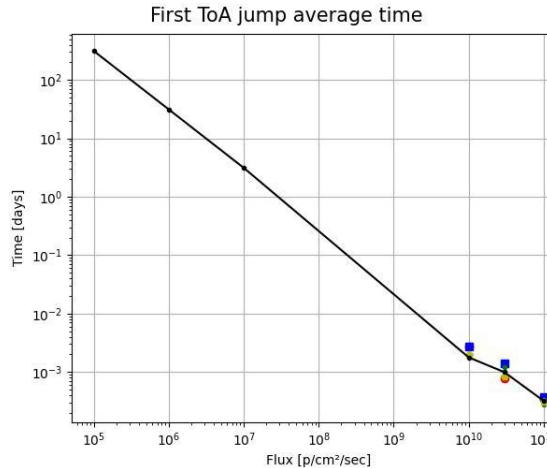

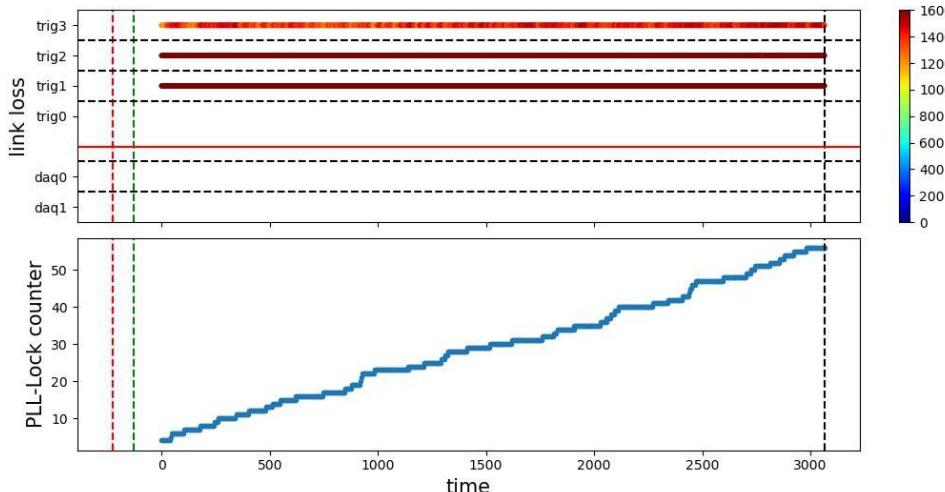

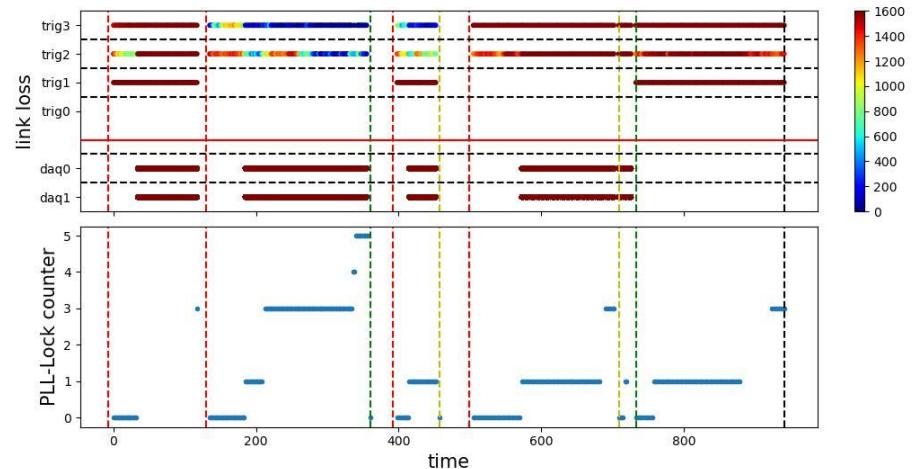

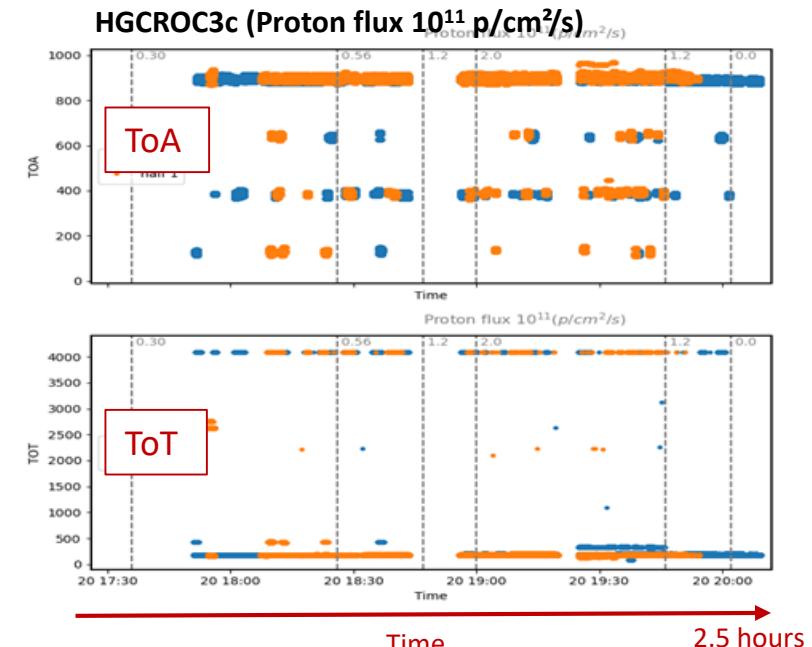

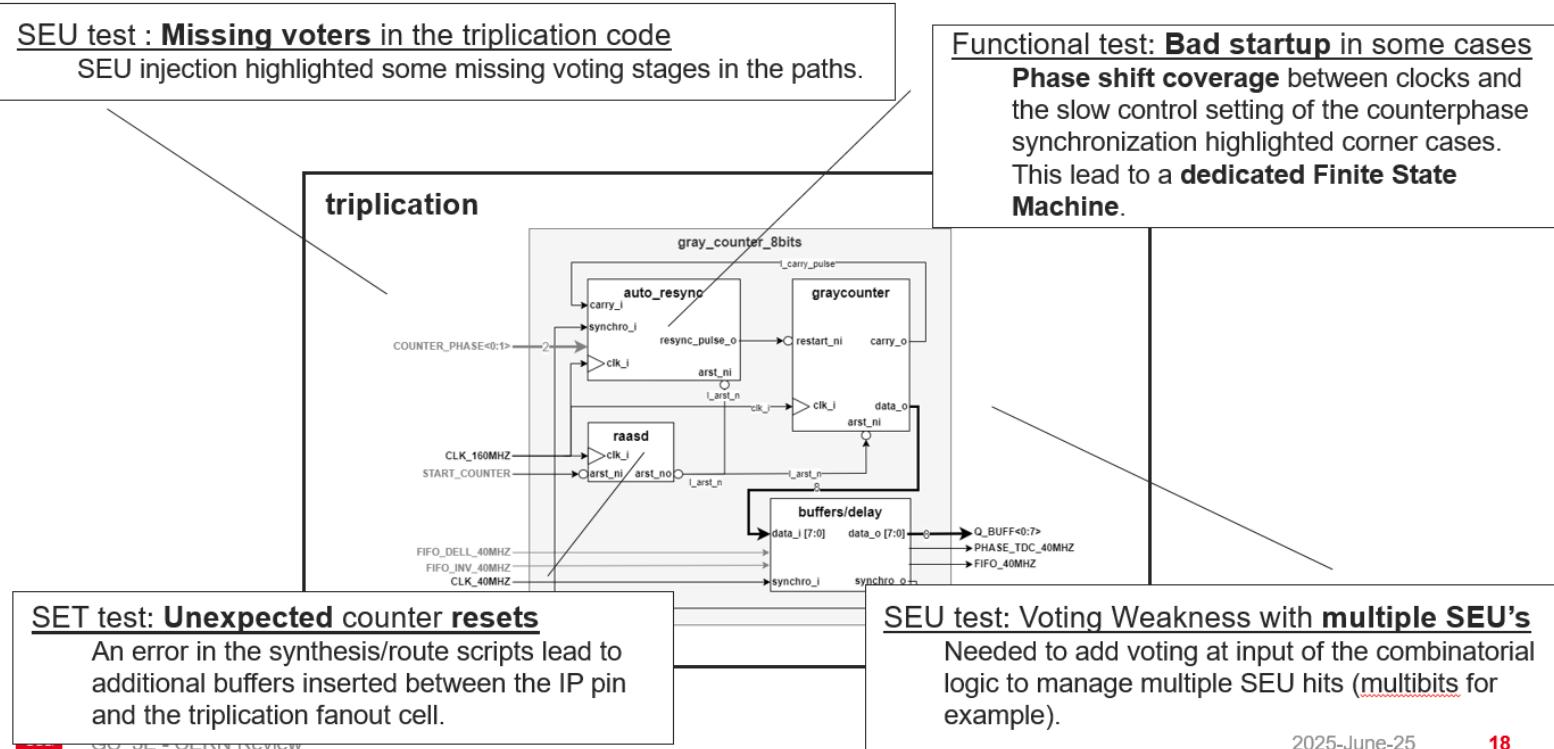

# HGCROC3b bug 5: SEE ToA gray encoder errors

- Present in the previous versions, but only observed with 3b version during a SEE campaign with 70 MeV protons

- Observed ToA jumps when irradiating with protons at high flux

- The magnitude of the jumps pointed to another part of the TDC, a counter responsible for the 2 most significant bits of the ToA

- Asynchronous triplicated counter, but still too sensitive to SEE

- By changing only the metal routing, we believed we could implement a correction

- Allowing counter jumps but correcting them within a maximum of 1.6  $\mu$ s

- But ToA still jumped, and now **ToT get stuck** (frequently at the max) and therefore impact on the **Trigger path**

- The TDC is now sensitive to 2 consecutive SEE, which happens **less often but much more problematic** (blocked state)

- Those effects were not seen in simulations as they were unfortunately carried out in a less sensitive environment

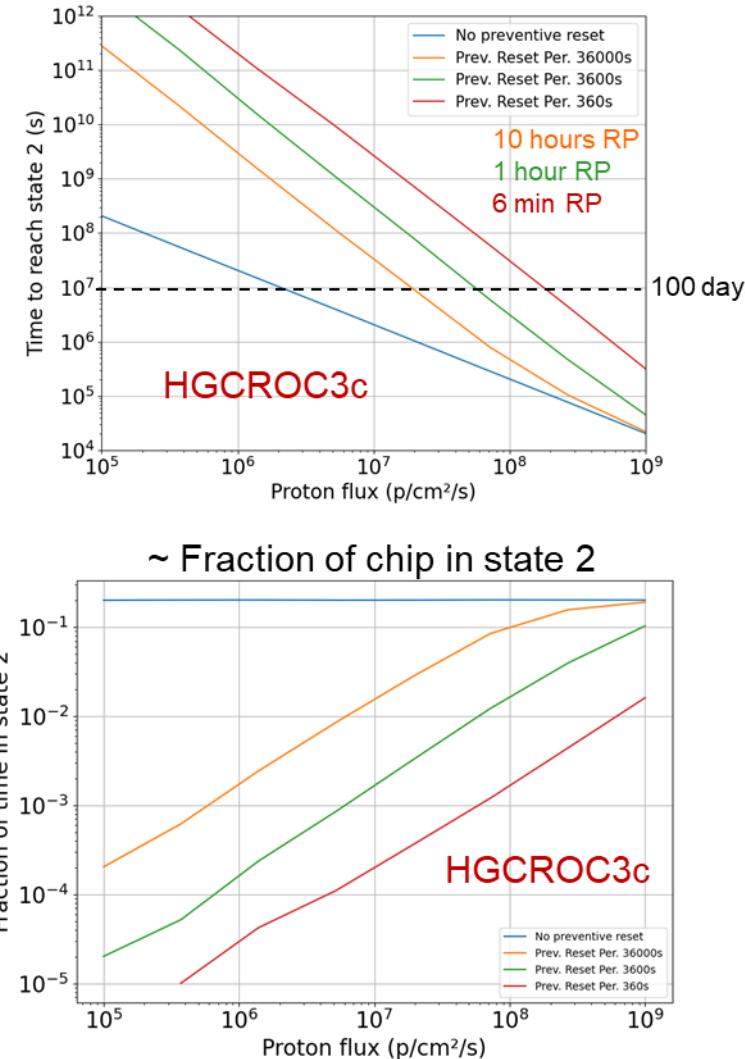

# HGCROC3b bug 5: SEE ToA gray encoder errors → HGCROC3c bug

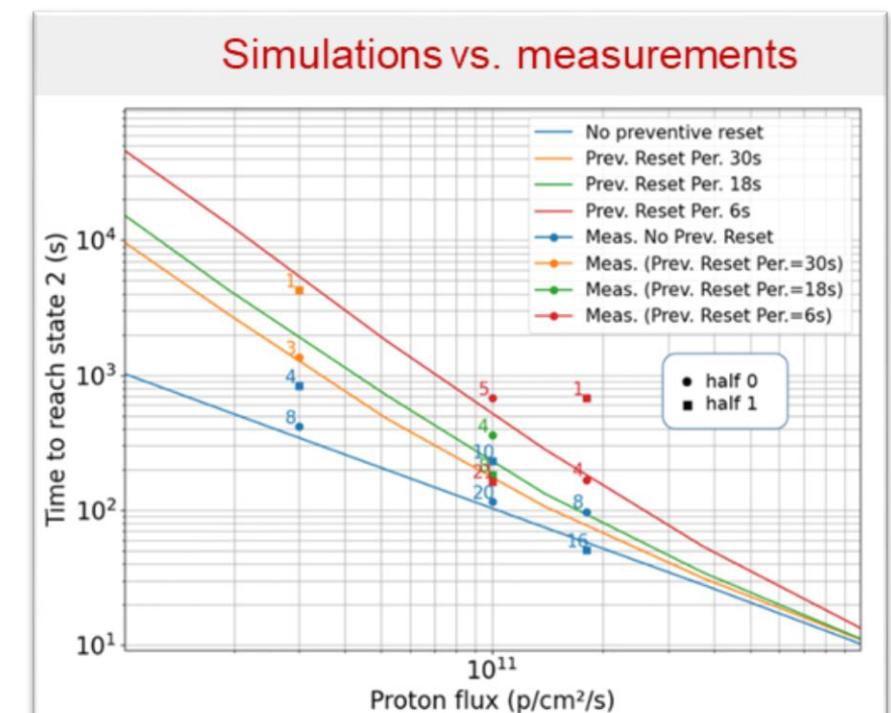

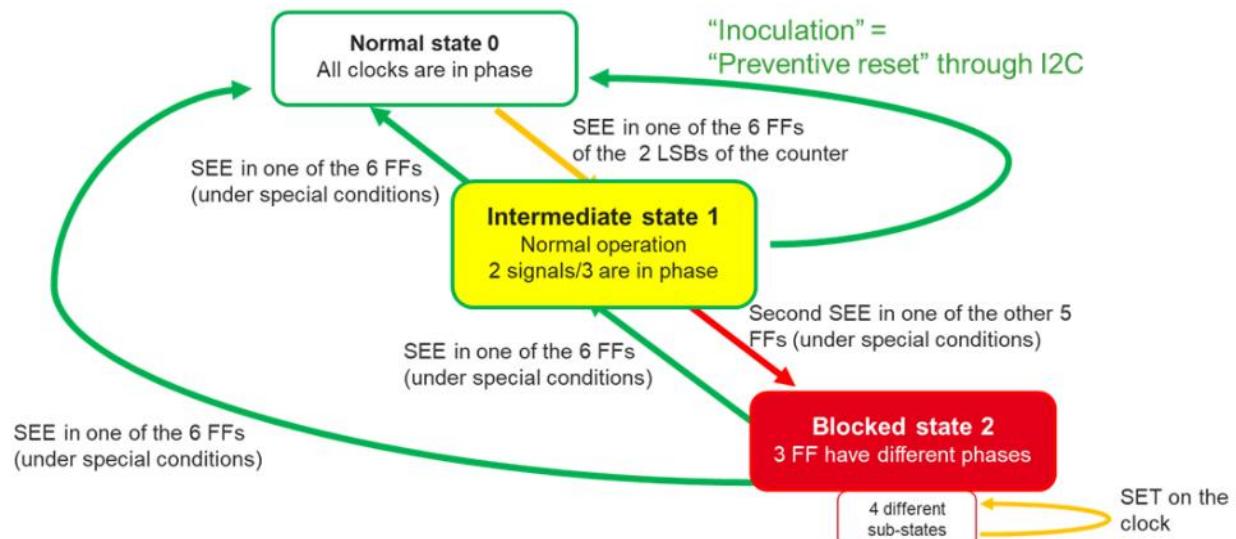

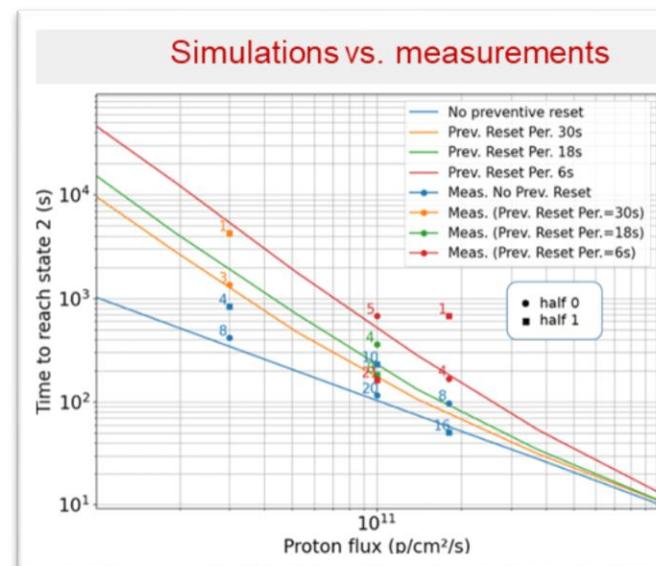

This can be explained by the TDC counters transitioning into three different states after SEEs:

- In the normal state (**state 0**), after power-up, all the counters are in phase.

- When a first SEE occurs in one of the two LSBs of the three counters, there is no visible effect because the majority voter provides the correct value. However, one of the counters is now (and remains) out of phase since there is no auto-correction (**state 1**).

- A preventive I2C toggle (or "**inoculation**") can reset the counters back to state 0.

- When a second SEE occurs in one of these two LSB counters, the majority vote can now be wrong, and the voting mechanism removes the clock from the subsequent counters (**state 2**). The TDC is now blocked. The ToA and ToT values can now be incorrect and remain so.

- Only another SEE can recover the blocked counter or a **power cycle**

# HGCROC3b bug 5: SEE ToA gray encoder errors → HGCROC3c bug

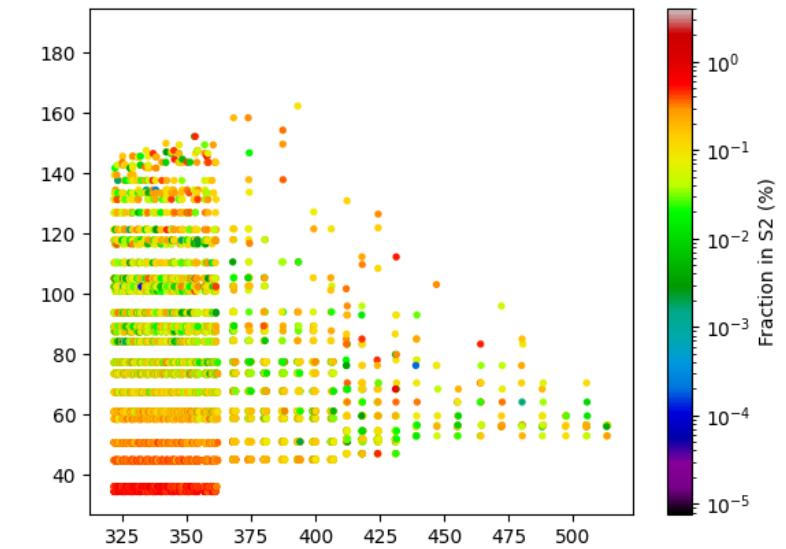

- Since inoculation can be applied to reduce the probability of the chip entering in state 2, HGCROC3c can be installed in back layers of HGCal

1/4 full detector, 100 days, No Power cycling,

SC reset period : 1 hr

Mean nb of HC entered in S2: 541

Mean nb of transitions to S2: 633

Mean nb of HC simultaneously in S2: 21

Averaged fraction of time spent in s2: 0.071%

# HGCROC3 bugs

## Main issues solved during verification cycle

| Version | Features |                         | SEU | SET | Comment                                                                                                                                              |

|---------|----------|-------------------------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | startup  | Auto-restart            |     |     |                                                                                                                                                      |

| 3C      | ✓        | ✓                       | ✗   | -   | Blocking in test beam.<br>Graycounter blocking in simulation.                                                                                        |

| 3D      | ✓        | not impl.<br>(as in 3B) | ✗   | -   | In simulation, no blocking behavior, but spurious counting due to unexpected restarts (as in 3B)<br>Need to be confirmed by <a href="#">testbeam</a> |

| 3E      | ✓        | ✓                       | ✓   | ✓   | Need to be confirmed by <a href="#">testbeam</a>                                                                                                     |

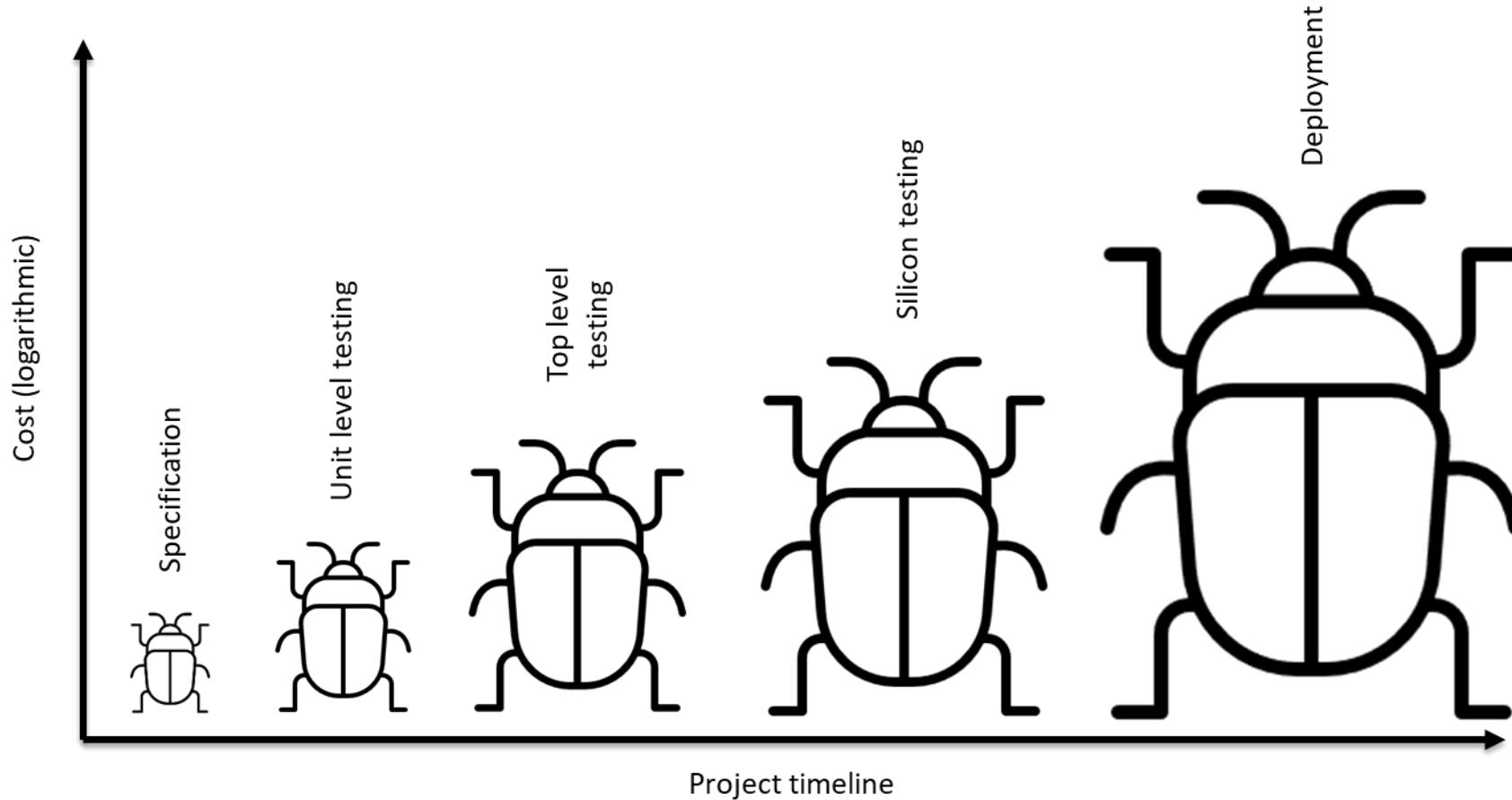

# Que peut-on en conclure?

- La vérification est certes importante et nécessaire!

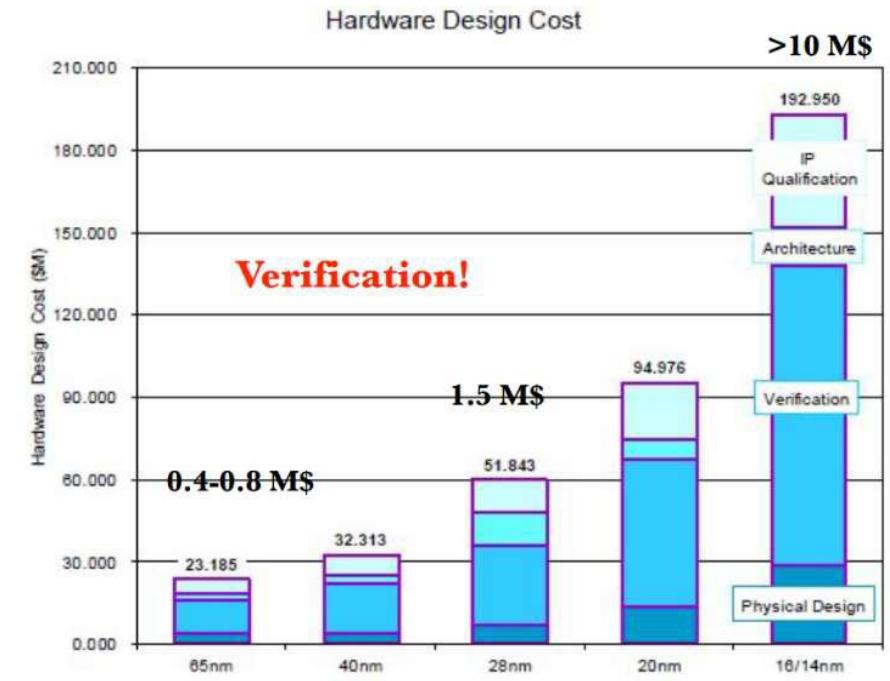

- + 70 % de la charge d'un grand projet aujourd'hui

- Besoin d'experts, autres que les designers

- Mais les tests sont encore plus importants!

- La vérification est rarement totalement agnostique et exhaustive

- Les modèles peuvent être faux ( $\mu$ F capa dans ECON-D)

- On simule parfois dans les conditions favorable (LpGBT, HGCROC)

- Il est extrêmement difficile de reproduire les effets des irradiations sur l'analogique (bPOL12, HGCROC)

# En conclusion

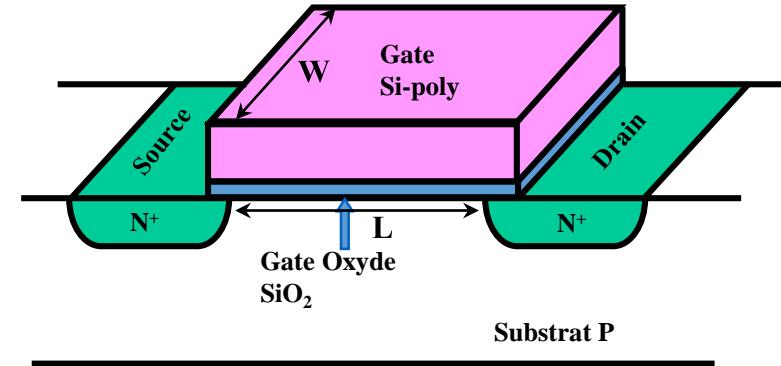

# « CMOS scaling »

- Reduction of dimensions

- Gate length : L

- Oxide thickness :  $t_{ox}$

- Reduction of power supplies

- Reduction of power dissipation

- Improvement of speed in  $1/L^2$

- Transconductance :  $g_m \propto W/L$

- Capacitance :  $C \propto WL$

- speed :  $F_T = g_m/C \propto 1/L^2$

- Reduction of costs (?)

- Increase of integration density

- Radiation hardness in bonus !

- Less trapping in gate oxide

Principle of Nchannel MOSFET

# Défis structurels

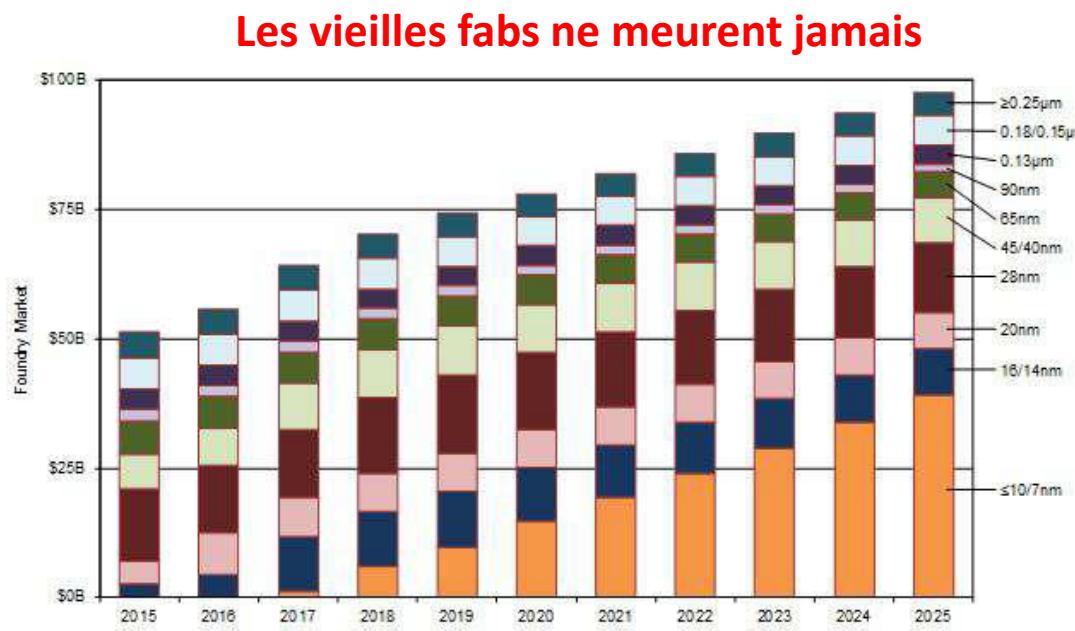

- Accès aux technologies plus fines (coûts) et pérennité

- L'infrastructure des instituts devra s'adapter pour correspondre aux nouvelles nécessités en termes de masse critique, de compétences nouvelles (DoT, vérification)

**La part de la vérification est croissante → nouveau métier**

# Défis techniques

- Mêmes performances analogiques

- Timing ( $\sim 1 - 10$  ps)

- Des blocs mixtes de plus en plus précis et rapides

- Key IP: ADC, LDO, Data transmission, TDC

- De plus en plus de digital intégré

- Algorithme, processing de données, intelligences dans le chip (processeur intégrés/custom)

- Mémoire

- Liens rapides  $\sim$  Gbps

- Radiations requises par les futurs expériences

- Besoin d'être adressé dans un effort commun international

- Intégration de plus en plus fine

- Pixel plus petits, granularité fine latéralement et longitudinalement

- Basse conso

- Intégration, packaging, post-processing

- Couteux

- Accessibilité (reliable et NDA)

- Accès aux techno de pointes est souvent restreint au grand projets, et sera donc facilité par une approche community-wide