**IN2P3**

Les deux infinis

# La microélectronique dans les expériences

Damien Thienpont

# Remerciements

- Pour réaliser ce cours, je me suis inspiré de ceux de

- Généralités: Christophe de La Taille, Gianluigi De Geromino

- Numérique: Frédéric Dulucq, Christophe Flouzat, Xavir Llopart

- Effets des radiations: Giulio Borghello, Szymon Kulis

- J'ai tenté le plus souvent de mettre les slides en français (les transparents...)

- Mais il en reste pas mal en anglais...

- Conception et tests (caractérisation, intégration sur détecteur) de circuits intégrés (ASICs, chips) pour les expériences de physique des particules + activités de R&D et de valorisation

- ASIC dits de «**Front End**» (**au plus près du détecteur**): bas bruit, large dynamique, tolérant aux radiations, faible puissance et haute fréquence.

- Fortes compétences dans le **design de circuits mixtes**: FE analogique et traitement numérique interne des signaux analogiques.

**Simulations**

**Layout**

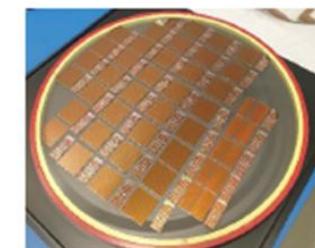

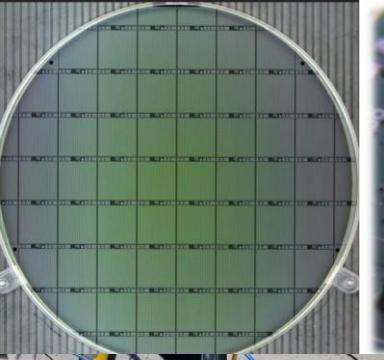

Fabrication des wafers, découpe,

découpe et mise en boîtier =

compagnies privées

**Caractérisation**

- Caractérisation des ASIC: cartes de test, FPGA (firmware), prise et analyse des données (python)

# Plan du cours

- Introduction: de l'électronique partout dans nos détecteurs

- Fondamentaux de l'électronique

- Rappel général des bases de l'électronique

- Détecteur et préamplificateur

- Conversion Analogique/Numérique

- Numérique

- Le langage HDL (VHDL ou Verilog), synthèse, vérification

- De plus en plus de numérique dans les ASICs

- Design Flow: Analog-on-Top ou Digital-on-Top

- Bruit électronique

- Fondamentaux

- Filtrage, shaping

- Techniques de mesure

- Effets des radiations sur l'électronique

- TID et SEE

- Campagnes d'irradiation, performances, cross-section

- Extrême importance des tests: sur table, radiation, beam, système

- La mesure de temps

- Généralité

- Les TDCs

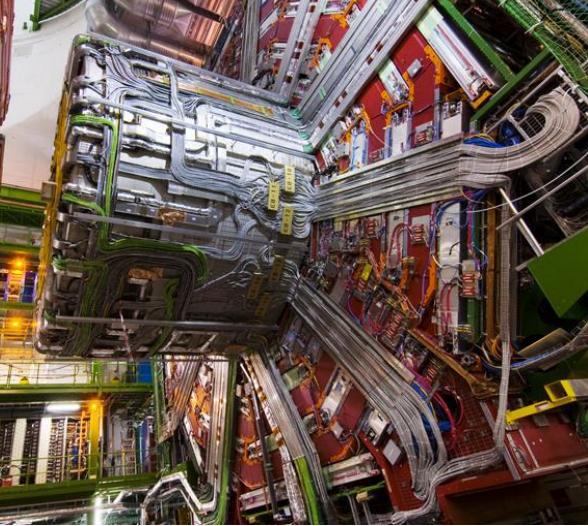

- Beaucoup d'électronique dans les expériences

- Déterminante dans la performance des détecteurs

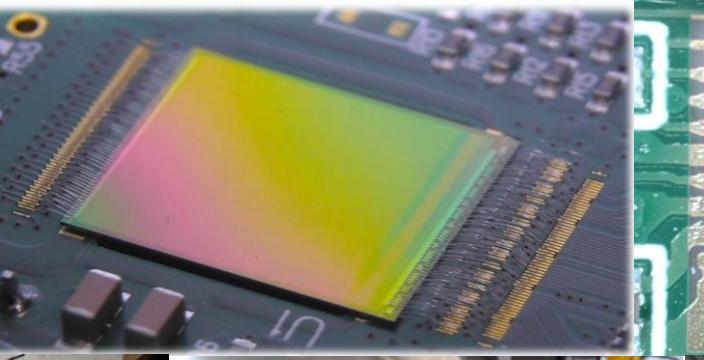

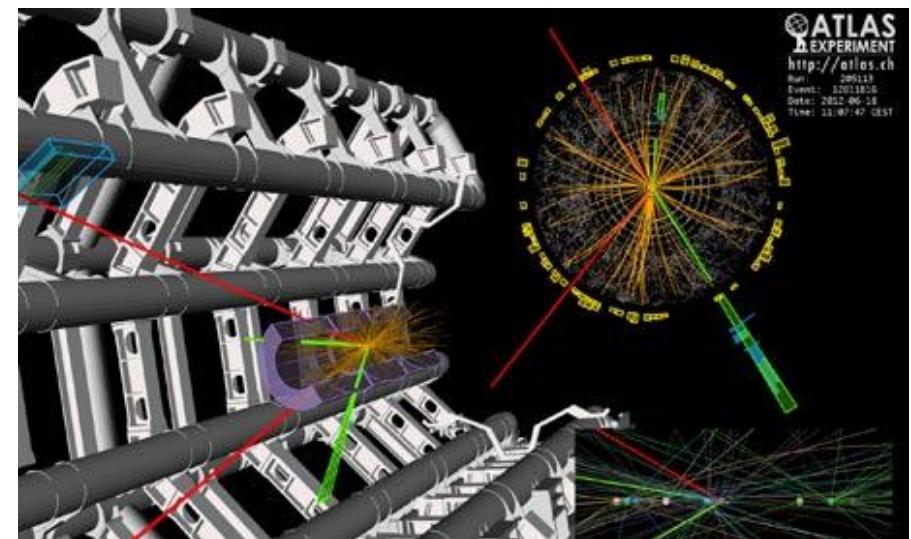

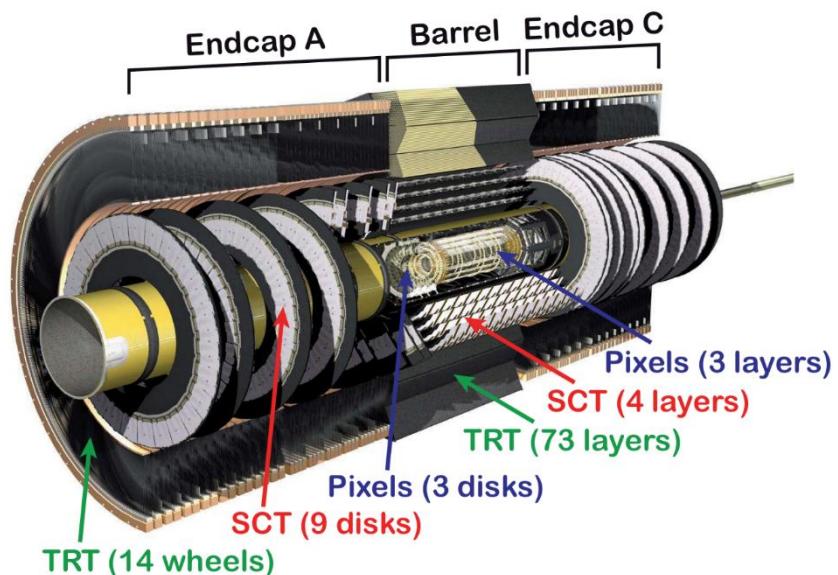

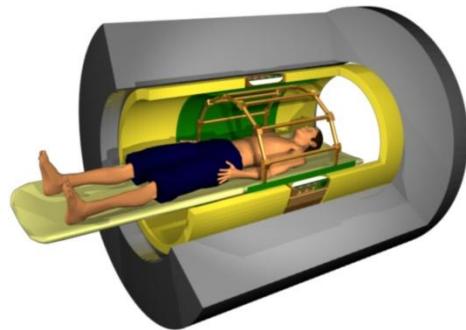

# Mesure de la position: x, y, z

## Tracker

- Mesure de la position des particules (chargées ou pas)

- Reconstruction des traces dans le détecteur

- Identification du/des vertex(s)

- Identification des particules

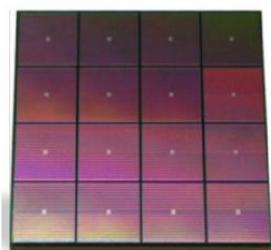

- L'électronique permet de meilleurs détecteurs

- Millions de pixel, lecture « presque » binaire

- Très haut niveau de radiation

- Seulement rendu possible par les ASICs

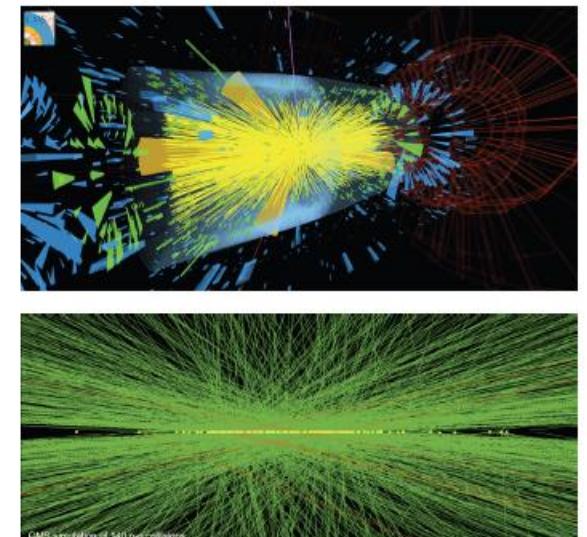

Pileup 140-200 at HL-LHC

(over 2x w.r.t. LHC busiest interactions)

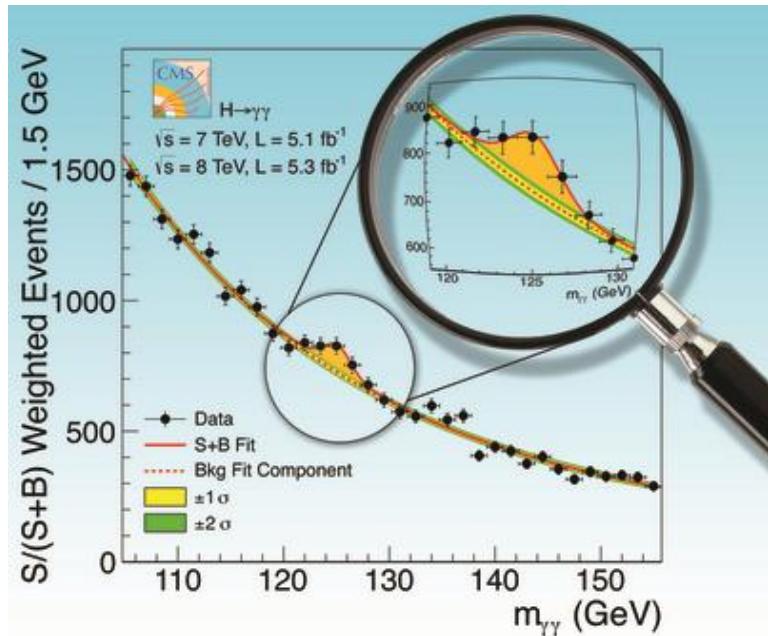

# Mesure de l'énergie

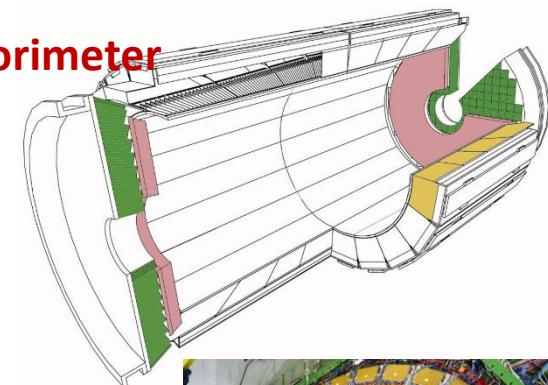

## Calorimètre

- Mesure de l'énergie des particules

- Grande dynamique de lecture:  $10^3$  à  $10^5$  (10 – 18 bits)

- Précision autour de 1%

- Résolution de l'énergie

- Importance: bas-bruit, uniformité et linéarité, calibration

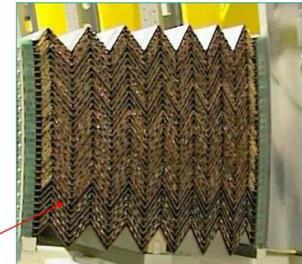

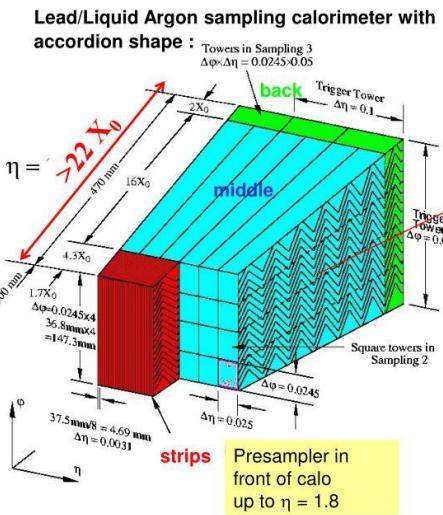

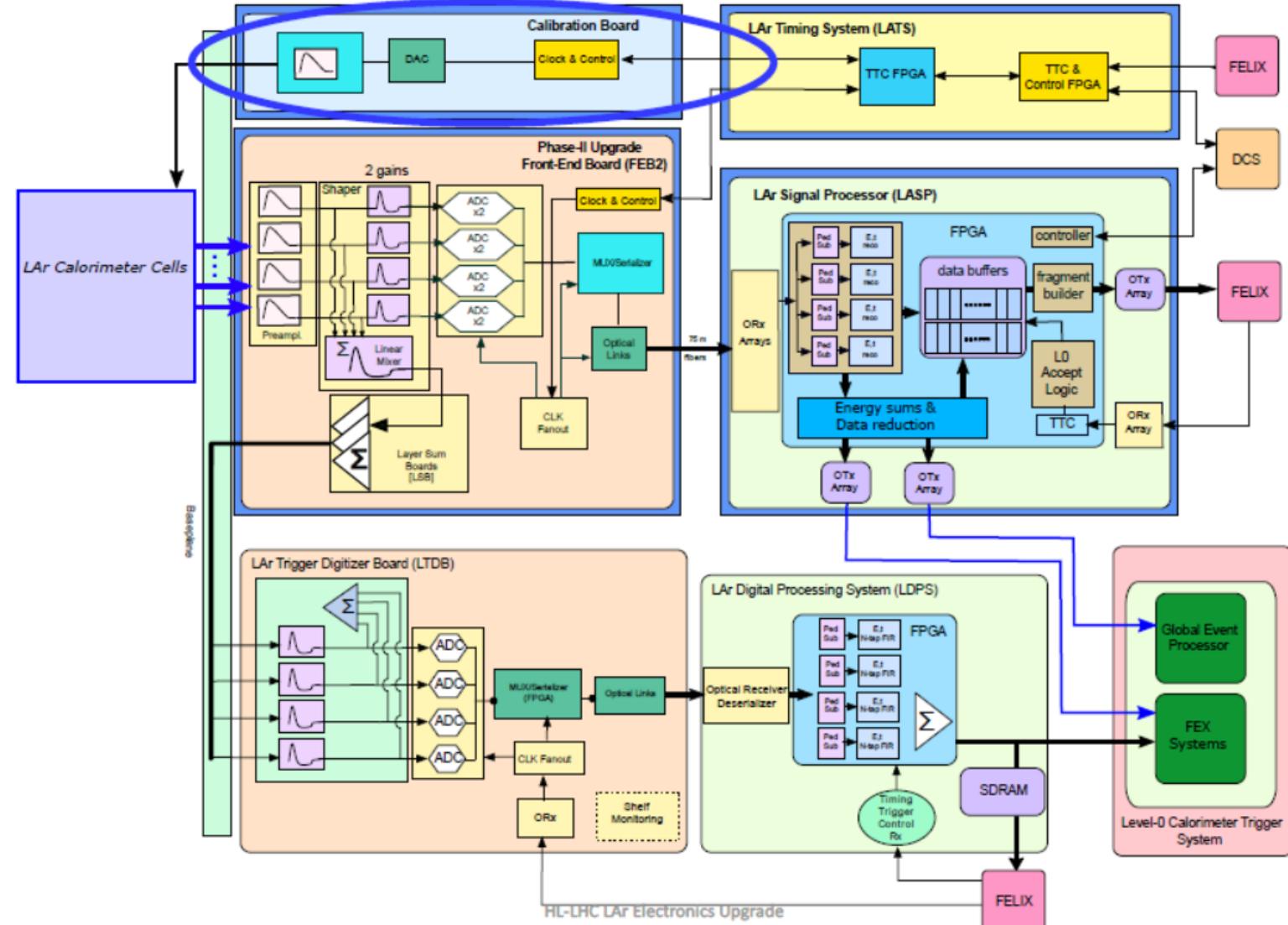

## The E.M. Barrel ATLAS Calorimeter

Main advantages:

LAr as act. material inherently linear

Hermetic coverage (no cracks)

Longitudinal segmentation

High granularity (Cu etching)

Inherently radiation hard

Fast readout possible

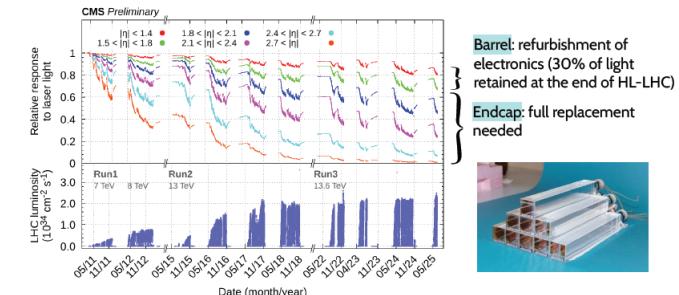

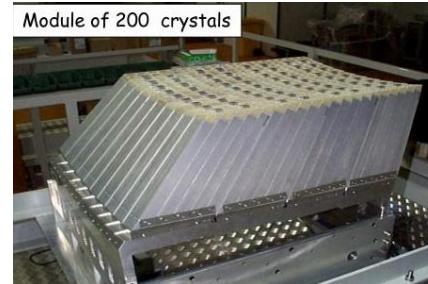

## E.M. CMS Calorimeter

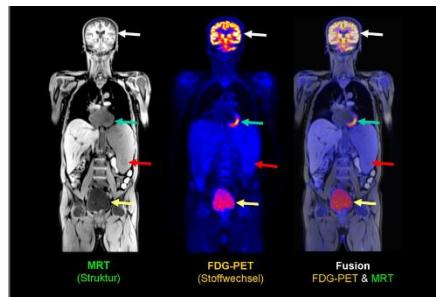

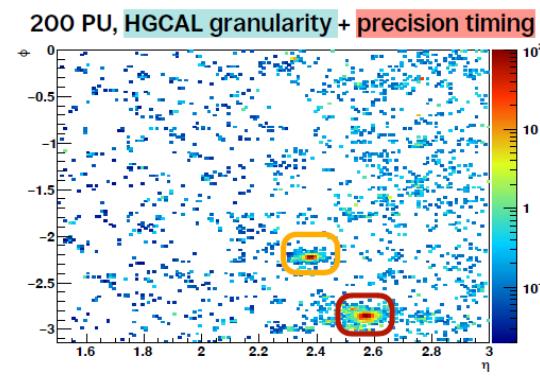

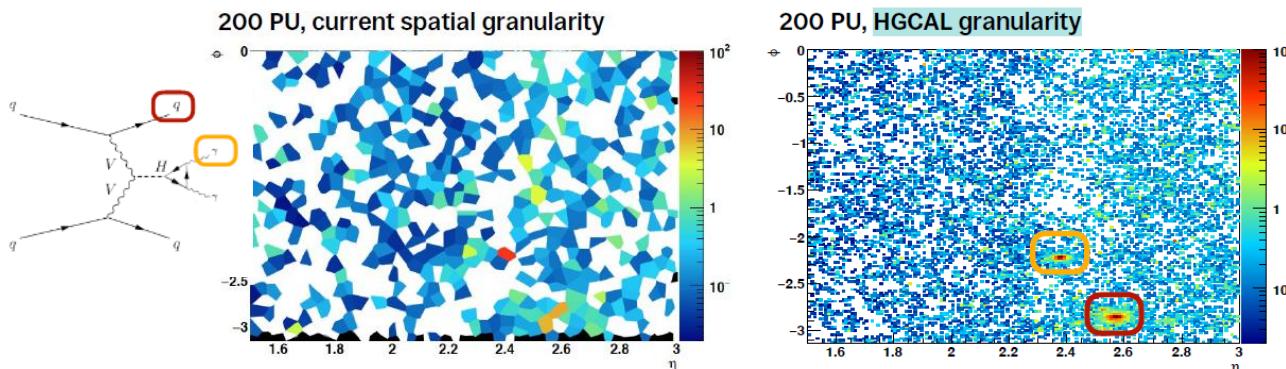

# Mesure du temps

- Mesure du temps des particules

- 1 ns à 10 ps ou moins

- Pour reconstruire et identifier les particules

- Pile-up élevés

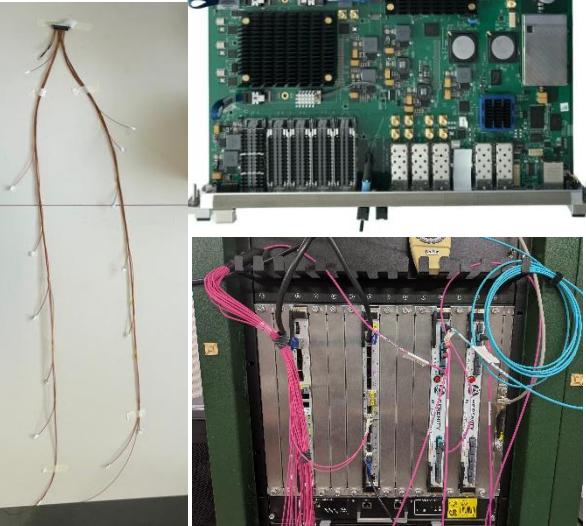

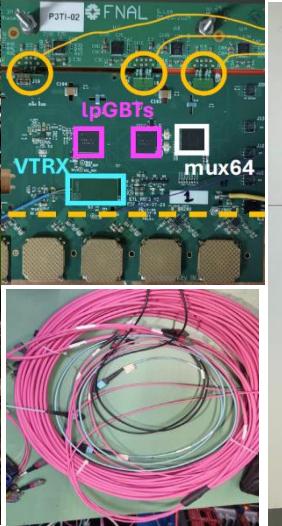

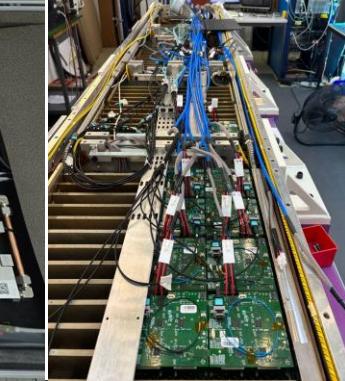

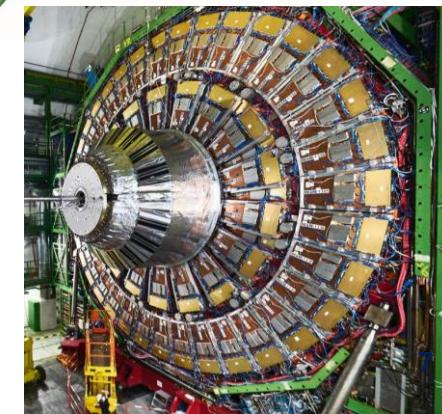

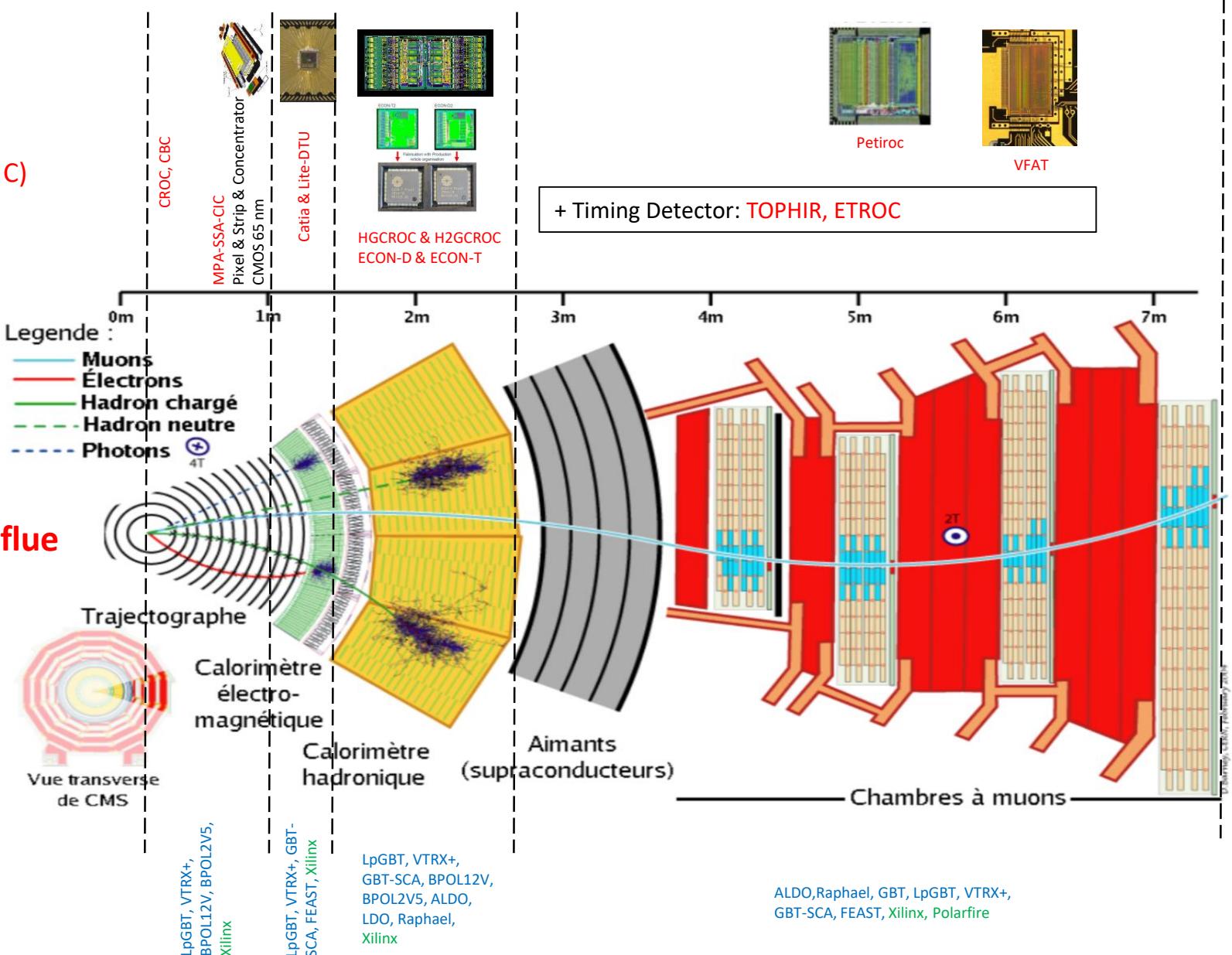

# Les ASIC dans nos expériences: upgrade de CMS

## Beaucoup d'électronique

- amplifications, filtrage → Read-Out chips (A, V, C)

- Processing & Transmission → digital elec

- Puissance, alimentation

- Chips du commerce

Les performances de l'électronique influe souvent sur celle du détecteur

$$V_{out}(t) = -\frac{Q_0}{C_f} \cdot \frac{1}{\left(1 + \frac{C_d}{G_0 \cdot C_f}\right)} \left(1 - e^{-t/\tau}\right) \quad \text{avec } \tau = \frac{C_d}{G_0 \omega_0 C_f}$$

# Les fondamentaux de l'électronique et des préamplificateurs

# Plan du cours

- Introduction: de l'électronique partout dans nos détecteurs

- **Fondamentaux de l'électronique**

- Rappel général des bases de l'électronique

- Détecteur et préamplificateur

- Conversion Analogique/Numérique

- Numérique

- Le langage HDL (VHDL ou Verilog), synthèse, vérification

- De plus en plus de numérique dans les ASICs

- Design Flow: Analog-on-Top ou Digital-on-Top

- Bruit électronique

- Fondamentaux

- Filtrage, shaping

- Techniques de mesure

- Effets des radiations sur l'électronique

- TID et SEE

- Campagnes d'irradiation, performances, cross-section

- Extrême importance des tests: sur table, radiation, beam, système

- La mesure de temps

- Généralité

- Les TDCs

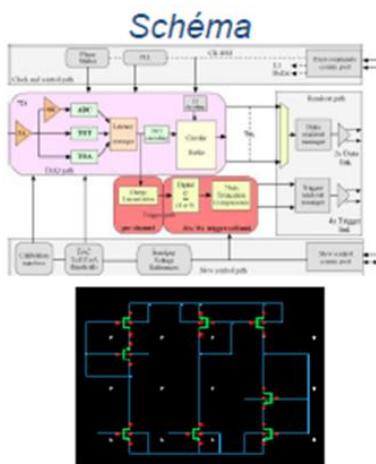

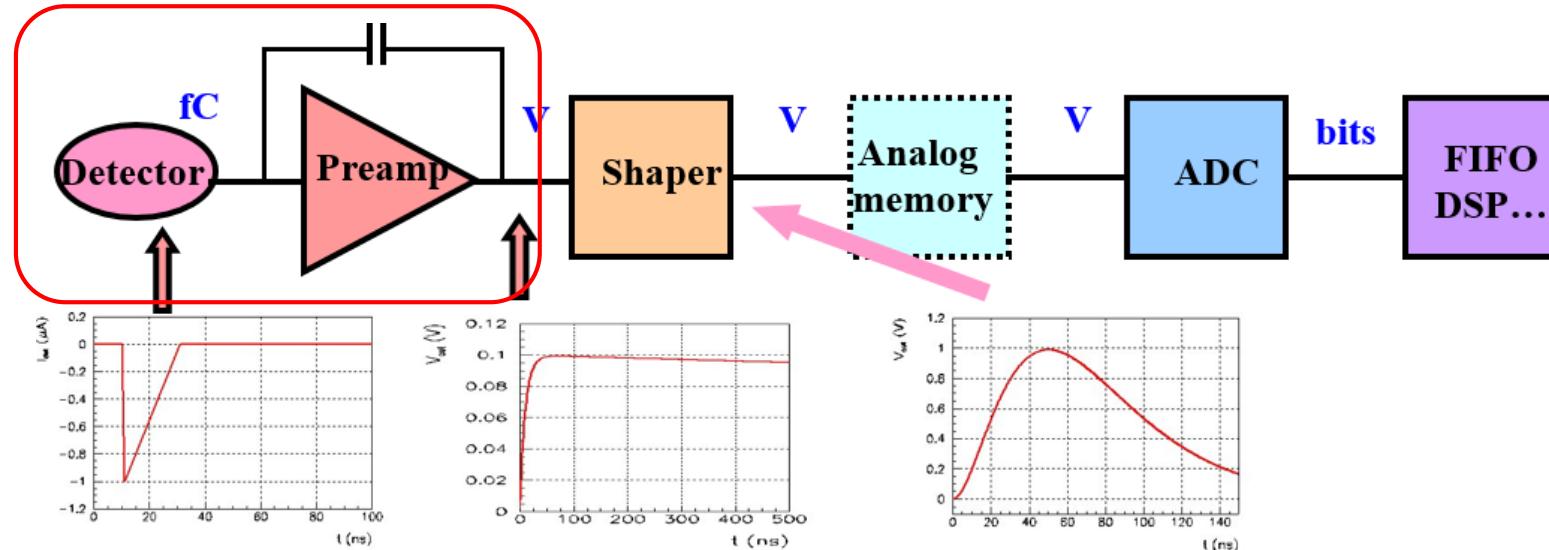

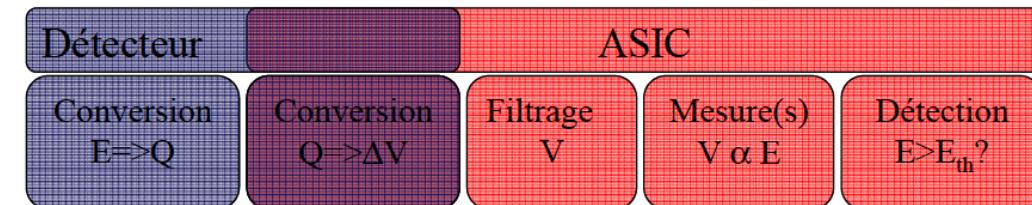

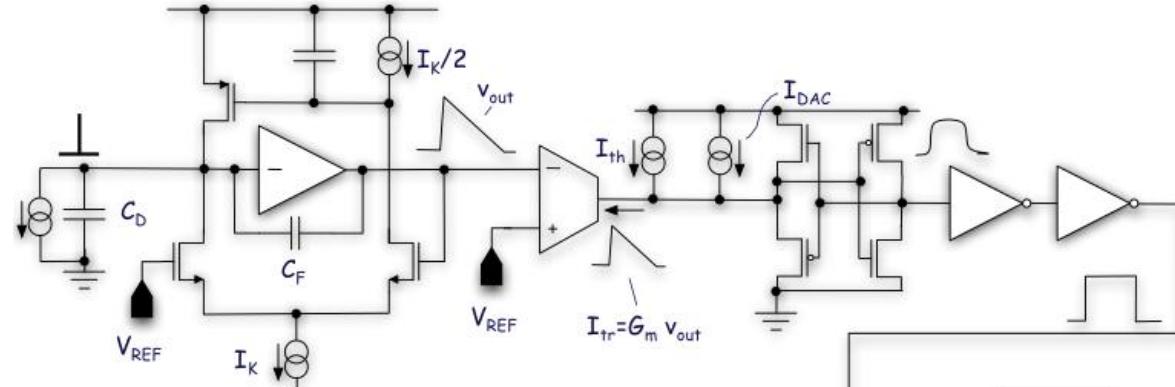

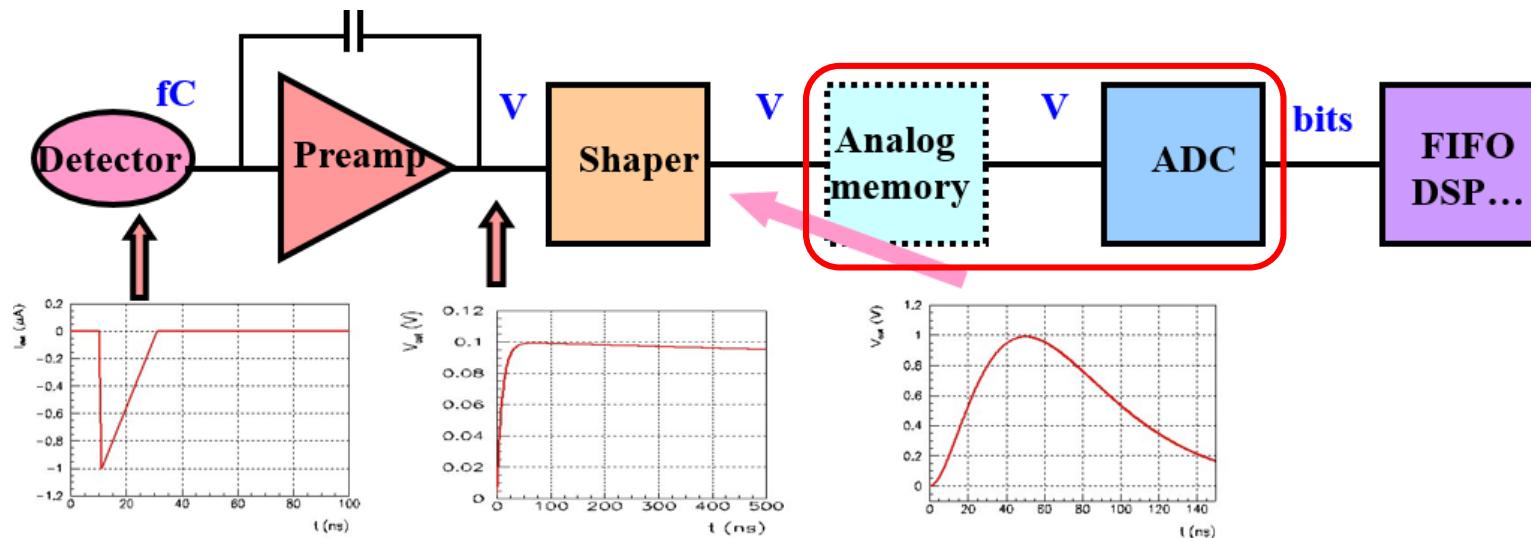

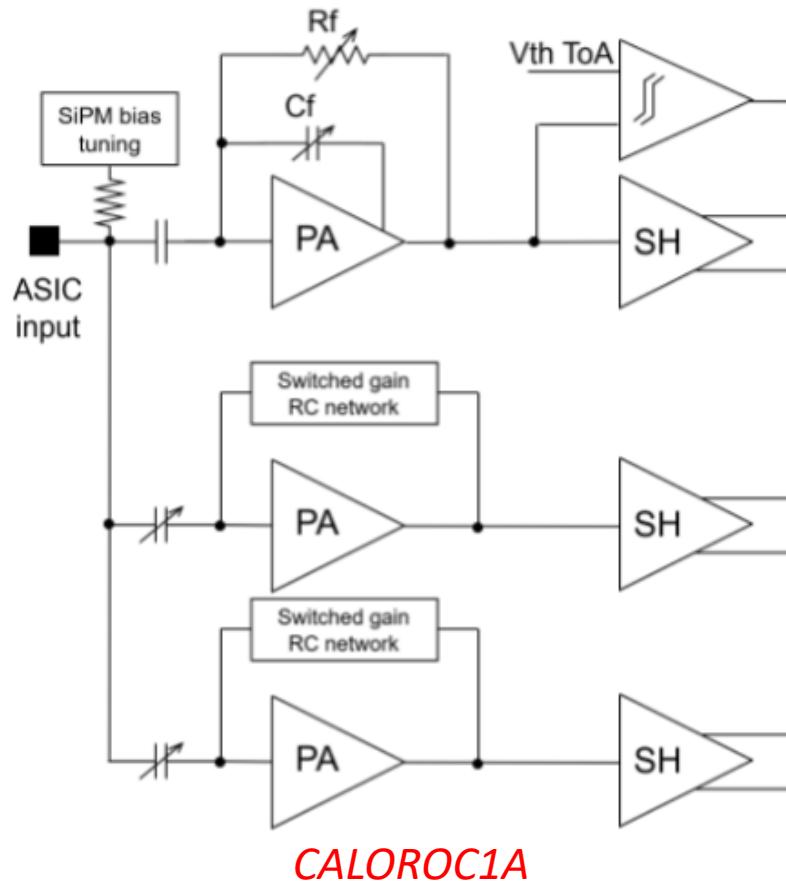

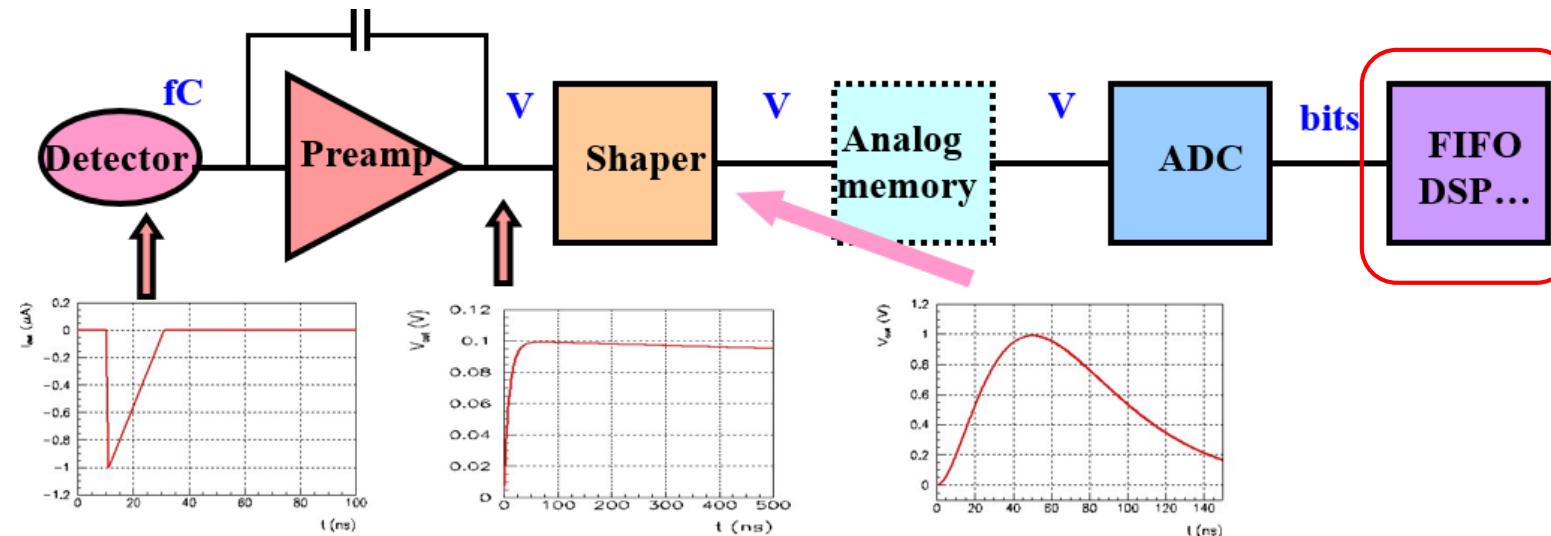

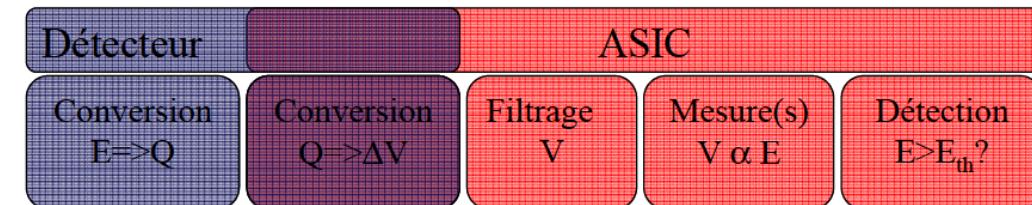

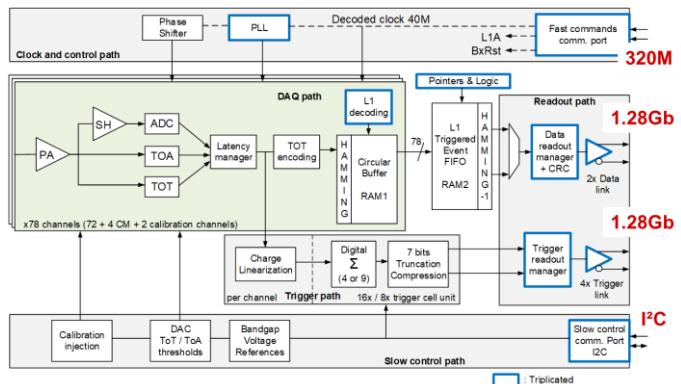

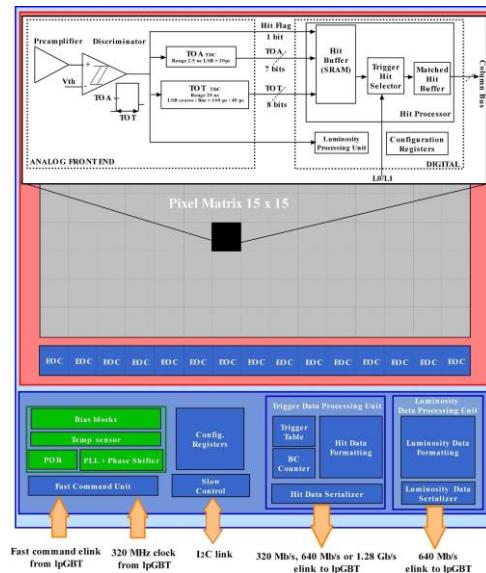

# Aperçu d'un ROC (Read-Out Chip)

- Le plus souvent, une architecture similaire

- Très petits signaux (fC) → besoin d'amplification → préamplificateur

- Mesure de l'amplitude et/ou du temps → ADC, discri, TDC

- Plusieurs milliers à millions de voies → forte intégration, basse conso

- Environnement → radiation, température

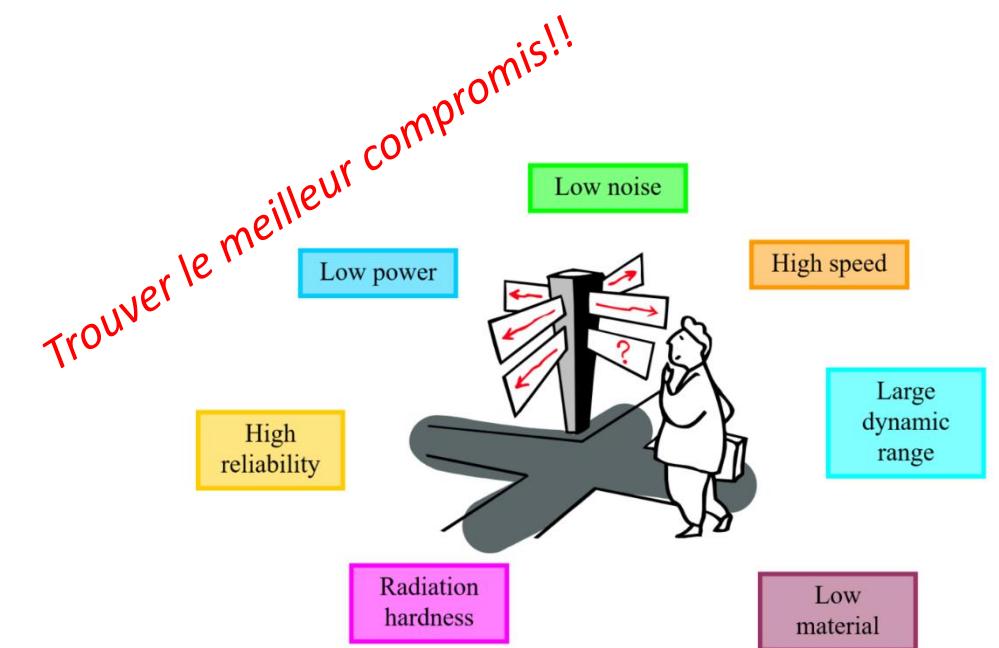

# Cahier des charges

Spécifications des circuits très différentes selon le type de détecteur et les applications

- **Chips pour trackers:**

- Readout quasi binaire, « *la performance analogique n'est pas dans le front-end* »

- 90% de numérique, GHz/cm<sup>2</sup> hit rate

- data sérialisées à 1.28 Gb/s

- 1000 – 10 M canaux/chip

- Radiations: 1 Grad

- **Chips pour Calorimètres:**

- Bas bruit, précision, grande gamme dynamique (16 bits), bande passante 1GHz

- 50% analogique et 50% numérique

- data sérialisées à 1.28 Gb/s

- 50 - 100 canaux/chip

- Radiations: 200 Mrad

- **Chips pour spatial:**

- Bas bruit

- Analogique, peu de numérique

- 1 - 100 canaux

- Radiations (1 kGy)

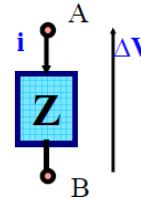

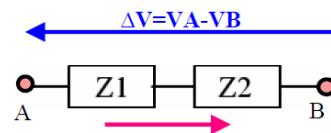

# Fondements de l'électronique: la loi d'Ohm (1)

- Loi d'ohm

- $U = VA - VB = Z * I$ , convention du signe

- Z est l'impédance

- Résistance:  $Z = R$  en Ohms ( $\Omega$ ), ne dépend pas de la fréquence de V/I la traversant, valeurs usuelles en  $\mu$ elec:  $\Omega$ ,  $k\Omega$ ,  $M\Omega$

- Capacité:  $Z(\omega) = \frac{1}{j\omega C}$  en Farads, valeurs usuelles en  $\mu$ elec: pF, nF

- $Q = C \cdot V, I = \frac{dQ}{dt} \Rightarrow I = C \frac{dV}{dt}$

- Inductance:  $Z(\omega) = j\omega L$  en Henry (H), valeurs usuelles en  $\mu$ elec: nH

- $V = L \frac{dI}{dt}$

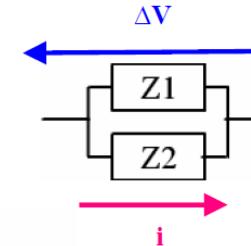

- 2 impédances en série  $Z = Z1 + Z2$ , 2 impédances en parallèle  $Z = \frac{Z1 \cdot Z2}{Z1 + Z2}$

- Puissance

- $P = V \cdot I$  en Watt (W), valeurs usuelles en  $\mu$ elec:  $\mu W$ , mW

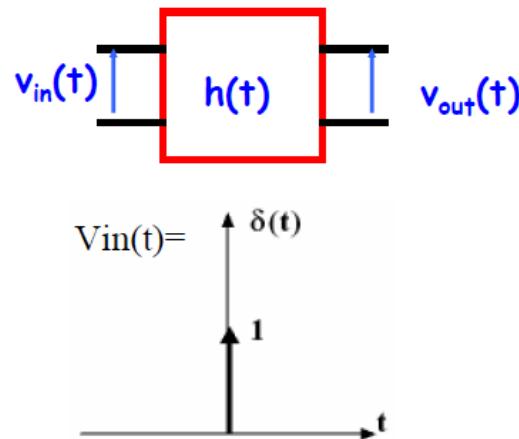

# Fondements de l'électronique: modèle temporel (2)

- Système électronique (linéaire) peut être caractérisé dans le domaine du temps ou des fréquences

- Dans le domaine temporel

- On caractérise un quadripôle par **sa réponse impulsionnelle**:  $h(t)$ , signal de sortie obtenu lorsqu'on injecte une impulsion (delta ou dirac) à l'entrée

- Le signal de sortie pour n'importe quel signal d'entrée  $V_{in}(t)$  est obtenu par **convolution**

$$V_{out}(t) = (V_{in} * h)(t) = \int_0^t V_{in}(u) * h(t - u)du$$

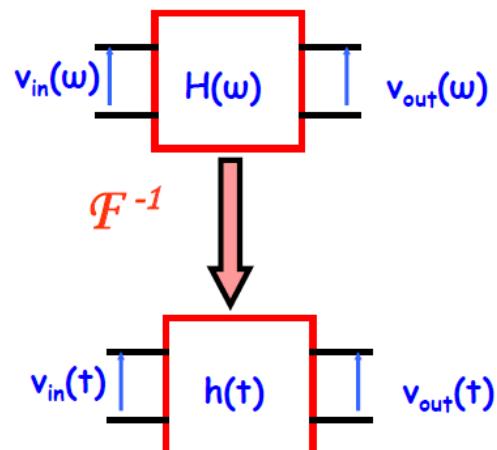

# Fondements de l'électronique: modèle fréquentiel (3)

- Domaine des fréquences

- $V_{out}(\omega) = V_{max} \cos(\omega t + \phi)$ , amplitude et phase ( $V_{max}, \phi$ )

- Fonction de transfert

- $H(\omega) = \frac{V_{out}(\omega)}{V_{in}(\omega)}$ , rapport entre signal de sortie et signal d'entrée dans le domaine des fréquences, avec  $\omega = 2\pi f$  en rad/s et  $f$  en Hz

- Parfois (souvent) noté  $H(s)$  avec  $s = j\omega$  (on trouve aussi  $p$  à la place de  $s$ )

- Correspondance en utilisant les transformées de Fourier et leur inverse:

$$X(\omega) = \mathcal{F}\{x(t)\} = \int_{-\infty}^{\infty} x(t) e^{-j\omega t} dt \text{ et } x(t) = \mathcal{F}^{-1}\{X(\omega)\} = \frac{1}{2\pi} \int_{-\infty}^{\infty} X(\omega) e^{j\omega t} d\omega$$

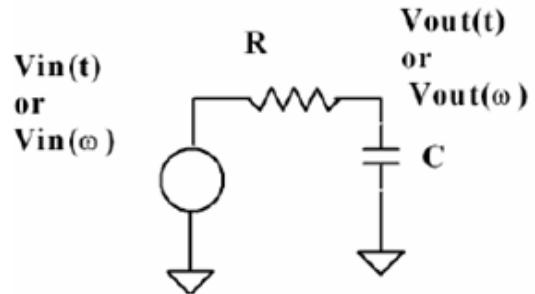

# Exemple de calcul

$$\text{Avec } v = Ri \text{ et } i = C \frac{dv}{dt}$$

On trouve:

$$RC \frac{dV_{out}(t)}{dt} + V_{out}(t) = V_{in}(t)$$

Plutôt que de résoudre cette équation différentielle, on passe dans le **domaine de Laplace** pour obtenir une **équation algébrique**

$$RC sV_{out}(s) + V_{out}(s) = V_{in}(s)$$

$$V_{out}(s) = \frac{V_{in}(s)}{1+sRC}$$

$$\text{avec } s = j\omega = j2\pi f$$

Puisque pour n'importe quel signal de sortie d'entrée  $V_{in}(t)$ , le signal de sortie est obtenu par **convolution** de ce signal d'entrée et de la réponse impulsionnelle

$$V_{out}(t) = (V_{in} * h)(t) = \int V_{in}(u) * h(t-u)du$$

Dans le domaine de Laplace, on aura:

$$V_{out}(s) = V_{in}(s).H(s)$$

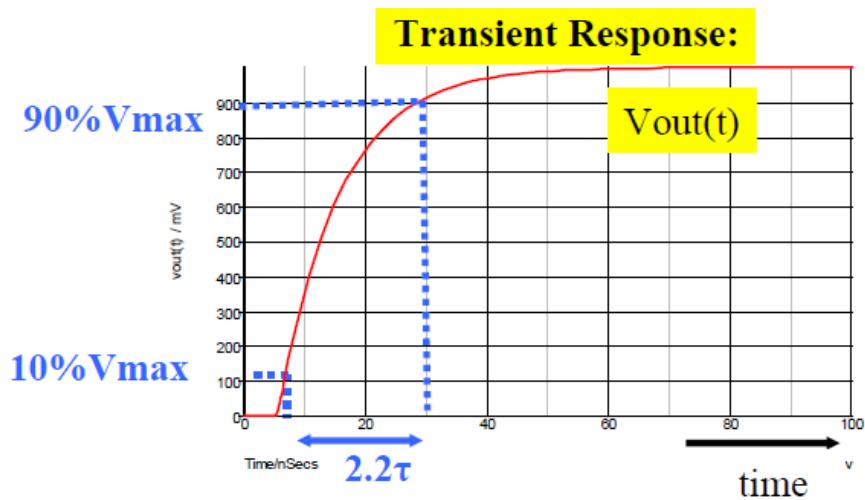

Avec notre circuit passe-bas RC et un step de tension,

$$V_{out}(s) = \frac{1}{s} \cdot \frac{1}{1+sRC} V_0$$

$$\text{Donc } V_{out}(t) = F^{-1}\{V_{out}(s)\}$$

$$= V_0 \left(1 - e^{-\frac{t}{RC}}\right)$$

Constante de temps:  $\tau = RC$

Temps de montée (10% - 90%) =  $2.2\tau$

| Transformée de Laplace de la fonction | Fonction                                                                                                            |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| 1                                     | $\delta(t)$                                                                                                         |

| $\frac{1}{p}$                         | 1                                                                                                                   |

| $\frac{1}{p^2}$                       | $t$                                                                                                                 |

| $\frac{1}{p^n}$                       | $\frac{t^{n-1}}{(n-1)!} \quad \forall n \geq 1$                                                                     |

| $\frac{1}{\sqrt{p}}$                  | $\frac{1}{\sqrt{\pi t}} \quad \forall t \in R_+$                                                                    |

| $\frac{1}{\sqrt{p^3}}$                | $2\sqrt{\frac{t}{\pi}}$                                                                                             |

| $\frac{1}{p+a}$                       | $e^{-at}$                                                                                                           |

| $\frac{1}{p(p+a)}$                    | $\frac{1-e^{-at}}{a} \quad \forall a \neq 0$                                                                        |

| $\frac{1}{p^2(p+a)}$                  | $\frac{e^{-at}-1+at}{a^2} \quad \forall a \neq 0$                                                                   |

| $\frac{1}{p(p+a)^2}$                  | $\frac{1-e^{-at}(1+at)}{a^2} \quad \forall a \neq 0$                                                                |

| $\frac{1}{(p+a)(p+b)}$                | $\frac{e^{-bt}-e^{-at}}{a-b} \quad \forall a \neq b$                                                                |

| $\frac{p}{(p+a)(p+b)}$                | $\frac{ae^{-at}-be^{-bt}}{a-b} \quad \forall a \neq b$                                                              |

| $\frac{1}{(p+a)(p+b)(p+c)}$           | $\frac{(b-c)e^{-at}+(c-a)e^{-bt}+(a-b)e^{-ct}}{(a-b)(a-c)(b-c)} \quad \forall a \neq b \vee a \neq c \vee b \neq c$ |

| $\frac{1}{(p+a)^2}$                   | $te^{-at}$                                                                                                          |

| $\frac{p}{(p+a)^2}$                   | $e^{-at}(1-at)$                                                                                                     |

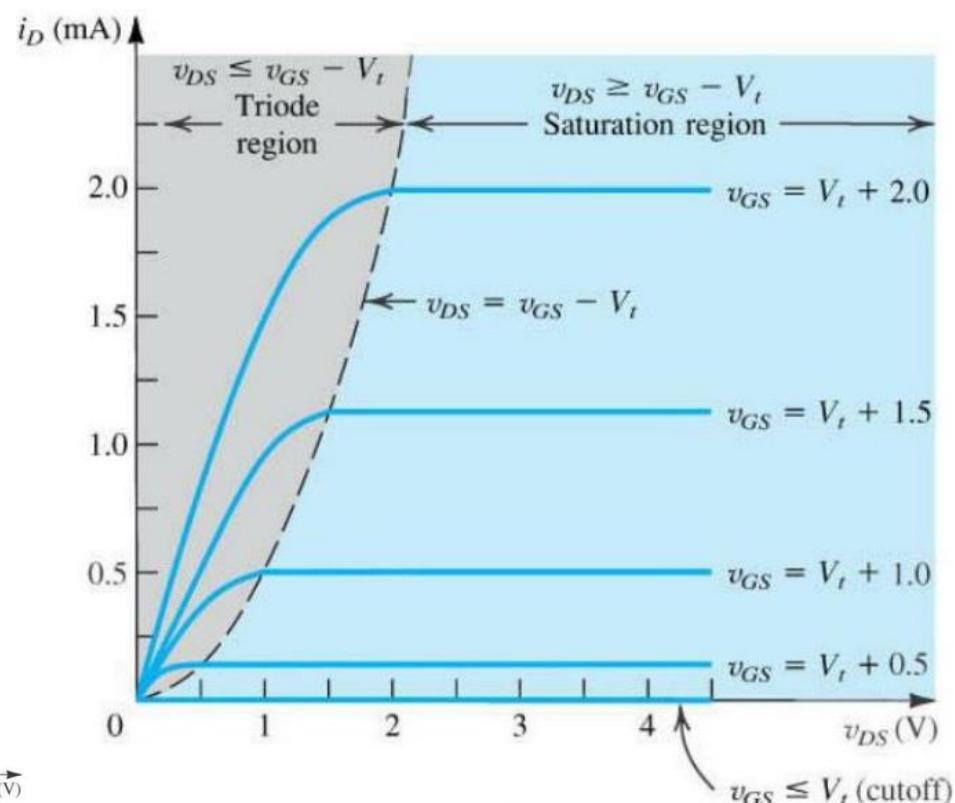

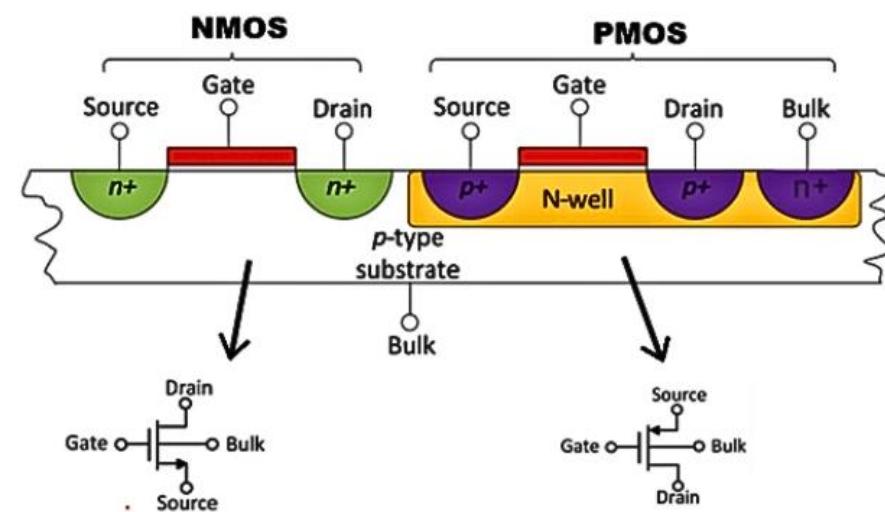

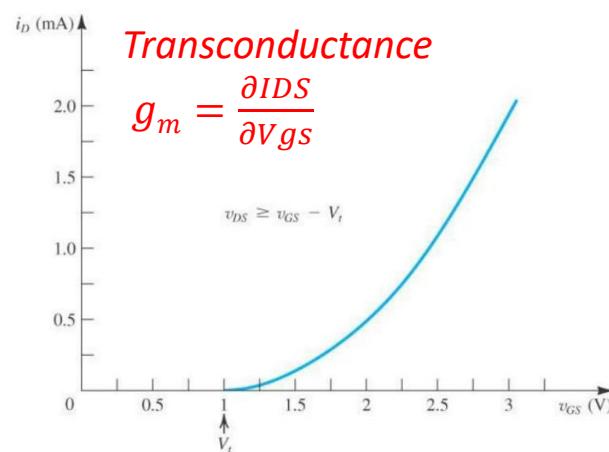

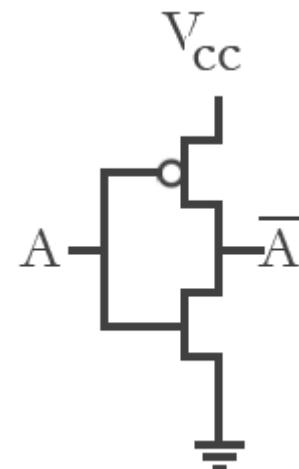

# Fondements de l'électronique: le transistor (4)

- Deux types fondamentaux

- Bipolaire: npn et pnp

- CMOS: nmos et pmos

- 3 (+1) pattes: gate (grille), source, drain (+ substrat)

- Électronique analogique

- Amplification, buffer

- Source commune:  $v \rightarrow i$ , Grille commune:  $i \rightarrow i$ ,

Drain commun:  $v \rightarrow v$

- Électronique numérique

- En tout ou rien: 0, 1

- Portes logiques, cellules mémoires,

FlipFlop (logique synchrone

avec horloge)

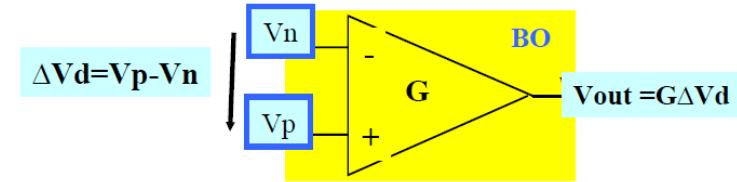

# Fondements de l'électronique: Open Loop vs. Closed Loop Gain (5)

- Gain en boucle ouverte (Open Loop Gain)

- Sans élément de contre réaction:  $gain = G = \frac{V_{out}}{\Delta V_d}$

- gain imprécis, très variable (ampli à ampli, température, alim, etc.)

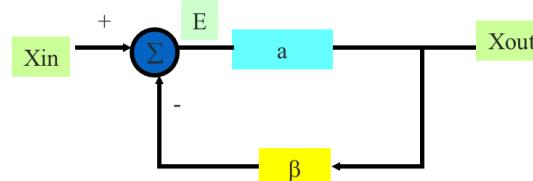

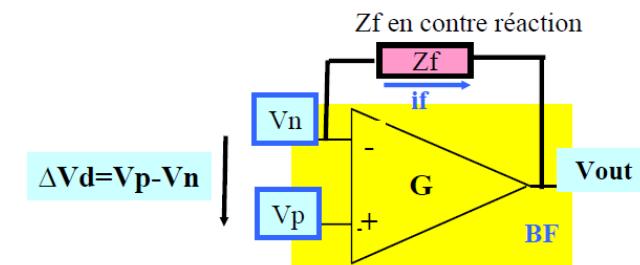

- Gain en boucle fermée (Closed Loop Gain)

- Avec élément de contre réaction:  $Z_f$  entre la sortie et l'entrée négative

- Ampli (idéal ou non):  $\Delta V_d = V_p - V_n$ ,  $V_{out} = G \Delta V_d$ ,

$$V_n - V_{out} = Z_f \text{ if}, \quad i_p = i_n = 0$$

$$E = V_i - \beta V_o, \quad V_o = G E \rightarrow \frac{V_o}{V_i} = \frac{G}{1+G\beta} = \frac{1/\beta}{1+1/G\beta} = \sim 1/\beta$$

- La contre réaction améliore la performance

- Moins sensible au gain en boucle ouverte ( $G$  vs.  $1/\beta$ ), meilleure linéarité

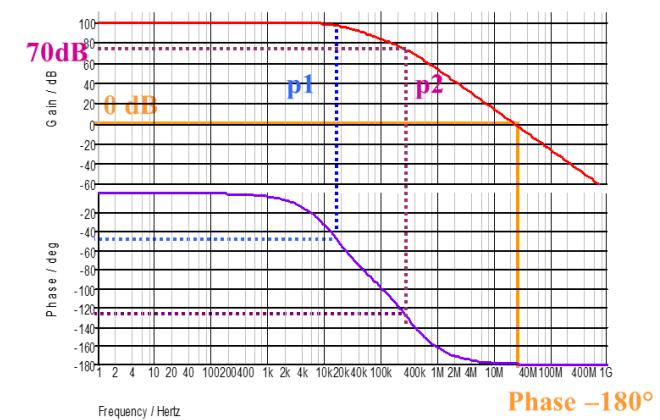

- **Instabilité**  $G\beta = -1 \rightarrow |G\beta| = 1$  et  $Phase = 180^\circ$

- Notion de **marge de phase** ( $\phi_{G\beta}(|G\beta| = 1) - 180 > 45 - 65^\circ$ ), **marge de gain** ( $G\beta(180^\circ) \ll 0$ )

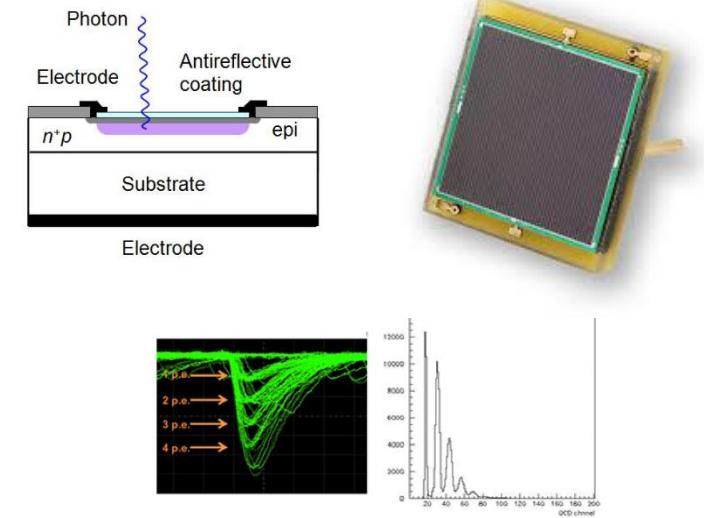

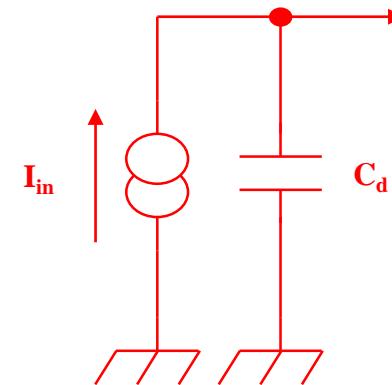

# Une grande variété de détecteurs...

- Mais une modélisation similaire ...

- Détecteur = capacité  $C_d$

- Pixels : 0.1 – 10 pF

- PMs : 3 – 30 pF

- Ionization chambers 10 – 1000 pF

- Directement connecté à l'électronique ou non

- Attention à l'effet de la ligne de transmission?

- Signal : source de courant

- Pixels :  $\sim 100 \text{ e-}/\mu\text{m}$

- PMs : 1 photo-electron  $\rightarrow 10^5 – 10^7 \text{ e-}$

- Modélisation comme un pulse (Dirac) de charge (fC) :  $i(t)=Q_0\delta(t)$

- ou un échelon de tension à travers un capa (importance de  $t_d$ )

- Attention il manque:

- Polarisation (bias) par la Haute Tension

- Connexions, distribution des masses, retour du courant

- Voisins: diaphonie (crosstalk)

- Calibration

- Attention, le signal réel peut être un peu différent, à prendre en compte !

PMT

PIN diode

SiPM

Liquid Argon

RPC

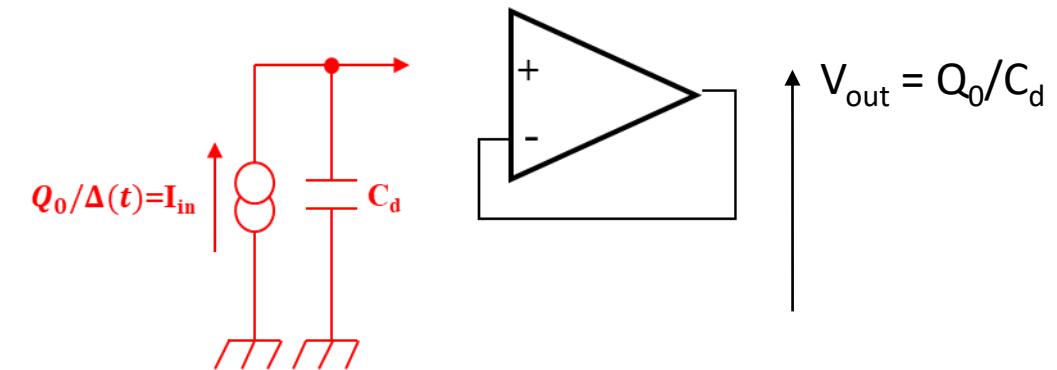

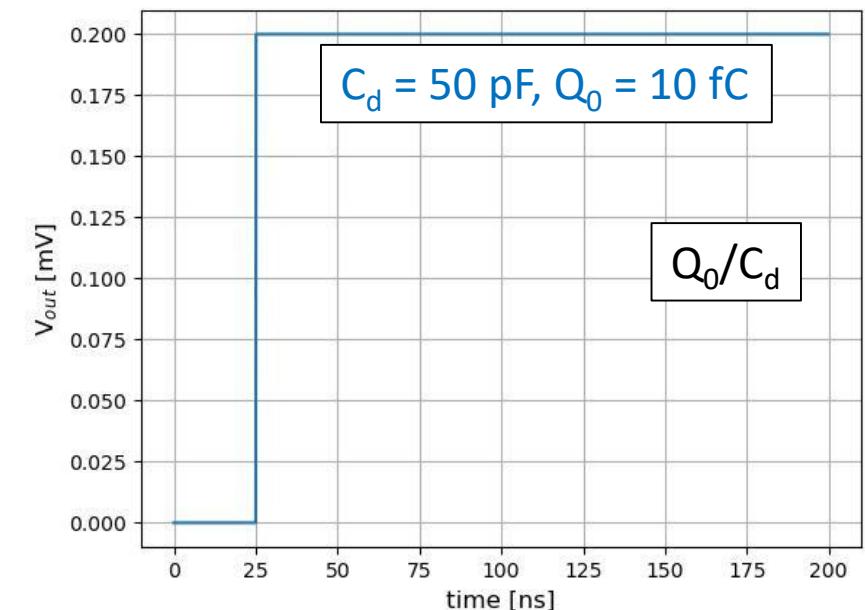

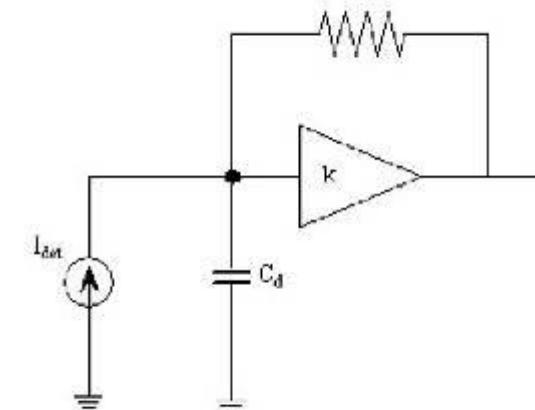

# Lire le signal

- Signal

- Signal = source de courant

- DéTECTeur = capacité  $C_d$

- Quantité à mesurer

- Charge → intégrateur

- Temps → discriminateur + TDC

- Intégration sur  $C_d$

- Simple :  $V = Q/C_d$

- « Gain » :  $1/C_d$  : 1 pF → 1 mV/fC

- Besoin d'un suiveur pour bufferiser la tension

- La capacité d'entrée devient  $C_d // C_{pa}$

- Perte de gain, possible non-linéarités entre voies

- Crosstalk

- Besoin de vider  $C_d$

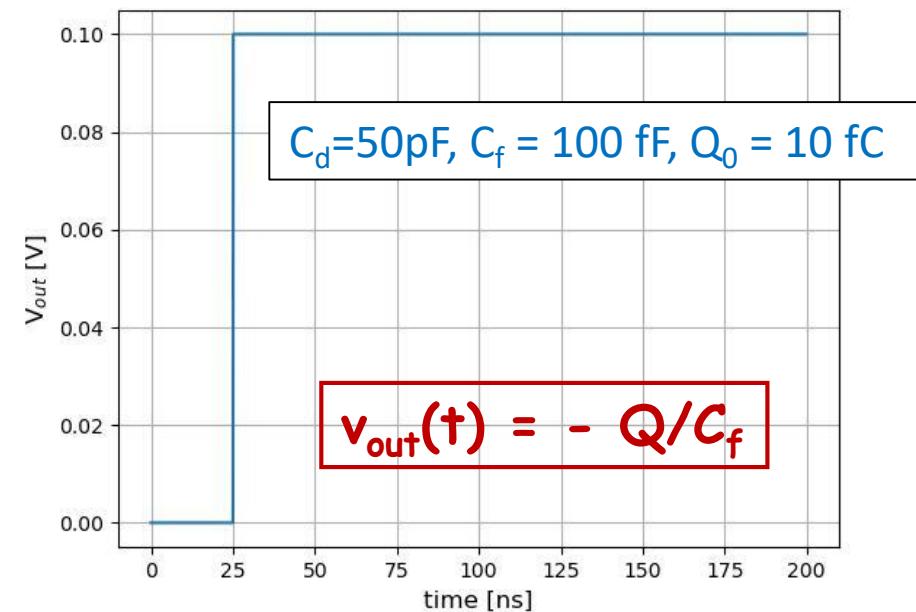

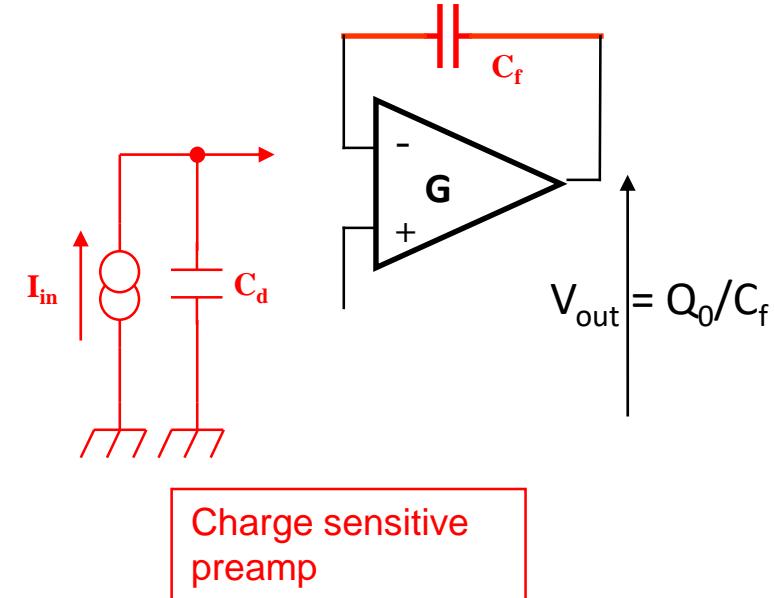

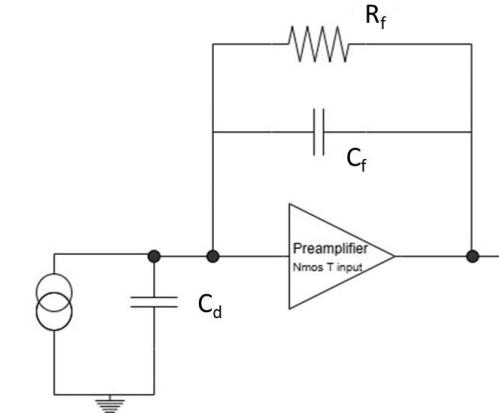

# Préamplificateur de charge idéal

- Préamp idéal en transimpédance ( $i \rightarrow V$ )

- Shunt-shunt feedback: low  $Z_{in}$ , low  $Z_{out}$

$$i_{in}(\omega) = j\omega.C_d.V_{in}(\omega) + j\omega.C_f(V_{in}(\omega) - V_{out}(\omega)) \quad \text{et} \quad V_{out}(\omega) = -G.V_{in}(\omega)$$

$$\frac{V_{out}(\omega)}{i_{in}(\omega)} = -\frac{1}{j\omega.C_f} \cdot \frac{1}{\left(1 + \frac{C_d}{G.C_f}\right)} \quad \text{avec } C_d \gg C_f$$

- Préamp idéal:  $G \rightarrow \infty$  et  $f_c \rightarrow \infty$

$$\frac{V_{out}(\omega)}{i_{in}(\omega)} = -\frac{1}{j\omega.C_f}$$

- Intégration :

$$V_{out}(t) = -\frac{1}{C_f} \int_0^{\infty} i_{in}(t) dt = -\frac{Q_O}{C_f}$$

- « Gain » :  $1/C_f$  : 0.1 pF  $\rightarrow$  10 mV/fC

- $C_f$  déterminé par le signal maximal

## • Intégration sur $C_f$

- Simple:  $V = -Q/C_f$

- Le gain ne dépend pas de la capa  $C_d$ , ni de la capa du preamp  $C_{pa}$

- Transforme un signal court en un signal long

- C'est la base de 90% des front-end

- Mais toujours construit à partir de circuits custom

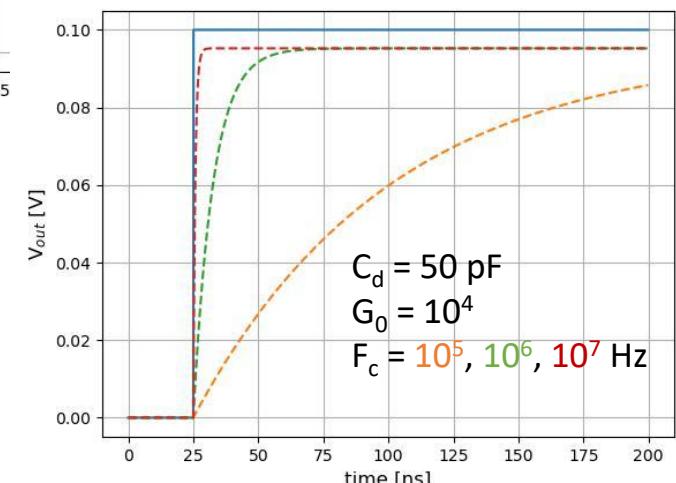

# Préamplificateur de charge non-idéal

- Gain non-infini:  $G_0$

- $V_{out}(\omega)/i_{in}(\omega) = -Z_f / (1 + C_d / G_0 C_f)$

$$\frac{V_{out}(\omega)}{i_{in}(\omega)} = -\frac{1}{j\omega \cdot C_f \cdot \tau} \cdot \frac{1}{\left(\frac{1+\omega_0 \cdot \tau}{\tau} + j\omega\right)} \quad \text{avec } \tau = \frac{C_d}{G_0 \omega_0 C_f}$$

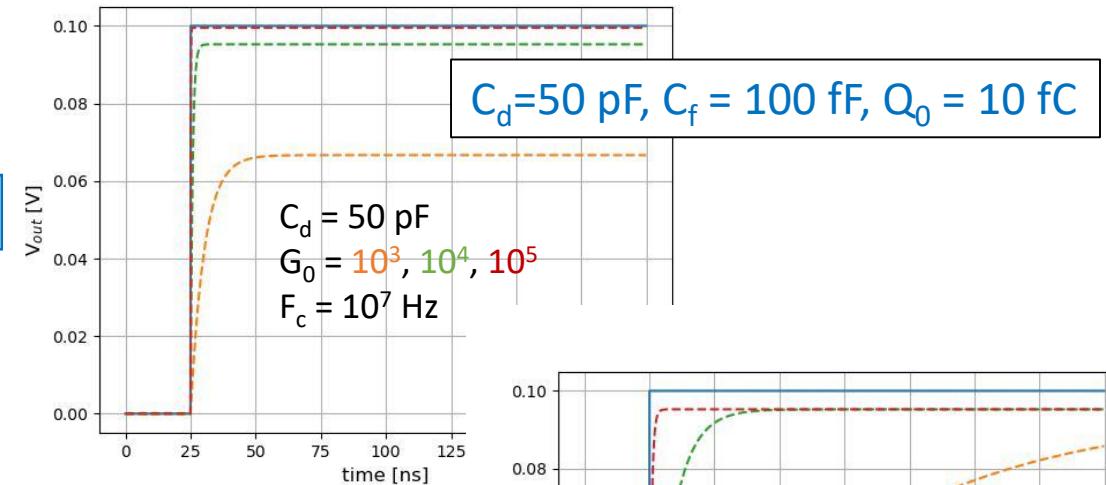

$$V_{out}(t) = -\frac{Q_0}{C_f} \cdot \frac{1}{\left(1 + \frac{C_d}{G_0 C_f}\right)} \left(1 - e^{-t/\tau}\right) \quad \text{avec } \tau = \frac{C_d}{G_0 \omega_0 C_f}$$

- Déficit balistique: petit signal perdu dans  $C_d / G_0 C_f \ll 1$

- Pour minimiser le déficit balistique:

$$C_d / G_0 C_f < 100 \rightarrow G_0 > 100 C_d / C_f$$

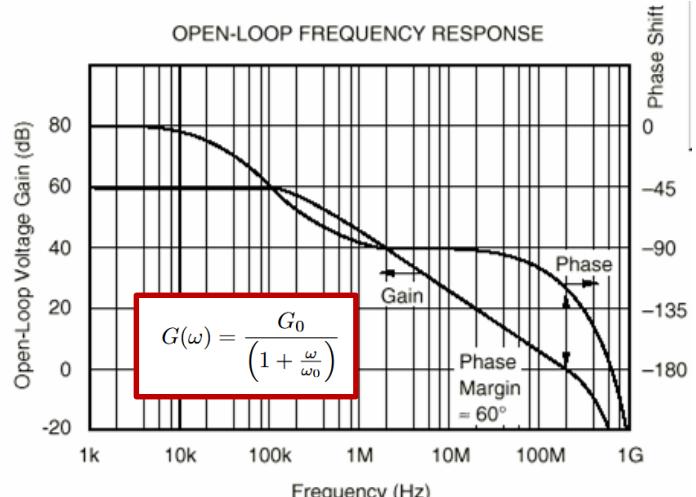

- Bande-passante non infinie:  $\omega_0$

- $G(\omega) = G_0 / (1 + j \omega / \omega_0)$

- $G_0$ : gain de basse fréquence

- $G_0 \omega_0$ : produit gain-bande (GBP)

- Pour minimiser l'influence :  $\tau < \frac{1}{10 \omega_0} \rightarrow GBP > 10 \omega_0 \frac{C_d}{C_f}$

- Temps de montée du préamp

- A cause de la variation du gain avec la fréquence

- Temps de montée :  $t_{10-90\%} = 2.2 \tau$

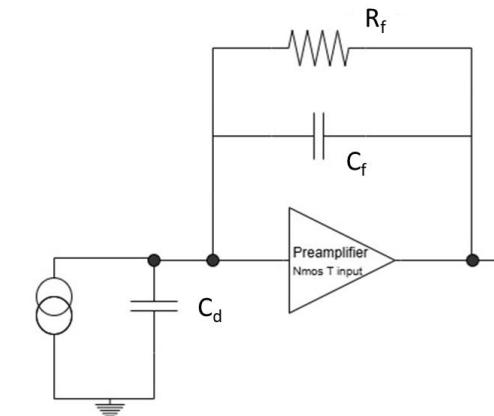

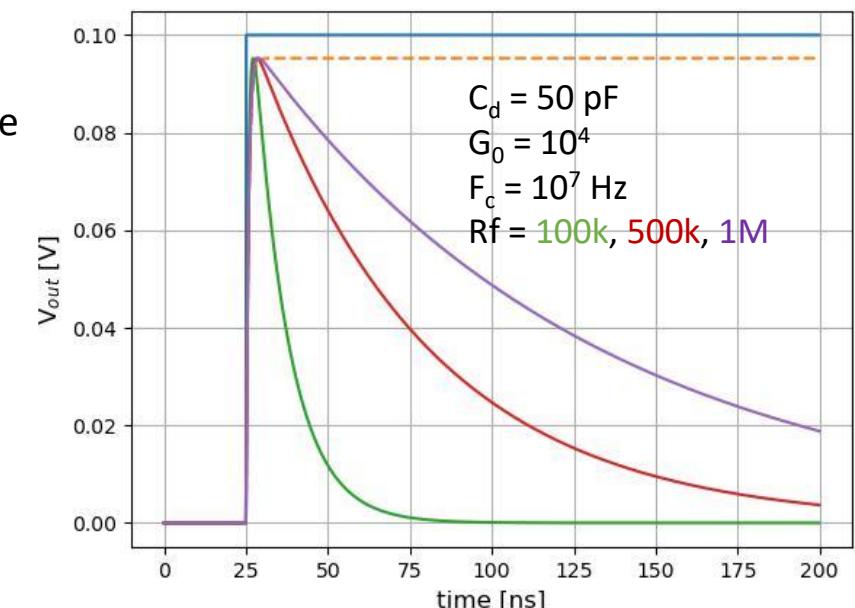

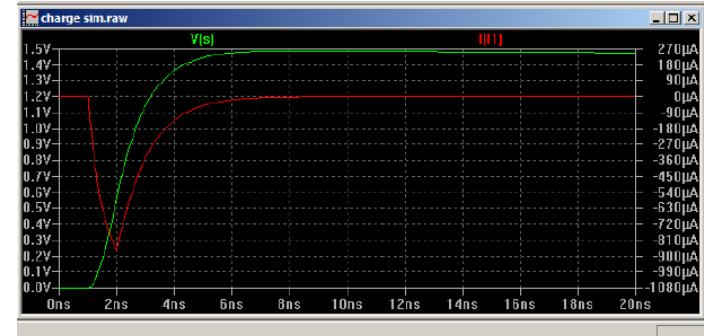

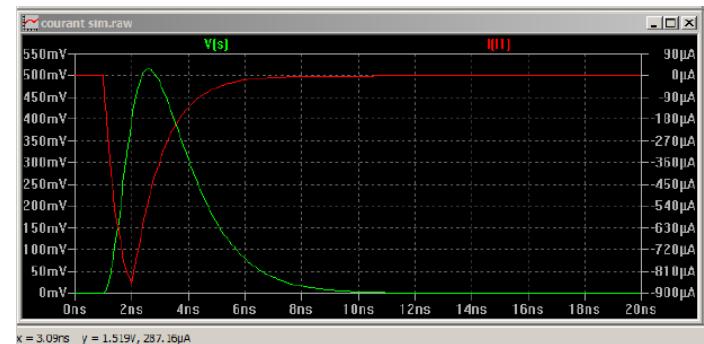

# Comment vider $C_f$ ? Besoin d'un « reset »

- Nécessité de vider  $C_f$  (remise à 0)

- Assure la polarisation statique

- Évite la saturation

- Résistance de contre réaction  $R_f$

- Vide  $C_f$  avec la constante  $R_f C_f$

- Calcul de la réponse impulsionnelle plus difficile

$$\frac{V_{out}(s)}{i_{in}(s)} = -\frac{Z_f}{\left(1 + \frac{Z_d + Z_f}{G_0 Z_d} + \frac{Z_d + Z_f}{G_0 \omega_0 Z_d} s\right)} = -\frac{R_f}{1 + s\tau_f} \frac{1}{1 + \frac{1+s\tau_d}{(1+s\tau_f)G_0} + \frac{1+s\tau_d}{(1+s\tau_f)G_0\omega_0}}$$

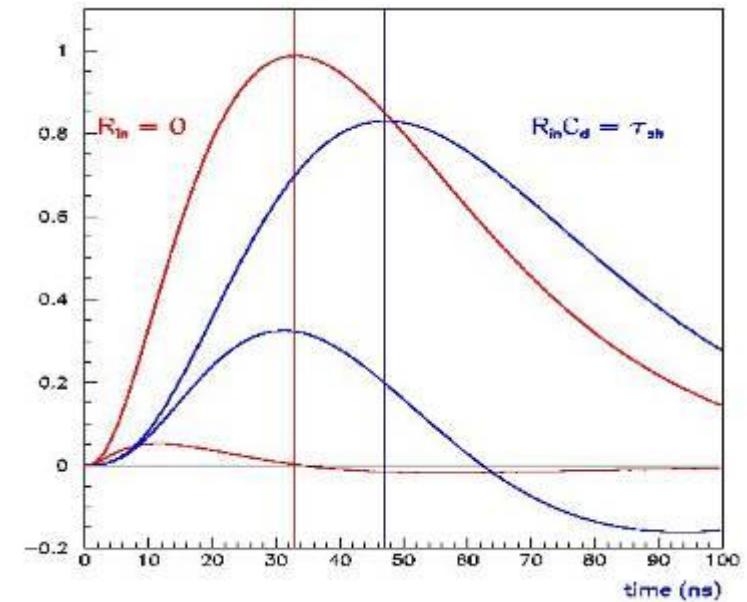

- En temporelle sous la forme suivante, avec  $\tau_0 = \frac{C_d}{G_0 \omega_0 C_f}$  temps de montée et  $\tau_1 = R_f C_f$  temps de redescente

$$V_{out}(t) = A \left( e^{-\frac{t}{\tau_0}} - e^{-\frac{t}{\tau_1}} \right)$$

- $R_f$  choisi tel que  $R_f C_f \gg$  shaping

- $R_f = M\Omega$ - $G\Omega$  pour minimiser le bruit parallèle (difficile à intégrer)

- En ASICs: multiplicateurs de résistance par miroirs

$C_d = 50 \text{ pF}$ ,  $C_f = 100 \text{ fF}$ ,  $Q_0 = 10 \text{ fC}$

# Autres techniques de reset

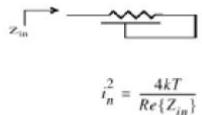

$$i_n^2 = \frac{4kT}{Re\{Z_{in}\}}$$

## Physical resistor

- always accompanied by parasitic capacitance

- de-stabilizes circuit and increases noise

- noise higher than  $4kT/R$  by factor  $\sim RC/t_m$

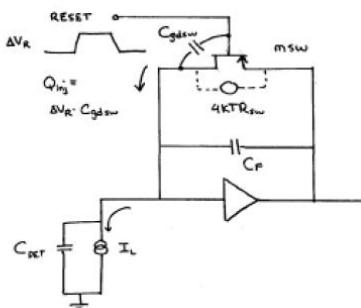

## Pulsed reset by MOS switch

- sampled noise  $\sqrt{kTC_F}$

- $Q_{inj}$  noise from switch control voltage

- leakage current integrates on output node  $dV_{out}/dt = I_L/C_F$

O'Connor et al., TNS v44 n3 (1997)

De Geronimo et al., NIM A421 (1999)

De Geronimo et al., TNS v47 n4 (2000)

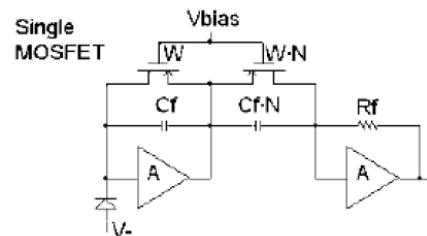

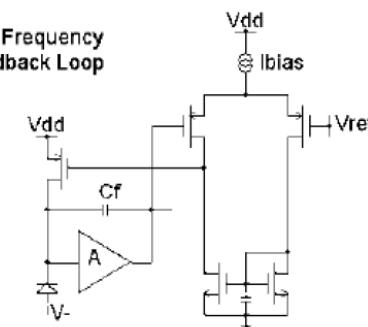

- provides **effective current gain**  $-N$

- full compensation (high linearity)

- minimum noise (thermal)

- requires baseline stabilization

- can be realized in multiple stages

Krummenacher, NIM A350 (1991)

Ludewigt et al., TNS v41 n4, (1994)

Vandenbussche et al., TNS v45, n4 (1998)

Manfredi et al., Nucl.Phys.B 61B, Proc.Suppl. (1998)

- noise can be high

- requires baseline stabilization at high rates

- compensation an issue

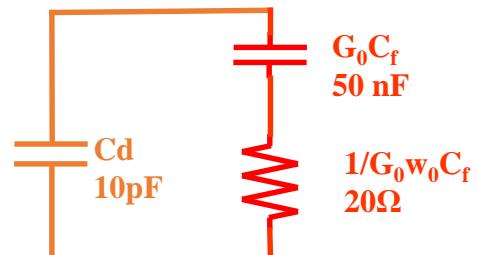

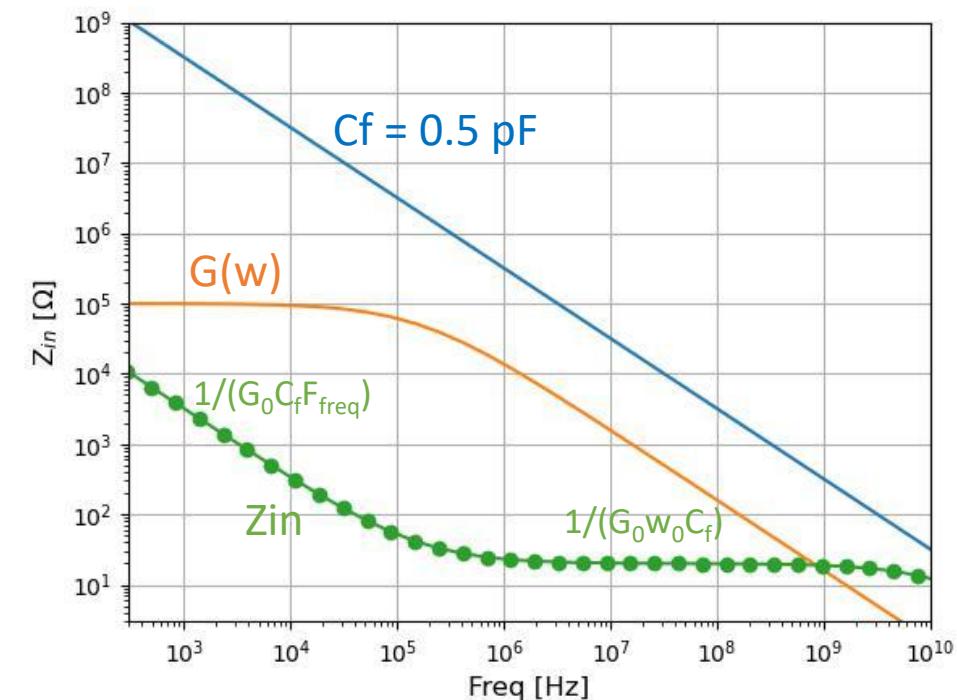

# Préamplificateur de charge vue de l'entrée

- Impédance d'entrée d'un ampli idéal

- $Z_{in} = Z_f / (G+1)$

- $Z_{in} \rightarrow 0$  pour un ampli idéal

- $V_{in} = 0$ : « Masse virtuelle »

- Minimise la sensibilité à l'impédance du détecteur:

$I_d = V_{in}/Z_d = 0$

- Minimise le crosstalk

- Impédance d'entrée d'un ampli réel

- $Z_{in} = 1/j\omega G_0 C_f + 1/ G_0 \omega_0 C_f$

- Un terme résistif :  $R_{in} = 1/ G_0 \omega_0 C_f$

- Exemple :  $G_0 = 10^5$ ,  $\omega_0 = 10^6$  rad/s,  $C_f = 0.5$  pF  $\Rightarrow R_{in} = 20 \Omega$

- Détermine la constante de temps d'entrée :  $t = R_{eq} C_d$

- Circuit équivalent :

$$G(\omega) = \frac{G_0}{\left(1 + \frac{\omega}{\omega_0}\right)}$$

Input impedance of charge preamp

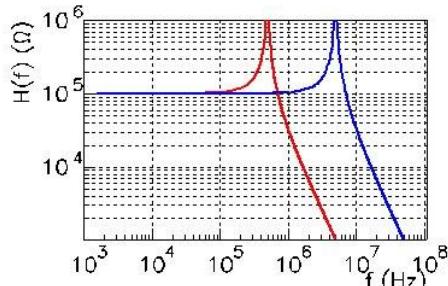

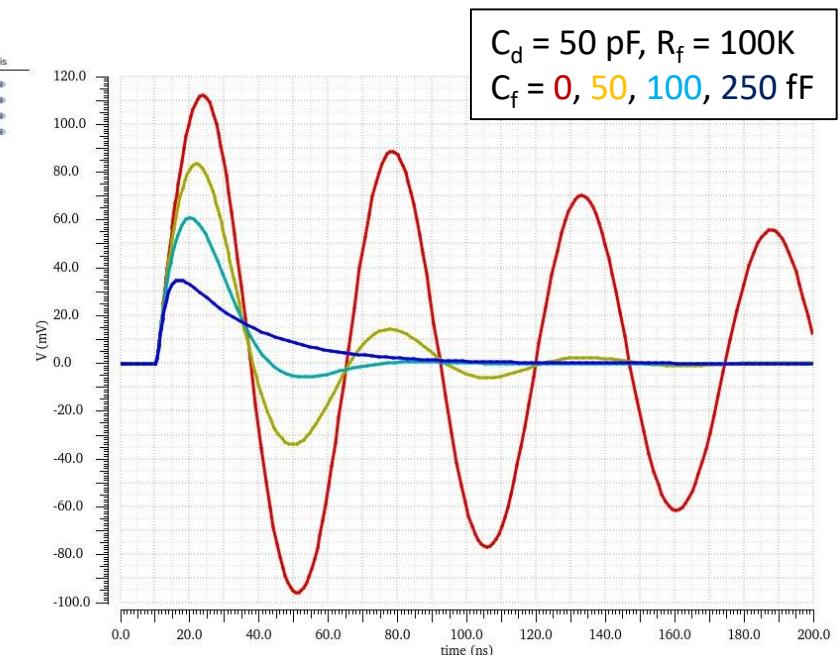

# Préamplificateur de courant

- Configuration en transimpédance

- $V_{out}(w)/i_{in}(w) = -R_f / (1+Z_f/GZ_d)$

- Gain =  $V_{out}/i_{in} = R_f$

- High counting rate: durée du signal = durée de  $i_{in}$

- Typically optical link receivers

- Facilement oscillatoire

- Impédance d'entrée:  $Z_{in} = \frac{R_f}{G_0} + j\omega \frac{R_f}{G_0 \omega_0}$

- Impédance d'entrée inductive :  $L_{eq} = \frac{R_f}{G_0 \omega_0}$

- Instable à cause de la capa détecteur

- Résonnant à :  $f_{res} = 1/2\pi\sqrt{L_{eq}C_d}$

- Amortissement (Damping) avec  $C_f$

- $H(\omega) = \frac{R_f}{1+j\omega R_f C_d + \frac{\omega^2 R_f C_d}{G_0 \omega_0}}$

Current sensitive preamp

# Préamplificateur de charge ou de courant? Ou autres?

- Préamplificateurs de charge

- Gain =  $1/C_f$

- Meilleur performance de bruit

- Meilleur avec des signaux courts ( $\sim Q$ )

- Meilleur avec petite capacité

- Préamplificateurs de courant

- Gain =  $R_f$

- Meilleur avec des longs signaux ( $\sim I$ )

- Meilleur pour haut taux de comptage

- Plus sensible au bruit parallèle (bruit du courant de fuite)

- Il existe encore d'autres architectures de front-end:

- Ampli de tension:  $G = C_1/C_2$

- Open loop

- Convoyeur de courant: base commune, super base commune

- RF amplifiers

H. Lebbolo

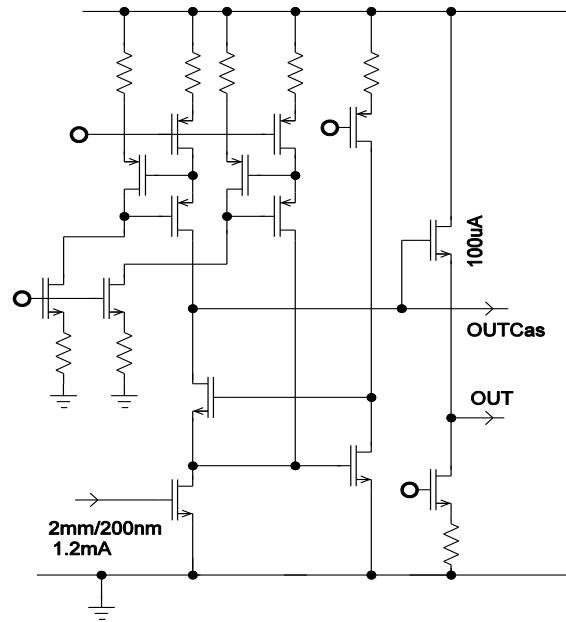

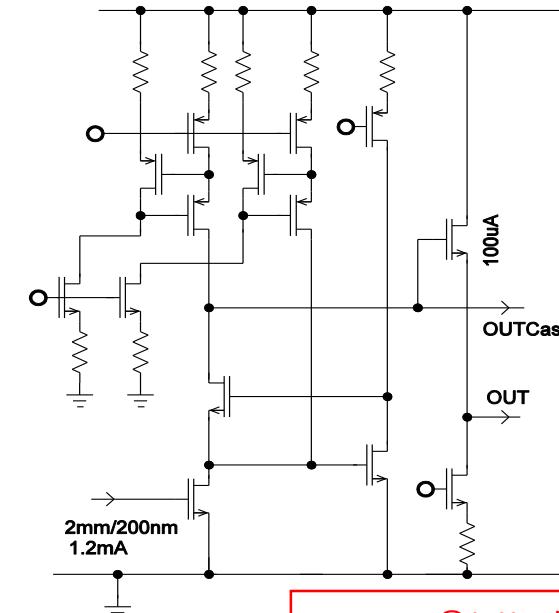

# Exemple : designer un préampli de charge (1)

- Un design performant est au niveau transistor

- 3 briques de bases

- Source commune:  $I_{out} = g_m V_{in}$  (gain principal)

- Grille commune:  $I_{out} = \sim I_{in}$  (cascode)

- Drain commun:  $V_{out} = \sim V_{in}$  (buffer de tension)

- Optimiser tailles et courants

- Ne pas oublier les éléments de polarisation (bias)

- Modèle petit-signaux équivalent

- Permet de calculer gain et bande passante:  $G_0$  et  $\omega_0$

- $V_{out}/V_{in} = -gm_1 R_0 / (1+j\omega R_0 C_0)$

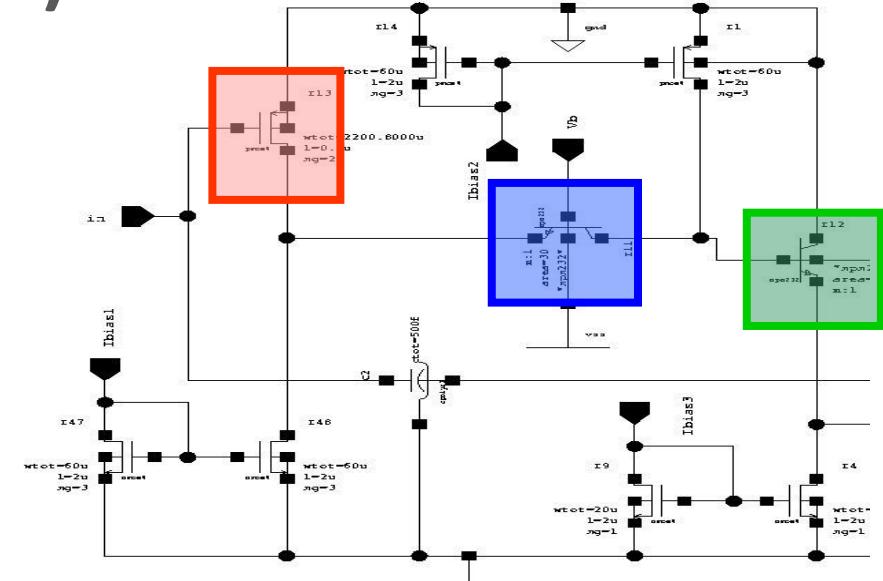

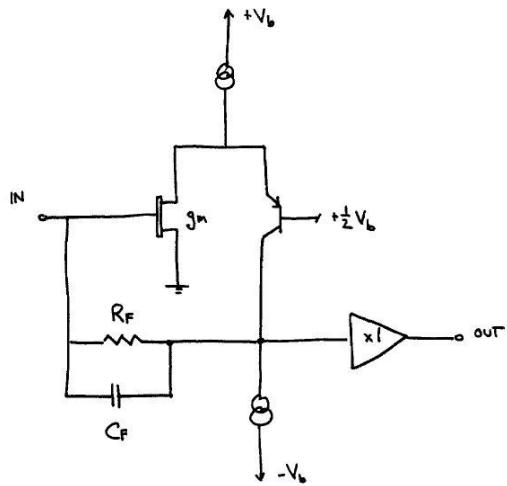

Schematic of charge preamp

Small signal equivalent model of charge preamp

# Exemple : designer un préampli de charge (2)

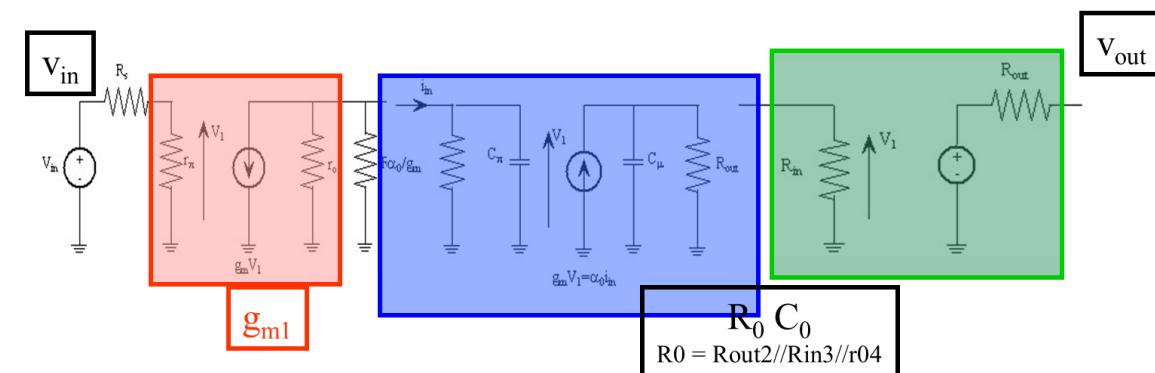

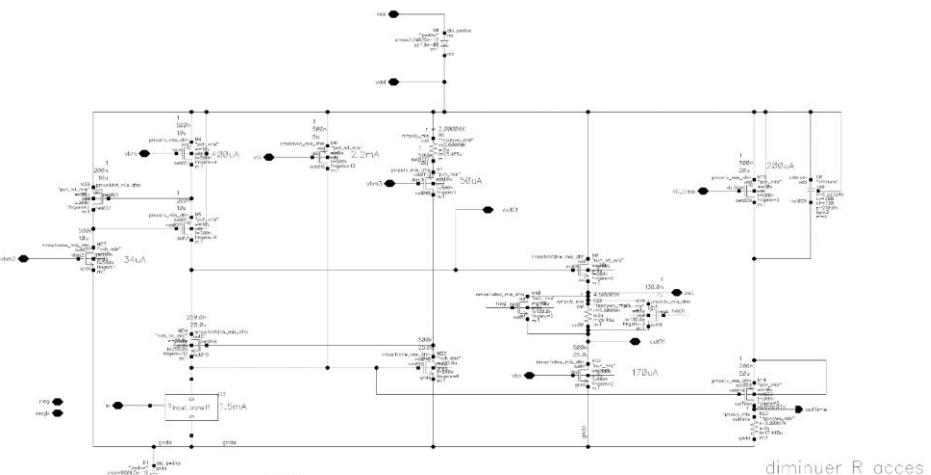

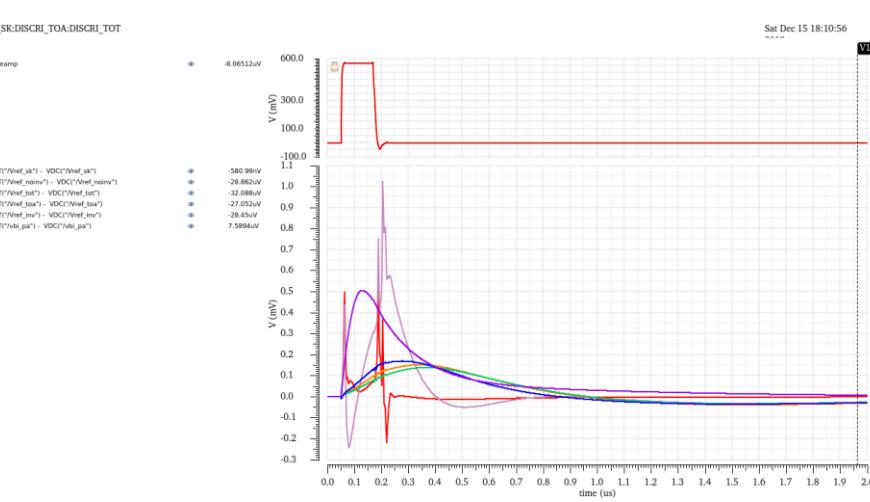

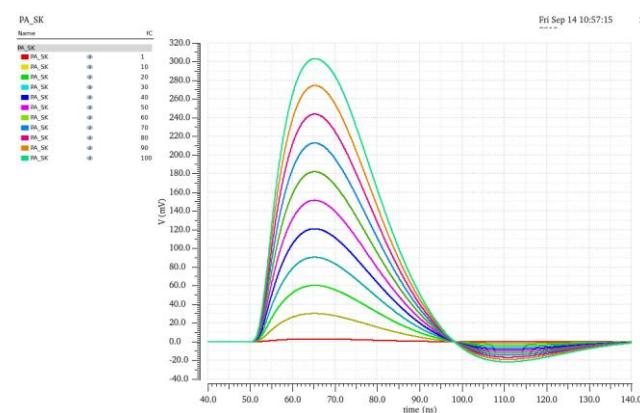

- Simulation complète

- Vérifier les calculs et les effets de deuxième ordre: gain, linéarité, saturation, bruit

- Tester la performances avec toutes les variations de Process, Tension, Température (PVT)

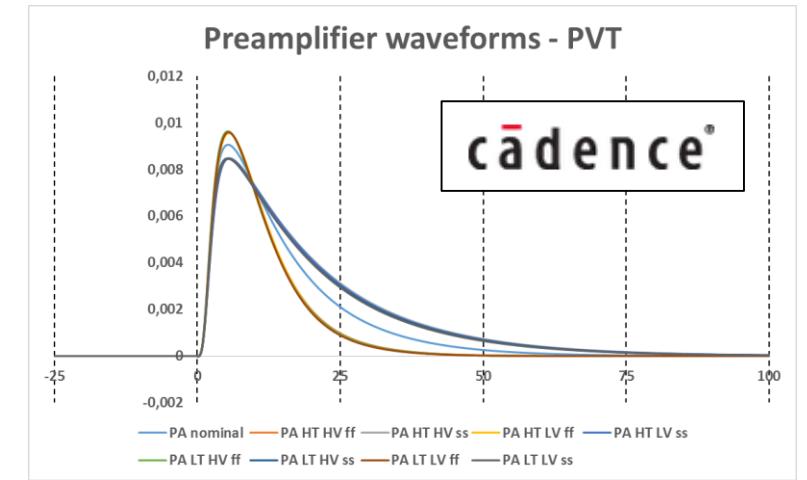

- Tester la performance contre les variations de taille: Monte-Carlo

- Tester couplage quand multi-voies

| Process | T (°C) | V Supply | ENC  | PeakTime | BX+1/BX | Power | VDC(out_inv) | VDC(out_noinv) |

|---------|--------|----------|------|----------|---------|-------|--------------|----------------|

| nominal | -20    | 1,2      | 1776 | 23,8     | 3,7     | 5,6   | 1060         | 97             |

| ff      | 27     | 1,35     | 1903 | 19       | -13     | 9,6   | 835,7        | 104            |

| ss      | 27     | 1,35     | 1947 | 23,8     | 9,4     | 6,2   | 783          | 94             |

| ff      | 27     | 1,08     | 2135 | 22       | -12     | 5,5   | 821          | 83             |

| ss      | 27     | 1,08     | 2150 | 29,9     | 15      | 3,3   | 766          | 76             |

| ff      | -30    | 1,32     | 1594 | 16,2     | -3,7    | 9,4   | 877          | 104            |

| ss      | -30    | 1,32     | 1715 | 24       | 11,8    | 6     | 805          | 114            |

| ff      | -30    | 1,08     | 1860 | 22,3     | -9      | 5,3   | 860          | 88             |

| ss      | -30    | 1,08     | 1920 | 25       | 19      | 3,1   | 788          | 98             |

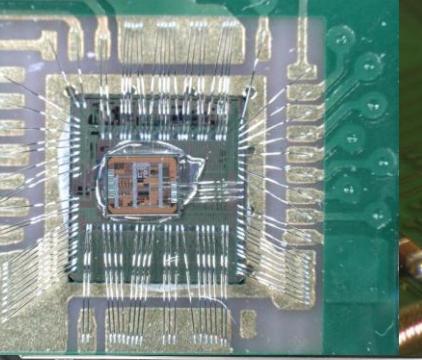

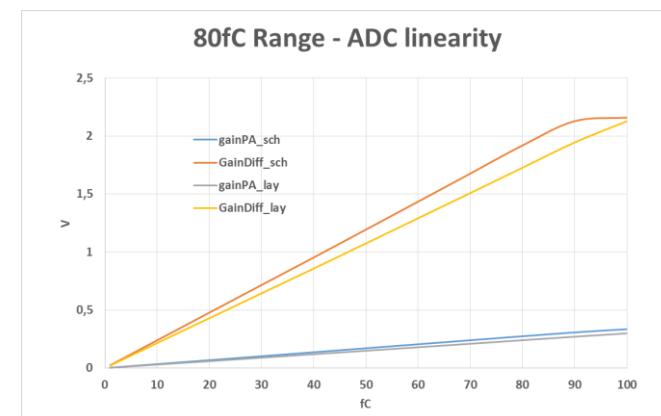

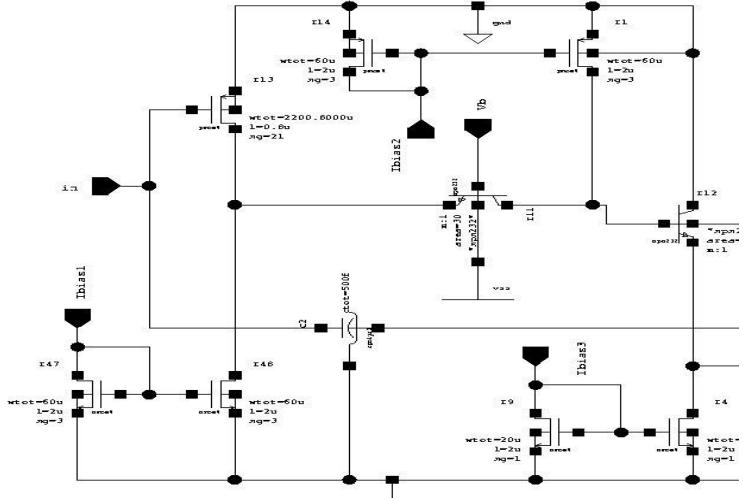

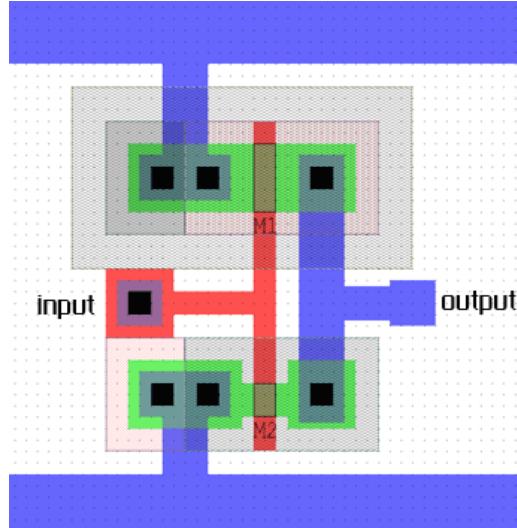

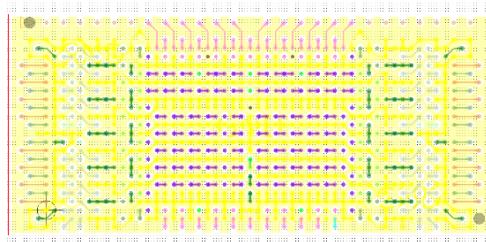

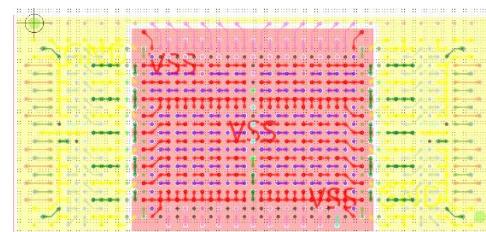

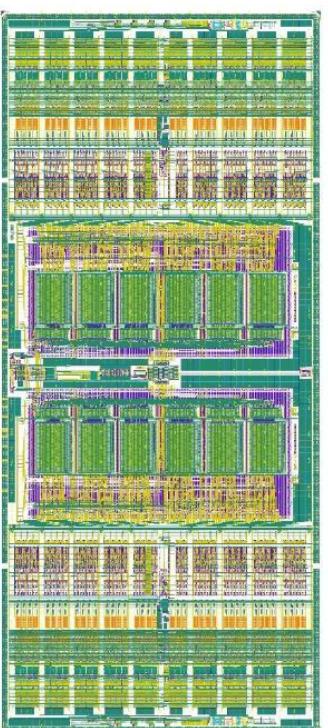

# Exemple : concevoir un préampli de charge (3)

- Layout

- Chaque composant est dessiné

- Ils sont interconnectés par des niveaux de métal

- Vérification

- DRC : vérification des règles de dessin (isolation, dimensions minimales...)

- ERC : extraction du schéma électrique correspondant (Nwell, substrat)

- LVS (layout vs schematic) : comparer schéma extrait vs. Initial schéma

- Simulation de la vue extraite avec les parasites (R, C, L)

- Génération du fichier GDS2

- Fabrication des masques: « réticule »

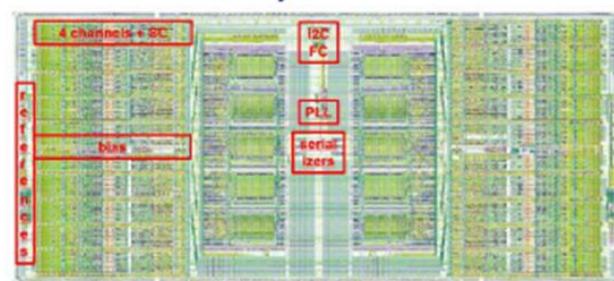

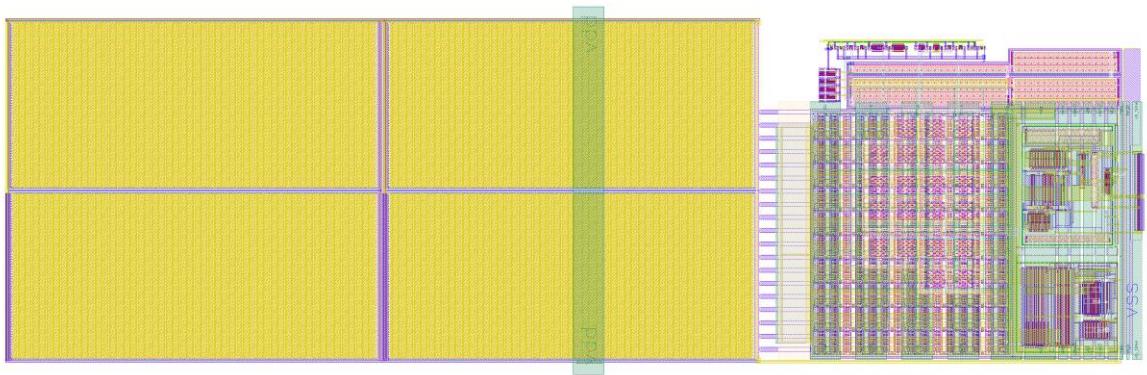

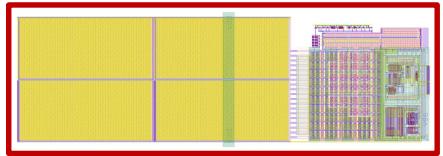

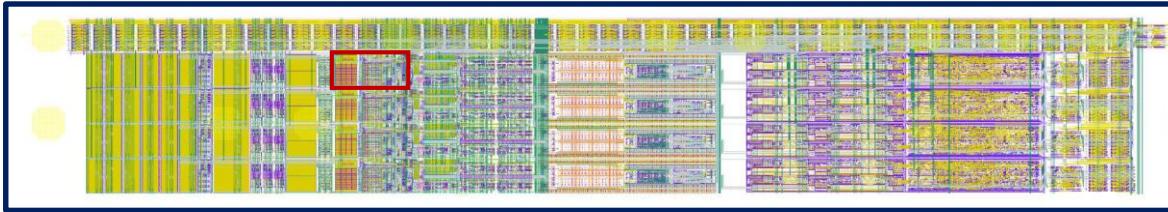

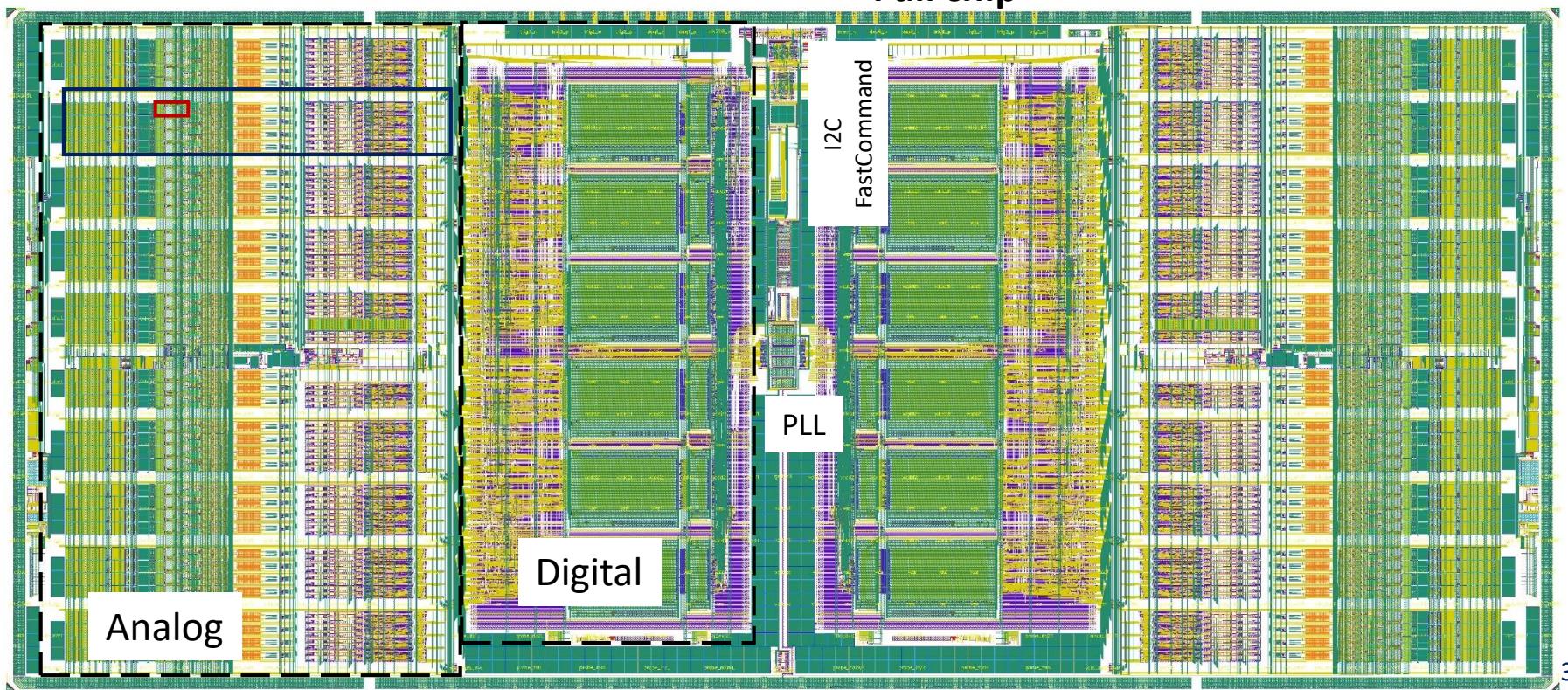

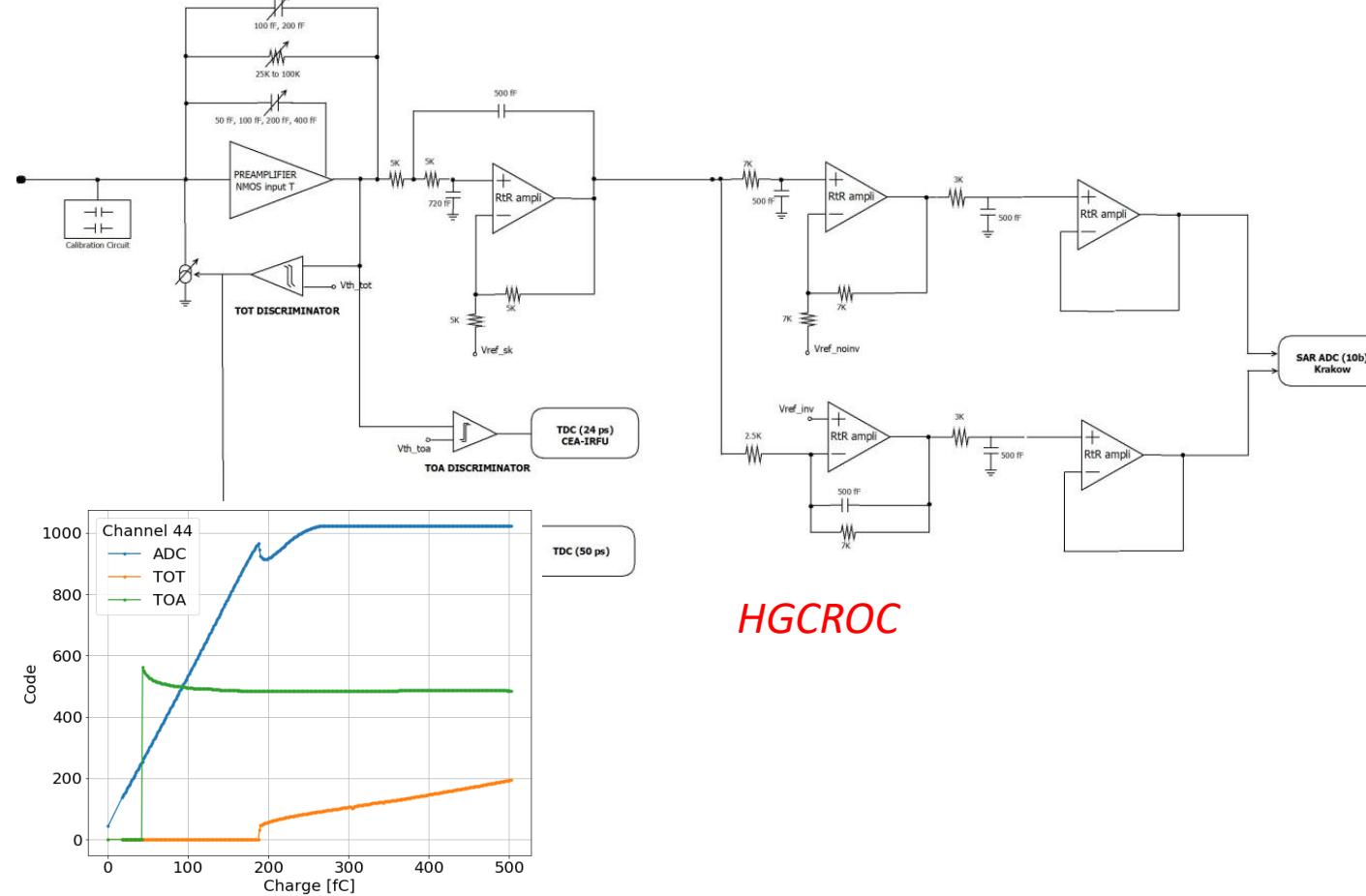

# From preamp to chip : HGCROC

Préamplifier

Four full analog channel

Full chip

# Exemple de préamplificateurs

Charge preamp ©Radeka 68

RD53 preamp ©INFN

preamp ©J. Kaplon

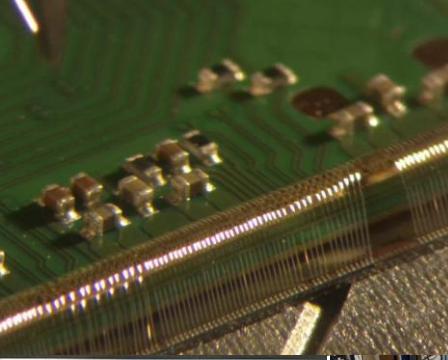

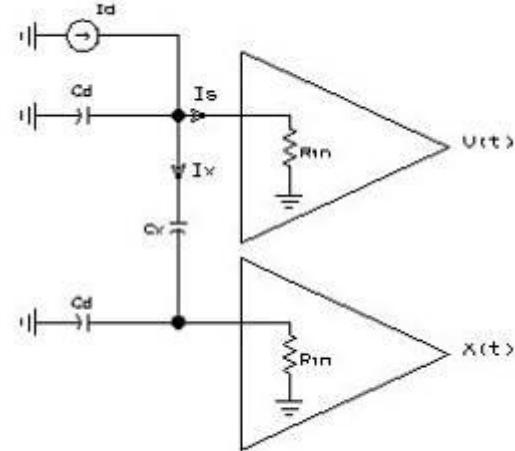

# Crosstalk

- Couplage capacitif entre voisins

- Le signal de crosstalk est dérivé avec la même polarité

- **Petite contribution au pic du signal**

- Small contribution at signal peak

- Proportionnel à  $C_x/C_d$  et l'impédance d'entrée du préamp

- Crosstalk longue distance

- À cause des inductances communes et masses communes

- À cause des impédances communes: bias, tensions de référence

- À cause des connecteurs

- Visible aussi sur le bruit corrélé

# Crosstalk

Internal injection with calibration DAC

1-2 % crosstalk

⇒ Parasitic testpulse injection

External injection from the preamp input

< 0.2 % crosstalk

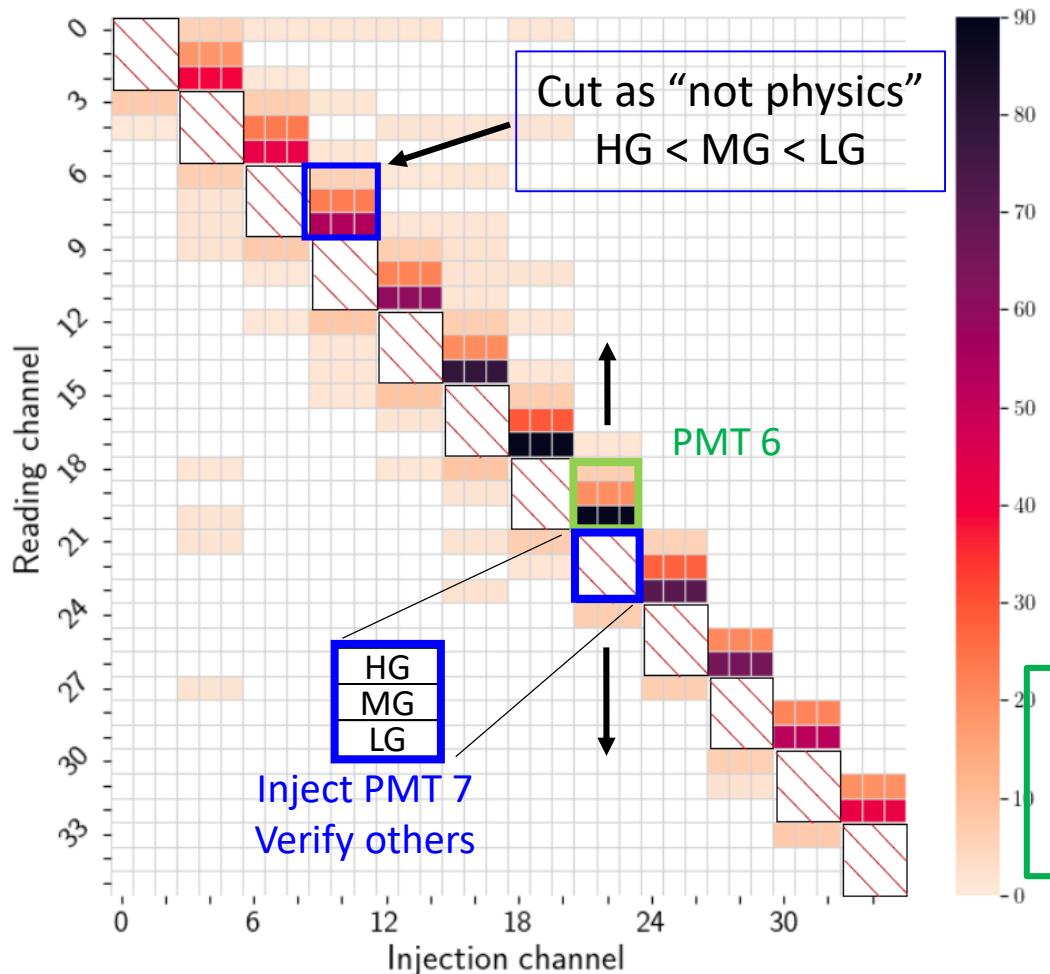

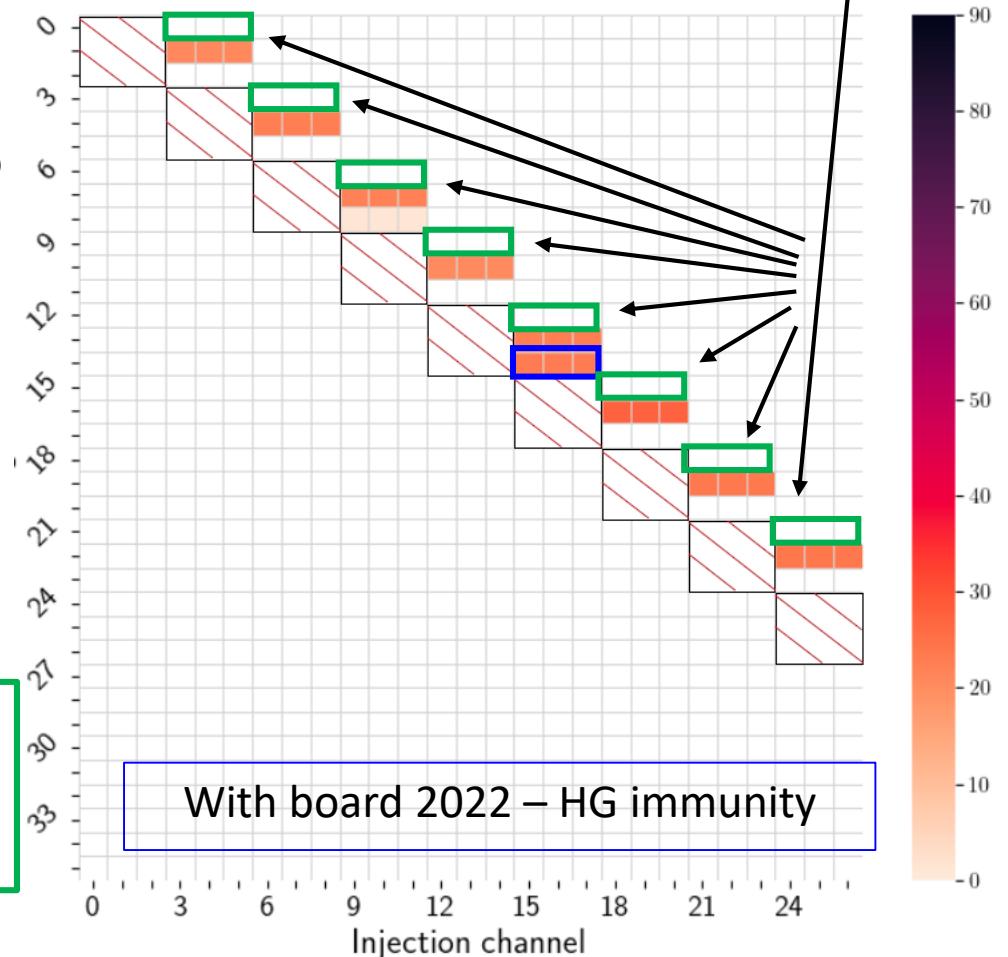

# Crosstalk: HKROC, acquisition board improvements

- Coupling map by injecting large charge (> 900 pe)

- Importance of electronics board stackup

- Huge work on the PCB with focus on suppressing HG coupling

Board v1 (Mezzanine) [ADC units]

Acq. board 2022:

3 PMT gains split into

2 layers

HG and LG immunity

to coupling

Acq. board 2023:

3 PMT gains split

into 3 layers

Board v2 (BGA) [ADC units]

Coupling fully cut thanks to HG

“immunity” to crosstalk (veto)

# Aperçu d'un ROC (Read-Out Chip)

- Le plus souvent, une architecture similaire

- Très petits signaux (fC) → besoin d'**amplification** → préamplificateur

- Mesure de l'**amplitude** et/ou du **temps** → ADC, discri, TDC

- Plusieurs milliers à millions de voies → forte intégration, basse conso

- Environnement → **radiation, température**

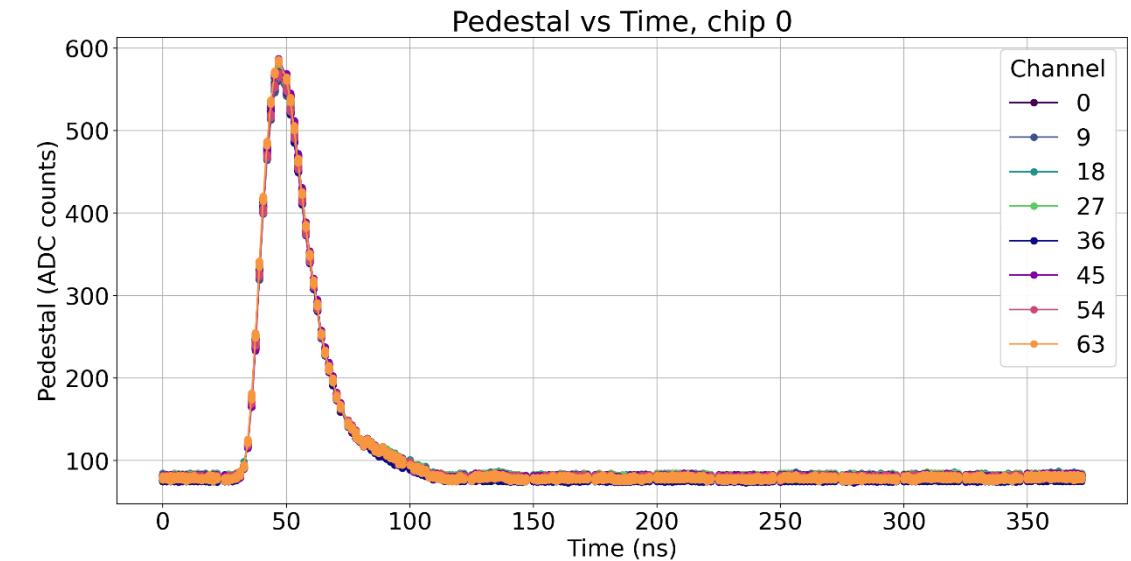

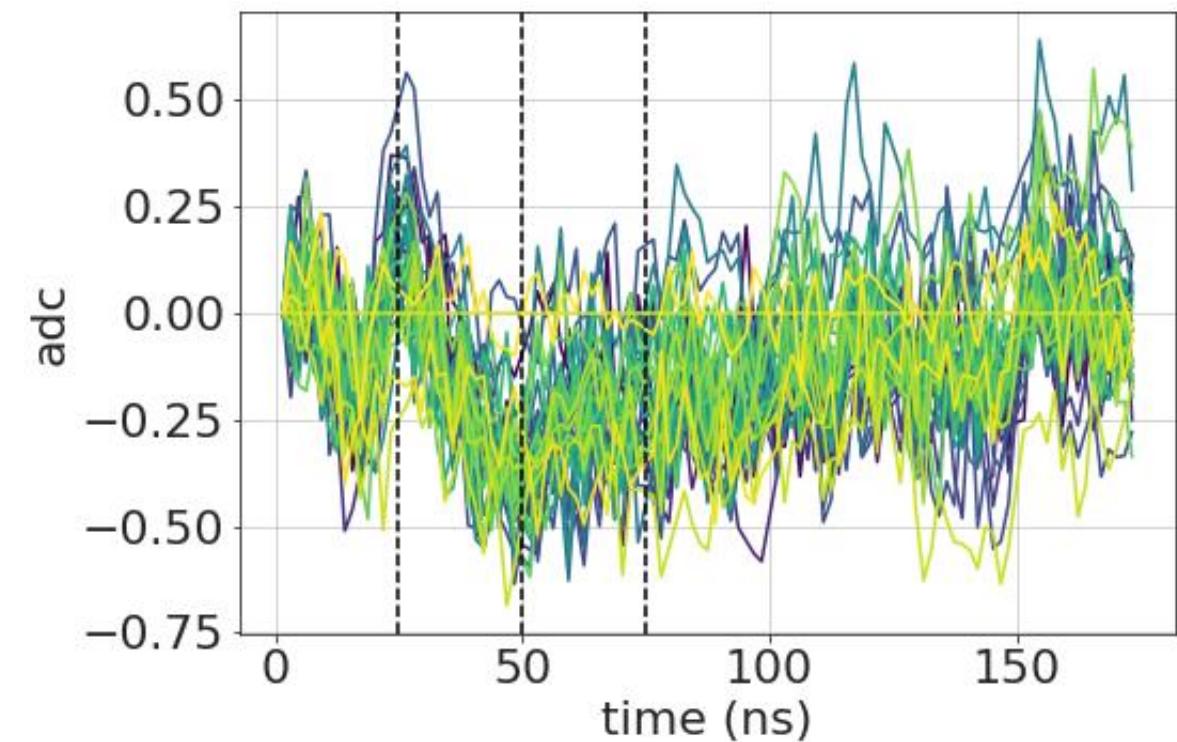

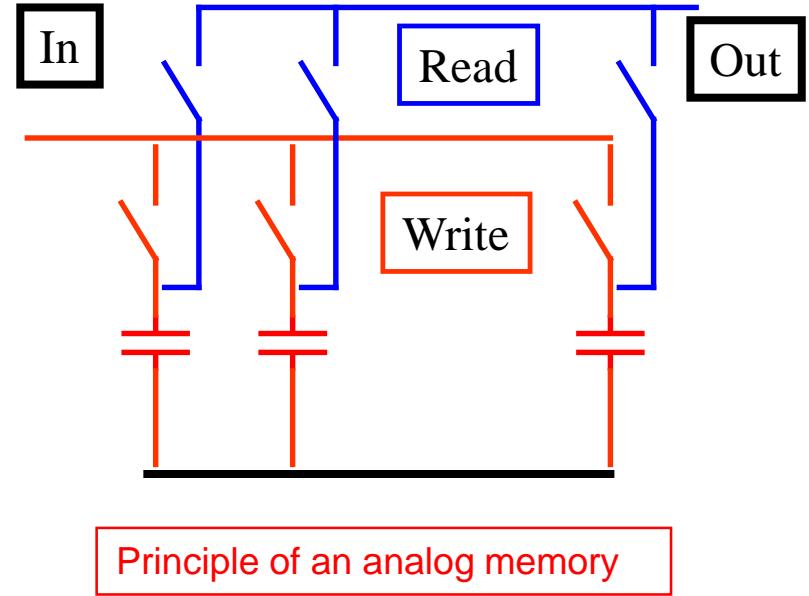

# Analog memories

- **Switched Capacitor Arrays (SCAs)**

- Stocke le signal dans des capacités ( $\sim \text{pF}$ )

- Écriture rapide ( $\sim \text{GHz}$ )

- Lecture lente ( $\sim 10\text{MHz}$ )

- Plage dynamique : 10-13 bits

- profondeur : 100-2000 caps

- Insensible à la valeur absolue des capa (écriture et lecture de tension)

- **Basse conso**

- Possible perte de l'intégrité du signal (**droop, leakage current**)

- À la base de 90% des oscilloscopes numériques!

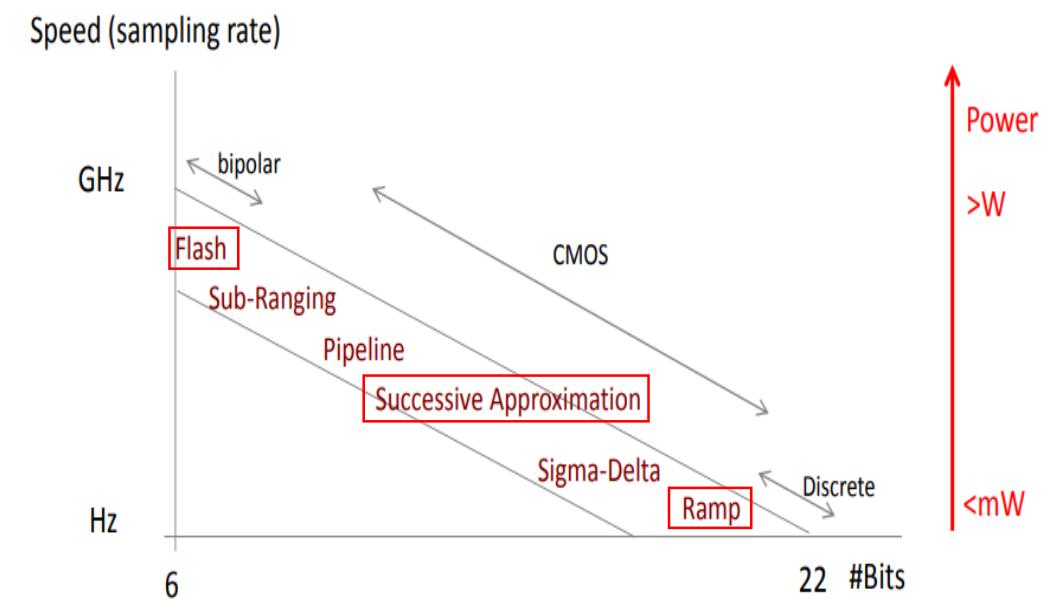

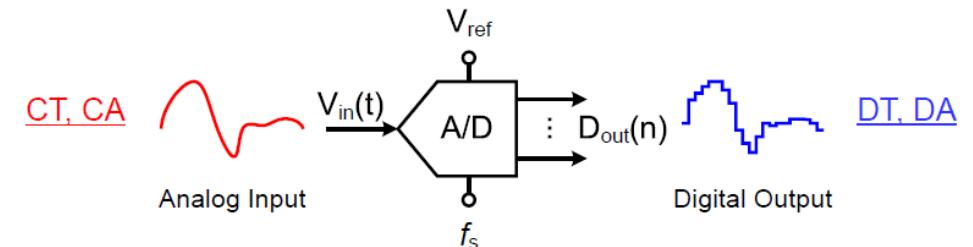

# ADC

- Un **convertisseur analogique-numérique** est un circuit qui traduit un signal analogique en une valeur numérique codée sur plusieurs bits

- Analogique: grandeur (V et I) continue, temps continu

- Numérique: grandeur discrète (quantification), temps discret (synchronous system)

- $D_{out} = 2^n \frac{V_e}{V_{ref}}$ ,  $D_{out}$  sortie de l'ADC,  $n$  le nombre de bits,  $V_e$  la tension d'entrée,  $V_{ref}$  la tension de référence de la mesure ( $LSB = \frac{V_{ref}}{2^n}$ )

- Critères

- Vitesse de conversion, dynamique d'entrée ( $V_{ref}$ )

- Résolution (nombre de bits), INL, DNL, ENOB, SINAD

- Puissance consommée

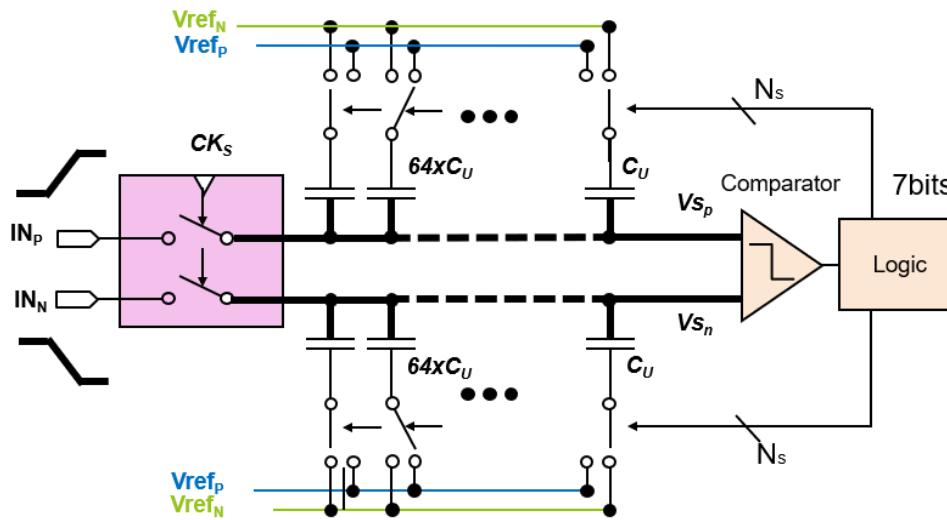

- Architectures

- Wilkinson: ADC à rampe

- SAR-ADC: Successive Approximation Register

- Pipeline

- Flash

- $\Sigma - \Delta$

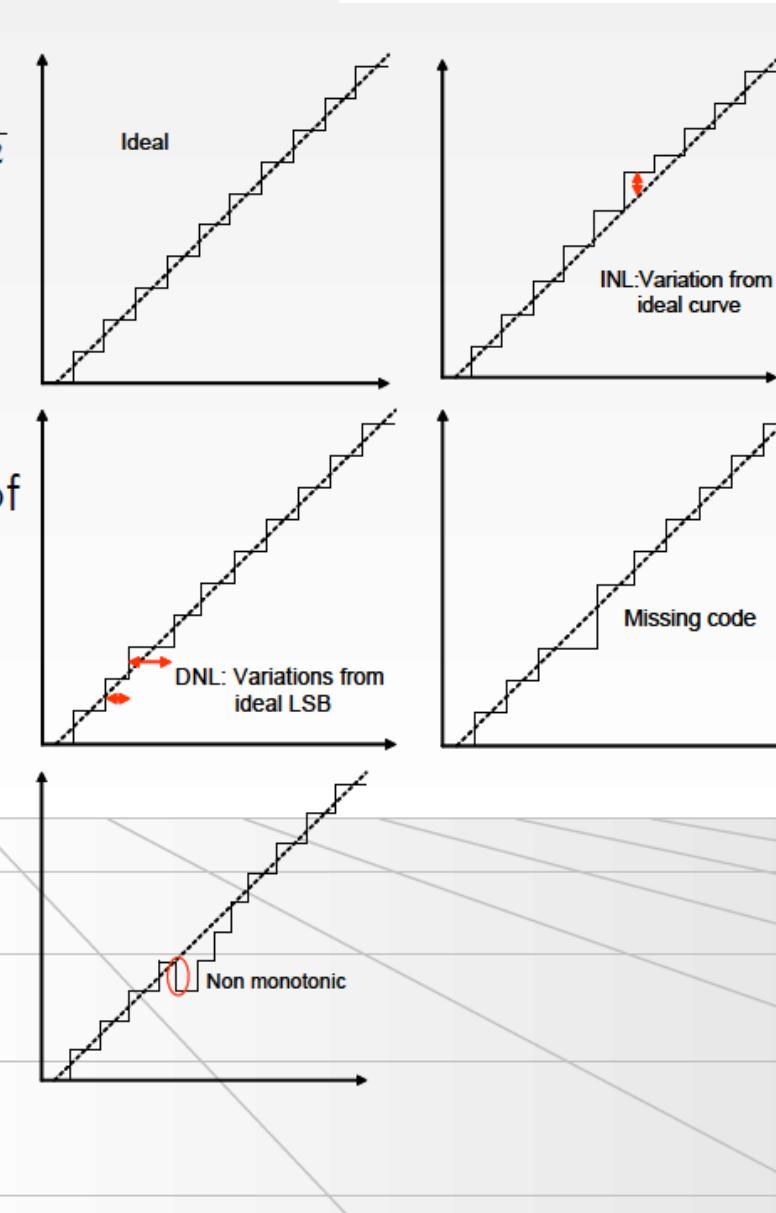

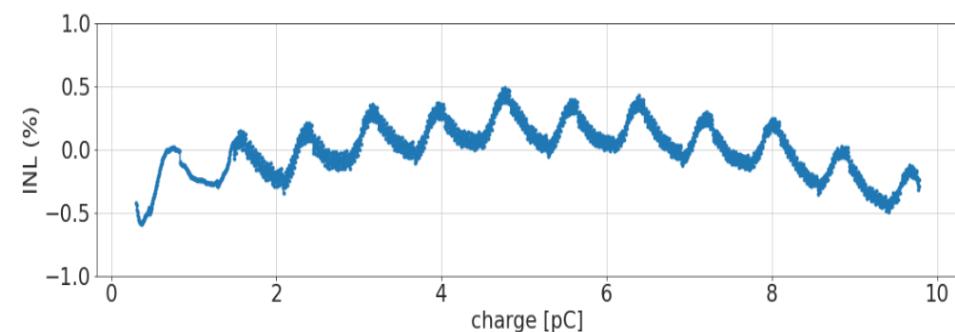

# Performance des ADC

$$DNL(i) = \frac{V_{out}(i+1) - V_{out}(i)}{\text{ideal LSB step width}} - 1$$

- Quantization (static)

- Bin size: Least significant bit (LSB) =  $V_{max}/2^n$

- Quantization error: RMS error/resolution:  $\text{LSB}/\sqrt{12}$

- Integral non linearity (INL): Deviation from ideal conversion curve (static)

- Max: Maximum deviation from ideal

- RMS: Root mean square of deviations from ideal curve

- Differential non linearity (DNL): Deviation of quantization steps (static)

- Min: Minimum value of quantization step

- Max: Maximum value of quantization step

- RMS: Root mean square of deviations from ideal quantization step

- Missing codes (static)

- Some binary codes never present in digitized output

- Monotonic (static)

- Non monotonic conversion can be quite unfortunate in some applications.

A given output code can correspond to several input v values,

# De nombreuses architectures d'ADC

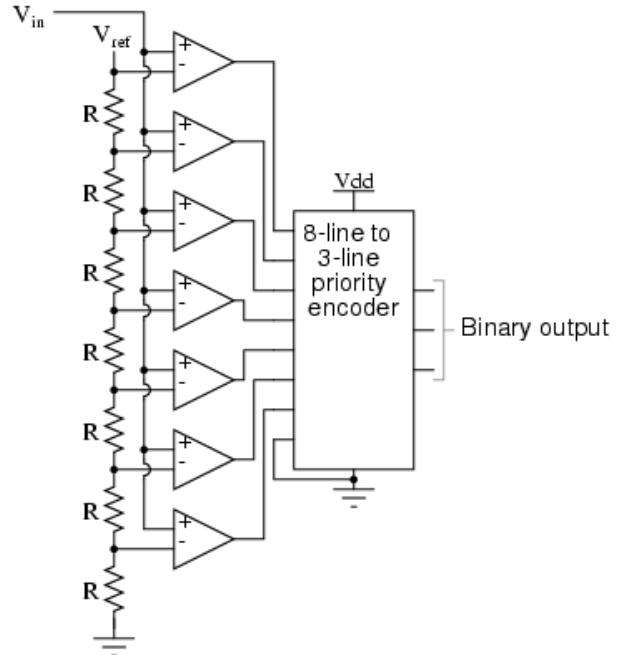

- Flash ADC

- Entièrement parallèle

- Très rapide

- Réseau de résistances

- $2^N$  résistances égales

- Entrée comparée à  $2^N-1$  références de tension

- Rarement utilisé au-delà de 6-8 bits

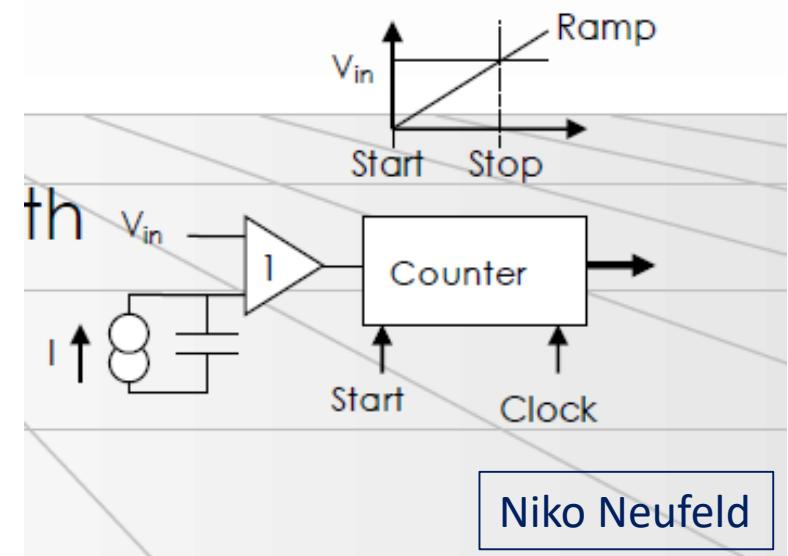

- ADC à rampe (Wilkinson)

- Échantillonnage de l'entrée sur une capa

- Décharge de cette capa à courant constant

- Mesure du temps de décharge: clock + compteur

- Lent:  $2^N$  coups d'horloge, temps mort

- Basse consommation, grande résolution

Niko Neufeld

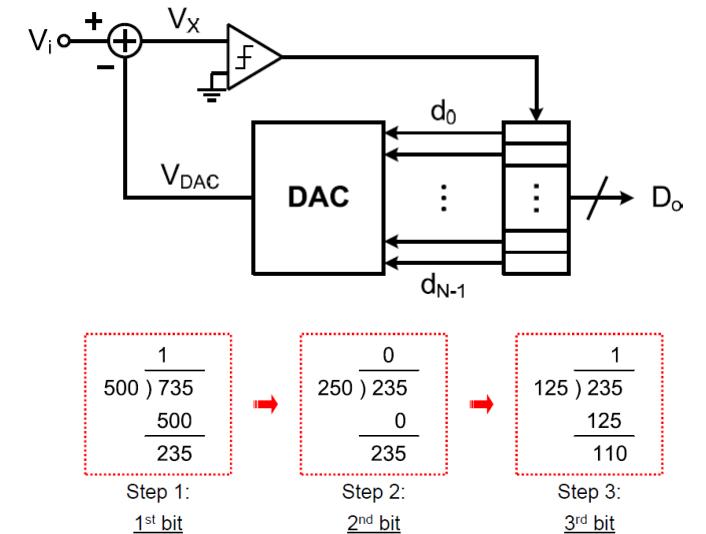

# De nombreuses architectures d'ADC

$N = 3$ ,  $FS = 1000$ ,  $\Delta = 1000/8 = 125$ ,  $V_{in} = 735$

- SAR ADC: Successive Approximation Register

- Recherche binaire à travers un DAC et un discriminateur

- Durée de conversion =  $N$  coups d'horloges (souvent asynchrone)

- Relativement lent, basse consommation

- 10-12 bits de résolution

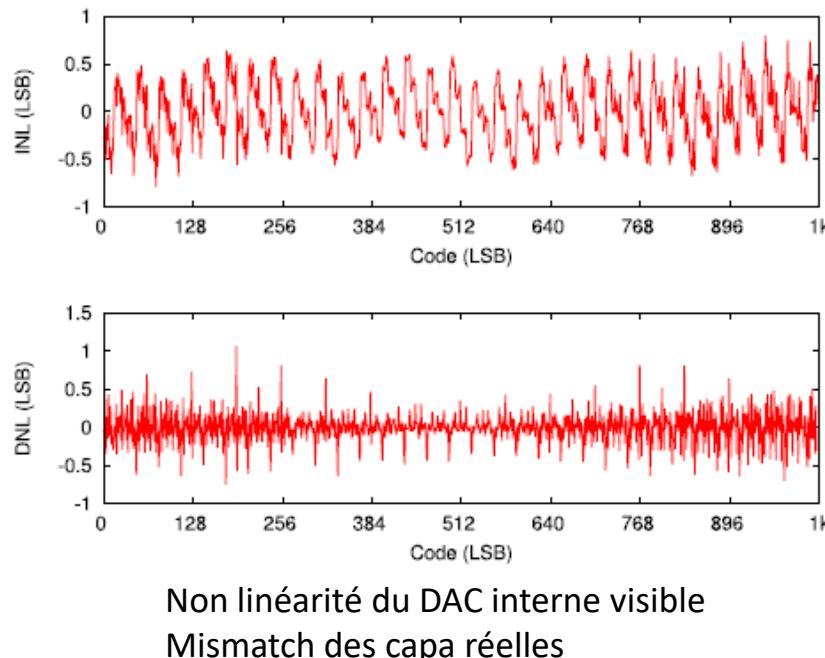

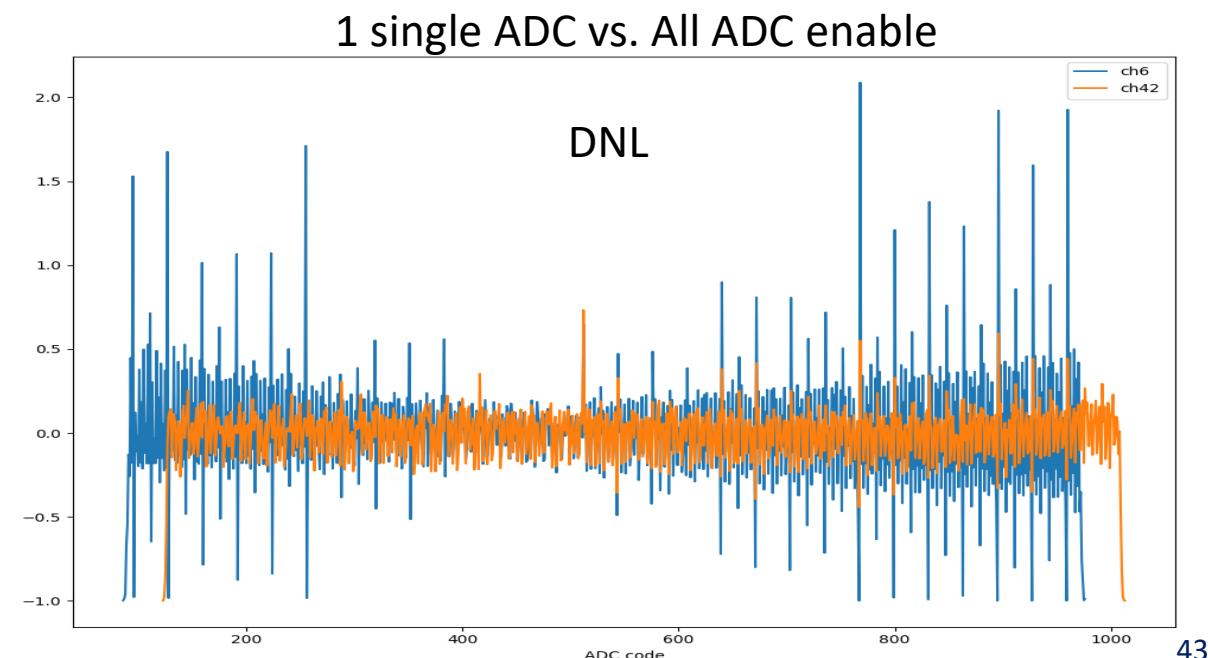

# Importance des tensions de référence

- Importance d'un layout soigné

- Minimiser capa parasites

- Prendre en compte les timing (R parasite)

- PVT simulations

- DNL et INL

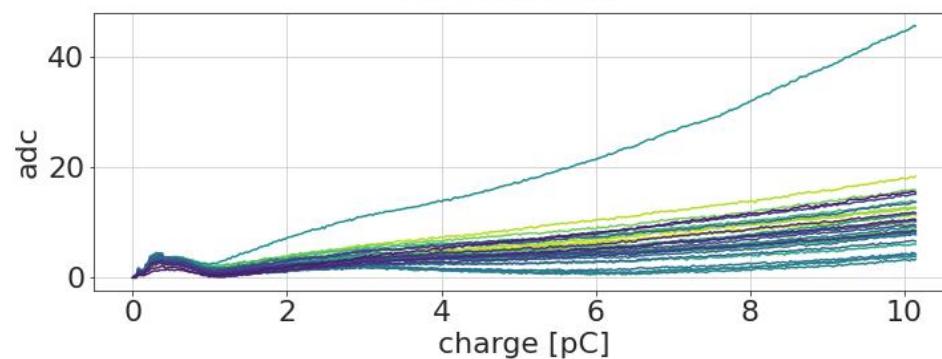

- 1 ADC / chip vs. > 30 ADC/chip

- Détérioration DNL dans régions basse et haute de la dynamique

- Plus grand excursion de la tension d'entrée

Figure 5. Layout of a single channel of 10-bit SAR ADC.

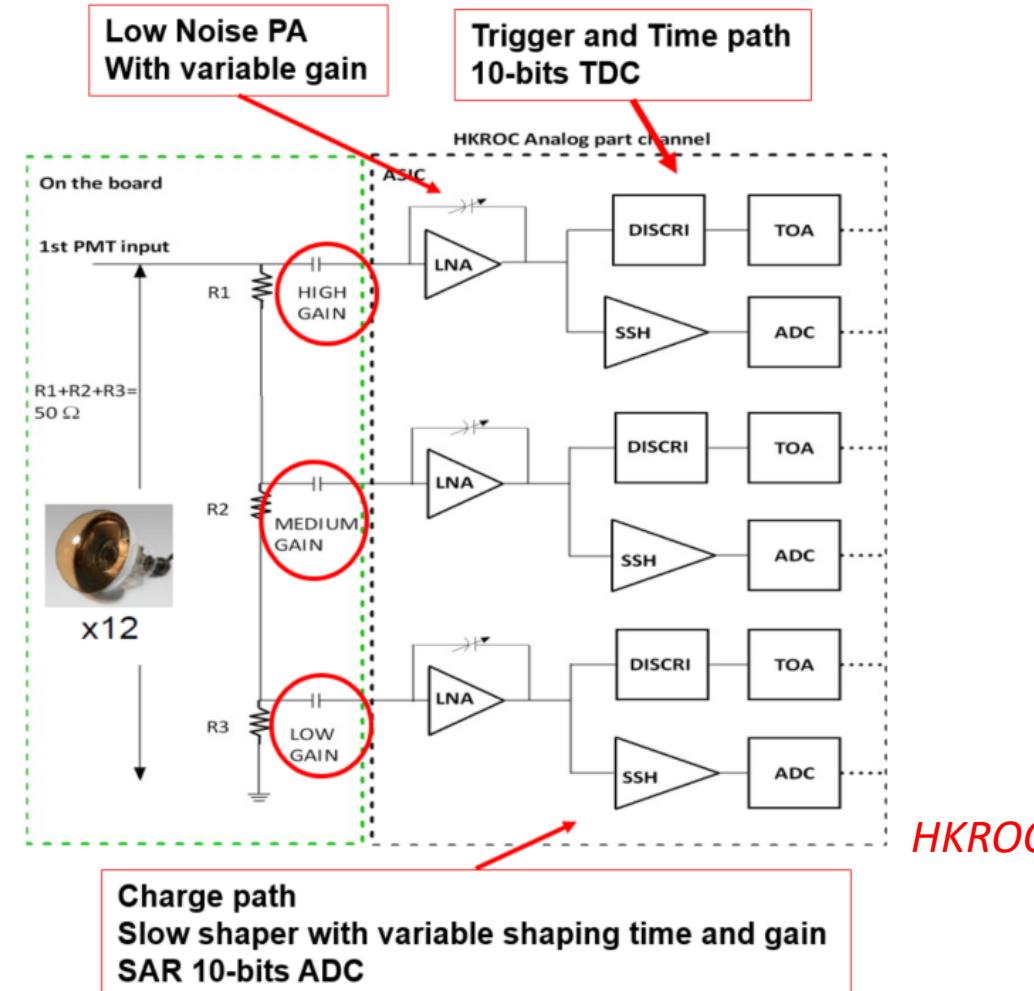

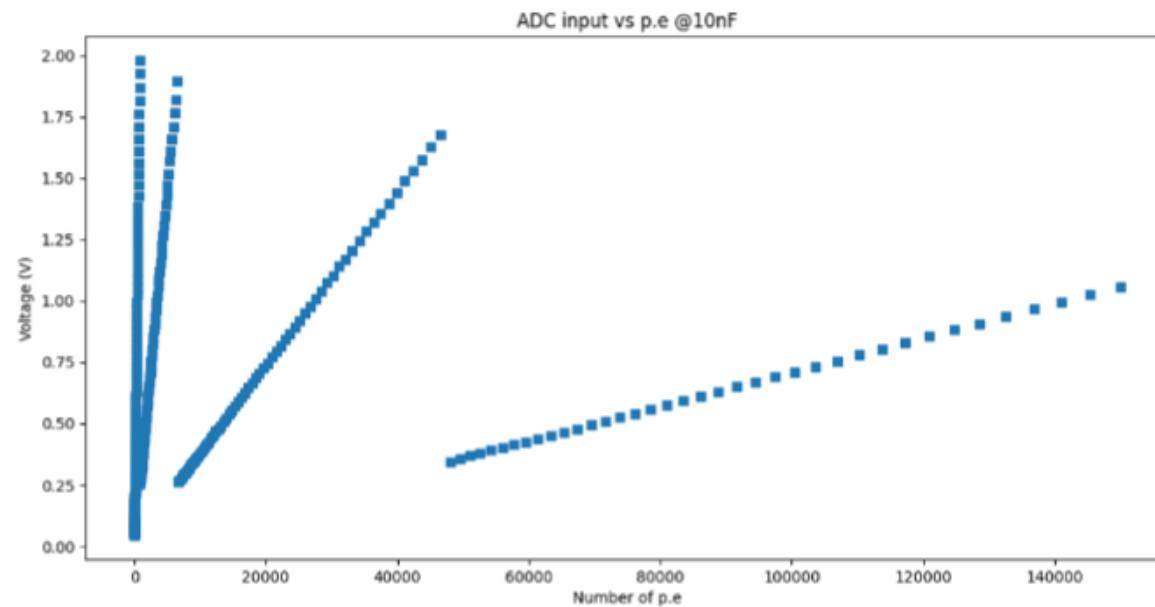

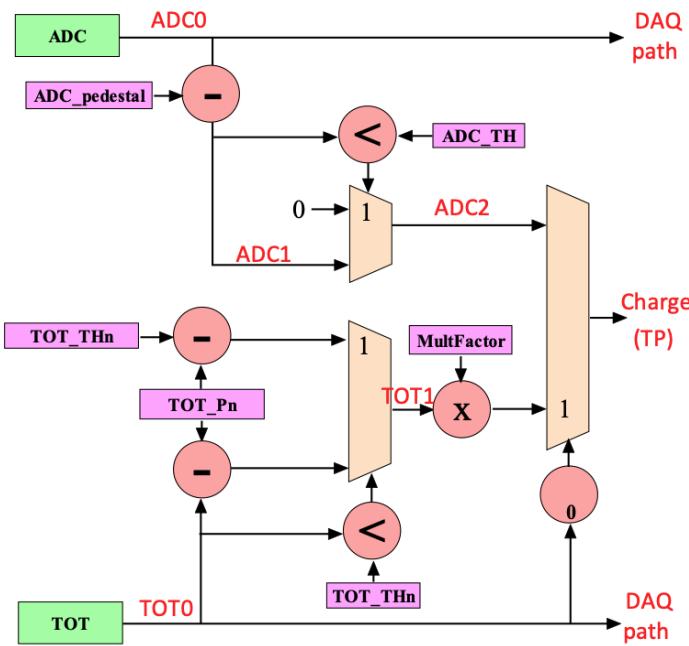

# Comment étendre la gamme dynamique (1)

- La gamme dynamique du signal à mesurer excède souvent la gamme analogique (préamp, shaper, ADC)

- Multi-gain

- Bon recouvrement

- Plus grande conso

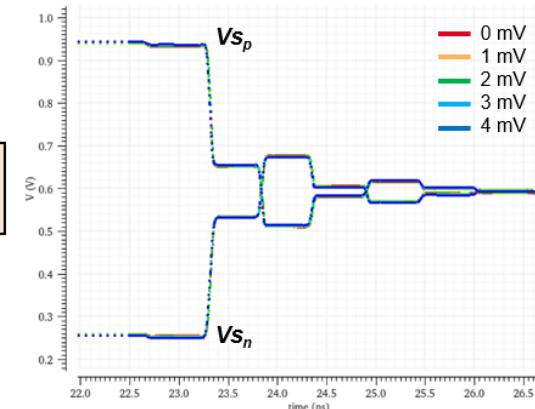

# Comment étendre la gamme dynamique (2)

- La gamme dynamique de signal à mesurer excède souvent la gamme analogique (préamp, shaper, ADC)

- Gain switching: changement de gain dynamique

- Recouvrement critique

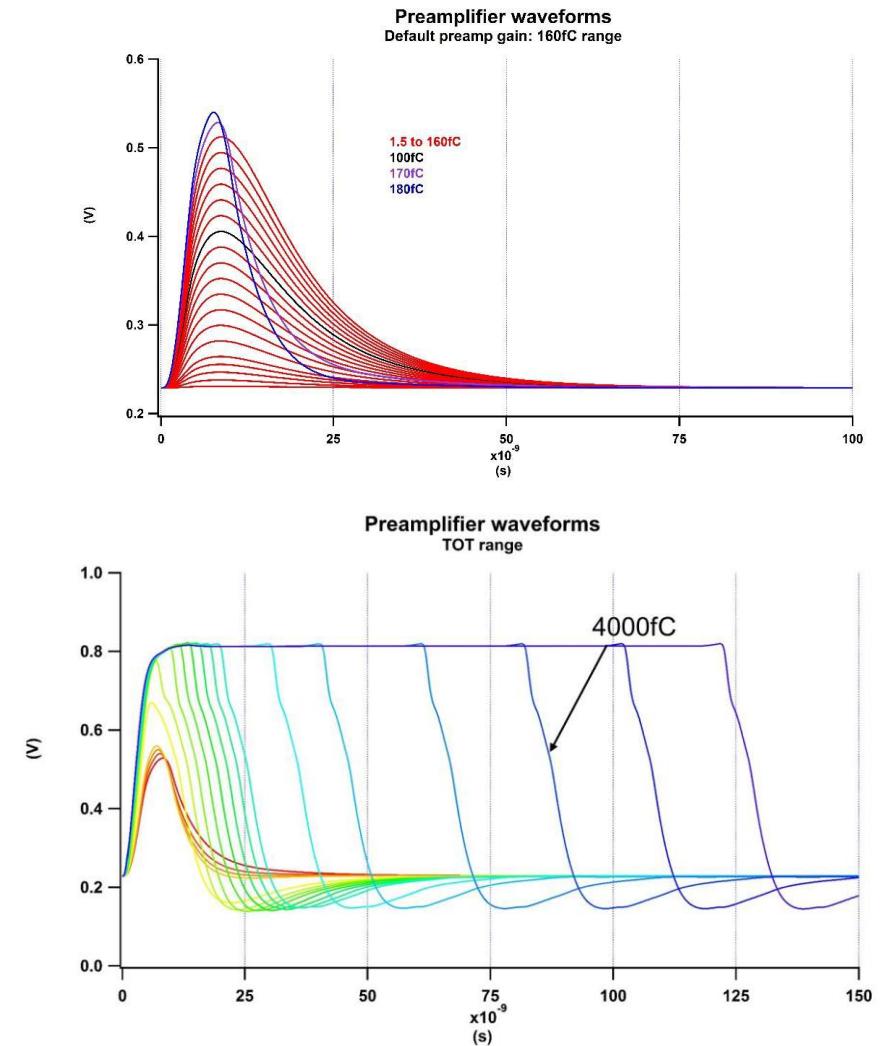

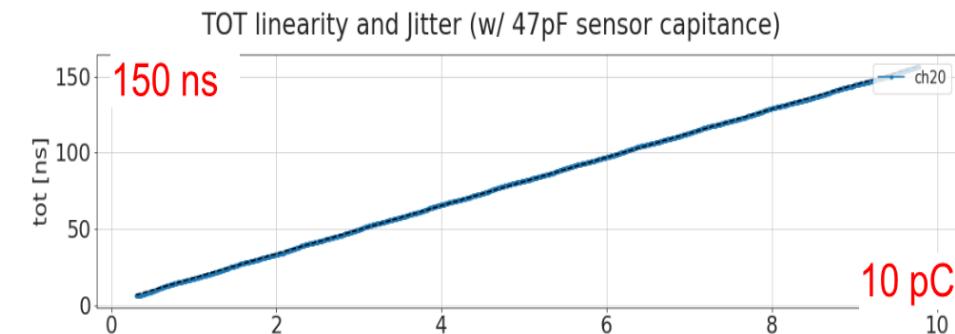

# Comment étendre la gamme dynamique (3)

- La gamme dynamique de signal à mesurer excède souvent la gamme analogique (préamp, shaper, ADC)

- Time-over-Threshold (ToT)

- Recouvrement possible mais grand temps mort

HGCROC

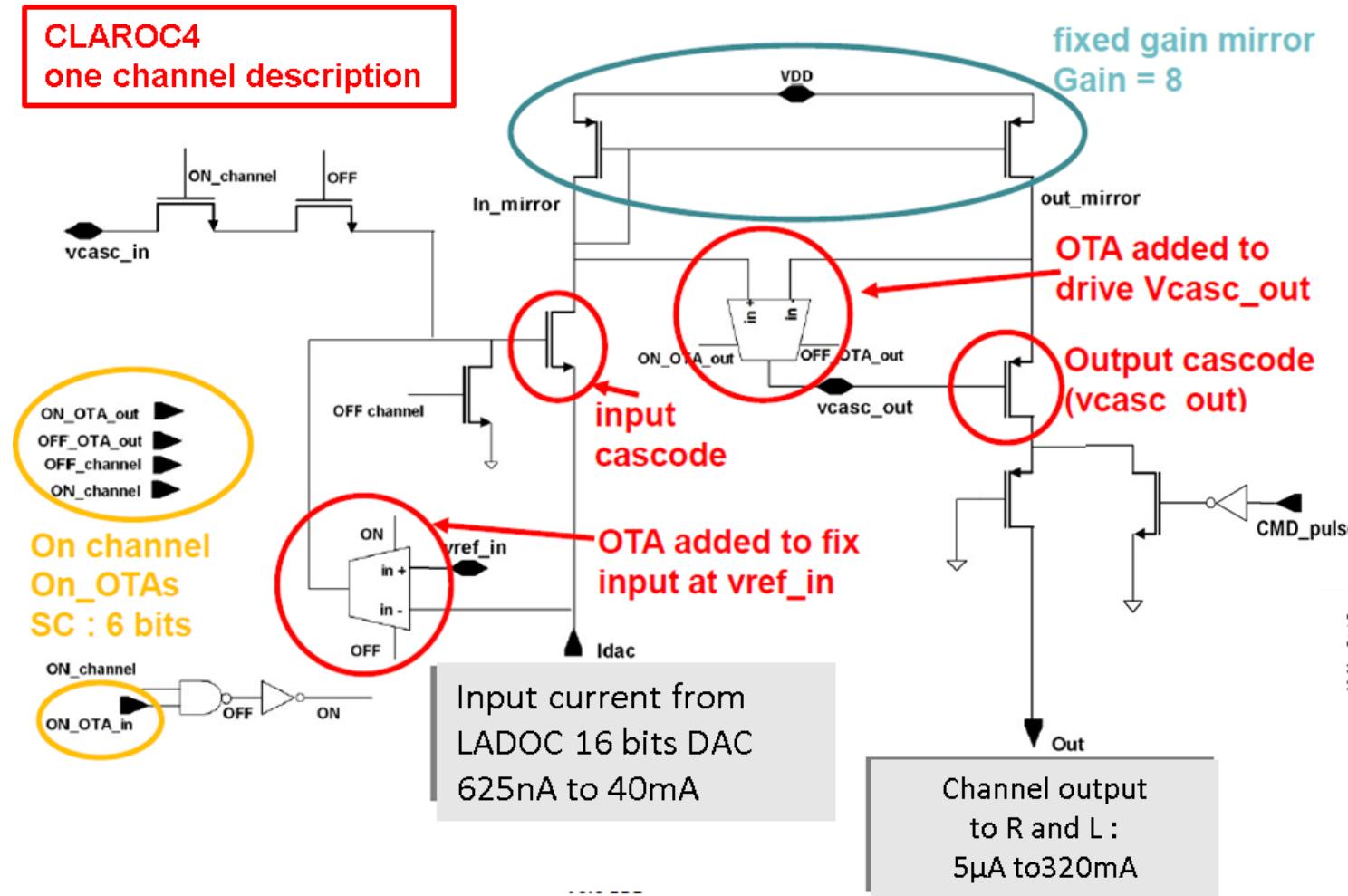

# Système de calibration dédié

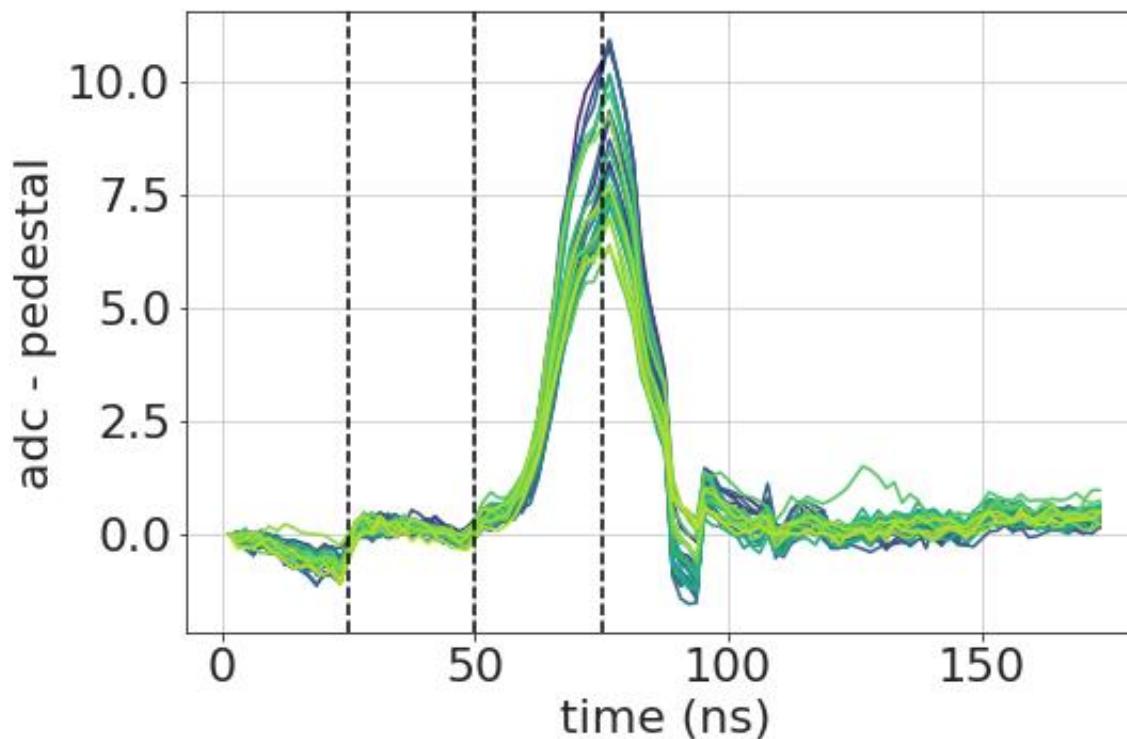

- Le signal de calibration doit imiter au mieux le signal venant du sensor!

- Grande gamme dynamique

- 16 bits ( $5\mu\text{A}$  à  $300 \text{ mA}$ )

- Excellente résolution

- Très basse non uniformité entre voies

- < 0.25 %

- Radiation hard

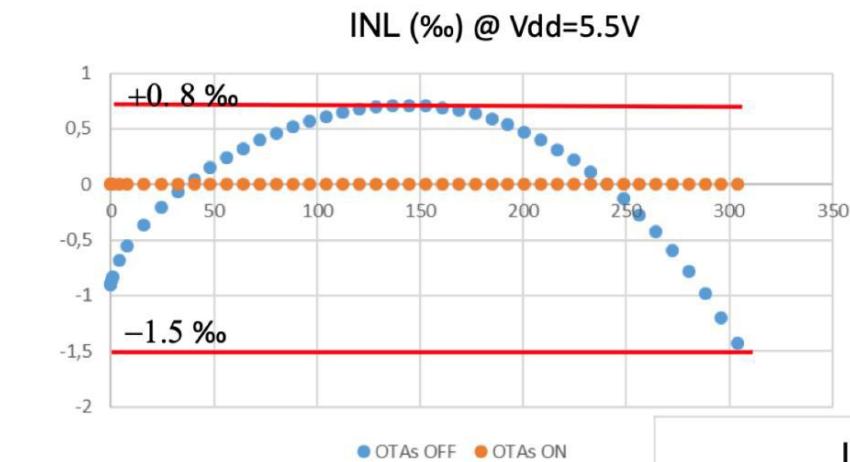

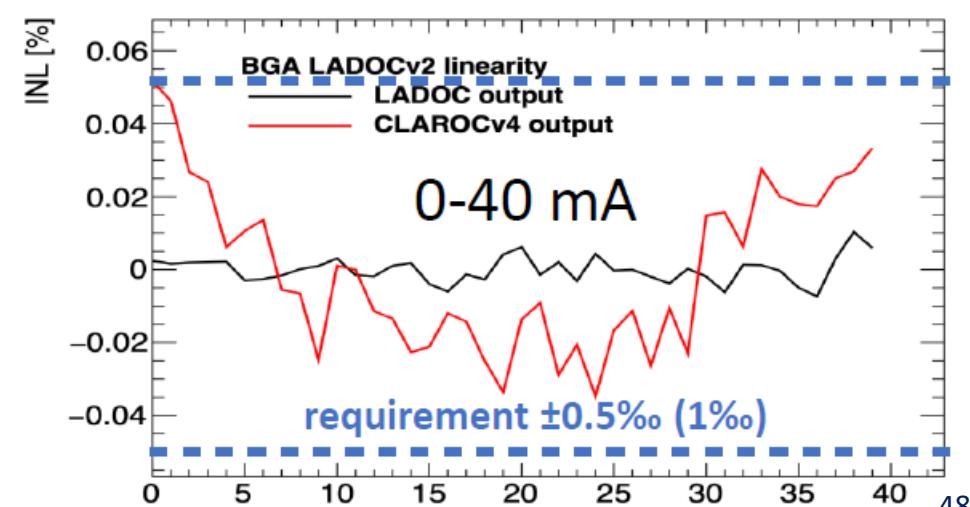

# Système de calibration dédié

Simulation

Mesures

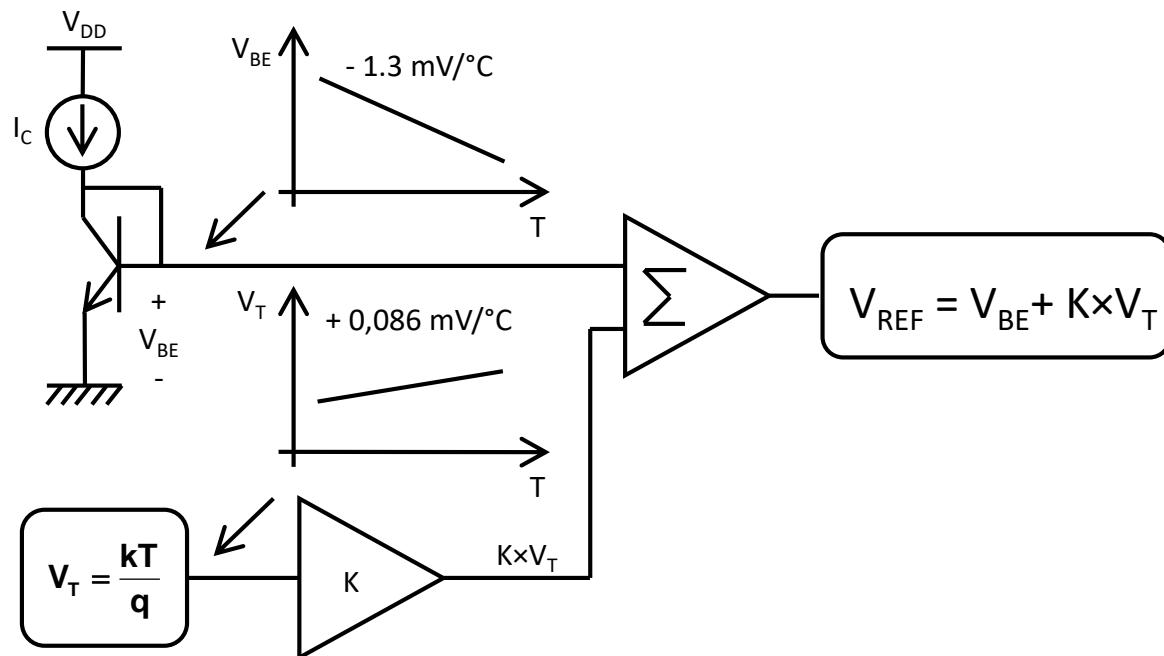

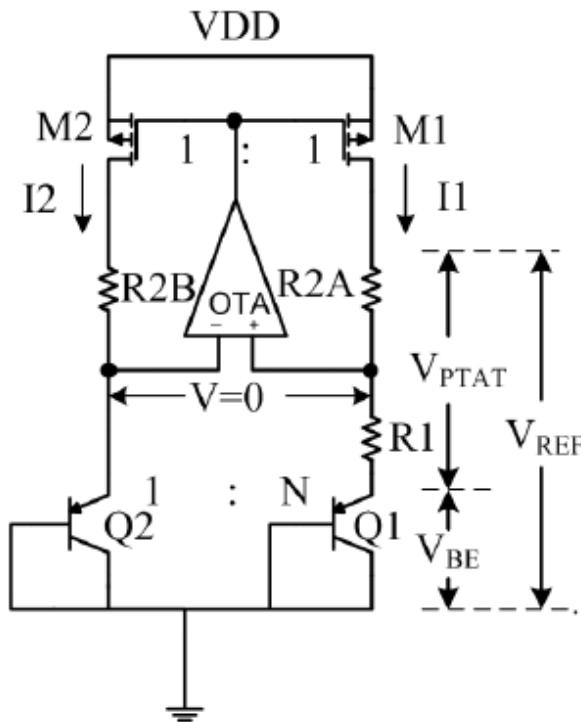

# Bandgap: principe

- Bloc analogique élémentaire dont la fonction est de générer une référence de tension indépendante des fluctuations de la température de fonctionnement

- Proche de la tension de gap du silicium → appellation "*band-gap reference*"

- Les performances sont typiquement de l'ordre d'une **dizaine de ppm/°C**

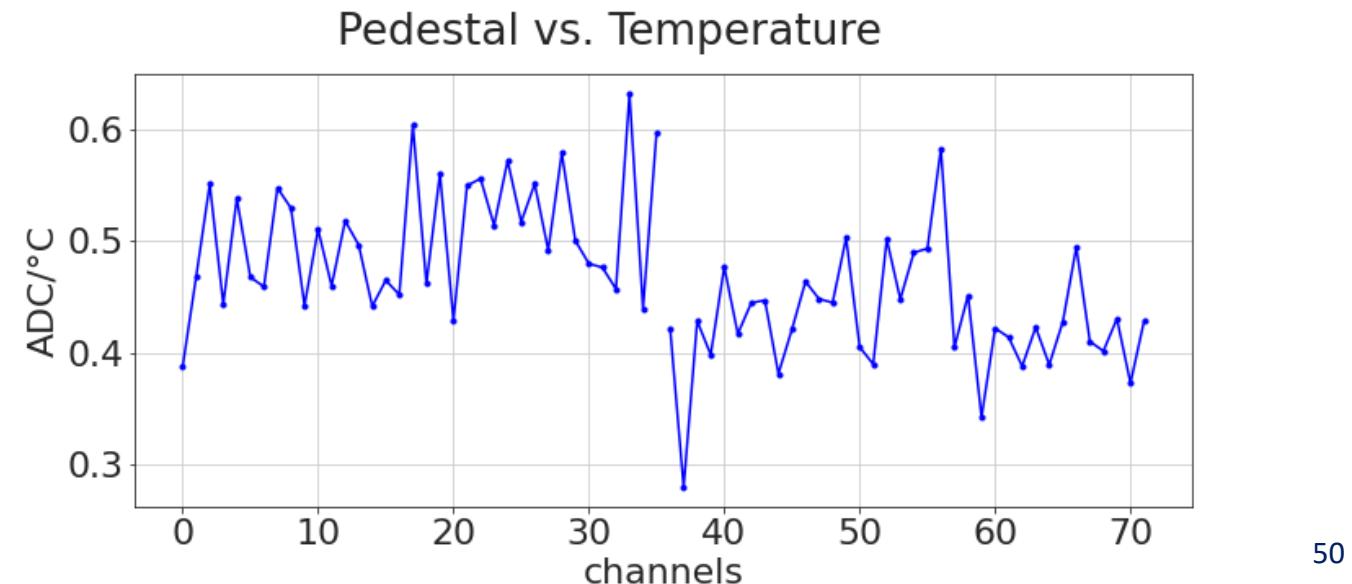

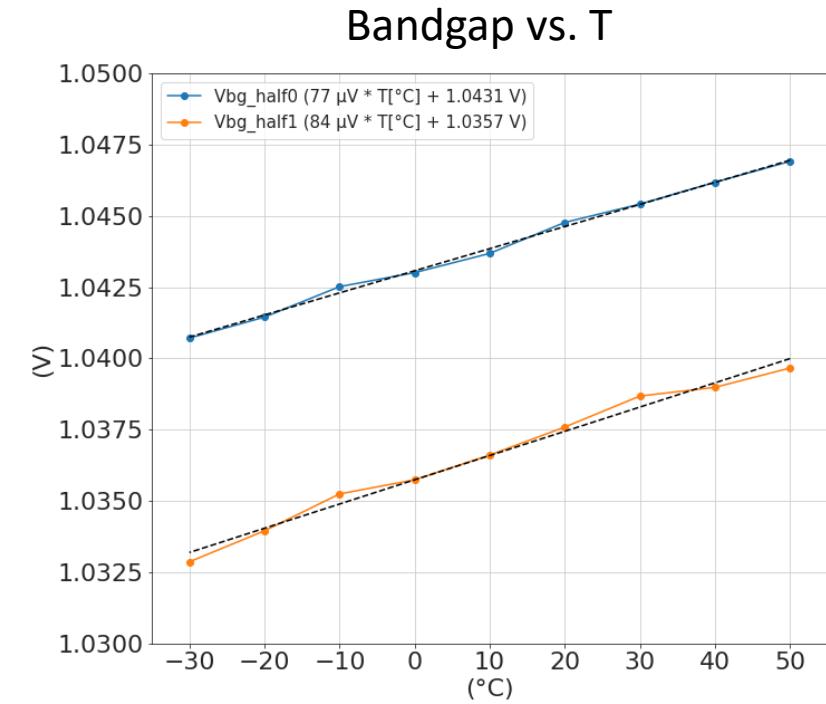

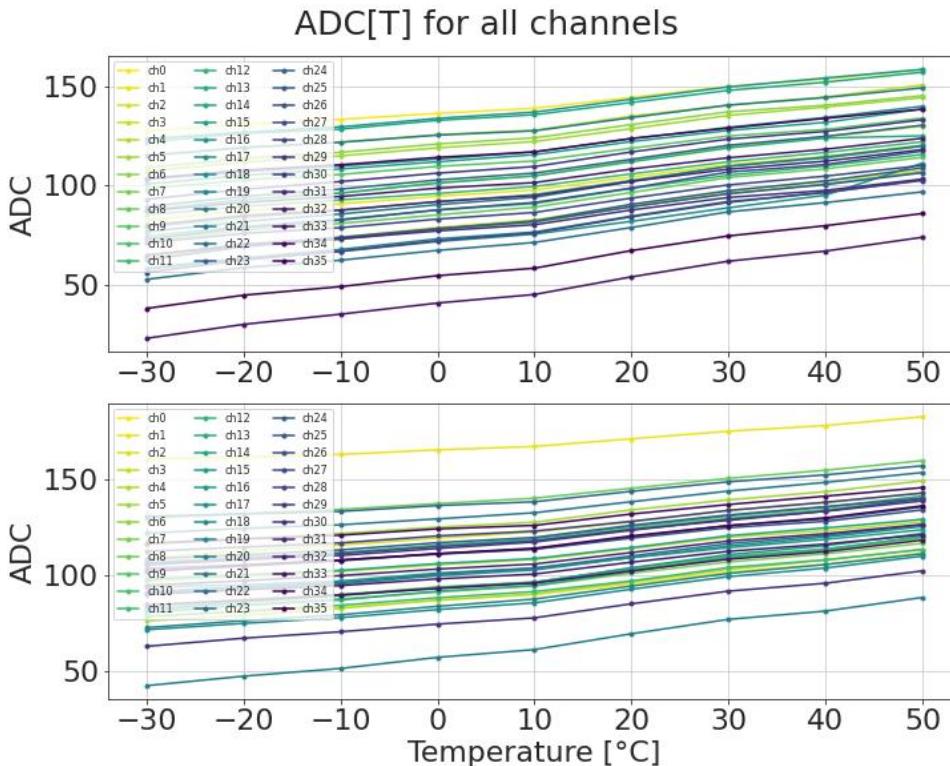

# Temperature sensitivity

- Bandgap

- $80 \mu\text{V} / ^\circ\text{C}$

- Le bandgap n'est pas suffisant:  $V_{\text{ref}} = V_{\text{bg}} + R^*i$

- Variation de R avec T.

- Exemple:  $R = 89\% \text{ rphpoly} + 11\% \text{ rplpoly}$

- Pedestals

- $+ 0.5 \text{ ADCu}/^\circ\text{C}$

# Électronique numérique

```

module dff(

output [7:0] Q, // data output

input  [7:0] D, // data input

input  RST,   // Synchronous Reset

input  CLK); // clock input

reg [7:0] Q;

always @ (posedge CLK)

begin

if (RST)

Q <= 0;

else

Q <= D;

end

endmodule

```

# Aperçu d'un ROC (Read-Out Chip)

- Le plus souvent, une architecture similaire

- Très petits signaux (fC) → besoin d'**amplification** → préamplificateur

- Mesure de l'**amplitude** et/ou du **temps** → ADC, discri, TDC

- Plusieurs milliers à millions de voies → forte intégration, basse conso

- Environnement → **radiation, température**

# Plan du cours

- Introduction: de l'électronique partout dans nos détecteurs

- Fondamentaux de l'électronique

- Rappel général des bases de l'électronique

- Détecteur et préamplificateur

- Conversion Analogique/Numérique

- **Numérique**

- **Le langage HDL (VHDL ou Verilog), synthèse, vérification**

- **De plus en plus de numérique dans les ASICs**

- **Design Flow: Analog-on-Top ou Digital-on-Top**

- Bruit électronique

- Fondamentaux

- Filtrage, shaping

- Techniques de mesure

- Effets des radiations sur l'électronique

- TID et SEE

- Campagnes d'irradiation, performances, cross-section

- Extrême importance des tests: sur table, radiation, beam, système

- La mesure de temps

- Généralité

- Les TDCs

# Pourquoi le numérique?

- Représenter une grandeur physique par des nombres discrets

- Volt = différence de potentiel: réalité physique continue

- ADC = représentation numérique d'une tension

- Résolution, perte d'information

- Facilité de calcul, mémorisation, transmission, encodage, etc.

- En électronique nombre en base 2 (fonctionne comme la base 10)

- $19,05 = 1 \times 10^1 + 9 \times 10^0 + 0 \times 10^{-1} + 5 \times 10^{-2}$  (chiffre, poids)

- $(19)^{10} = (10011)_2 = 1 \times 2^4 + 0 \times 2^3 + 0 \times 2^2 + 1 \times 2^1 + 1 \times 2^0$

- Utiliser les transistors (gates) pour effectuer des opérations logiques

- OU, ET, XOR, Latch

- Logique combinatoire, algorithme

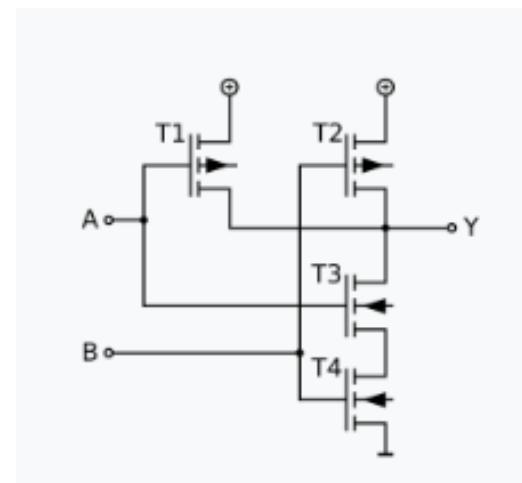

- NMOS(0,1) = (X, 0) et PMOS(0,1) = (1,X)

- « Facilement » describable par un code/langage

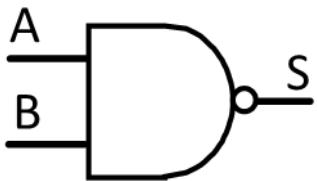

| NAND |   |   |

|------|---|---|

| A    | B | Y |

| 0    | 0 | 1 |

| 0    | 1 | 1 |

| 1    | 0 | 1 |

| 1    | 1 | 0 |

# Langage de description matériel

Very High Speed Integrated Circuit

Hardware

Description

Langage

WIKIPÉDIA

L'encyclopédie libre

VHDL est un langage de description de matériel destiné à représenter le comportement ainsi que l'architecture d'un système électronique numérique

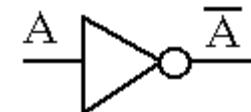

# VHDL : une abstraction de plus

```

entity INV1 is

port (

A: in STD_LOGIC;

B: out STD_LOGIC);

end INV1;

```

```

architecture RTL of INV1 is

begin

B <= NOT A;

end RTL;

```

Silicium

Transistor

Gate

VHDL

# Pourquoi utiliser un HDL ?

- Accélérer la conception de circuits (raisons économiques)

- Développer des architectures numériques de circuits très complexes (milliards de portes logiques)

- Permettre de réutiliser et/ou d'améliorer le code pour des systèmes futurs (code VHDL)

- Être indépendant de la technologie et de la cible

- Avoir les avantages d'un « langage de programmation »

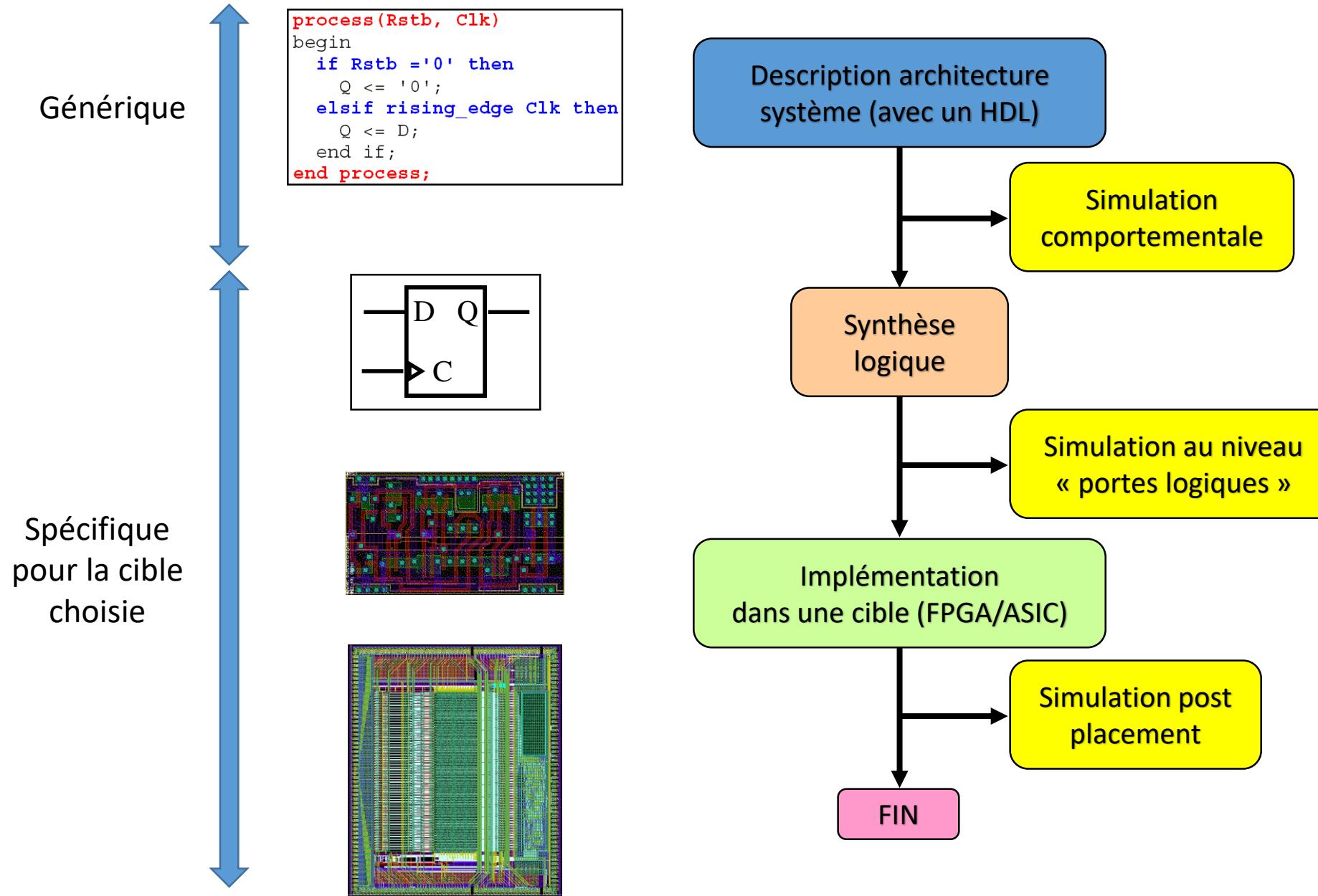

# Flot de conception avec un HDL

# Exemples de systèmes

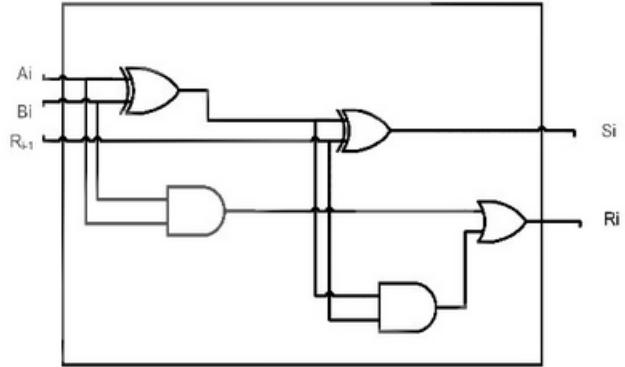

## Calcul/opérations sur des nombres

## Machine d'états - automate

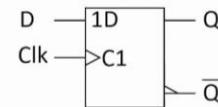

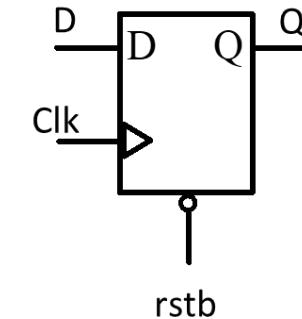

## Logique synchrone (D FlipFlop) (Discrétisation du temps)

| Table de vérité |   |    |            |

|-----------------|---|----|------------|

| Clk             | D | Q  | $\bar{Q}$  |

| 0, 1, ↓         | X | Q0 | $\bar{Q}0$ |

| ↑               | 0 | 0  | 1          |

| ↑               | 1 | 1  | 0          |

|                 |   |    | (Reset)    |

|                 |   |    | (Set)      |

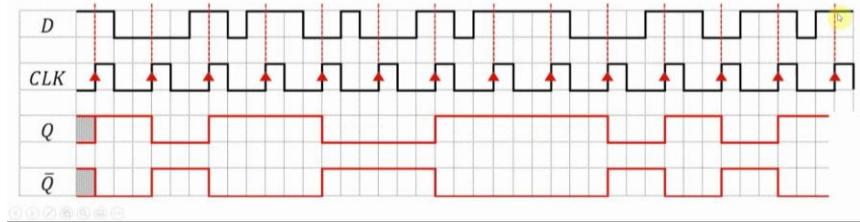

## Processeur (hw/fw/sw)

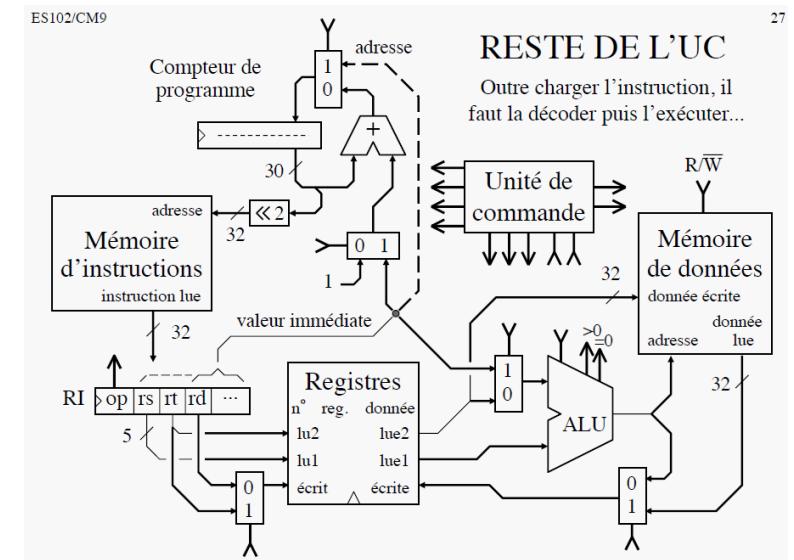

# VHDL est-il le seul HDL ?

- Le « Verilog HDL » (abréviation Verilog... et non VHDL) est un autre langage de description matérielle. Il a été développé par CADENCE (IEEE 1364 maintenant)

- Le system Verilog (IEEE 1800) est la suite logique du Verilog

- Utilisation

- VHDL bien implanté pour la programmation de FPGA

- Verilog préféré pour la conception d'ASIC

# Quelles cibles ?

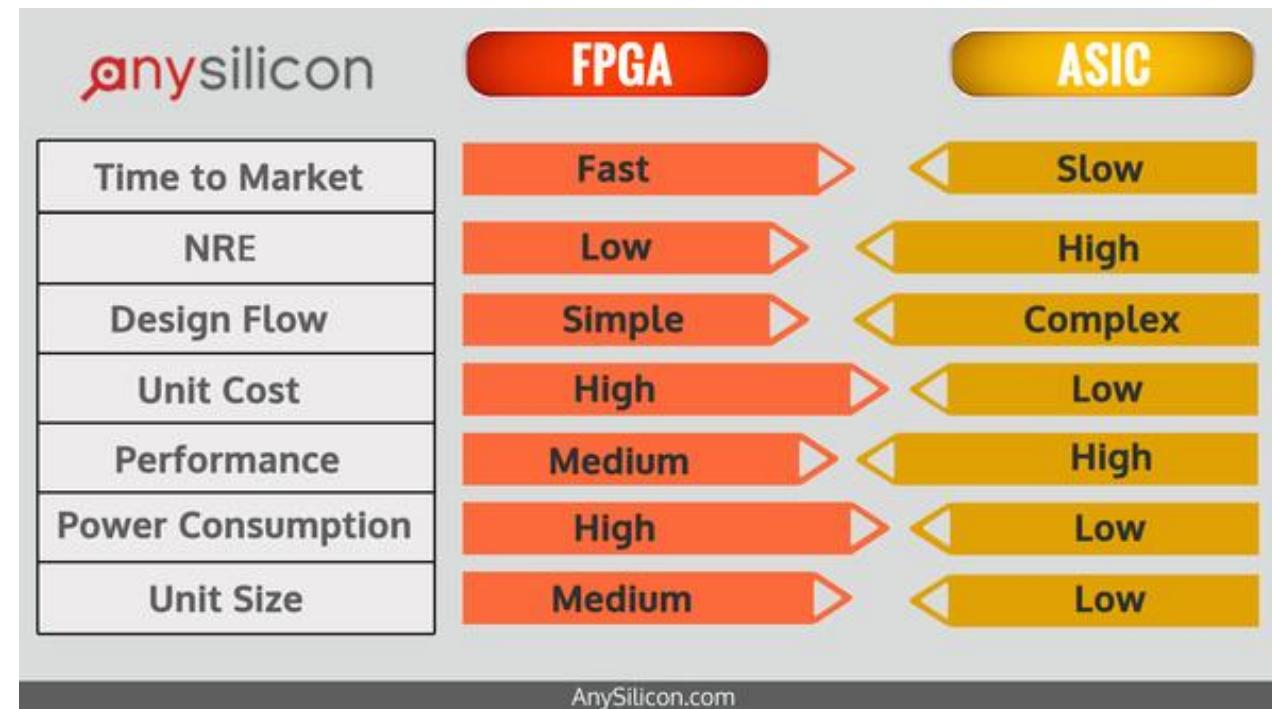

- **FPGA** (Field Programmable Gate Array) est un circuit intégré qui comporte une matrice de portes logiques programmable (reconfigurable) après sa fabrication. C'est un composant que l'on achète pour y planter notre code HDL

- **ASIC** (Application Specific Integrated Circuit) est un circuit intégré dédié à une seule application. C'est un composant que l'on va développer : son architecture est définie par le code HDL. Il est ensuite envoyé en fabrication

NRE: coût de recherche et développement

# Traduction VHDL

```

1 -- Simple NAND gate design

2 library IEEE;

3 use IEEE.std_logic_1164.all;

4

5 entity nand_gate is

6 port(

7     a: in std_logic;

8     b: in std_logic;

9     s: out std_logic);

10 end nand_gate;

11

12 architecture rtl of nand_gate is

13 begin

14     s <= a nand b;

15 end rtl;

16

```

```

1 Library IEEE;

2 USE IEEE.std_logic_1164.all;

3

4 entity DFlipFlop is

5 port(

6     D: in std_logic;

7     Clk: in std_logic;

8     rstb: in std_logic;

9     Q: out std_logic

10 );

11 end DFlipFlop;

12

13 architecture rtl of DFlipFlop is

14 begin

15

16     process(Clk,rstb)

17     begin

18         if(rstb = '0') then

19             Q <= '0';

20         elsif rising_edge(Clk) then

21             Q <= D;

22         end if;

23     end process;

24

25 end rtl;

```

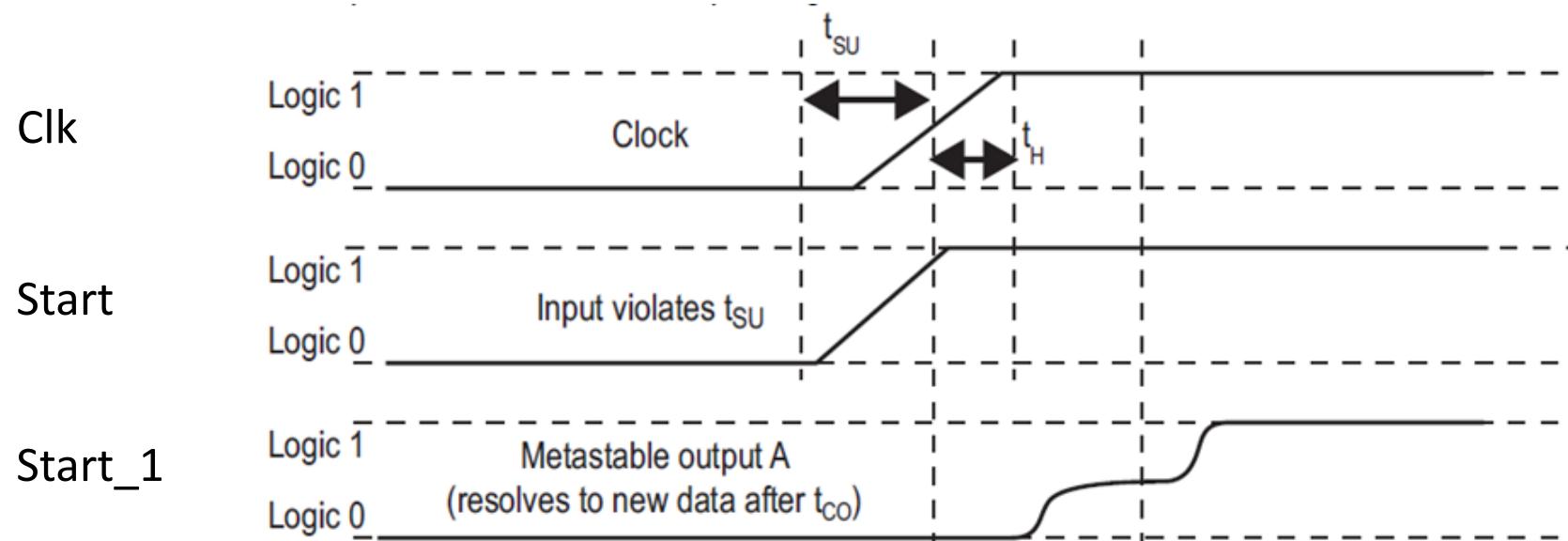

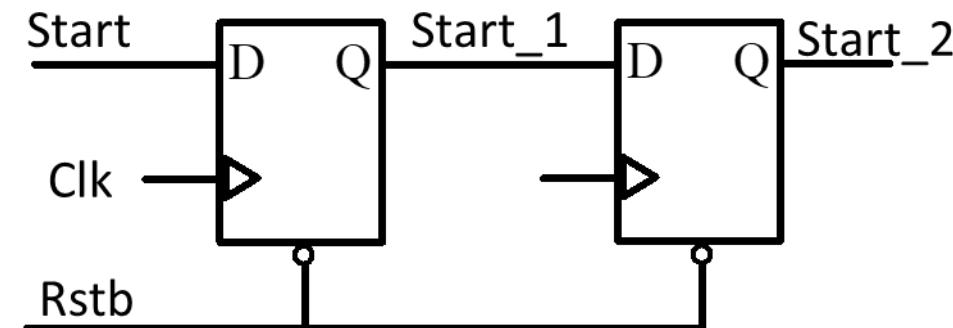

# Synchronisation d'un signal

- Pour « éviter » les métastabilités (violation du temps de setup/hold de la bascule D) dues à un signal asynchrone

```

SynchroStart : process (Rstb, Clk)

begin

if Rstb = '0' then

Start_1 <= '0';

Start_2 <= '0';

elsif rising_edge(Clk) then

Start_1 <= Start;

Start_2 <= Start_1;

end if;

end process SynchroStart;

```

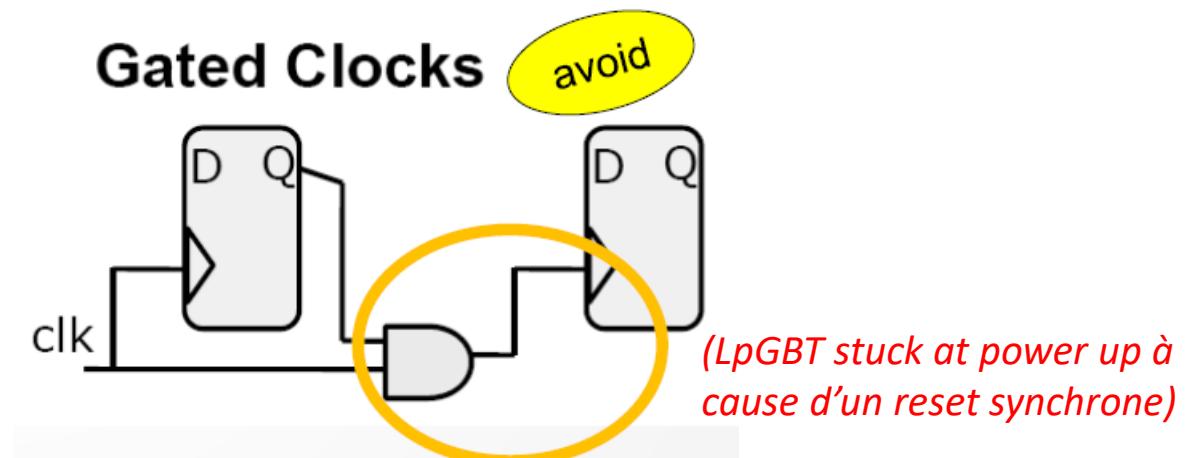

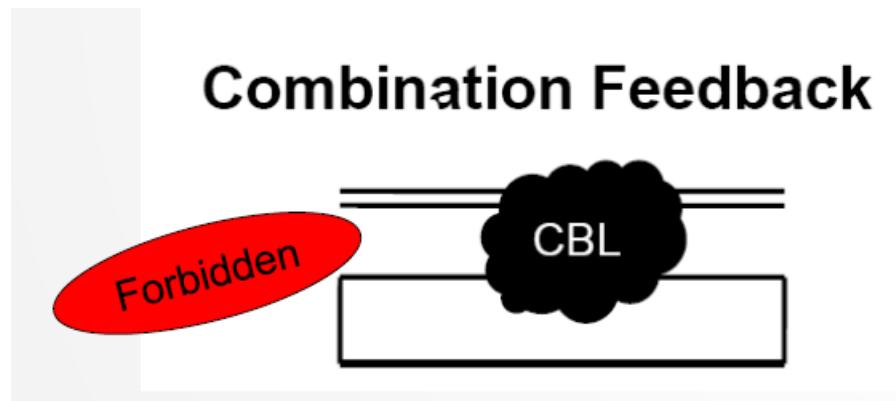

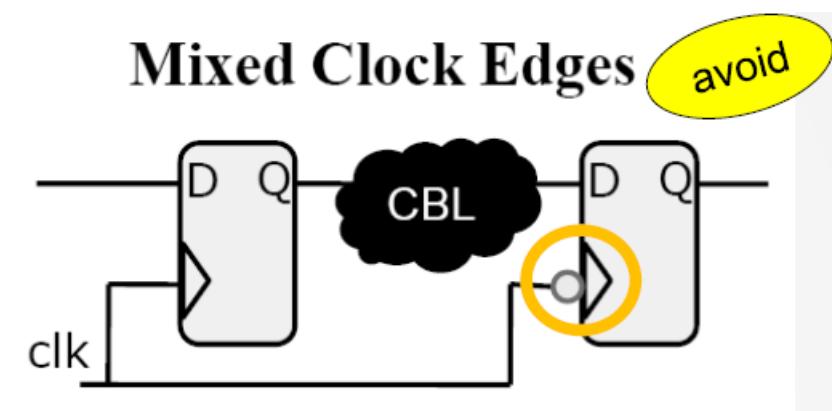

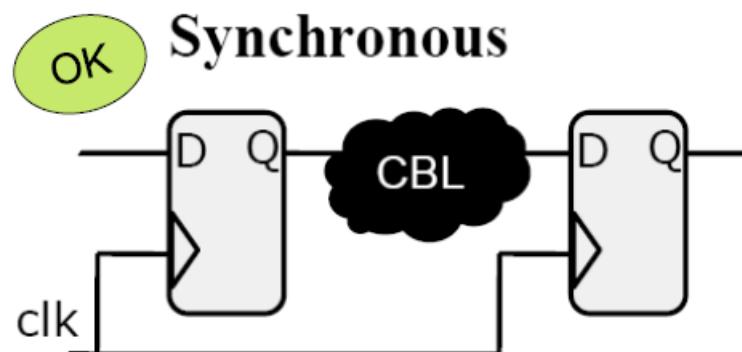

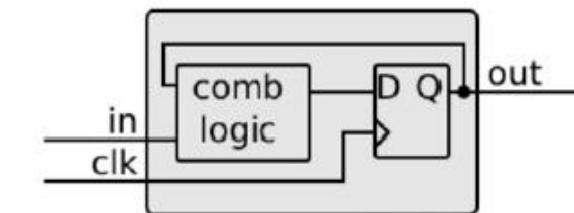

# Register Transfert Level (RTL)

- Le numérique doit être synchrone

- RTL: Register transfert Level

- Ou alors vous devez savoir ce que vous faites!

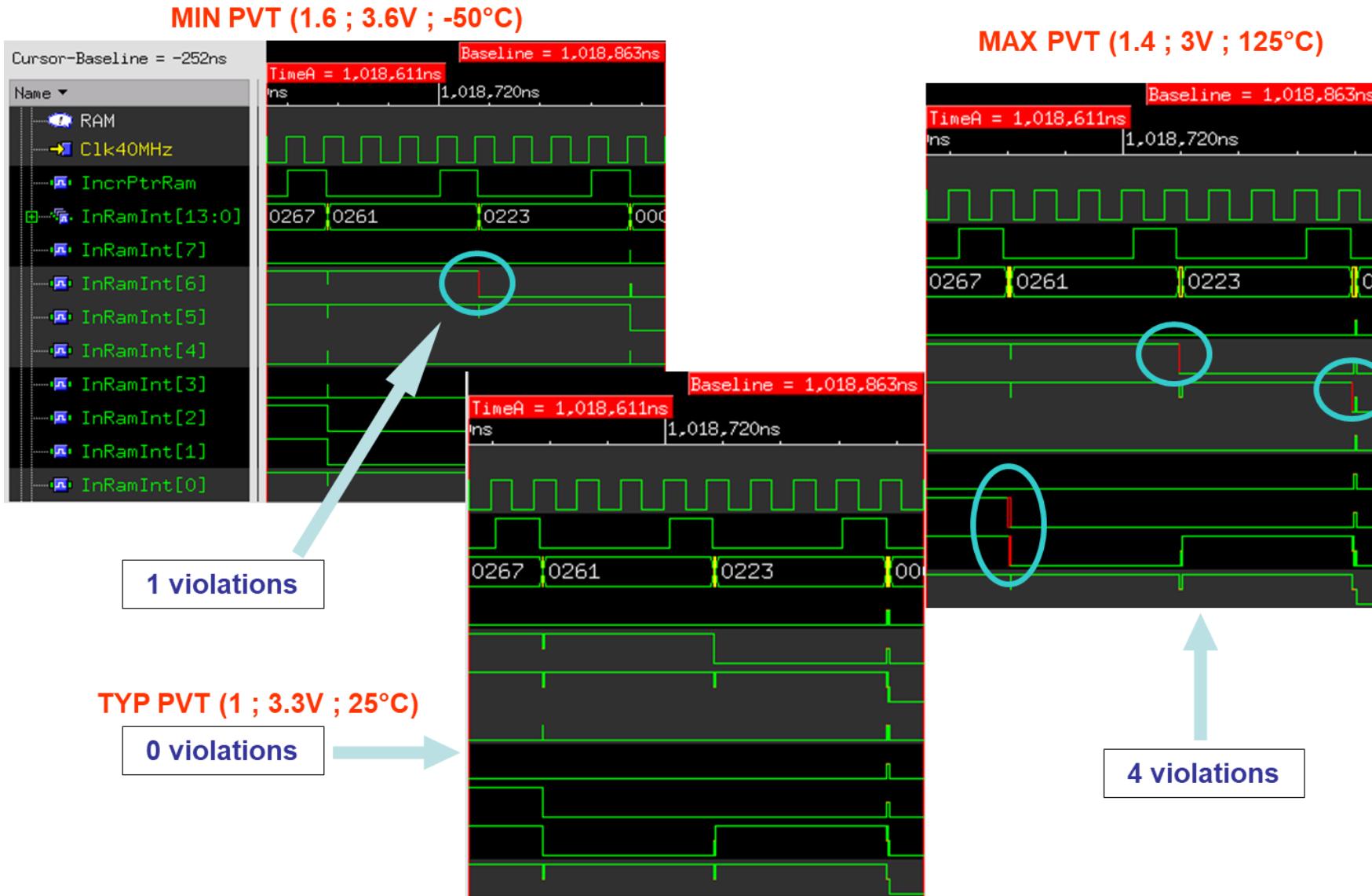

# Les simulations post-placement, PVT

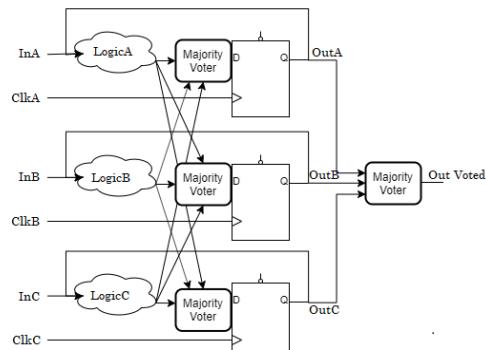

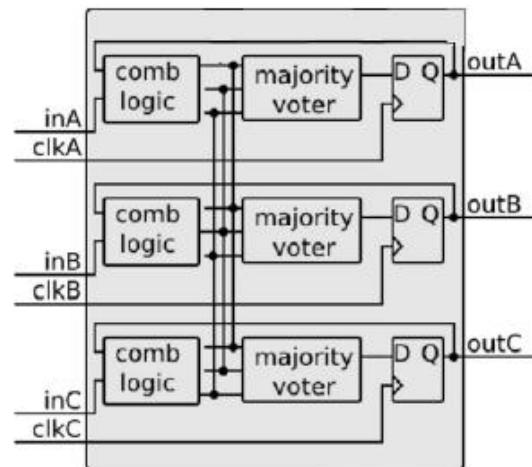

# Robuste aux SEEs: dans la logique

## Logic

```

always @(+)

begin

if (EC_reset || Startup_reset) begin

EventCounter_iNext <= 6'd1;

end else begin

if (L1Trig) EventCounter_iNext <= EventCounter_i + 1'b1;

else EventCounter_iNext <= EventCounter_i;

end

end

```

## Register

```

always @posedge clk

begin

EventCounter_i <= EventCounter_iNextVoted;

end // always

```

## Majority Voter

```

wire [5:0] EventCounter_iNextVoted = EventCounter_iNext;

```

## TMRG Utility

```

[INFO] Triplication starts here

[INFO]

[INFO] Triplicating file EventCounter.v

[INFO] TMR voting EventCounter_iNext -> EventCounter_iNextVoted (bits:6)

[INFO] Creating TMR error group A

[INFO] Creating TMR error group B

[INFO] Creating TMR error group C

[INFO] Instializing voter EventCounter_iNextVoterA (addWires:output)

[INFO] Instializing voter EventCounter_iNextVoterB (addWires:output)

[INFO] Instializing voter EventCounter_iNextVoterC (addWires:output)

[INFO] Declarations of voters and fanouts are being added to ./EventCounterTMR.v.new

[INFO] Taking voter declaration from ./exp/design/extier/tools/tmrg/src/..../common/voter.v

[INFO] Saving output to './EventCounterTMR.v'

[INFO] Generating SDC constraints file ./EventCounterTMR.sdc

omega4/extier >

```

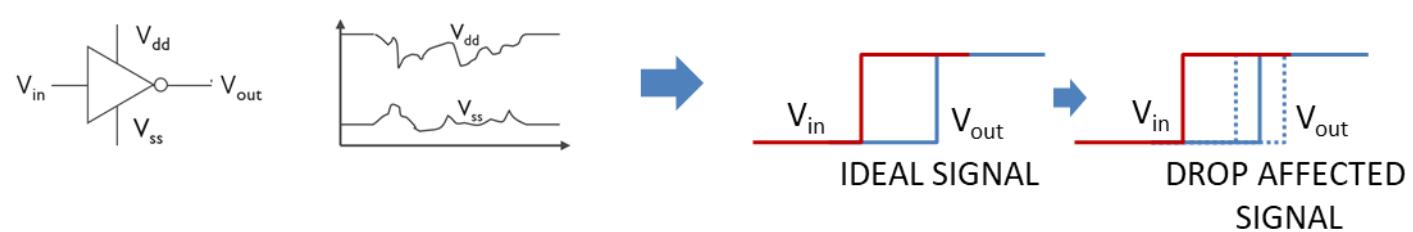

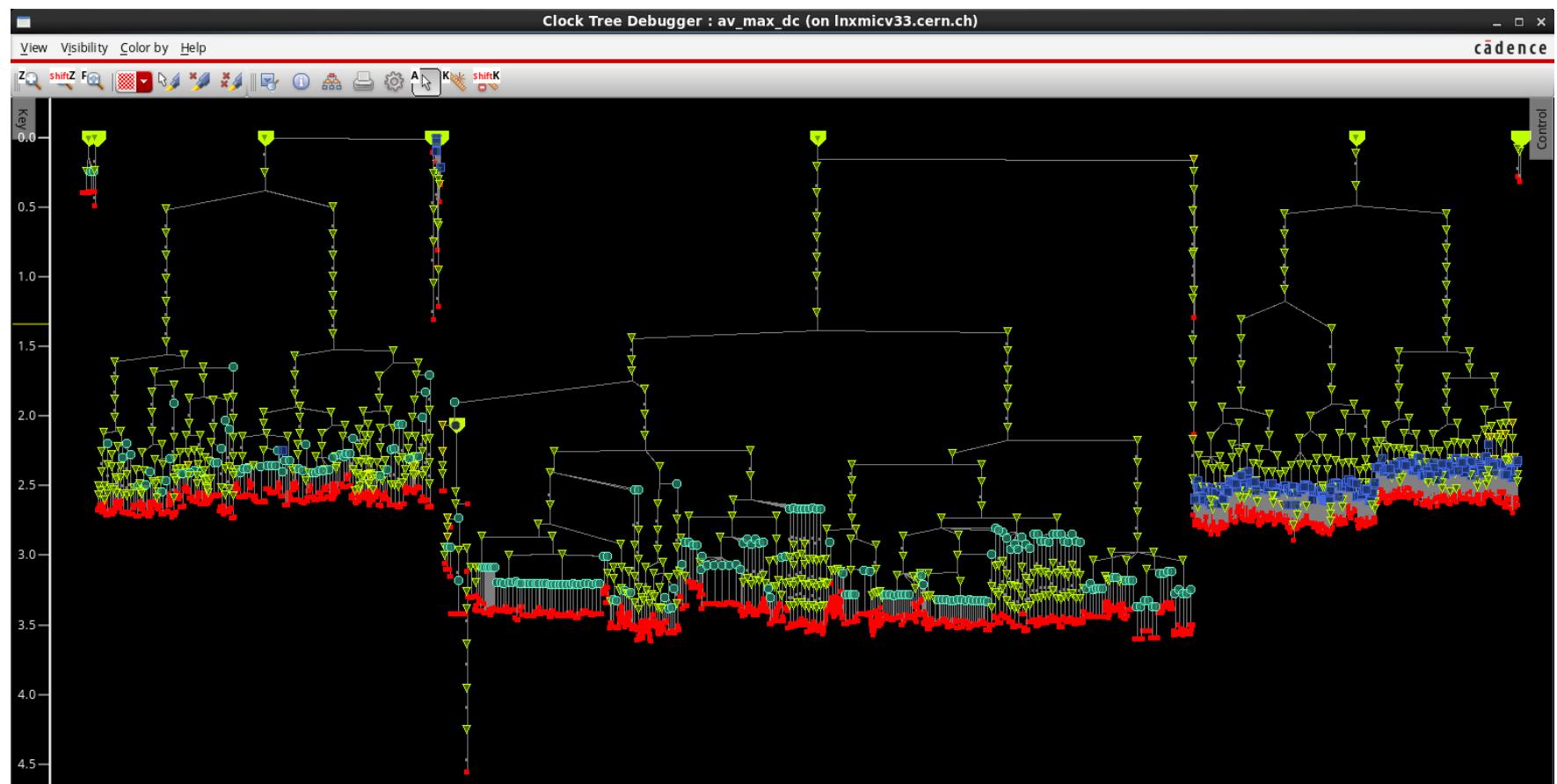

# Arbre d'horloge et IR-drop

L'IR-drop peut introduire des variations de temps de Setup et Hold

(problème dans SRAM de ECOND)

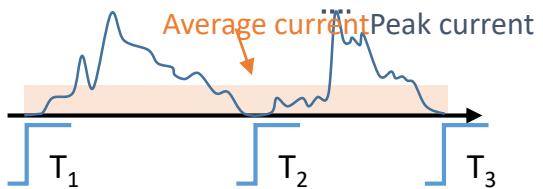

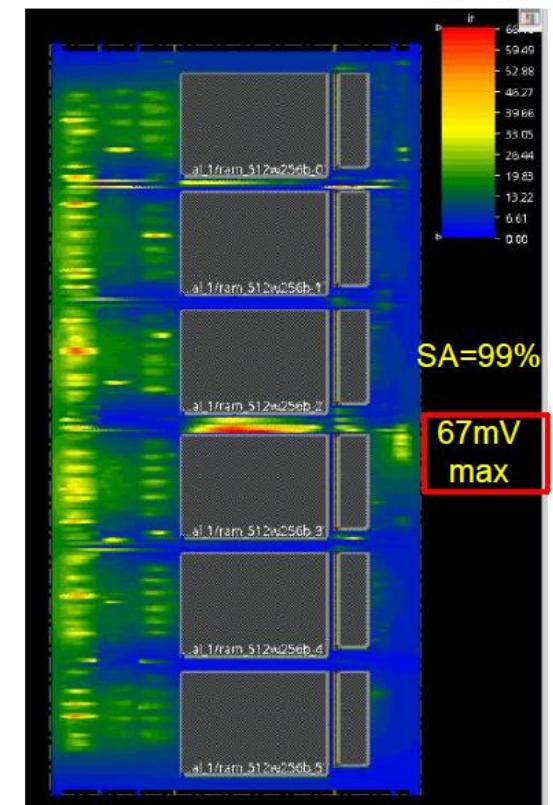

# IR drop dynamique

- Simuler en fonction de l'activité

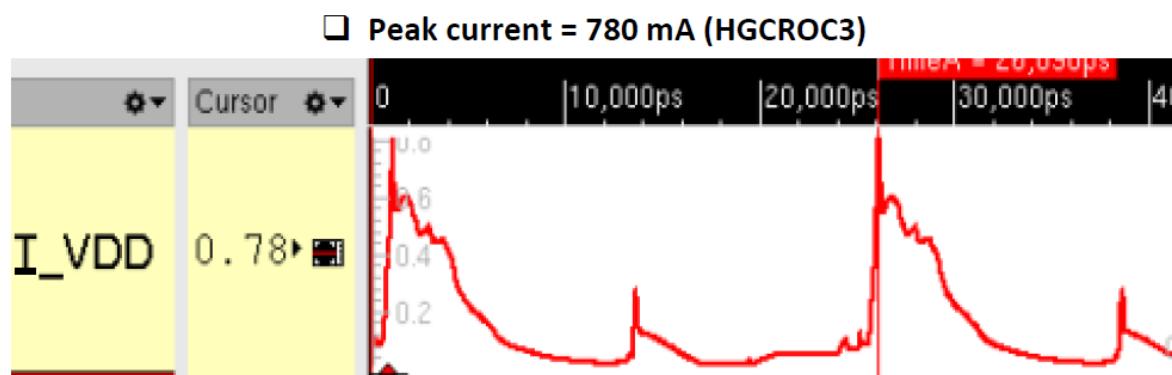

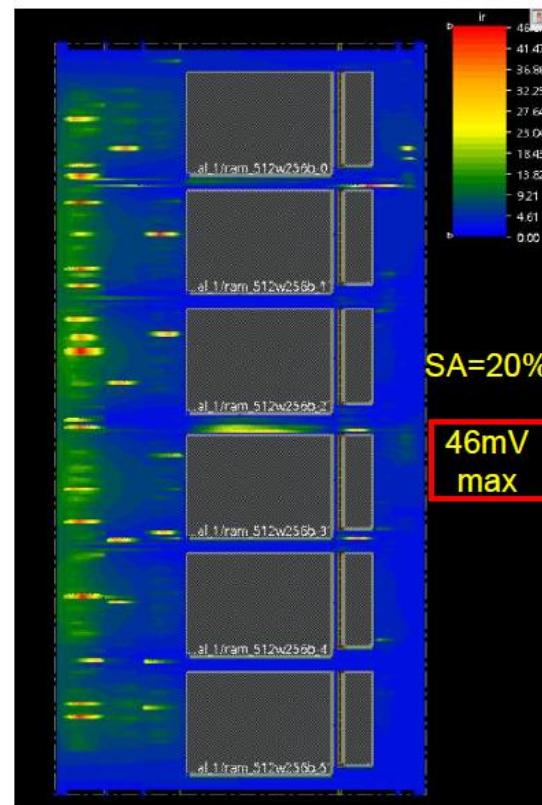

# Signoff Analysis: Dynamic Current & Parasitic

## Voltage probing on-package

Data Corruption caused by large dynamic current in combination with significant parasitic inductance

$$V = L \cdot \frac{dI}{dt}$$

Static assumption is not valid anymore

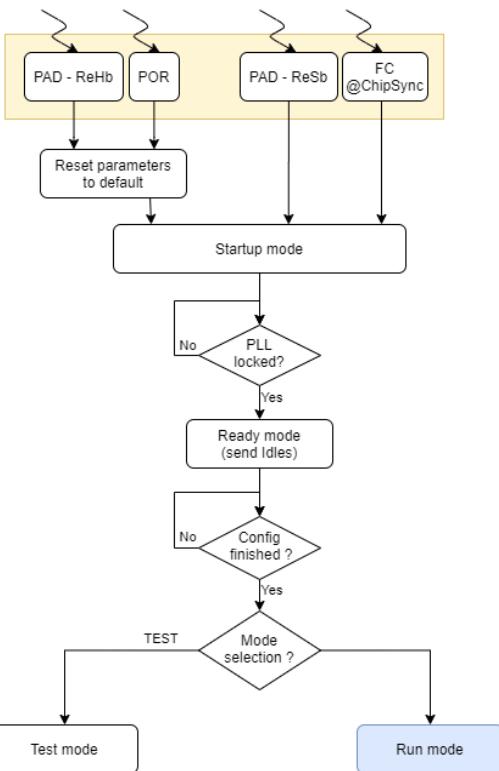

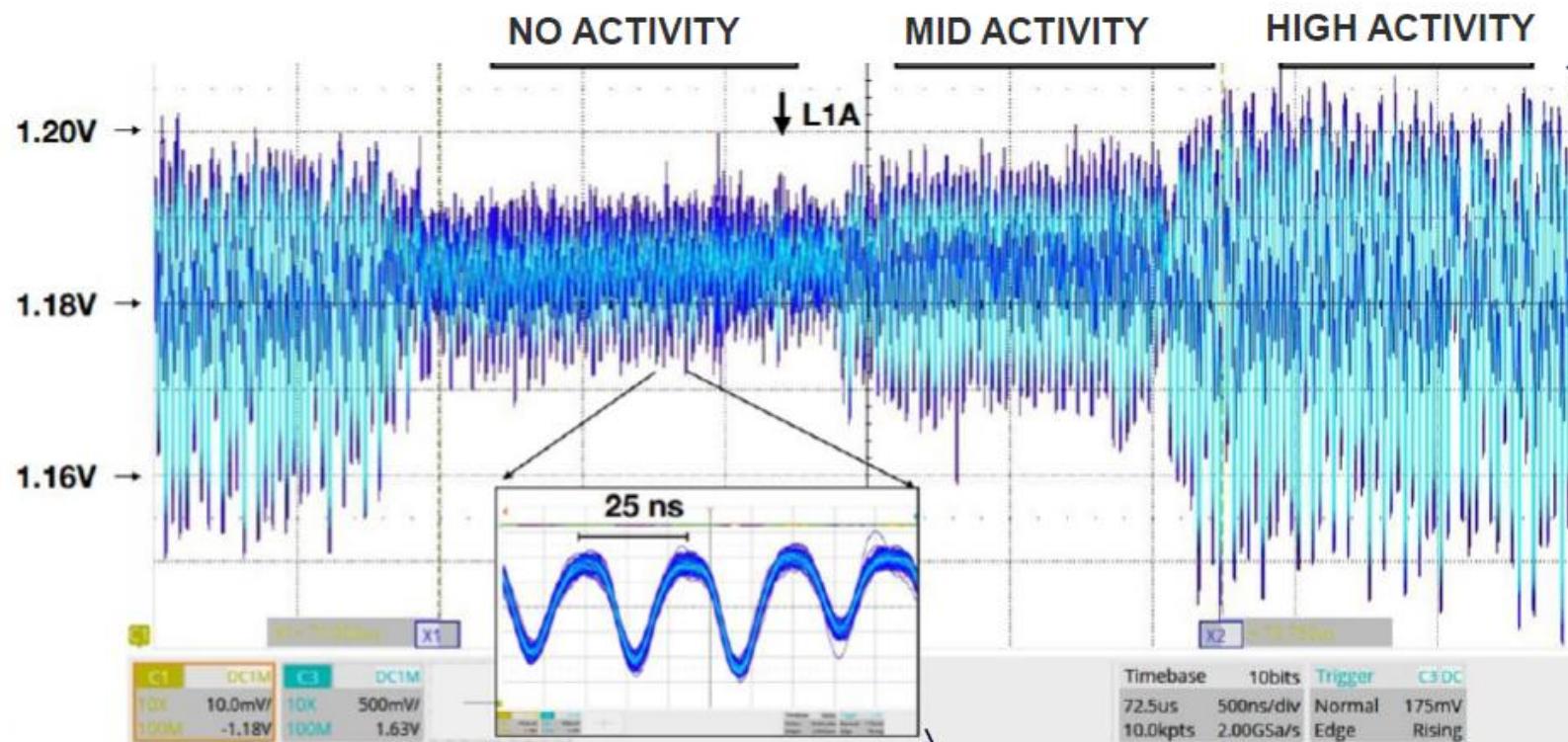

# Des ASICs purement numériques: LpGBT

## LpGBT Block Diagram

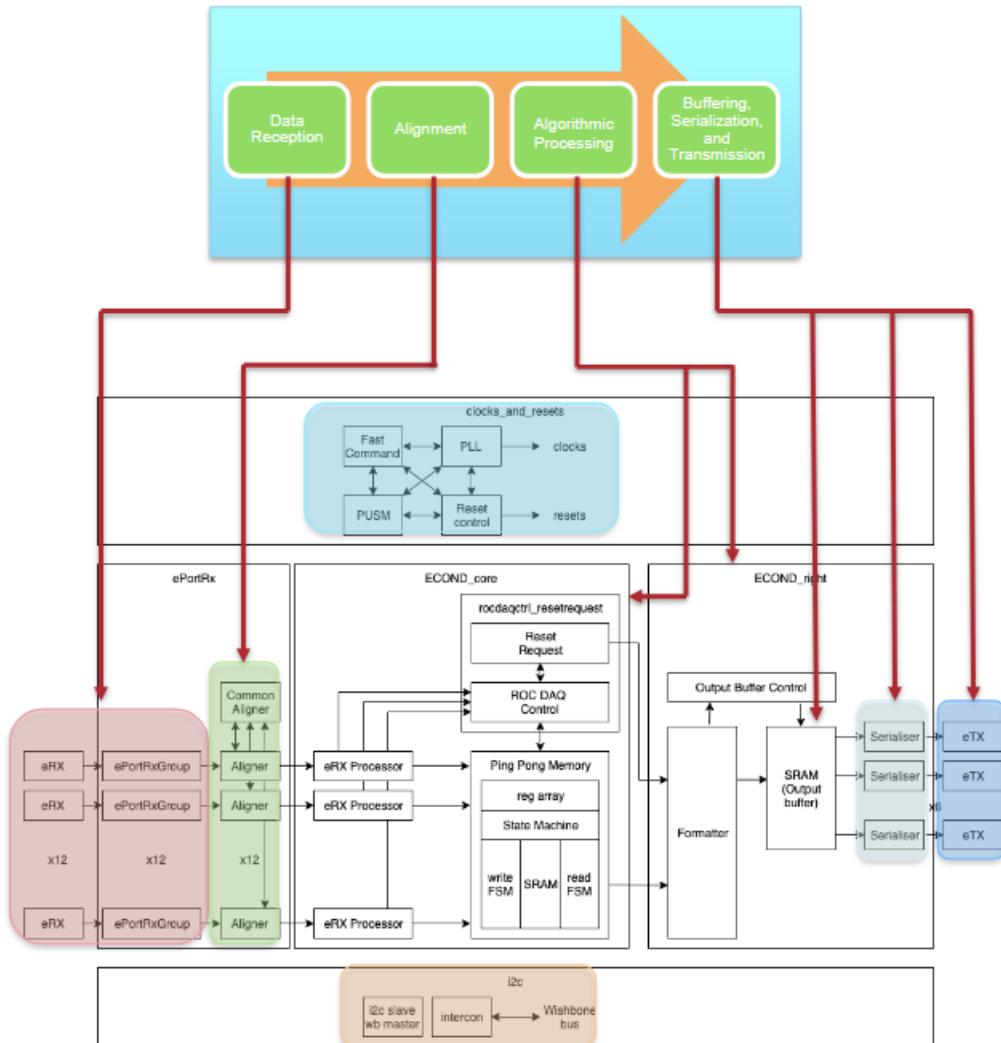

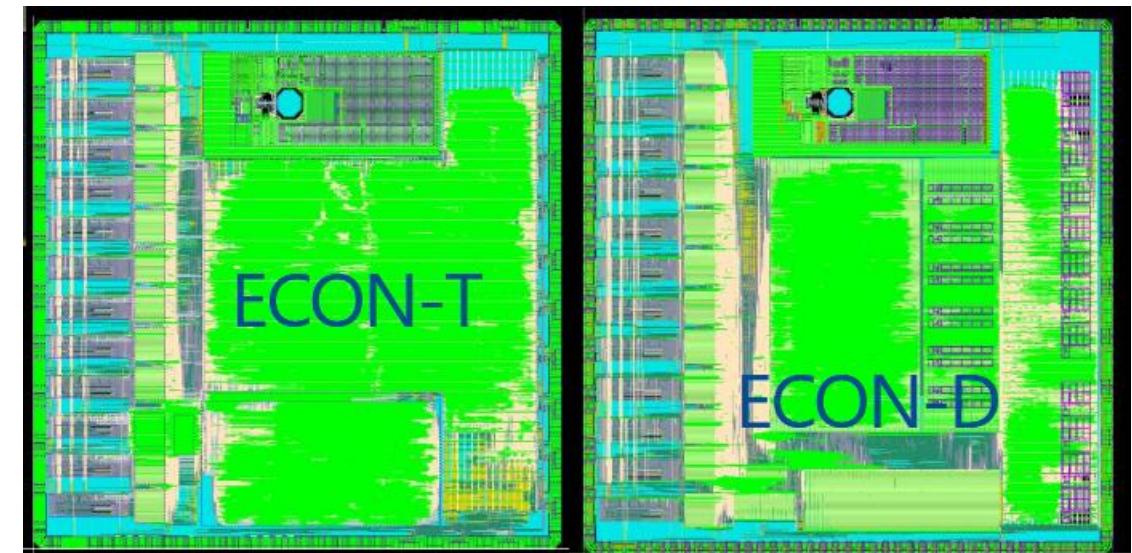

# Concentrator ASICs: CIC, ECON-D et ECON-T

Pré-traitement des données

- zero-suppress

- pré-traitement trigger data

ASIC vs FPGA

- radiation, nombres I/Os, puissance

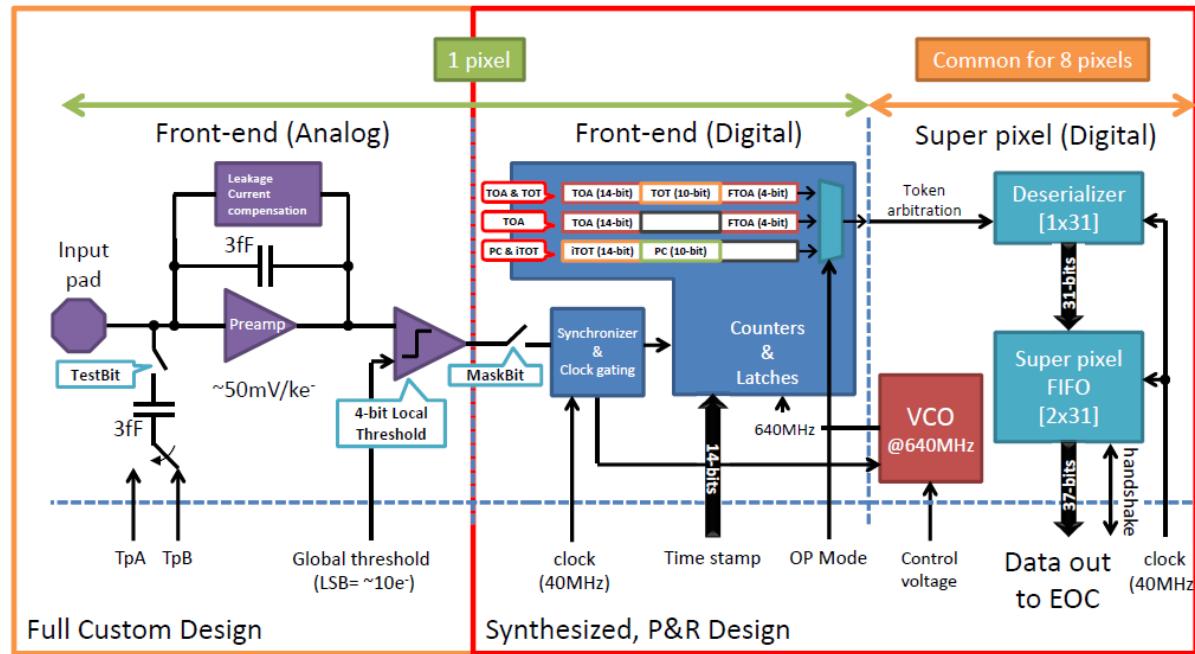

# Ou presque...

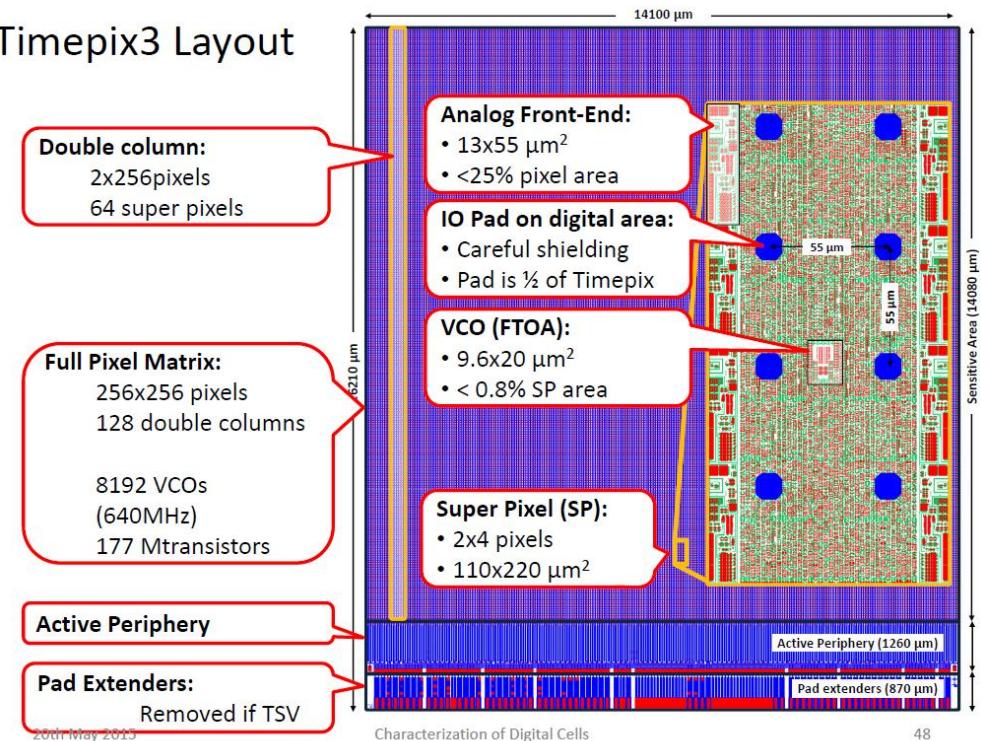

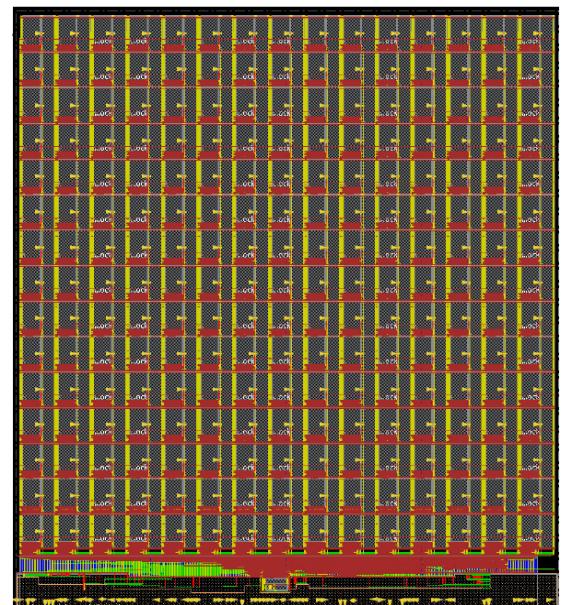

## Timepix3 Pixel Schematic

20th May 2015

Characterization of Digital Cells

45

## Timepix3 Layout

20th May 2015

Characterization of Digital Cells

48

# Electromagnetic compatibility (EMC-EMI)

- Coexistence analogique-numérique

- Couplages capacitifs, inductifs et d'impédances communes

- Il n'existe pas de masse parfaite! Attention au retour du courant!

- Bien étudier le substrat/PCB

# Analog-on-Top ou Digital-on-Top?

- Digital On Top:** outil fait les schémas et layouts automatiquement, à partir des codes RTL et contraintes données par le concepteur.

- Analog On Top:** schémas et layout faits manuellement par le concepteur pour assurer performance analogique

|                        | A                                                                                                                                | A/d                                                                                                                                                         | A/D                                                                                                               | D/A | D/a     | D |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----|---------|---|

| Methodology            | Analog on Top (AoT)                                                                                                              | Mixed-Signal on Top (MSoT)                                                                                                                                  | Digital on Top (DoT)                                                                                              |     |         |   |

| Design Flow            | Schematic-Driven                                                                                                                 |                                                                                                                                                             | Netlist-Driven                                                                                                    |     |         |   |

| Top level Connectivity | Schematic                                                                                                                        |                                                                                                                                                             | Verilog                                                                                                           |     | Verilog |   |

| Design Characteristics | <ul style="list-style-type: none"> <li>Top level is analog</li> <li>Standard cell digital designed in a digital flow</li> </ul>  | Analog blocks and standard cell digital mixed at the top level                                                                                              | <ul style="list-style-type: none"> <li>Top level is digital</li> <li>Analog designed in an analog flow</li> </ul> |     |         |   |

| Floorplanning          | Virtuoso floorplanner and Virtuoso Digital Implementation                                                                        | Virtuoso floorplanner and Innovus                                                                                                                           | Innovus                                                                                                           |     |         |   |

| Analog Content         | Main and Top Level                                                                                                               | Co-Designed                                                                                                                                                 | Separate Hierarchy                                                                                                |     |         |   |

| Digital Content        | Separate Hierarchy                                                                                                               | Co-Designed                                                                                                                                                 | Main and Top Level                                                                                                |     |         |   |

| Routing                | <ul style="list-style-type: none"> <li>VSR for top level and analog</li> <li>NR for routing within the digital blocks</li> </ul> | <ul style="list-style-type: none"> <li>VSR for analog blocks and NR for digital blocks</li> <li>Top level uses VSR for analog and NR for digital</li> </ul> | <ul style="list-style-type: none"> <li>Top level is digital</li> <li>Analog designed in an analog flow</li> </ul> |     |         |   |

| Chip Integration       | Virtuoso                                                                                                                         | Innovus                                                                                                                                                     | Innovus                                                                                                           |     |         |   |

| Signoff                | MSPS                                                                                                                             | Tempus                                                                                                                                                      | Tempus                                                                                                            |     |         |   |

| Chip Finishing         | Virtuoso                                                                                                                         | Virtuoso                                                                                                                                                    | Virtuoso/Innovus                                                                                                  |     |         |   |

# En conclusion

# Principales évolutions en micro-électronique

- **Circuits front-end de + en + proches du détecteur**

- Peut intégrer le détecteur

- Beaucoup de voies et peu de connectique

- Chips autonomes (sans composant discret autour)

- **Circuit intégrant de + en + le back-end**

- Conversion interne (ADC, TDC)

- Mémorisation intégrée (SCA, RAM)

- Slow control intégré (chargement de registres internes)

- **Contraintes :**

- Réduire la dissipation

- Gérer les couplages analogique/numérique (CEM)

- **Défis pour chips de trackers et calorimétrie**

- Mesure de temps à 10 ps

- Augmentation du numérique et évolution des outils de vérifications du numérique

- Maintenir la performance de l'analogique

- Performance au niveau système (couplages, bruit numérique)

- Accès aux technologies plus fines (coûts) et pérennité

- Organisationnel, masse critique

# En bref!

- Les chips de demain ne seront plus faits par des ingénieurs isolés... ni même par des groupes isolés

- Métiers davantage **diversifiés** et **spécialisés**

- **Analogique**: front-end, ADC, TDC, PLL, Serializers et Desérializers

- **Digital**, code, back-end

- **Intégrateur**: analogique et numérique

- **Vérification**, simulation comportementale

- L'institut fournit l'infrastructure

- Outils, machine (CC-IN2P3)

- Techno, NDA

- Bibliothèque partagée d'IP

We can do so much more!