# Application of FPGA devices in experimental high-energy physics

Yun-Tsung Lai

**KEK IPNS**

ytlai@post.kek.jp

Seminar @ CPPM Marseille

14th Mar, 2025

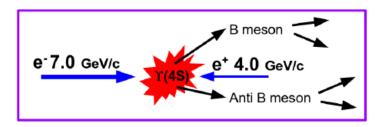

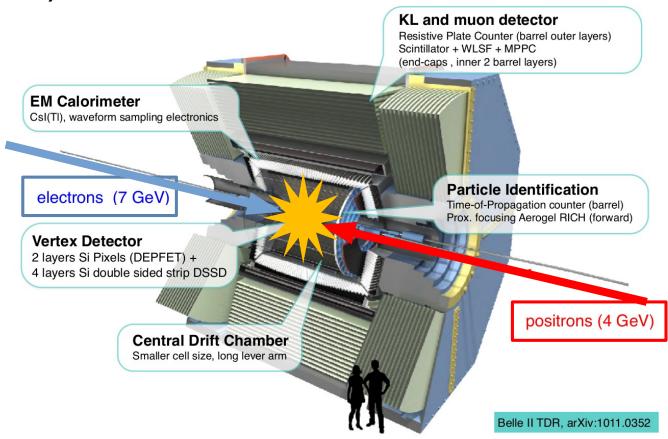

#### **SuperKEKB**

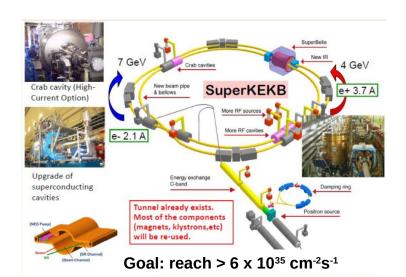

- SuperKEKB: Upgraded from KEKB.

- More than 30 times larger luminosity of KEKB with nano beam scheme.

- Asymmetric energy collider:

- 7.0 GeV e<sup>-</sup> and 4.0 GeV e<sup>+</sup> for Y(4S) → BB.

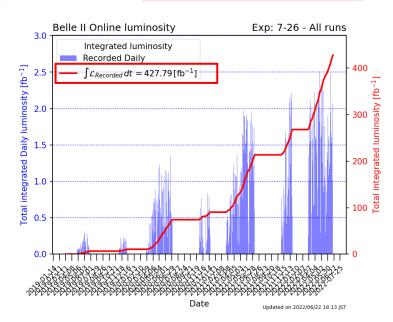

- · Luminosity achievement:

- L<sub>peak</sub> = 4.65 x 10<sup>34</sup> cm<sup>-2</sup>s<sup>-1</sup>.

World record. ~Two times of KEKB record with much smaller beam current.

- $L_{int} = \sim 427 \text{ fb}^{-1} \text{ up to Jun. } 2022.$

- Resumed beam collision in 2024 with PXD full installation.

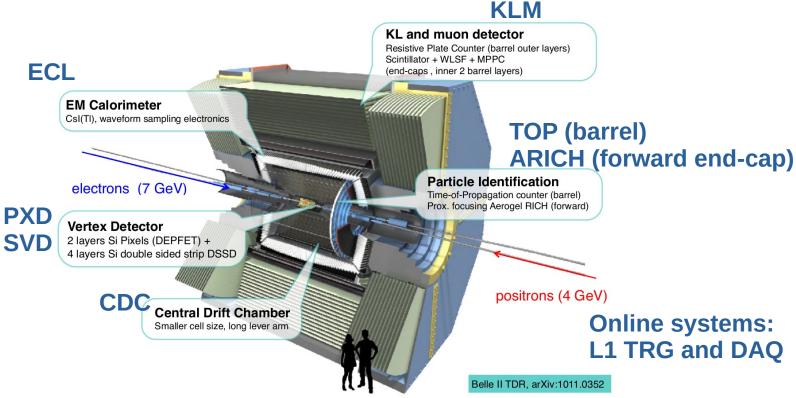

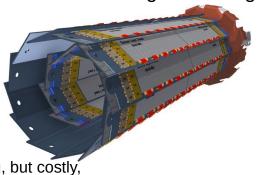

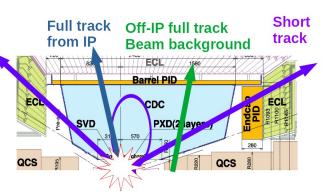

#### Belle II

Belle II: Newly-designed sub-detectors set to improve detection performance.

- Physics target of Belle II:

- Rare B, τ, charm physics, Dark Matter search, CP Violation.

- Requirement for data taking:

- High L1 trigger rate (~30 kHz), high background, and large event size.

#### Data taking in HEP

- First, let's paint a picture about what is going on during the experiment.

- Electronics (7 GeV) and Positron (4 GeV) are collided with high rate: luminosity

- O(10 kHz)

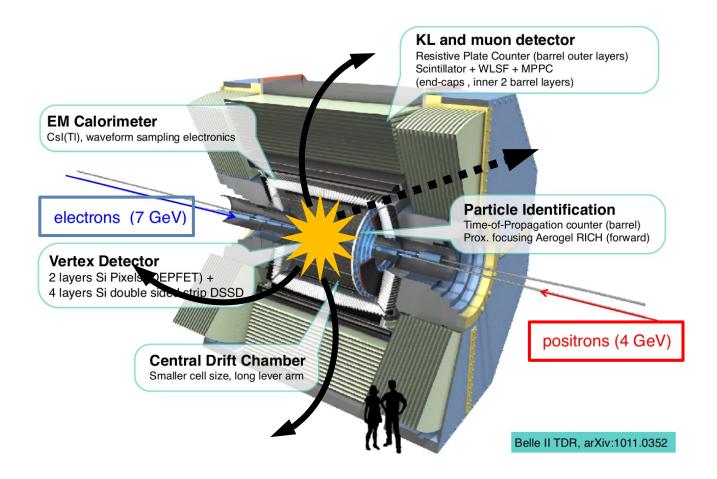

### Data taking in HEP (cont'd)

- Collision will produce some kinds of rare particles, then they will decay immediately (O(ps)).

- B meson, D meson, τ lepton, or even Dark Matter particles.

- Then decayed particles will fly out of the detectors with close to the speed of light.

### Data taking in HEP (cont'd)

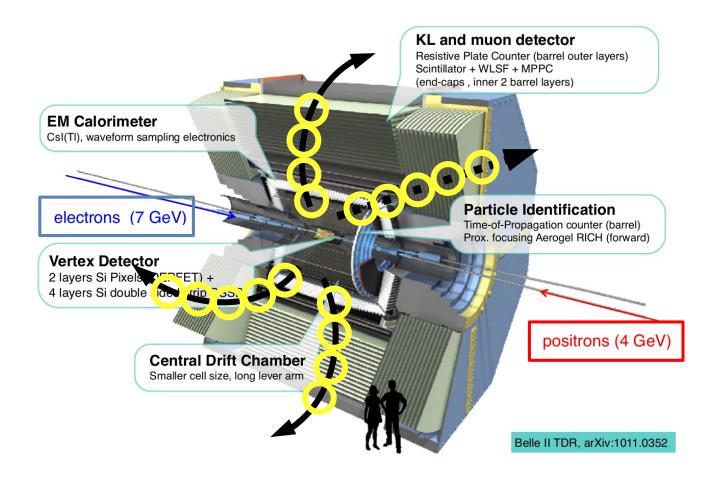

- There are many different types of detectors to capture different types of particles

- Crystal, PMT, plastic scintillator, sense wire, silicon, ......

- Signal is generated in O(10~100 ns) after the particles flies through.

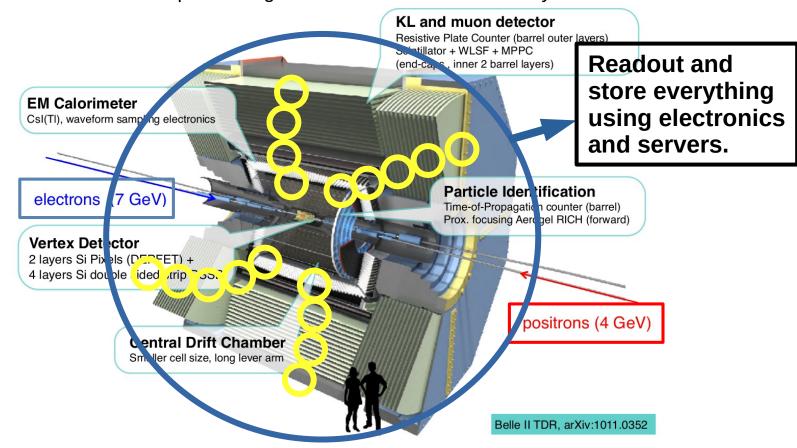

#### Data taking in HEP (cont'd)

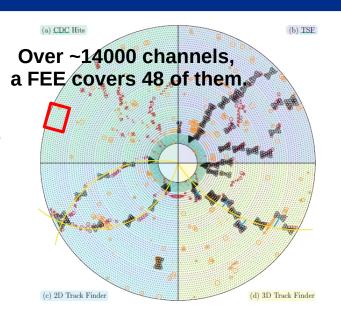

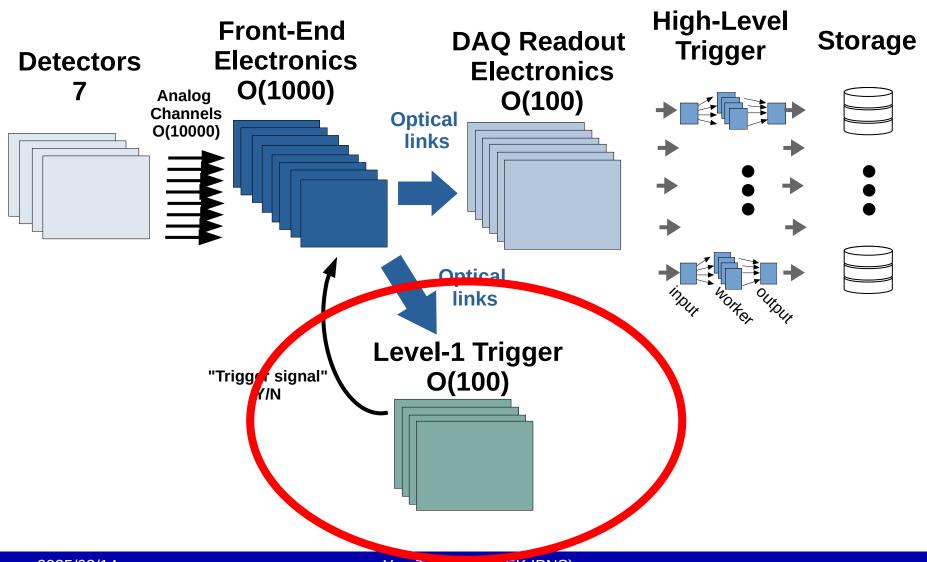

- For all the signals from the detectors, the number of channels is O(10000).

- We will readout and store them by using electronics system and computing servers.

- "Data acquisition" (DAQ).

- Fast data collection and processing in real-time and limited latency.

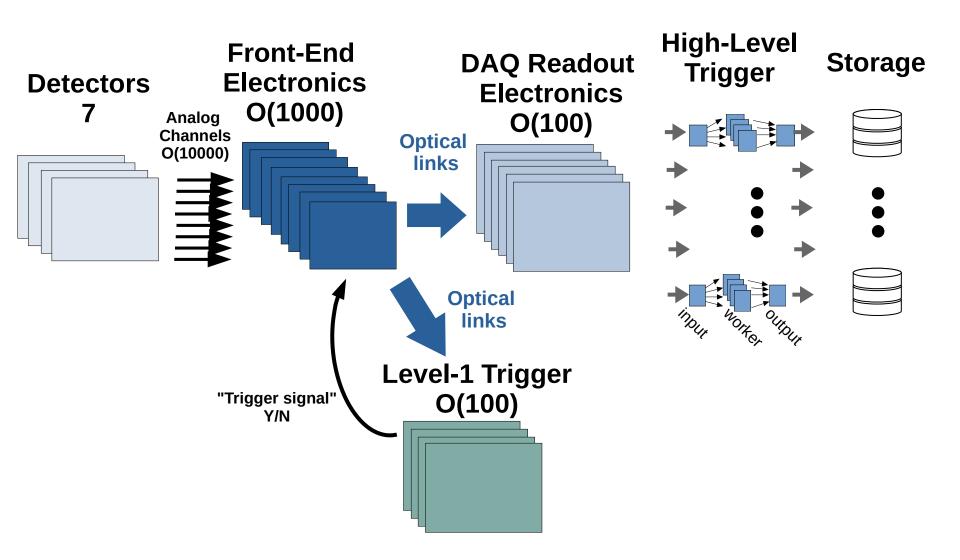

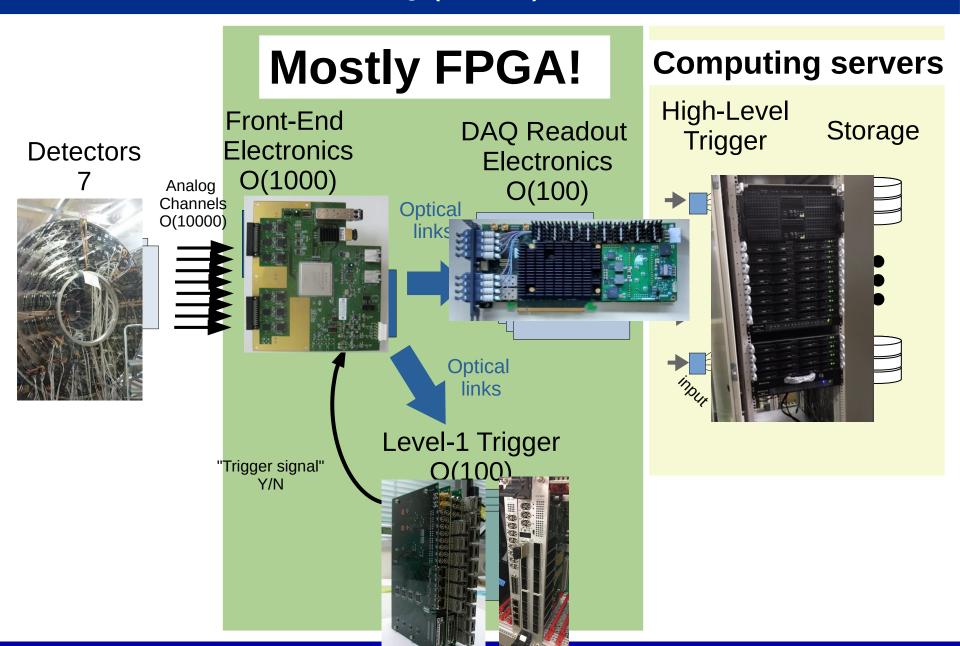

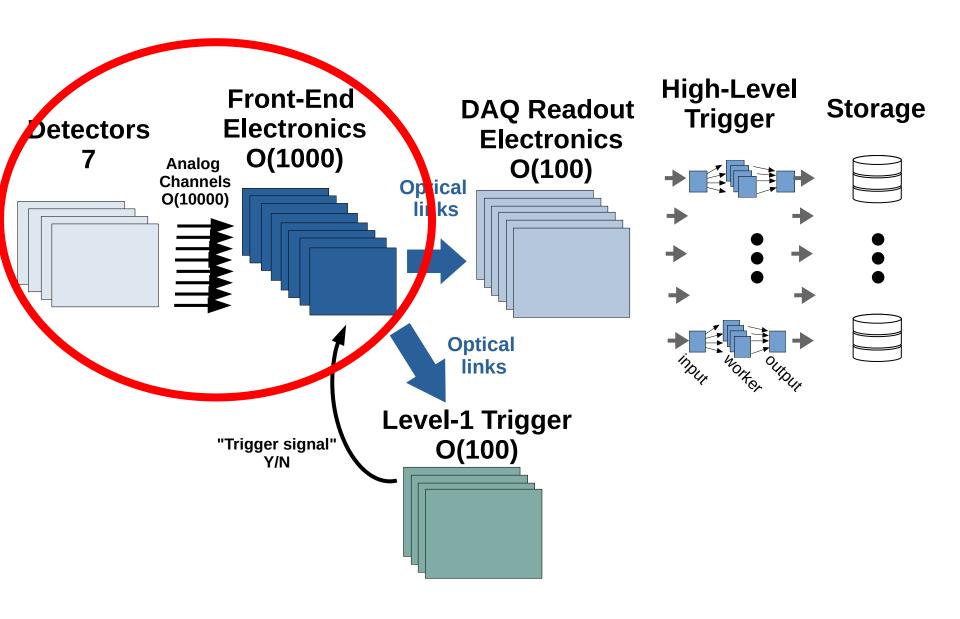

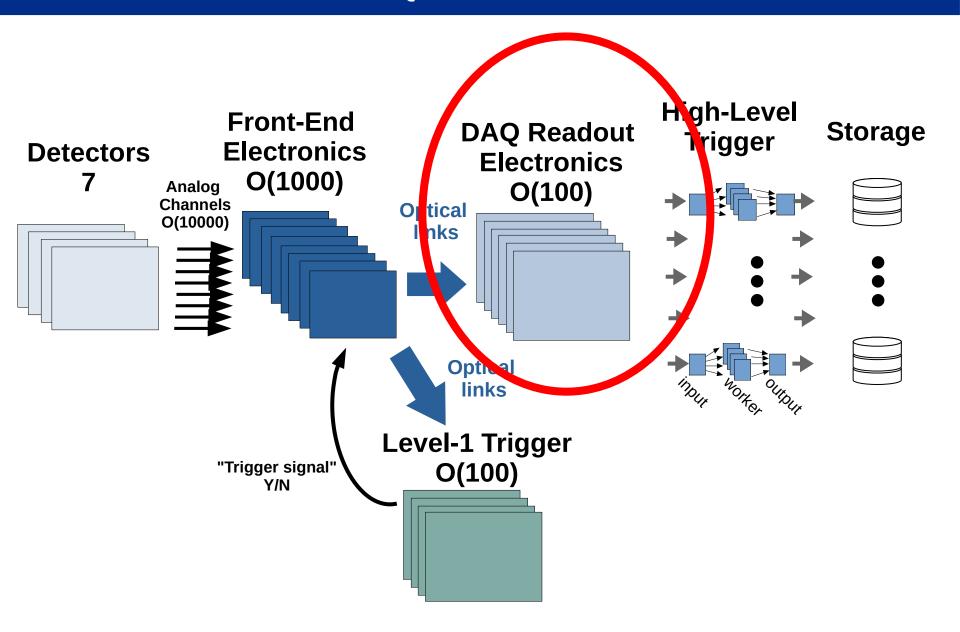

#### Data flow in Belle II DAQ

### Data flow in Belle II DAQ (cont'd)

roung Lai (KEK IPNS)

2025/03/14

#### **FPGA**

- FPGA: Field-Programmable-Gate-Array

- Configurable integrated circuit

- Array of programmable logic cells interconnected to each other. Based on the user's design using Hardware Description Language (HDL), the logic cells' array will be configured to realize different digitized logics.

- · Programmable: better flexibility.

- High speed, small latency.

- Application in industry: Aerospace, military, telecommunication, video/image processing, data center, etc.

- source: Intel

Adaptive Logic

Module (ALM)

Programmable

Routing Switch

DSP Block

- Why FPGA in HEP?

- Fast processing on large amount of data in real-time and limited latency.

- Flexibility on the processing design.

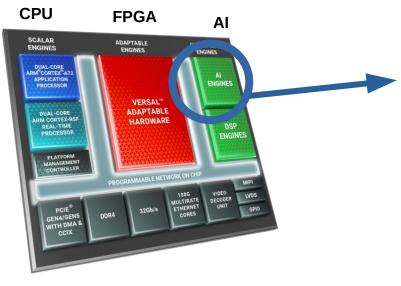

Versal series:

One of the latest product

from AMD Xilinx

for high-end application

**RAM Block**

source: AMD Xilinx

### Data flow in Belle II DAQ

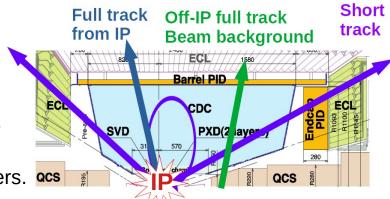

#### Detectors in Belle II

- Silicon Vertex Detector (SVD):

- double-sided silicon-strip

- Precise charged tracking.

- Pixel Detector (PXD):

- Pixelated DEPFET sensors

- Precise charged tracking.

- Central Drift Chamber (CDC):

- Wire chamber with ionization gas

- Precise charged tracking.

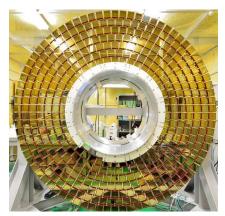

Electromagnetic Calorimeter (ECL):

so usually at the inner-most region.

- Array of CsI(Tl) crystal with PMT

- For electronics and photon.

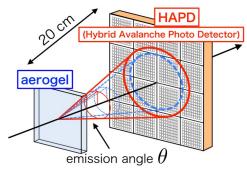

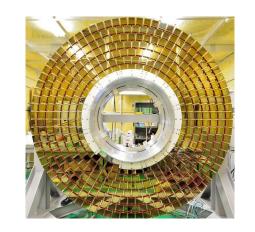

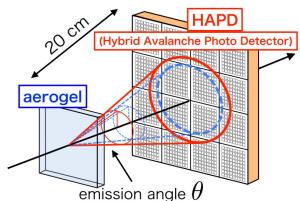

- Aerogel Ring Image Cherenkov Counter (ARICH):

- For hadron identification.

#### Front-End Electornics

- Front-End Electronics (FEE):

- Readout the analog signals from detectors, and record the digitized signal.

- A FEE receives a part of channels of an entire detector.

- Near collision: Rad-hardness is critical.

- For different types of the detector sensors:

- Sense wire, crystal+PMT, semiconductor, etc

- Their analog responses are also different.

- The design of FEE is hence dedicated.

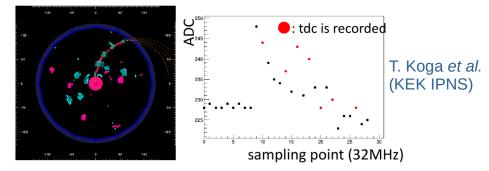

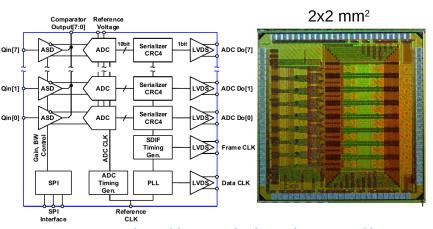

#### • CDC:

- ADC: custom designed ASIC.

- Amp, ADC, shaping, TDC, .

- Xilinx Virtex-5 FPGA for digital signal processing.

- Zero suppression.

- Output to downstream: SFP and QSFP modules with FPGA MGT.

Xilinx Virtex-5

#### Single channel

From t Chamber Analog buffer BLR-S To TDC To Trigger Vref

2.5x2.5 mm<sup>2</sup>

NIM A 735 (2014) 193-197

**ASIC: CMOS 65nm**

### Data flow in Belle II DAQ

### DAQ readout board

- Readout: receives data from O(10)~O(100) of FEE via optical links, performs event building, and transfer data from readout board (FPGA) to server (PC).

- Possible options for FPGA → PC:

source: Wiki

**GbE**

source: Intel

PCI-Express

**VME**

source: Wiki

source: Wiki

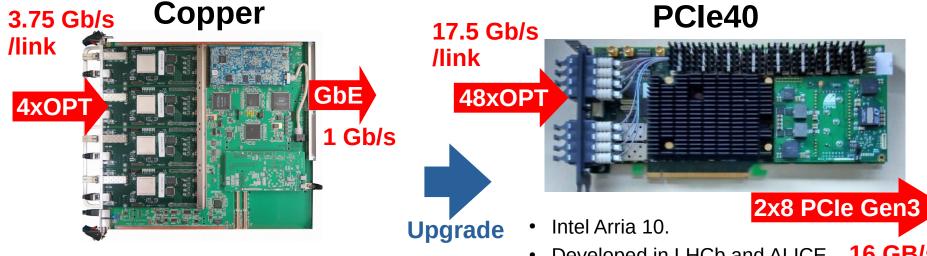

#### DAQ readout board in Belle II

- PCI-Express is the popular nowadays.

- The PCIe40 board was newly installed in Belle II in 2023.

- ALICE and LHCb at the LHC have been using it.

- The upgrade project was carried out with collaborating KEK (Japan) and IJCLab-Orsay (France).

- 4 Xilinx Virtex-5 receiver boards.

- PrPMC: data procession, pre event building.

- In total **203 coppers** were used in Belle II.

- 203 x 6 daughter boards.

- Developed in LHCb and ALICE. 16 GB/s

- 48 optical links.

- 2x8 PCIe Gen3.

- In total **21 PCle40 boards** are used in Belle II.

### Data flow in Belle II DAQ

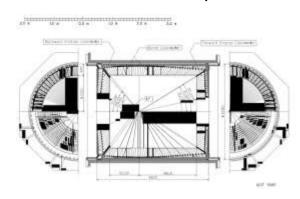

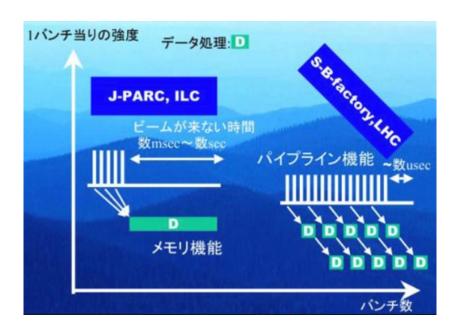

#### L1 trigger

- Provide L1 trigger signal to DAQ using FPGA chips for real-time processing on detector raw data within limited latency (~5 μs).

- Why L1?

- Buffer storage are not enough for all data due to high event rate and short bunch spacing in collider experiment.

- But hardware-based trigger system design is complicated and costly.

- Some of the experiments are based on trigger-less streaming DAQ: LHCb, ILC, nuclear experiments, etc.

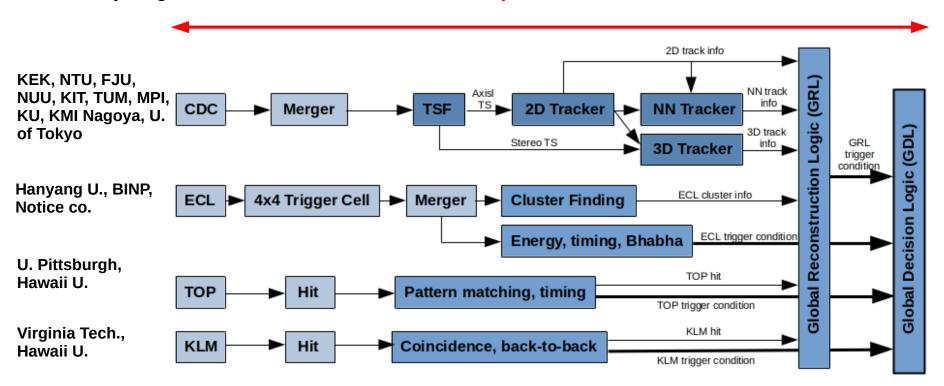

#### Belle II L1 trigger

- 4 sub-trigger systems + 2 global trigger systems.

- Every block is FPGA boards with specific algorithm.

- Comprehensive trigger menu to select various kinds of physics events.

- Everything in this chain has to be finished in ~5 μs.

KEK, NTU, NCU

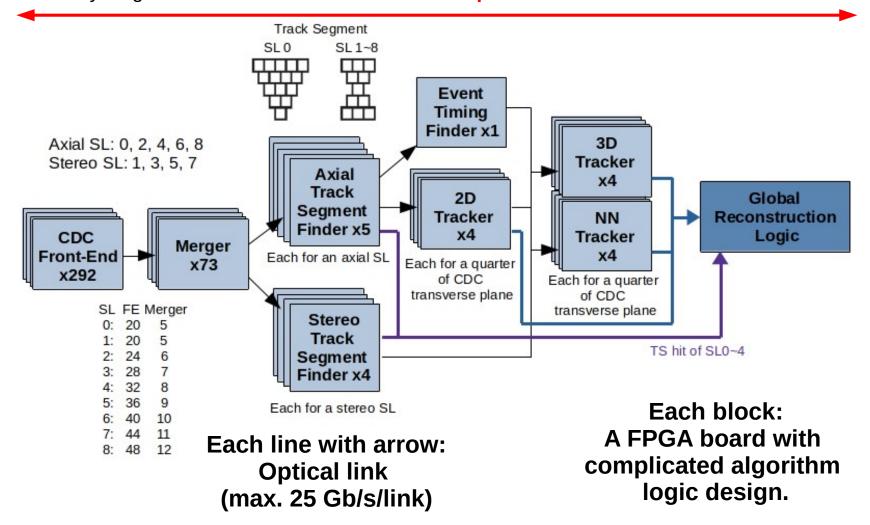

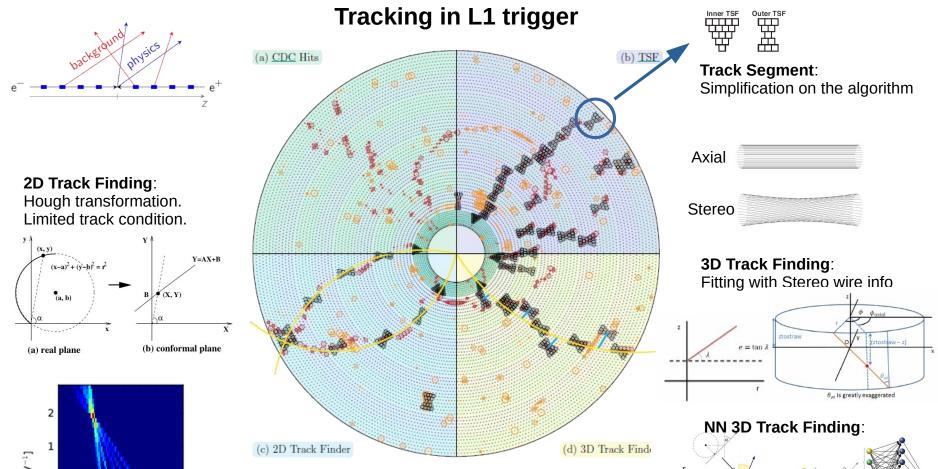

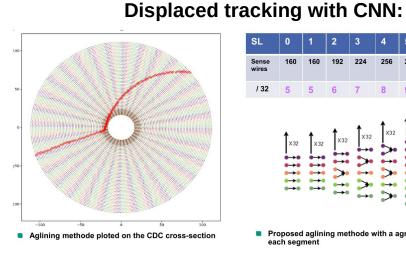

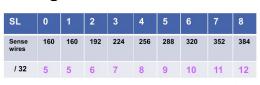

### Belle II CDC trigger

- A sub-trigger system in Belle II with one of the detector.

- Everything in this chain has to be finished in ~5 μs.

### FPGA in L1 trigger

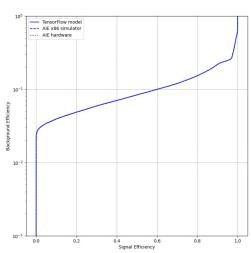

- For TRG purpose, complicated algorithm is implemented to process detector raw data in real-time. Utilization of machine-learning in the logic design became a trend recently.

- Strong FPGA with large resource: improve the logic itself, resolution of triggering, reduce the background rate, and perform everything within a latency limit.

#### Belle II UT3

Xilinx Virtex-6 xc6vhx380t, xc6vhx565t 11.2 Gbps with 64B/66B

#### Belle II UT4

Xilinx UltraScale XCVU080, XCVU160 25 Gbps with 64B/66B

#### **ATLAS Muon Trigger processor**

Xilinx UltraScale+ XCVU13P XCZU5EV GTH,GTY: 16.8 Gbps with 64B/66B

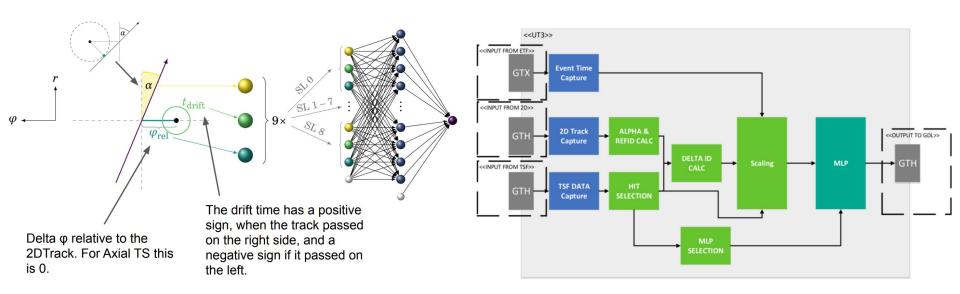

### L1 track trigger algorithms

The drift time has a positive sign, when the track passed

negative sign if it passed on

on the right side, and a

the left.

Delta  $\phi$  relative to the

is 0.

2DTrack. For Axial TS this

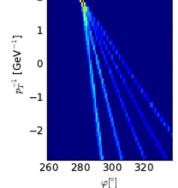

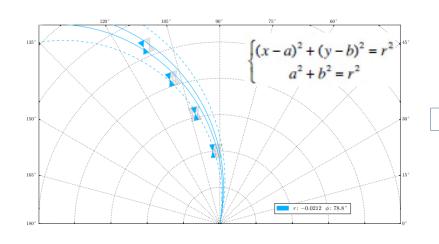

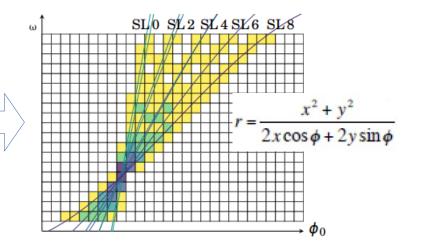

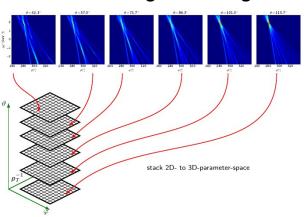

#### 2D tracker: Hough transformation

https://doi.org/10.6342/NTU201802022

T.-A. Sheng. Master thesis

Ping Ni. Master thesis

Full track: The charged tracks which go through all of the layers of CDC.

• 2D algorithm: Hough transformation.

- Assuming a circle.

- TS from 5 Axial SL are transferred into 5 lines in the conformal plane.

- Find the peak, which corresponds to track parameters.

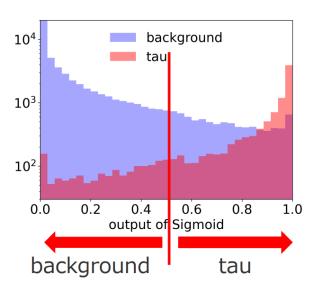

#### tau event trigger: NN

- In L1 trigger, not only the particle information from detector (charged track), but also the "physics event type" can be determined by ML in FPGA.

- A very advanced logic in L1 trigger.

- ML tau trigger:

- Input the position and energy information of clusters to a Neural Network, and determine if it is a tau event or not.

- A kind of topological application.

- Based on hls4ml.

- Validated and will be implemented in 2024 runs.

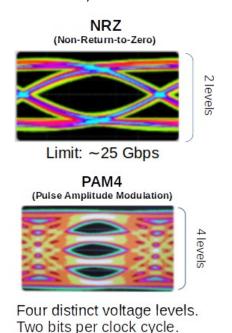

#### Toward the future: Versal ACAP

- Our group is targeting on using the Xilinx Versal ACAP for future electronics device's R&D. Now we plan to use Versal for L1 Trigger, DAQ or HLT purpose.

- The features of different Versal series ACAP:

- Al engine, DPU: stronger computing engine for ML.

- High Bandwidth Memory (HBM).

- Larger number of cells + High transmission bandwidth.

- PAM4, PCIe Gen5.

source: AMD Xilinx

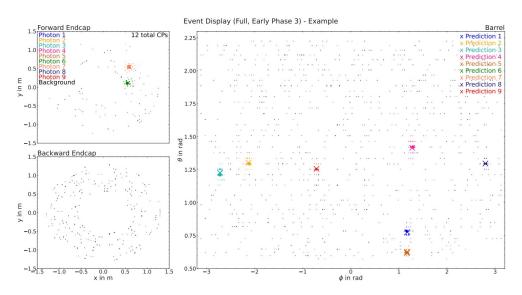

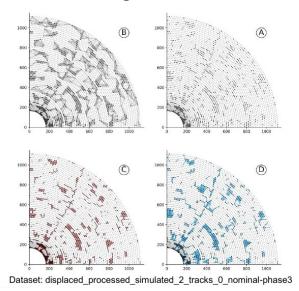

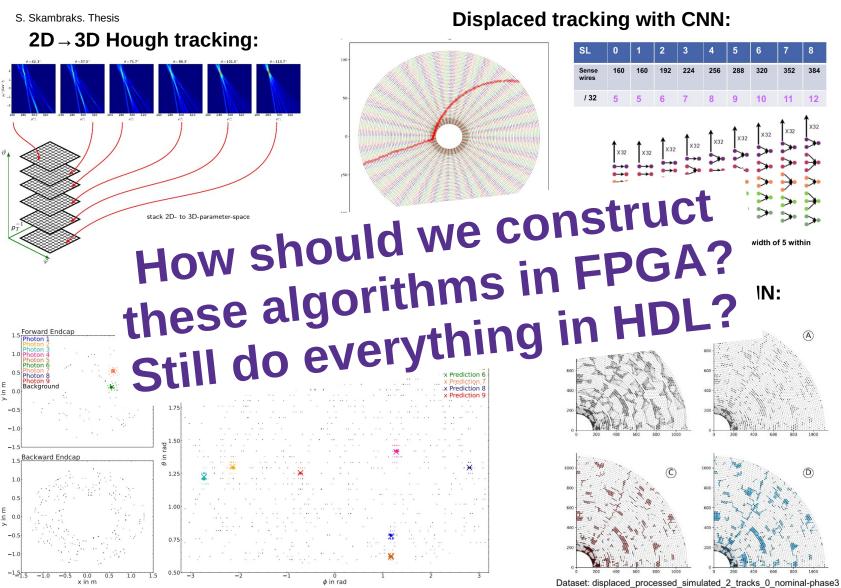

### New ideas for L1 trigger

S. Skambraks. Thesis

#### **2D** → **3D** Hough tracking:

Proposed aglining methode with a agning width of 5 within

#### **ECL clustering with GNN:**

#### **Tracking with GNN:**

### New ideas for L1 trigger

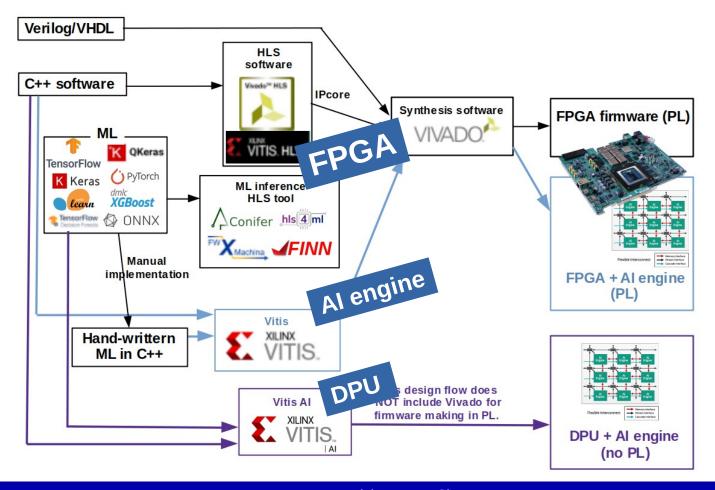

### Algorithm development: HDL, HLS, ML, Al engine

- Other than writing HDL, we have more options to construct our algorithms: HLS, ML/AI, etc.

- We have been trying to go through each path in this map, and to build up a database of technical knowledge.

- To support our experimental colleagues by proper documentations and hand-on lectures.

- We are mostly ready.

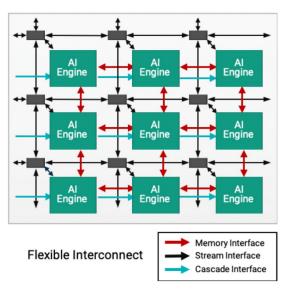

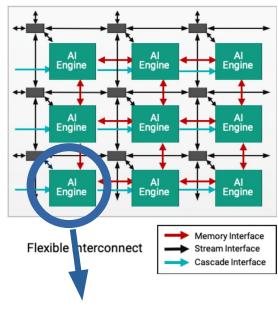

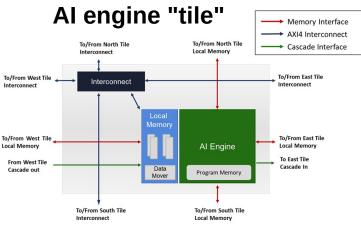

#### Versal AI engine

#### **Versal ACAP**

- Computation acceleration engine of Versal ACAP.

- Embedded processor of FPGA.

- High bandwith between FPGA and AI engine.

- C programmable.

- · High precision.

- No quantization loss on ML.

- Low latency.

#### **Versal AI engine**

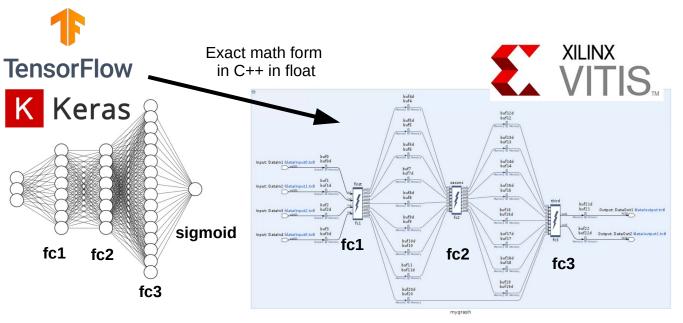

### Versal AI engine: ML inplementation

- We have been studying on the utilization of AI engine for the future application purpose.

- A NN model is built by Keras. 3 inputs → 3 hidden layers (8,8,16) → 1 output with sigmoid.

- Coding in C++ in Xilinx Vitis software.

- Everything for AI engine is in C++ and single-precision floating point.

- No quantization loss.

- Latency: ~3 μs.

#### Summary

- In the field of experimental particle physics, we utilize FPGA device to process high-rate data from detector in real-time in many different aspects. Our research group is working the R&D of various kinds of FPGA devices.

- Front-End Electronics: Interface to analog signals with using manual ASIC.

- DAQ: Data collection and transfer to PC via GbE, PCIe, etc.

- Trigger: Real-time physics algorithms in FPGA within limited latency based on different methods: HLS, ML, etc.

- Regarding the prospect for upgarde, we also have a project based on fundamental investigation on the Xilinx Versal device.

## **Backup**

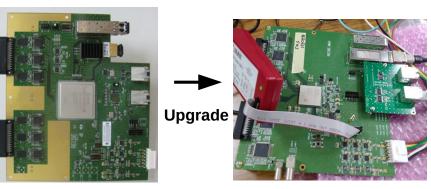

#### Considerations for FEE design/upgrade

- Newer FPGA chip: More resource for data processing and larger data output bandwidth.

- Usually, the FEE boards are close to collision: radiation damage as "Single-Event-Upset".

- Radiation hardness is important for all the chips: FPGA, ASIC, optical modules, etc.

- Hence, FPGA in FEE is usually not very strong one.

- We can also choose to pull down all the channels, but number of cables will be huge.

- ASIC: Improve the performance, precision and reduce the "cross-talk noise".

- Largely affects tracking performance

Xilinx Virtex-5 Xilinx Kintex-7

### Different design of system: FEE + Merger

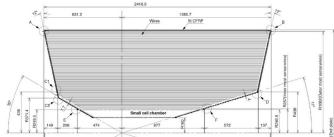

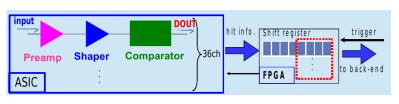

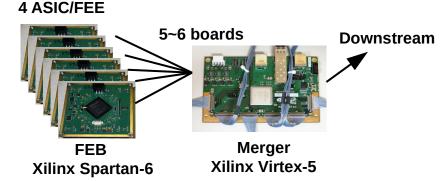

- Belle II ARICH detector:

- Cherenkov ring image produced by the aerogel.

- FEE + Merger design

- 1 ASIC: 36 ch

- 1 FEE: 4 ASIC

- 1 Merger: 5~6 FEE

- Overall: 72 Mergers, 420 FEEs

ASIC (36ch) design in FEE

- Merger is served as a master to:

- Configure/control/monitor the FEE.

- Merge FEE data with zero suppression: effectively reduce the data size and number of links.

### Different design of system: FEE + Merger (cont'd)

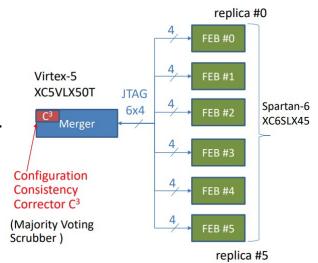

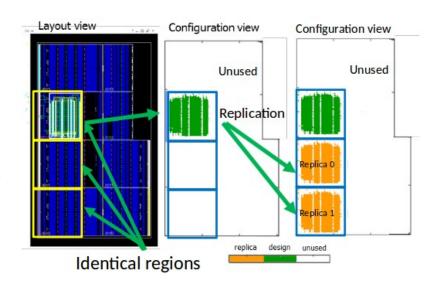

- Radiation damage on FPGA:

- Single-Event-Upset (SEU): Transistor signal is inverted while high-energy particle hits.

- One of the essential issue for electronics R&D of HEP.

- For Belle II ARICH, we expect to see 0.2/hr uncorrectable SEU error in peak luminosity.

R. Giordano et al., Instruments 2019, 3(4), 56

- A special SEU correction design in ARICH:

- Merger can readout the configuration frame of each FEE, and do majority voting on all.

- Voting can find the redundant frame bit on which FEE.

- Repair it in real-time by partial reconfiguration.

- Does not require any manual operation.

- Better performance than the Xilinx IPcore.

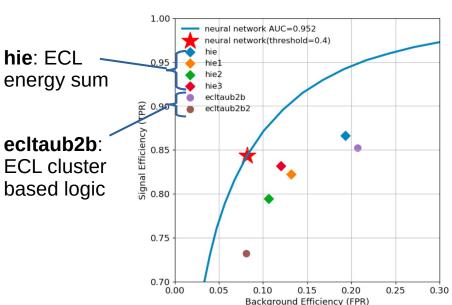

#### Conditions and requirements for TRG

- Requirements:

- Overall latency < 4.4 μs.</li>

- ~100% eff. for hadronic events.

- Max 30 kHz @ 8\*10<sup>35</sup> cm<sup>-2</sup>s<sup>-1</sup>

- Timing precision: < 10 ns</li>

- Event separation: 500 ns

- Physics processes in interest:

Examples of technical challenges so far:

- Low-multiplicity trigger mainly based on ECL, but contamination from noise, beam bkg or Bhabha.

- Energy trigger with high eff. but high rate too.

- Injection bkg.

- Drawback of track trigger at endcap.

Phase2 Lum. Record

- High track trigger rate due to crosstalk noise.

- Latency budget due to transmission or complicated logics.

L1 trigger condition for Belle II: Depend on you physics target!

| Process     | C.S. (nb) | R@L=5.5x10 <sup>33</sup> (Hz) | R@L=8x10 <sup>35</sup> (Hz) | TRG logic                                             |

|-------------|-----------|-------------------------------|-----------------------------|-------------------------------------------------------|

| Upsilon(4S) | 1.2       | 6.6                           | 960                         | CDC 3trk(fff) ECL high energy(hie) ECL 4 clusters(c4) |

| Continuum   | 2.8       | 15.4                          | 2200                        |                                                       |

| μμ          | 0.8       | 4.4                           | 640                         | CDC 2trk(ffo)<br>etc                                  |

| ττ          | 0.8       | 4.4                           | 640                         |                                                       |

| Bhabha      | 44        | 242                           | 350 *                       | ECL Bhabha(bhabha,<br>3D bhabha)                      |

| γ-γ         | 2.4       | 13.2                          | 19 *                        |                                                       |

| Two photon  | 13        | 71.5                          | 10000                       | CDC 2trk(ffo)<br>etc                                  |

| Total       | 67        | 357.5                         | ~15000                      |                                                       |

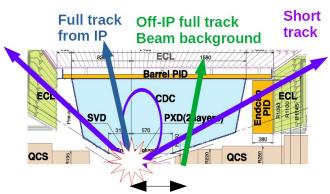

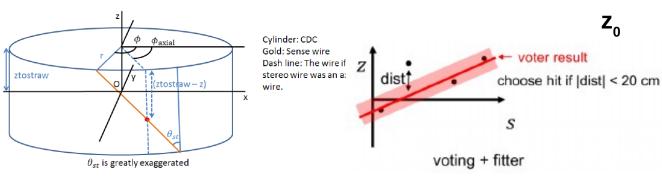

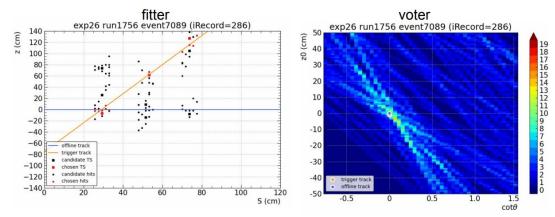

#### 3D tracker

- Purpose: find the longitudinal displacement of a track  $(z_0)$  to separate the off-IP track, e.g. beam background.

- Based on the 2D track, and perform fitting on the 4 stereo SL TS.

$\mathbf{Z}_{0}$

#### 3D tracker with NN

S. Neuhaus et al 2015 J. Phys.: Conf. Ser. 608 012052 Kai Lukas Unger et al 2023 J. Phys.: Conf. Ser. 2438 012056 F. Meggendorfer, DPG Conference 2021 Thesis: S. Skambraks, S. Pohl

- In addition to the conventional 3D tracker based on fitting method, Belle II has a Neural Network 3D tracker (NN) running in parallel in the system.

- Input the 2D tracker and stereo TS info

- Crossing angle, drift time,  $\varphi$  relative to 2D Track.

- Obtain  $z_0$  and  $\theta$ .

- NN is implemented in FPGA mainly with LUT.

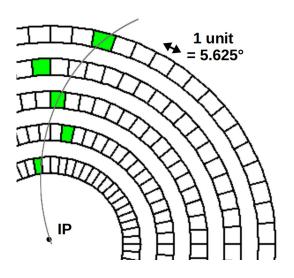

#### Short tracker

- The logic is implemented in part of the global trigger (GRL).

- Use the TS of inner 5 SL (3 axial, 2 stereo).

- Pattern recolonization over a 64 x 5 array. Simple design.

- Consider the resource of FPGA device.

- The logic is implemented as a LUT.

- Improve the angular acceptance of CDCTRG toward endcap.

- Also the curling-back tracks within the chamber: low-pt.

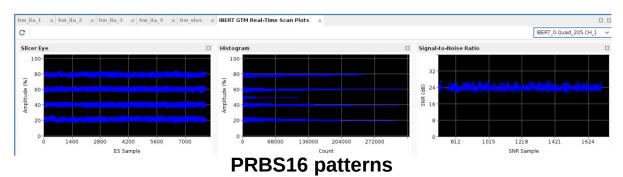

### PAM4 study of Versal

- We have successfully tested the real transmission with PAM4 and QSFPDD:

- QSFPDD-SR8 with MPO16, from FS company.

- 53.125 Gb/s x 16 lanes.

- Only this line rate is supported.

- 3-day BERT, Our self-designed protocol, PRBS16:

- BER of the worst lane: 9.0 x 10<sup>-14</sup>

- 16-lane combined BER: 6.7 x 10<sup>-15</sup>

- Latency: 210~240 ns

- Based on our experience, NRZ is usually O(10<sup>-16</sup>)

- This BER for PAM4 looksl acceptable.

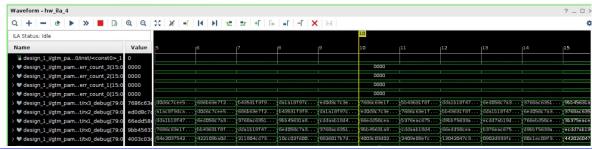

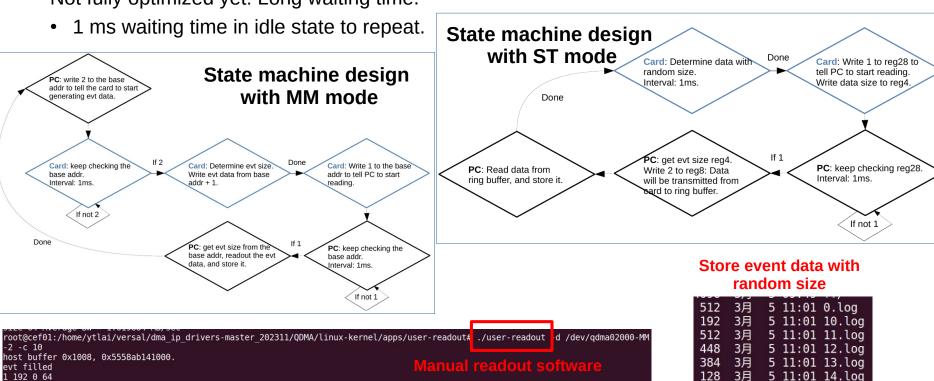

### PCIe study of Versal

- State machine of the readout protocol between PC and FPGA.

- Basically, handshake between PC and FPGA to know when is ready, what is data size, and when to take data.

- Random data size in the data generator.

- Not fully optimized yet: Long waiting time.

evt size:384 bytes

evt taking done

waiting...

waiting... waiting...

evt filled

128 0 64

5 11:01 15.log

5 11:01 16.log

5 11:01 17.log

5 11:01 18.log

5 11:01 19.log

5 11:01 1.log 5 11:01 20.log