## STATUS OF THE TRIGGERS AND TRIGGER PROCESSOR TESTS STATUS OF THE PHASE 1 ELECTRONICS AT LNL

ALAIN GOASDUFF - INFN LNL

# STATUS OF THE PHASE 1 ELECTRONIC @ LNL

#### RECENT UPGRADES ON THE SYSTEM

All LVPS have been moved to the new systems delivered by Saclay.

Improvement of the diagnostic on the array:

- Automatic monitoring and data logging of the boards, rates .... performed at the ggp\_server level

- Implementation of the slow control of the new ADCs board (S. Capra)

- Implementation of the decimation for the long traces capture: (D. Bazzacco)

- Allow to perform FT and check for low frequency noises (< 100 Hz to a few Hz)</li>

### TEST BENCH FOR THE DETECTOR LAB

VX2740 – 64 channels 2Vpp differential inputs – 16 bits

# STATUS OF THE TRIGGERS AND TRIGGER PROCESSOR TESTS

Istituto Nazionale di Fisica Nucleare Laboratori nazionali di Legnaro

#### **GTS ROOT ISSUE?**

Loss of events between the ROOT node and the Trigger Processor (idenpendantly of the TP) ???

This was **NOT** an issue of the GTS ROOT NODE ...

- GGPs have a local fifo able to store up to 8 events waiting for the GTS validation/rejection

- After a SETTABLE thresholds the backpressure flag (BF) is sent to GTS ROOT

- Once the BF is high → All the events coming to the ROOT are discarded, explaining the loss observed between the GGP GUI and TP monitor.

- The threshold was set in the SLC to 4 events since the GANIL campaign.

- We have modified the SLC to move the threshold to 7/8 events and recovered all the events at the TP

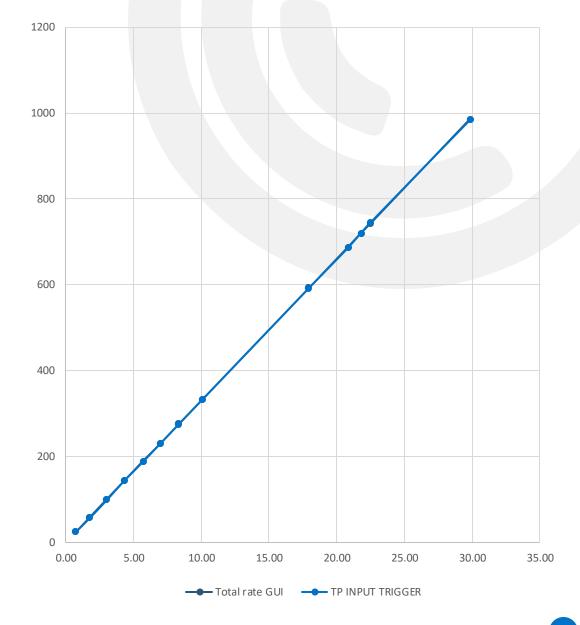

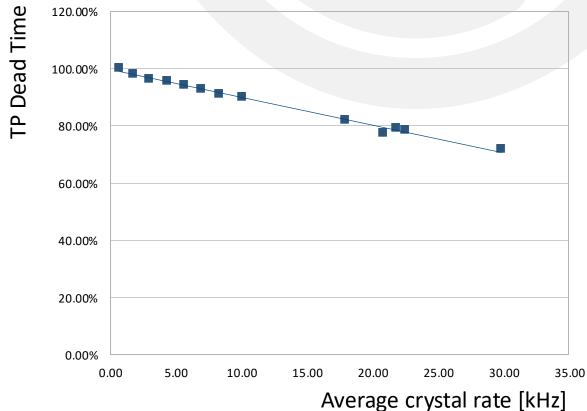

#### LIMITATIONS OF THE DEMONSTRATOR TP

Since the TP is performing time sorting and event reconstruction on the CPU -> limitation on the input rate

We have checked that the:

- GGP trigger request rate

- TP input rate

- Sorted trigger rate

Are consistent

The loss is happening between the sorted trigger and the sumbus trigger when the CPU is entering into play.

After this loss the rates are again consistent, i.e. the GGPs are seeing all the validations.

#### LIMITATIONS OF THE EXOGAM<sub>2</sub> TP

During the in-beam experiments we observed (AGATA-PRISMA-LaBr<sub>3</sub> experiment):

- Large fraction of AGATA events without PRISMA:

- 1. Issue in the PRISMA readout?

- 2. Issue in the event builder?

- 3. Issue on the GGP?

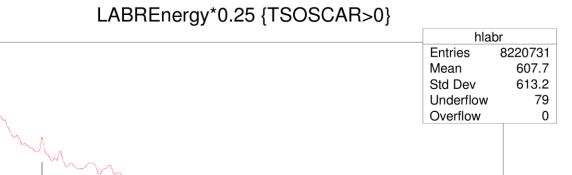

- "Strange" ratio of efficiency between AGATA and the LaBr<sub>3</sub> in coincidence with PRISMA

- 1. Source measurement ( $^{60}$ Co):  $\varepsilon_{AGATA} = 6 \times \varepsilon_{LaBr}$

- 2. In-beam measurement:  $\varepsilon_{AGATA} = 0.1 \text{ x } \varepsilon_{LaBr}$

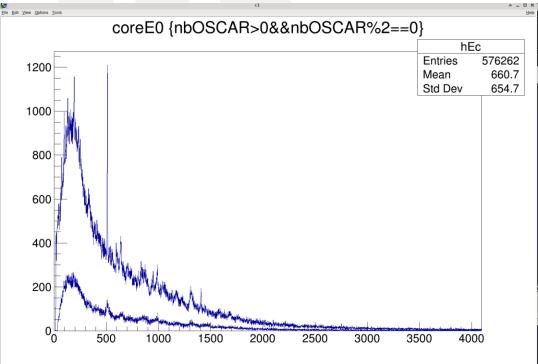

#### CLEAR FAILURE OF THE ACCEPTANCE / COMISSIONING TESTS OF THE NEW TP

The issue on the fold was identified during the initial tests but the coincidence between partitions was not fully tested

#### **EXOGAM2 TP VS DEMONSTRATOR TP**

- Initialization scripts of the TP were not fully stable (reset procedure)

- Firmware issue was detected on the operation of the input FIFO:

- Input FIFO was fully validated/rejected based on single events

- NEW FIRMWARE VERSION DELIVERED AND TESTED AT LNL

10<sup>5</sup>

$10^{3}$

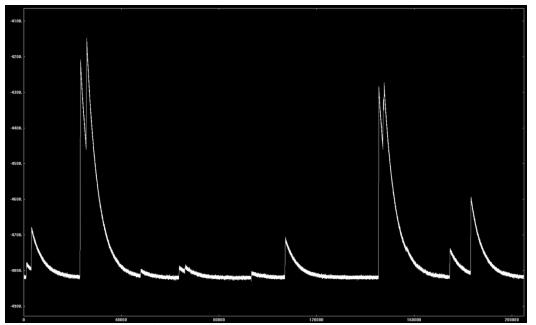

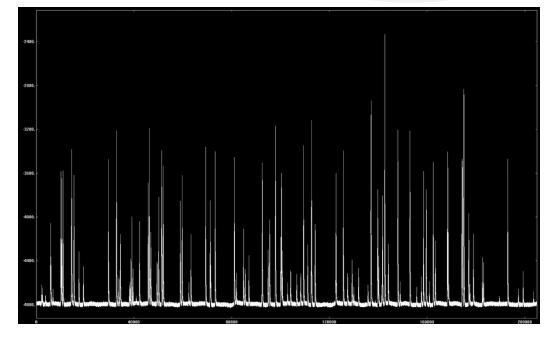

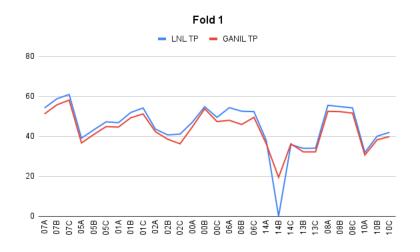

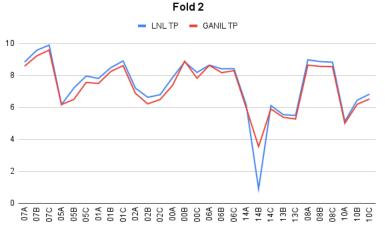

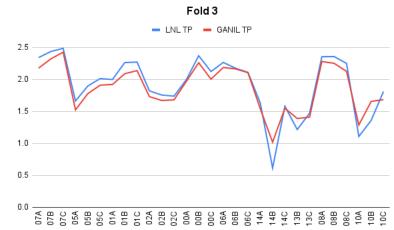

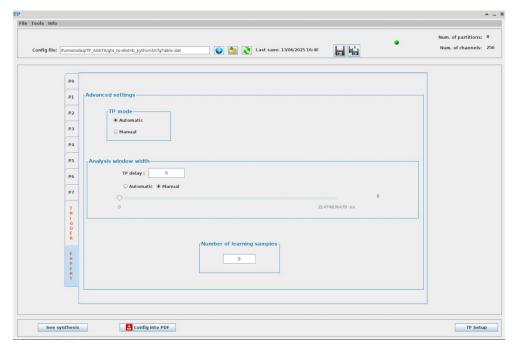

#### **NEW TP EXOGAM2 FIRMWARE TEST**

Source test with the <sup>60</sup>Co, integrating the 1332 keV peak EXOGAM2 TP seems to performed a bit worse than the old TP, this was understood as a wrong setting of the "TP delay"

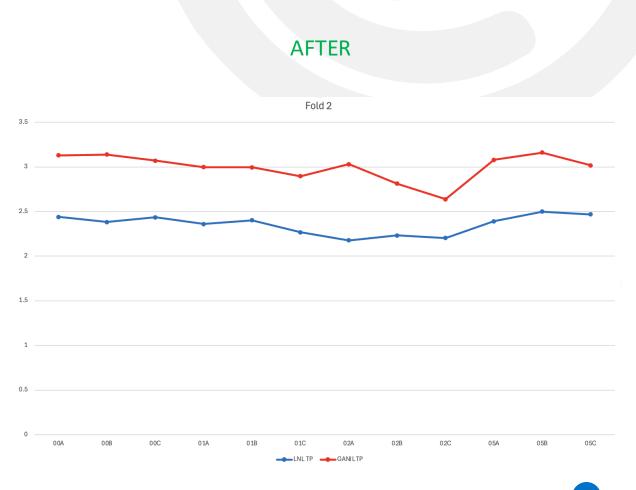

## CORRECTION OF THE TP DELAY EFFECT: 152EU

#### **BEFORE**

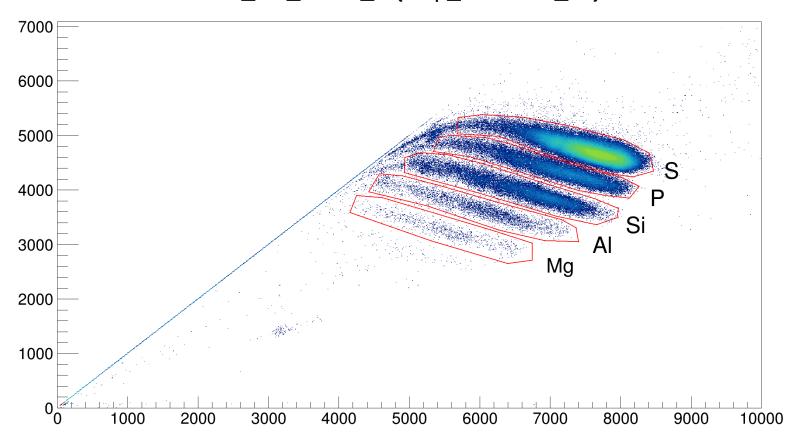

# IN BEAM TEST WITH PRISMA JUNE 2025

<sup>32</sup>S+<sup>124</sup>Sn @ 160 MeV Runs made with:

- LNLTP

- EXOGAM2 TP

- Hardware trigger

- HW + LNL FOLD 1

- HW + EXOGAM2 FOLD 1

- HW + LNL FOLD 2

- HW + EXOGAM2 FOLD 2

Beam intensity from 10 enA to to 50 enA, adding sources to push AGATA to 50 kHz / crystals

Data analysis in progress – PRISMA part is done

IC\_DE\_AB:IC\_E {mcp\_ok && tof\_ok}

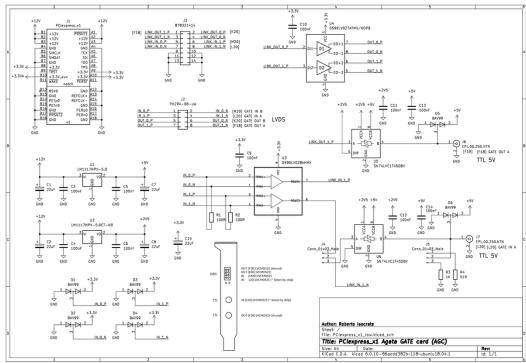

#### **HARDWARE TRIGGER**

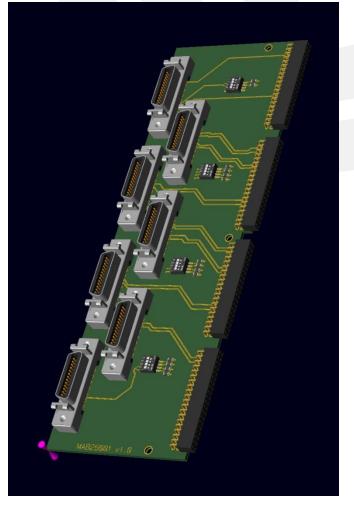

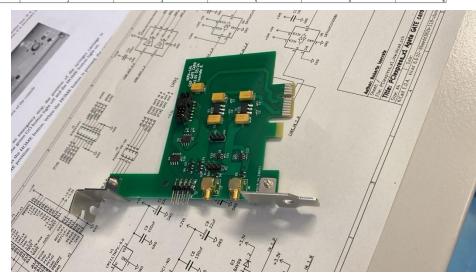

New GGP add-on board:

2 LVDS inputs

2 LVDS outputs

#### Present version of the GGP FW:

- Prompt external validation → Cutting down the trigger request

- Delayed external validation → Cutting the down the events in the FIFO

- Difficult to set and adjust but still feasible

Using a V2495 as FIFO to distribute the external signal to all the GGPs:

- Adjustable delay and width of the signal

- Validate/Reject all using slow control (To be used for beam on/beam off)

- Internal pulser to validate the system

#### **COMBINATION OF HARDWARE AND TP**

Typical experiment with 50 kHz / crystal

- With  $2\pi$ -array the TP would have to deal with 4.5 MHz ???

- Hardware gate could be used to reduce the TR arriving to the TP

For VAMOS/PRISMA you will have that over the 50 kHz of TR only ~1-2% will be in coincidence with the spectrometer

- Coincidence with the ancillary on the hardware condition

- TP could be used for the FOLD selection online

#### **CONCLUSIONS**

- 33 V1 channels are taking data

- GGPs SLC and FW still being updated / upgraded to cope with the new ADCs board, trigger system

- Investigation on the trigger boards:

- Back-pressure issue on the GGP on the SLC ... since???

- Dead-time origin on the demonstrator TP → No possible solution

- FW issue on the EXOGAM2 TP → New FW delivered and tested

- Low level hardware solution available for the V1, implementation in progress for the V2

- Definition of the needs for the GANIL campaign in terms of TP for SMART