# **Scintillator Tileboards for the CMS HGCAL**

**Design, Integration, Performance**

Mathias Reinecke CMS HGCAL ESR day1, Nov. 10<sup>th</sup>, 2023

HELMHOLTZ RESEARCH FOR GRAND CHALLENGES

#### **Outline**

- Tileboard Introduction

- Tileboard Prototypes History

- Pre-Series Status

- Tileboard Types and Status of Final Design

- Mechanical Integration (3D), Thermal Simulation

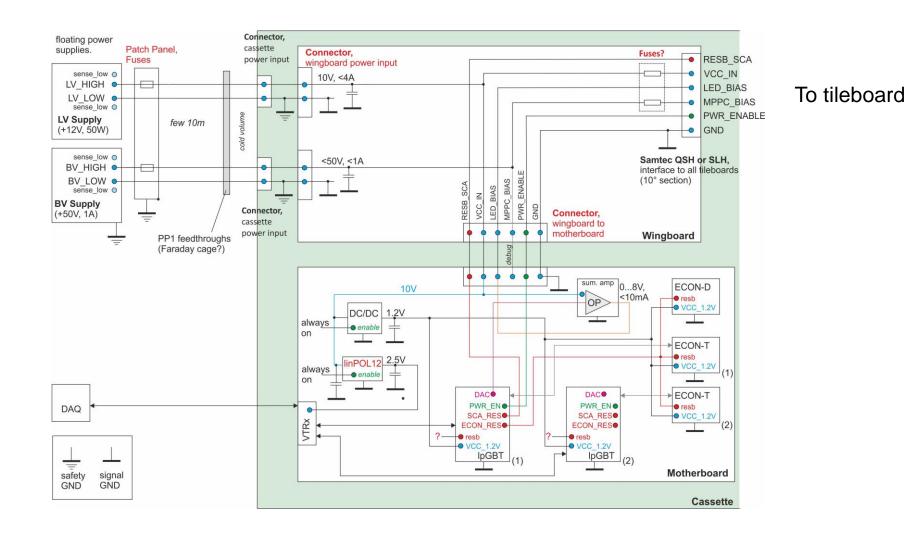

- Powering System

- Results from Bench Tests

- Results from Beam Tests

- Open Points

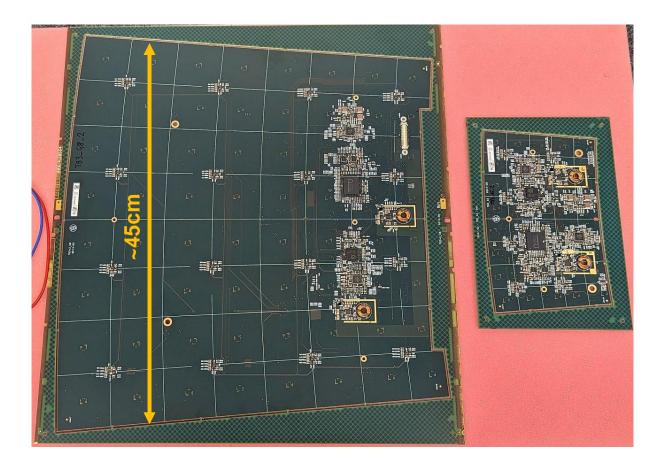

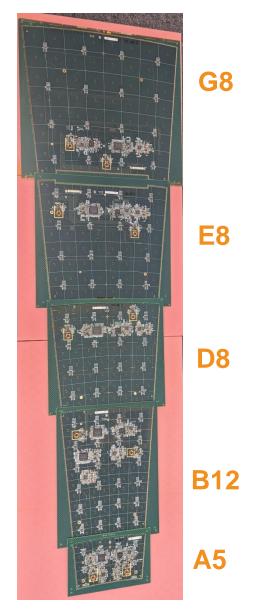

Pre-Series Tileboards TB3\_G8 and TB3\_A5

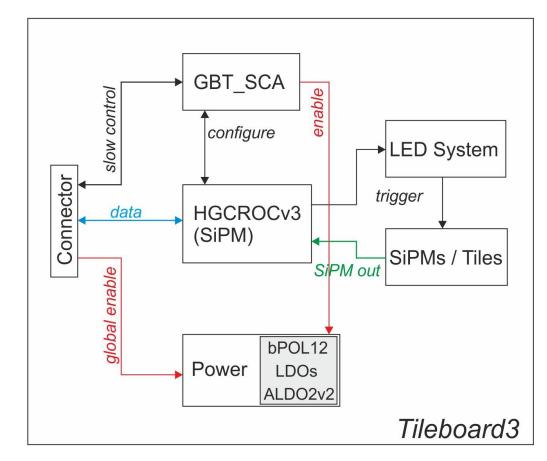

### **Tileboard3 - Introduction**

- Basic Detector-Module for CMS HGCAL Scintillator Detector.

- Typically 64 SiPMs and plastic scintillator tiles.

- One or two HGCROCv3(b) in LD packages.

- GBT\_SCA for slow-control

- Integrated LED system for gain calibration and monitoring.

- On-board integrated power setup.

- Single connector as only interface for power and signals.

TB3 Block-Diagram

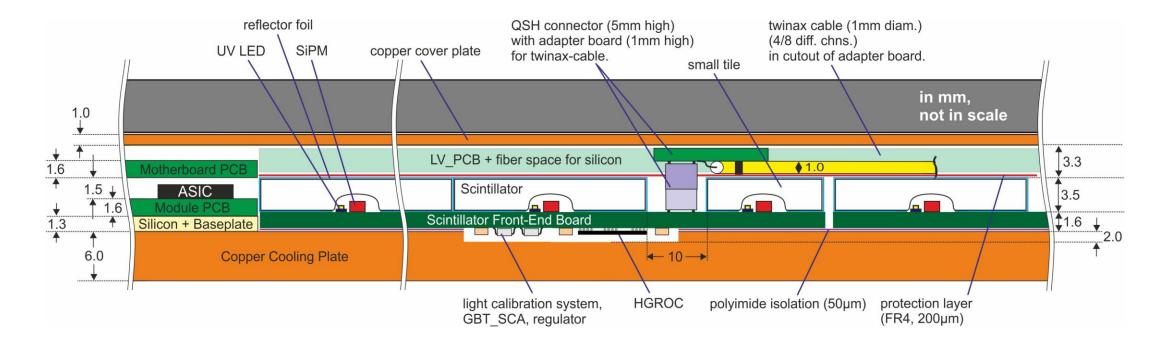

#### **Tileboard3 - Introduction**

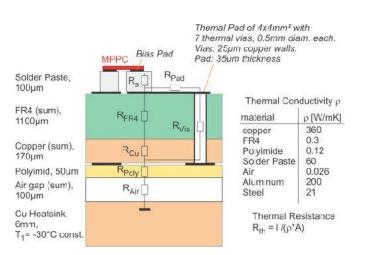

- Scintillator Tileboards with SiPMs, LEDs and Tiles on copper heatsink (-30°C).

- All other active components are on the backside in pockets of the copper heatsink.

- Polyimide isolation foil (50µm) under tileboards, FR4 protective cover (600µm) on top.

### **Tileboard Prototype History**

- Tileboard\_Prototype0 (Jan. 2019):

- GBT\_SCA,

- 8 temperature sensors, power producers (Resistors),

- LED test circuit.

- Tileboard Prototype 1 (TB1, Sept. 2019), TB1.2 (March 2020), TB1.3 (Sept. 2020)

- HGCROCv1

- CALICE based LED system

- Commercial LDOs, FEAST DCDCs

- SiPMs in CALICE package (TB1) and in first custom packages (TB1.2, TB1.3)

- Tileboard Prototype 2 (May 2021)

- HGCROCv2

- New, MOSFET-based LED system

- Commercial LDOs, FEAST DCDCs

- SiPMs in custom HGCAL packages (2mm<sup>2</sup> and 4mm<sup>2</sup>).

- Tileboard\_Prototype3 (Nov. 2022):

- HGCROCv3

- bPOL12V and HGCAL LDOs

- ALDO2v2

- SiPMs in custom HGCAL packages (2mm<sup>2</sup>, 4mm<sup>2</sup> and 9mm<sup>2</sup>).

- Mini Tileboard HD (Sept. 2021), LD (May 2023)

- Pre-Series Tileboards (A5, B12, D8, E8, G8): June 2023.

- 4 years of experience with basic signal chain and board structure

- Thermal validation as 1<sup>st</sup> step 2019

- (back-up slide)

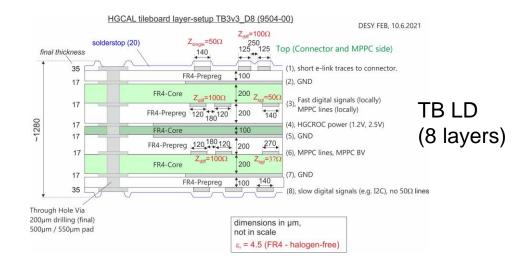

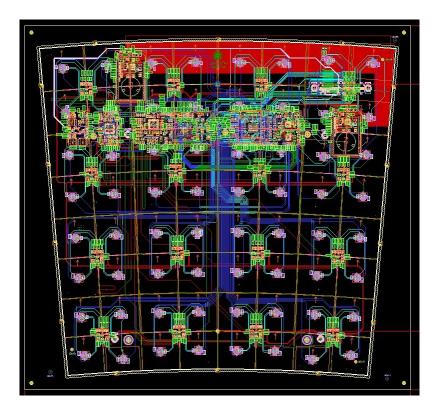

#### Scintillator Tileboards – Layer Structure

- Full tileboard specifications: Procurement Document. See backup for technical details.

- Typically: 8 signal layers

- 100Ω differential lines, SiPM lines adapted to HGCROC input impedance (37Ω).

- Near SiPMs and power consumers: thermal vias.

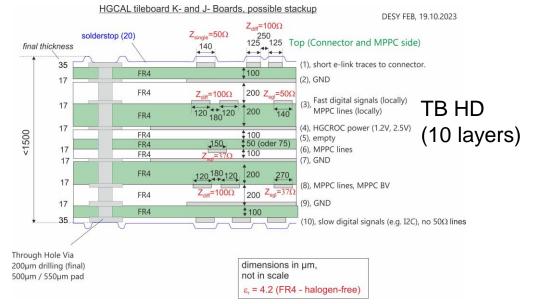

- New: High-density Tileboards in front section (former FH).

- 64chs => 144chs.

- 10 signalling layers required.

- Setup under discussion with vendors.

- No buried/micro-vias, no via-in-pad (costs, complexity).

- Except board size for largest tileboards (G8: 475x440mm<sup>2</sup>) no critical design features.

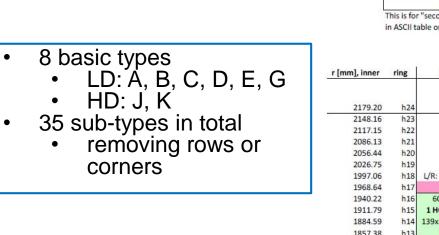

#### **Scintillator Tileboards – Variants**

Cross-sectional view of CMS endcap, showing only the scintillator detector

|                    | Layer Overview: No. Channels and ROCs, Dimensions.                        |                        |                        |                        |                        |  |  |  |  |  |  |  |

|--------------------|---------------------------------------------------------------------------|------------------------|------------------------|------------------------|------------------------|--|--|--|--|--|--|--|

|                    | This is for "second optimization". The outer rings in FH are not included |                        |                        |                        |                        |  |  |  |  |  |  |  |

|                    | in ASCII t                                                                | able on tab "Lay       | er_Data" (BV cu        | rrents!). Some in      | nner rings delet       |  |  |  |  |  |  |  |

|                    |                                                                           |                        |                        |                        |                        |  |  |  |  |  |  |  |

|                    |                                                                           |                        | 65 H                   | 5110.43                |                        |  |  |  |  |  |  |  |

| r [mm], inner      | ring                                                                      | 34                     | CE-H: layers for<br>35 | 37                     |                        |  |  |  |  |  |  |  |

| r (min), miler     | ing.                                                                      | 54                     | 35                     | 36                     | 57                     |  |  |  |  |  |  |  |

|                    |                                                                           |                        |                        |                        | L/R: 2x6tiles          |  |  |  |  |  |  |  |

| 2179.20            | h24                                                                       |                        |                        |                        |                        |  |  |  |  |  |  |  |

| 2148.16            | h23                                                                       |                        |                        |                        |                        |  |  |  |  |  |  |  |

| 2117.15            | h22                                                                       |                        |                        | L/R: 2x5tiles          |                        |  |  |  |  |  |  |  |

| 2086.13            | h21                                                                       |                        | L/R: 2x5tiles          | 120chns                | 144chns                |  |  |  |  |  |  |  |

| 2056.44            | h20                                                                       |                        |                        |                        |                        |  |  |  |  |  |  |  |

| 2026.75            | h19                                                                       |                        | 96chns                 | 2 HGCROCs              | 2 HGCROCs              |  |  |  |  |  |  |  |

| 1997.06            | h18                                                                       | L/R: 2x5tiles          | 2HGCROCs               | 302x372mm <sup>2</sup> | 349x380mm <sup>2</sup> |  |  |  |  |  |  |  |

| 1968.64            | h17                                                                       |                        | 227x364mm <sup>2</sup> |                        |                        |  |  |  |  |  |  |  |

| 1940.22            | h16                                                                       | 60chns                 |                        |                        |                        |  |  |  |  |  |  |  |

| 1911.79            | h15                                                                       | 1 HGCROC               |                        |                        |                        |  |  |  |  |  |  |  |

| 1884.59            | h14                                                                       | 139x348mm <sup>2</sup> |                        |                        |                        |  |  |  |  |  |  |  |

| 1857.38            | h13                                                                       | К5                     | К8                     | К10                    | K12                    |  |  |  |  |  |  |  |

| 1830.17            | h12                                                                       |                        |                        |                        |                        |  |  |  |  |  |  |  |

| 1804.12            | h11                                                                       |                        |                        |                        |                        |  |  |  |  |  |  |  |

| 1778.07            | h10                                                                       |                        |                        |                        |                        |  |  |  |  |  |  |  |

| 1752.03            | h9                                                                        |                        |                        |                        |                        |  |  |  |  |  |  |  |

| 1727.09            | h8                                                                        |                        |                        |                        |                        |  |  |  |  |  |  |  |

| 1702.16            | h7                                                                        |                        |                        |                        |                        |  |  |  |  |  |  |  |

| 1677.22            | h6                                                                        | 144chns                | 144chns                | 144chns                | 144chns                |  |  |  |  |  |  |  |

|                    | h5                                                                        | 2 HGCROCs              | 2 HGCROCs              | 2 HGCROCs              | 2 HGCROCs              |  |  |  |  |  |  |  |

| 1653.35            |                                                                           | 202.2102               | 293x319mm <sup>2</sup> | 293x319mm <sup>2</sup> | 293x319mm <sup>2</sup> |  |  |  |  |  |  |  |

| 1653.35<br>1629.48 | h4                                                                        | 293x319mm <sup>2</sup> | 233831311111           |                        |                        |  |  |  |  |  |  |  |

|                    | h4<br>h3                                                                  | 293X319mm-             | 233831311111           |                        |                        |  |  |  |  |  |  |  |

| 1629.48            | h3                                                                        | J12                    | J12                    | J12                    | J12                    |  |  |  |  |  |  |  |

| 1629.48<br>1605.61 | h3<br>h2                                                                  |                        |                        |                        |                        |  |  |  |  |  |  |  |

| gree-<br>oard, | Tileboard recess at Si-Interf.      |

|----------------|-------------------------------------|

| iles           | cassette infrastructure             |

|                | not assembled                       |

|                | Connector/HGCROC Pos.               |

|                | 4mm <sup>2</sup> SiPM, cast tiles   |

|                | 4mm <sup>2</sup> SiPM, molded tiles |

|                | 9mm <sup>2</sup> SiPM, cast tiles   |

r [mm],

|                    |      | CE-H: layers former BH 13-22 |                           |                        |                        |                        |                        |                        |  |  |  |

|--------------------|------|------------------------------|---------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|--|--|--|

| n], inner          | ring | 38                           | 39                        | 40                     | 41                     | 42-43                  | 44-45                  | 46-47                  |  |  |  |

|                    |      |                              |                           |                        | 1 10 4 0 11            |                        | 1/2 4 2 17             |                        |  |  |  |

| 2594.79            | 42   |                              |                           |                        | L/R: 1x2 tiles         | L/R: 1x2 tiles         | L/R: 1x2 tiles         | r                      |  |  |  |

| 2539.39            | 41   |                              | 73                        | L/R: 1x3 tiles         |                        |                        |                        | 121                    |  |  |  |

| 2483.99            | 40   |                              |                           |                        |                        |                        |                        | G5:                    |  |  |  |

| 2430.96            | 39   |                              | L/R: 1x3 tiles            | 56chns                 | 64chns                 | 64chns                 | 64chns                 | no L/R types           |  |  |  |

| 2377.93            | 38   |                              | 40chns                    | 1HGCROC                | 1 HGCROC               | 1 HGCROC               | 1 HGCROC               | 40chns                 |  |  |  |

| 2327.16            | 37   | L/R: 1x3 tiles               | 1HGCROC                   | 360x443mm <sup>2</sup> | 416x452mm <sup>2</sup> | 416x452mm <sup>2</sup> | 416x452mm <sup>2</sup> | 1HGCROC                |  |  |  |

| 2276.40            | 36   | 24chns                       | 251x424mm <sup>2</sup>    | 1000                   |                        |                        | 22.2                   | 251x424mm <sup>2</sup> |  |  |  |

| 2227.80            | 35   | 147x406mm <sup>2</sup>       | G5                        | G7                     | G8                     | G8                     | G8                     | G5                     |  |  |  |

| 2179.20            | 34   | G3                           |                           |                        |                        |                        |                        |                        |  |  |  |

| 2132.67            | 33   |                              |                           |                        |                        |                        |                        |                        |  |  |  |

| 2086.15            | 32   | 64chns                       | 64chns                    | 64chns                 | 64chns                 | 64chns                 | 64chns                 | 64chns                 |  |  |  |

| 2041.61            | 31   | 1 HGCROC                     | 1 HGCROC                  | 1 HGCROC               | 1 HGCROC               | 1 HGCROC               | 1 HGCROC               | 1 HGCROC               |  |  |  |

| 1997.08            | 30   | 349x380mm <sup>2</sup>       | 349x380mm <sup>2</sup>    | 349x380mm <sup>2</sup> | 349x380mm <sup>2</sup> | 349x380mm <sup>2</sup> | 349x380mm <sup>2</sup> | 349x380mm <sup>2</sup> |  |  |  |

| 1954.44            | 29   |                              | 50                        | 50                     |                        |                        |                        | 50                     |  |  |  |

| 1911.80            | 28   | E8                           | E8                        | E8                     | E8                     | E8                     | E8                     | E8                     |  |  |  |

| 1870.99            | 27   |                              |                           |                        |                        |                        |                        |                        |  |  |  |

| 1830.17            | 26   |                              |                           |                        |                        |                        |                        |                        |  |  |  |

| 1791.10            | 25   | <b>C4</b> (1)                |                           | C 1 1                  | <b>C1</b>              | -                      | COMPANY INCOME         | CAL                    |  |  |  |

| 1752.03            | 24   | 64chns                       | 64chns                    | 64chns                 | 64chns                 | 64chns                 | 64chns                 | 64chns                 |  |  |  |

| 1714.62            | 23   | 1 HGCROC                     | 1 HGCROC                  | 1 HGCROC               | 1 HGCROC               | 1 HGCROC               | 1 HGCROC               | 1 HGCROC               |  |  |  |

| 1677.22            | 22   | 293x319mm <sup>2</sup>       | 293x319mm <sup>2</sup>    | 293x319mm <sup>2</sup> | 293x319mm <sup>2</sup> | 293x319mm <sup>2</sup> | 293x319mm <sup>2</sup> | 293x319mm <sup>2</sup> |  |  |  |

| 1641.41            | 21   |                              |                           |                        |                        | 100                    |                        |                        |  |  |  |

| 1605.60            | 20   | D8                           | D8                        | D8                     | D8                     | D8                     | D8                     | D8                     |  |  |  |

| 1571.33            | 19   |                              |                           |                        |                        |                        |                        |                        |  |  |  |

| 1537.05            | 18   |                              |                           |                        |                        |                        |                        |                        |  |  |  |

| 1504.23            | 17   | 10.1                         | 10.1                      | 0C-h-c                 | 00.1                   | OC-h-r                 | OC-L                   | OC-h-r                 |  |  |  |

| 1471.42            | 16   | 40chns                       | 40chns                    | 96chns                 | 96chns                 | 96chns                 | 96chns                 | 96chns                 |  |  |  |

| 1440.00            | 15   | 1HGCROC                      | 1HGCROC                   | 2 HGCROCs              |  |  |  |

| 1408.59            | 14   | 159x268mm <sup>2</sup>       | 159x268mm <sup>2</sup>    | 354x268mm <sup>2</sup> | 354x268mm <sup>2</sup> | 354x268mm <sup>2</sup> | 354x268mm <sup>2</sup> | 354x268mm <sup>2</sup> |  |  |  |

| 1378.52            | 13   | C5                           | C5                        |                        |                        |                        |                        |                        |  |  |  |

| 1348.45            | 12   | C5: 8mm                      | C5: 8mm                   |                        |                        |                        |                        |                        |  |  |  |

| 1319.66            | 11   |                              |                           |                        |                        |                        |                        |                        |  |  |  |

| 1290.87            | 10   |                              |                           | 011 / 012              | 011 / 012              | 011 / 013              | 013                    | 012                    |  |  |  |

| 1263.31<br>1235.75 | 9    |                              |                           | B11 / B12              | B11 / B12              | B11 / B12              | B12                    | B12                    |  |  |  |

|                    |      |                              |                           |                        |                        |                        |                        |                        |  |  |  |

| 1209.37            | 7    |                              |                           |                        |                        |                        |                        |                        |  |  |  |

| 1182.99            |      |                              | 18                        | D11: Emer              | P12: 0mm               | D11: Emer              |                        |                        |  |  |  |

| 1157.73<br>1132.48 | 5    |                              |                           | B11: 5mm               | B12: 0mm               | B11: 5mm               | 48chns                 | 48chns                 |  |  |  |

| 1108.30            | 4    |                              |                           |                        |                        |                        | 1HGCROC                | 1HGCROC                |  |  |  |

|                    |      |                              |                           |                        |                        |                        | 145x206mm <sup>2</sup> | 145x206mm <sup>2</sup> |  |  |  |

| 1084.12            | 2    |                              |                           |                        |                        |                        | A5 / A6                | A5 / A6                |  |  |  |

| 1060.98            | 0    |                              |                           |                        |                        |                        | AS / AD                | A5 / A6                |  |  |  |

| 1037.83            | 0    |                              |                           |                        |                        |                        | A5/A6: 0mm             | A5/A6: 0mm             |  |  |  |

|                    |      |                              | 10 degree-                |                        |                        |                        | AS/A6: UMM             | A3/A6: UMM             |  |  |  |

|                    |      |                              |                           |                        |                        |                        |                        |                        |  |  |  |

|                    |      |                              | Tileboard,<br>1.25° tiles |                        |                        |                        |                        |                        |  |  |  |

|                    |      |                              | 1.25 tiles                | 9                      |                        |                        |                        |                        |  |  |  |

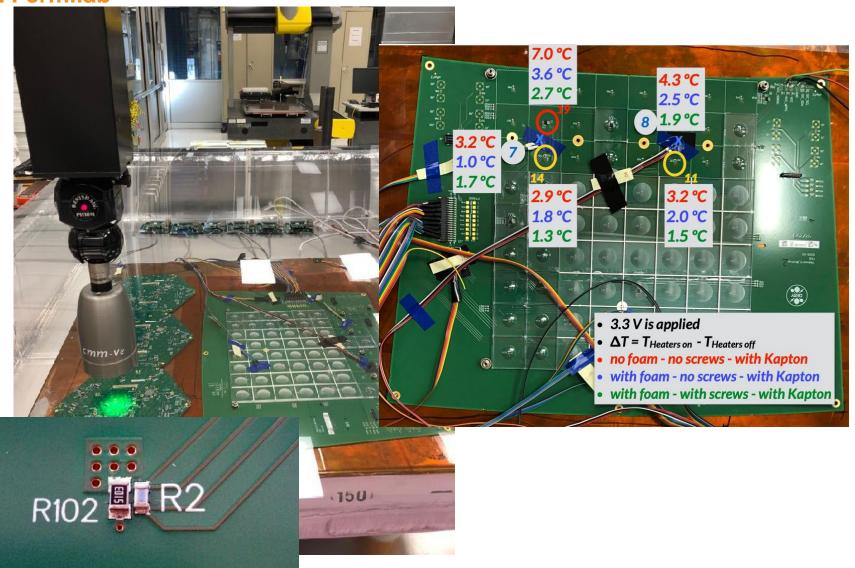

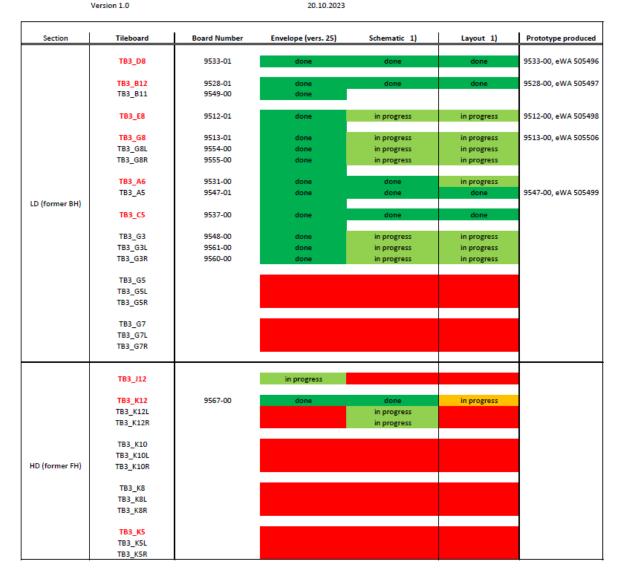

#### **Pre-Series Production - Status**

- Currently 2 Tileboards of A5, B12, D8, E8 and G8 assembled (10 in total)

- Commissioning of A5, D8, E8 and G8 completed.

- All work fine on testbench.

- A5 and G8 have been at DESY testbeam in August.

- Commissioning of B12 ongoing. Data taking already works.

- Remaining 31 tileboards are being assembled next week.

- One 10° sector reserved for HGCROCv3b.

- First pre-series Tileboards have been sent to US.

- Motherboard tests and Tilemodule assembly optimisation

- TB3.0 has been sent to UMD (USA) earlier. Teststand in operation.

- UMD students and postdoc have been trained in Tileboard operation at DESY

#### **Scintillator Tileboards – Remaining Design Work**

- Scintillator and Tileboard geometry in optimisation until recently.

- Status LD boards is final.

- Status HD boards:

- Mechanical integration of Wingboard and Motherboard to be finalised

- Still minor schematics updates (from tests, ALDO2v2 peripheral components). **Mostly done.**

- Scenario with all SiPMs in 9mm<sup>2</sup> package still to be implemented for several types (few days per type).

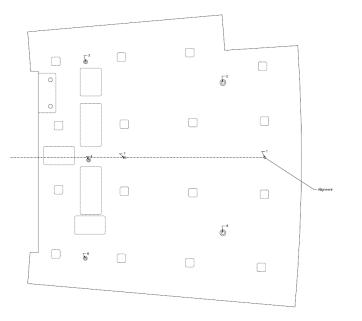

TB3\_G8L envelope

#### **Scintillator Tileboards – Status Layouts**

- 3 Layouters now working on updates

- 2 working on LD boards

- 1 (me) working on K12 in HD granularity

- Layouts in final state: A5/A6, B12, D8, C5, B11

- Layouts done to 98%: E8, G8, G3, G8L, G8R

- Next Layouts, to be completed very soon (end Nov.): G3L, G3R

- End 2023: G5, G7 with L/R, waiting for 9mm<sup>2</sup> SiPM decision.

- K12 with essential progress expected end Nov.

- Expected to be in time for vendor qualification

- Beginning 2024: J12, K5, K8, K10 (Ks with L/R)

- Expected to finish in time for production contract (April 24)

TB3\_D8 layout (planes not shown)

- All basic types designed (LD section)

- LD designs validated by final prototypes

- HD prototype cycle before production starts

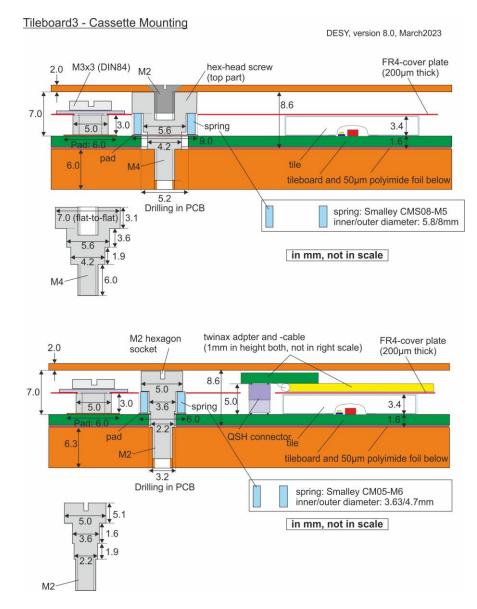

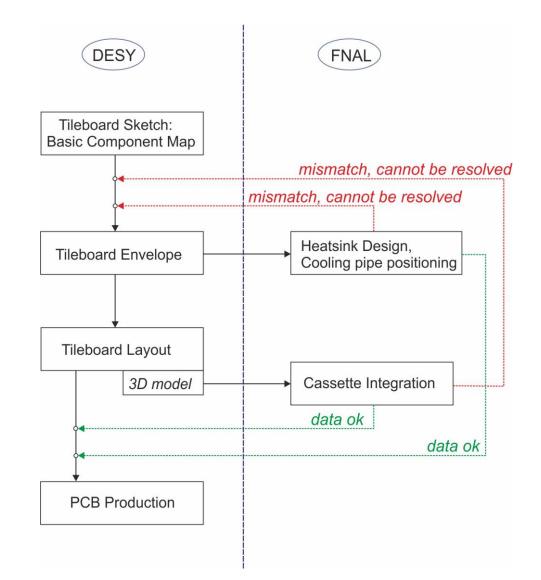

## **Tileboards – Mechanical Integration**

- Tileboard fixation agreed with cassette mechanical design team at FNAL.

- Use SMD nuts with inner threads (no copper cut-out) to fix:

- Protective cover: M3x3mm.

- Twinax Adapter: M3x5mm.

- Flexleads (E- and G-Boards): M2.5x2.5mm.

5mm-high SMD nuts next to QSH connector with inner M3 thread to fix twinax adapter

## **Tileboards – Mechanical Integration**

- Tileboard Designs start with basic mechanical models (3D):

- Board Outline, SiPM positions, Drillings, Heatsink pockets, Tiles.

- Resulting Envelopes are used for:

- heatsink/cassette design at FNAL (3D). Positioning of the cooling pipes (with possible feedback to envelopes).

- tileboard layout preparation (2D).

- Enables parallel development of copper heatsink and tileboard layouts without mechanical conflicts.

- From tileboard layouts detailed 3D models of tileboards are generated for cassette integration verification at FNAL.

- PCB production when passing verifications.

## **Tileboards – Mechanical Integration**

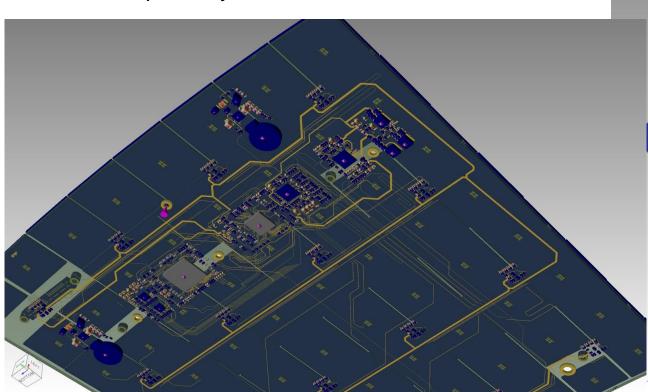

- 3D Tileboard Models for cassette integration verification.

- 3D models are generated in parallel to layout generation.

- Data compatibility checked with CERN/FNAL.

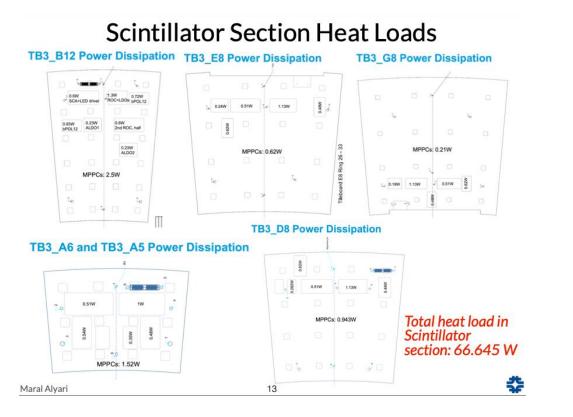

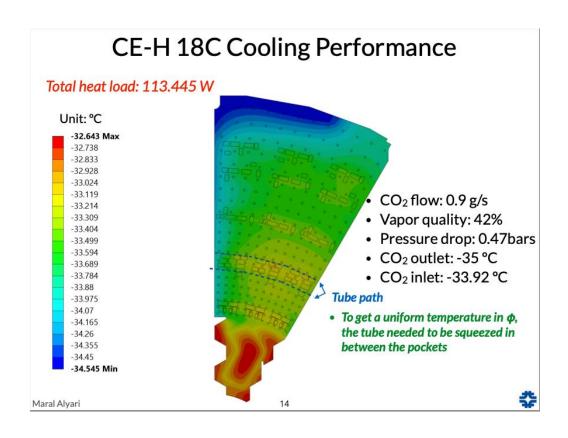

## **Tileboards: Thermal Integration (Simulation @FNAL)**

- Power map of all tileboards provided to FNAL.

- SiPM currents at end of lifetime (see backup).

- Switch to 9mm<sup>2</sup> SiPMs: No increase of power budget: Reduction of <u>global</u> overvoltage to meet HGCROC input current limit of 1.2mA per channel.

- Hot spot in silicon region only.

- Temperature increase/gradient in scintillator region within 1.5°C: No problems expected.

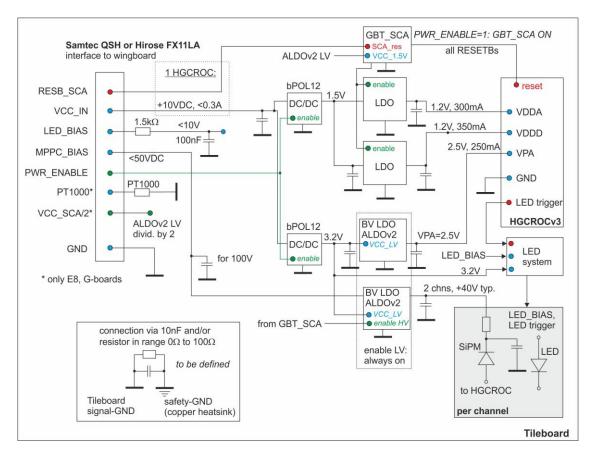

#### **Scintillator Tileboards – Power and Ground**

- Single connector as interface for power and signals.

- Integrated bPOL12Vs (no mezzanines)

- HGCAL LDOs for HGCROCv3 powering.

- ALDO2v2 from BTL group:

- SiPM BV and HGCROCv3 analog input stage.

- Qualification for CMS from BTL colleagues with more stringed operation limits. PRR of ALDO2v2 done.

- Production yield (Milano): ~99%

- GBT\_SCA (supply voltage 1.5V) for slow-control.

- No fuses on tileboards. In discussion: Fuses on wingboards.

- Huge HF capacitance Tileboard to Heatsink.

- Special connection of tileboard GND to heatsink (safety GND) for LF noise optimization.

- Powering Setup (LV and BV) is described in detail in edms document 2476375.

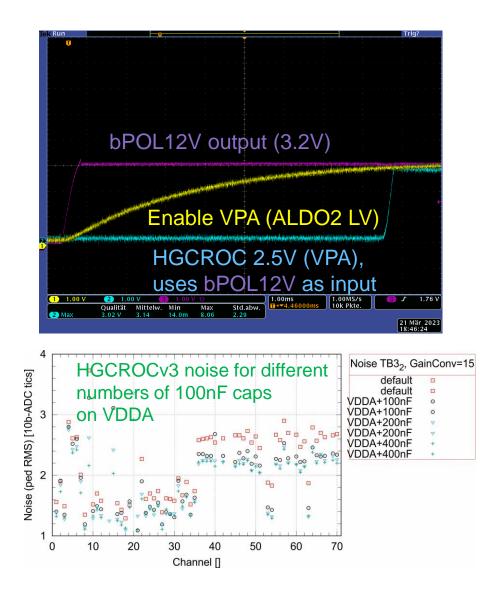

### **Tileboard3 – Supply Voltage Ripple, Switching and Filtering**

- TB3 supply voltages tested with oscilloscope:

- Integrated bPOL12 outputs,

- HGCROC voltages, ALDO2v2 LV outputs

- SiPM bias voltages (LDO: ALDO2v2)

- Ripple (below detection limit of scope), Spikes checked.

- Switch-on characteristics: No over-, undershoots.

- TB3 filtering setup has been checked by removing / adding filter capacitors at regulator in- and outputs:

- noise performance.

- supply voltage stability (no oscillation).

- filtering setup has been optimized based on these results.

- Sufficient margin on the filter setup on all voltages.

- If unexpected issues (excessive noise, oscillation on supply voltages) occur, improvements still possible:

- Removing filter capacitors, changing capacitor sizes

- Changing connection to safety GND (via R and C).

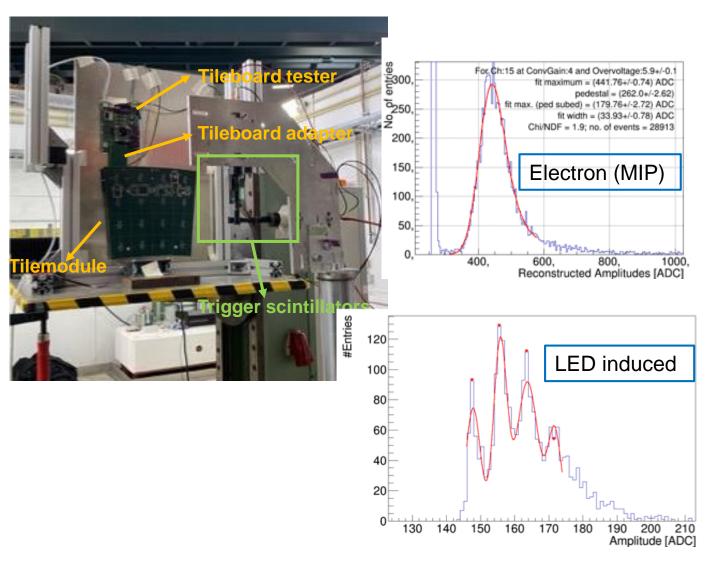

### **Tileboards in Testbeams**

#### Tileboards routinely used for scintillator tile and SiPM validation in realistic environment

- Most tests done at DESY with 3 GeV electrons

- producing MIP-like response in Tileboards without absorber

- Many different tile and SiPM types tested

- Basic scaling laws of signal variation with tile and SiPM size verified

- Optical performance of SiPM-tile system characterised in terms of light yield

- LY = MIP / gain (from single ph.e. peaks)

- Results entered into optimisation of detector layout in expected radiation field.

- Testbeam: Tilemodule performance verification:

- Realistic harsh environment. No stability issues (crashes) observed (DAQ communication).

- Realistic power supplies.

- Smallest signals to be detected: Single ph.e. peaks could be well recorded.

- No issues with noise with unirradiated SiPMs.

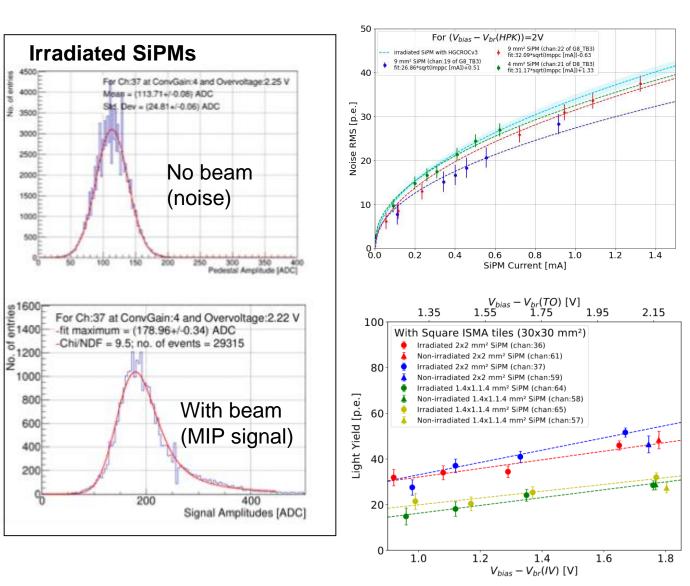

#### **Tests with irradiated SiPMs**

- Irradiated SiPMs on tileboards:

- 2E12 n/cm<sup>2</sup> at RT equivalent to 5E13 n/cm<sup>2</sup> at -30°C.

- Noise behavior has been characterized by

- Irradiated SiPMs

- Un-irradiated SiPMs illuminated by DC light source.

- Model confirmed also on tileboards: SiPM dark current to pedestal width (noise).

- Light yield (LY) compared for un-irradiated and irradiated SiPMs in DESY testbeam for different SiPM sizes.

- No deviation from LY predictions observed for irradiated SiPMs.

- Signal (LY) and noise validated for 9mm<sup>2</sup>

SiPMs in the same way as well.

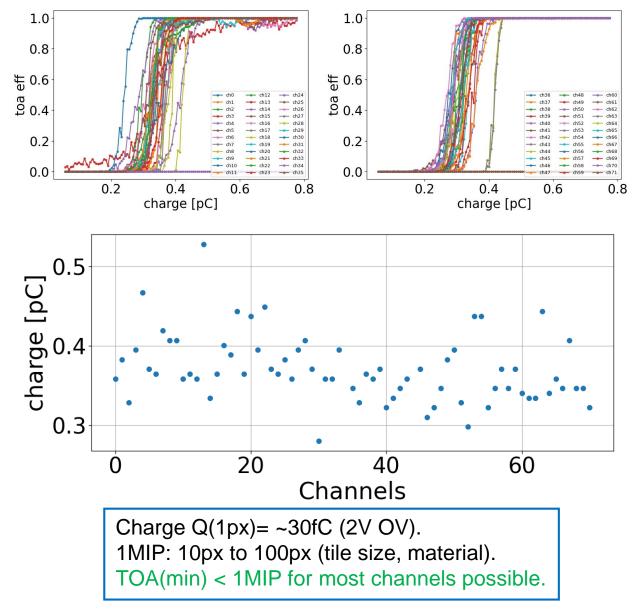

### Tileboard3 – Data Taking scripts (DAQ)

- Data taking scripts for all important tasks in place, as e.g.

- Pedestals /noise

- Timing scans

- Amplitude scans.

- Testbeam data taking with external (beam) trigger.

- Further improvements of the scripts in preparation as for example 'setting of Minimum TOA threshold':

- Results different for HGCROC alone and HGCROC on tileboard.

- Isolated HGCROC results without capacitance (SiPM) at the inputs.

- After configuration correction, good agreement of results. Minimum TOA threshold in the range of 1MIP possible for almost all channels.

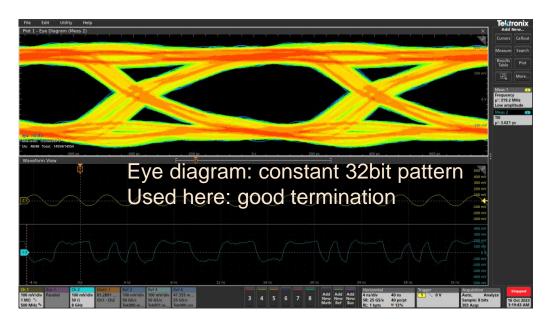

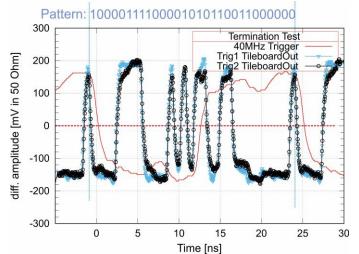

### **Tileboard3 – Fast Outputs Signal Integrity**

- HGCROCv3 has 6 fast digital outputs, each operated at 1.28GBit/s.

- Signal integrity studies with TB-Testerv2 show problems:

- Termination cannot be set correctly on TB-Testerv2.

- Reflections cause significant eye-diagram degradation.

- Common-mode level not correct.

- TB-Testerv2 will be replaced soon by KRIA based DAQ with correct termination.

- Termination tests with 1000hm on adapter between tileboard and TB-Testerv2 show good eye openings and signal shapes (test setup).

- Tests need to be repeated in final setup with twinax cable and motherboard.

Terminated at TB-Testerv2 input, Terminated at Tileboard output: ~10cm length difference

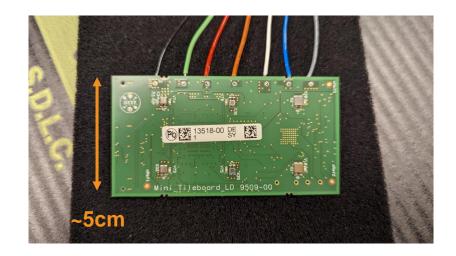

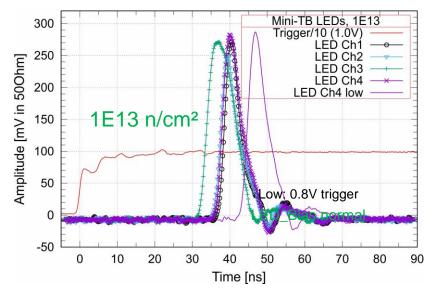

#### **Mini-TB irradiation tests**

- Mini-TB allows system irradiation tests: ROCv3 + GBT\_SCA + SiPMs + new LED system.

- How much irradiation (neutrons, gammas) does the LED system tolerate?

- Most important: LED system must not come into critical state.

- Considered unlikely but prefer to test.

- Irradiation of 4 un-biased Mini-TBs at JSI Ljubljana with fluences:

- 2E12 n/cm<sup>2</sup>, 1E13 n/cm<sup>2</sup>, 5E13 n/cm<sup>2</sup> (maximum expected dose), 1E14 n/cm<sup>2</sup>

- No special annealing. These tests: 6 months later.

- LED system fully functional till 1E13n/cm<sup>2</sup>. No critical state till 5E13n/cm<sup>2</sup>.

- Next test: TID (no critical states expected)

- Note that LED system mainly used for tests and commissioning, initial light yield calibration

- Later: not critical, but nice to have, and must be safe

#### **Scintillator Tileboards – Open points**

- Finish commissioning of B-tileboards (DAQ issues solved now, up to now no problems).

- Transition from HGCROC3 to HGCROCv3B.

- Prototype validation of HD tileboards (J- and K-).

- Irradiation (TID) tests of Mini-TB.

- Performance of tileboards in cassette with motherboard and twinax cable (full system test).

- Signal/Noise in cassette environment

- Signal transfer via twinax cable

- Grounding and power stability

- Cooling, temperature profiles

- Options available in filtering setup and connection to safety ground to improve power / noise / grounding setup.

- No issues expected from any of the listed items.

- Expect results on these topics within the next 6 months.

#### Conclusion

- Tileboard design is mature, production of design variants is routine now and well advanced.

- Prototypes were tested extensively on testbench and in many testbeam campaigns, at DESY and in the US.

- Pre-series Tileboards are in operation. B12 tests not completed. Up to now no issues.

- Assembly of remaining pre-series boards 'now'.

- Tileboard Procurement at CERN and in the US has started.

- Finishing remaining designs and tests in parallel.

- ESR2: System tests.

### **Tileboard Thermal Tests**

Mixed Cassette Mockup Effort at Fermilab

Thermal teststand at Fermilab

#### Mock-up tileboard:

Full cycle to -30°C ✔

validate SiPM cooling through PCB using thermal vias

max increase with load: 2K

no strong gradients

heat conductance: contact to cooling plate (100 K/W) is largest effect

#### Scintillator Tileboards – Status of Designs

TB3.1 Design Status Version 1.0

#### Done

Done to 98% (very minor changes) Started (new main geometry) Not started

- All basic types designed ٠

- LD designs validated by final prototypes ٠

#### **Scintillator Tileboards – QC**

- QC for bare boards, mainly by vendor:

- Acceptance tests at TACs

- See procurement document.

- QC procedure of Tileboards (no tiles) and Tilemodules (with tiles) in TACs discussed with UMD.

- Tileboard QC for DESY TAC to be developed together with KIT.

- Tileboard TB3p1\_D8 at KIT, but no TB-Testerv2/KRIA yet

- Required scripts for QC exist as separate tasks in general DAQ or at DESY (tileboard specific)

- Scripts and procedures need to be optimised and automatised:

- Not all procedures / scripts work satisfactorily yet, e.g. TOA/TOT threshold adjustment

- Define pass/fail criteria for tests

- Result transfer to database.

- Hardware setup (multi-channel power supplies with remote control, setup for parallel board tests)

#### **Pre-Series Production – Protective Foils**

- Pre-series TB3.1s in cassettes will have protective covers on top and isolation foil below.

- All designs ready for pre-series.

- Protective covers are made from halogen-free FR4 and will be ordered as PCBs at PCB company in thicknesses 600µm (final).

- Isolation foil (50µm polyimide) will be cut at DESY (Aristo cutter for tile reflector foils). Base material at DESY.

- Both: Not on time-critical paths.

Polyimide Isolation Foil (50µm)

#### **Scintillator Tileboards – PCB specifications**

| Mechanical Description  |                                                                 |

|-------------------------|-----------------------------------------------------------------|

| External size           | Smallest: 14cm x 20cm                                           |

|                         | Largest: 42cm x 45cm                                            |

| External size tolerance | +100µm / -300µm (outer tileboard: x1+x2<br>AND y1+y4 in Fig. 4) |

| Thickness               | 1.3mm +/- 0.15mm                                                |

| Number of layers        | 8                                                               |

|                         |                                                                 |

| Finished copper thickness requirements |                             |

|----------------------------------------|-----------------------------|

| External layers                        | 35μm-50μm (final thickness) |

| Internal layers – planes               | 17μm plus/minus 10%         |

| Internal layers – signals              | 17μm plus/minus 10%         |

| Hole (via) wall metallization          | >=25µm                      |

| Silkscreen on top    | Yes                                                               |

|----------------------|-------------------------------------------------------------------|

| Silkscreen on bottom | Yes                                                               |

| Silkscreen colour    | White                                                             |

| Soldermask on top    | Yes                                                               |

| Soldermask on bottom | Yes                                                               |

| Soldermask colour    | Green                                                             |

| Surface finish       | ENIG – electroless nickel immersion gold<br>according to IPC-4552 |

| Nickel thickness     | 3μm minimum – 8μm maximum                                         |

| Gold thickness       | 0.04µm minimum – 0.125µm maximum                                  |

| Tileboard specifications  |    |

|---------------------------|----|

| Blind/buried holes (vias) | No |

| Micro vias                | No |

| Vias class 2 derogation     | No                      |

|-----------------------------|-------------------------|

| Minimum track width         | 0.1mm                   |

| Minimum track/pad clearance | 0.1mm                   |

| Minimum hole (via) diameter | 0.20mm (final diameter) |

| Additional specifications          | •                    |

|------------------------------------|----------------------|

| Filled and capped vias?            | No                   |

| Via holes filled with resin        | No                   |

| Specified stackup                  | Yes                  |

| Controlled impedance               | Yes (plus/minus 10%) |

| Electrical tests                   | Yes                  |

| Test coupons required              | Yes                  |

| Exclusively halogen-free materials | Yes                  |

| RoHS compliant                     | Yes                  |

|                                    |                      |

#### Laminate and copper-foil requirements

Base material, when used, shall be flame retardant rated UL 94V-0 laminate glass-fibre epoxy and conform to L94 according to IPC-4101/128, halogen-free. Copper shall be type H with pits and dent, class B. When procuring base material, the following are required: minimum TG 160°C; minimum TD (5%) 350°C; minimum T-288 35min; maximum Z-axis thermal expansion coefficient above TG 280PPM/°C (alternatively Z-axis thermal expansion coefficient between 50-260°C of 3.5% maximum is acceptable)

Prepreg material shall conform to P94 according to IPC-4101/128, halogen-free and be subjected to the same requirement set forth for the laminate base material.

All internal layer copper foils shall conform to IPC-4562/2 CU-E3, class 2

#### Additional plating requirements

Finished external layers shall be  $35\mu$ m- $40\mu$ m and plated through holes plating shall be >=25 $\mu$ m. The copper plating shall be performed with plating chemistries/processes commensurate with the maximum aspect ratio plated hole in the board.

The quality of the copper plating shall be verified according to IPC-TM-650, 2.4.18.1 as to tensile strength and according to IPC-TM-650, 2.4.2.1 as to ductility.

Thieving may be added outside the circuit board border to compensate for high density areas on the board. For thieving within the borders of the circuit board approval is required.

#### Vias/through-hole requirements

Via drillings must be inside via pad – no breakouts are allowed

Negative etchback is not allowed. Positive etchback is permissible to  $5\mu m$  maximum.

All holes shall be located within a 100  $\mu m$  -diameter of true position. Drilling should be according to IPC-DR-572.

Via holes and drillings are specified as final hole size.

#### Additional board-finish requirements

Solder mask over bare copper according to IPC-SM-840, class H. All fiducials, lands, vias and holes shall be free of solder mask material.

Silkscreen shall be with permanent, organic, non-conductive and RoHS compliant ink. Silkscreen ink must be capable to withstand peak temperatures of 260-270°C for a duration of 60 seconds and at least 3-4 cycles without discoloration.

An identification marking shall be applied on the PCB. It shall contain the PCB manufacturer logo, UL marking, date-code and surface finish according to **J-STD-609**. Marking shall be applied on silkscreen at a specified position.

#### Additional quality-control requirements

The printed wiring board, and test coupon when used in lieu of a production board, shall be according to IPC-2221 and IPC-2222, type 3, class2. Date code and PCB manufacturer logo shall be present on test coupons for traceability.

Acceptance of finished printed boards shall be in accordance with IPC-A-600, class 2.

Fabrication and inspection shall be according to IPC-6011 and IPC-6012, class 2.

The maximum allowable bow and twist shall be 0.75%.

All quality controls shall be performed per IPC-TM-650 procedures and per IPC-4552.

#### Packing requirements

Boards shall be wrapped in sulfur-free neutral PH wrapping paper and shipped in vacuumsealed anti-static bags. A humidity indicator and desiccant should be inserted in the bags.

Table 2: Technical specifications for tileboard PCBs

#### **Scintillator Detector – SiPM Bias Currents**

|                                                                                             |            |                 |                       |                            |              |                                               |                    |          |              |              |              | CE-H: layers BH 13 |              |                |                |

|---------------------------------------------------------------------------------------------|------------|-----------------|-----------------------|----------------------------|--------------|-----------------------------------------------|--------------------|----------|--------------|--------------|--------------|--------------------|--------------|----------------|----------------|

| Bias currents per ring and                                                                  | tilahaa    | rd (9 channole  | 40\/) in uA for flu   | onco E*10012n/cm           |              | r [mm], inner                                 |                    | ring     | 38           | 39           | 40           | 41                 | 42-43        | 44-45          | 46-47          |

| bias currents per ring and                                                                  | i tileboal | ru (o channeis, | 40v) in µA for hu     | ence 5-10-15n/ch           | n-           | <del>_</del>                                  | 2594.79            | 42       |              |              |              |                    |              |                |                |

| Preliminary! Al                                                                             | LDOv2 (2   | 2 BV channels p | er ASIC), 25mA pe     | er channel max.            |              |                                               | 2539.39            | 41       |              |              |              | 310                | 220          | 160            | <u> </u>       |

|                                                                                             | 20012 (2   | e or channels p | er ristell, zantri pr |                            |              |                                               | 2483.99            | 40       |              |              | 460          | 350                | 240          | 160            |                |

|                                                                                             |            |                 |                       |                            |              |                                               | 2430.96            | 39       |              |              | 510          | 390                | 260          | 180            | 140            |

|                                                                                             |            |                 | CE-H: lay             | ers FH 9-12                |              |                                               | 2377.93            | 38       |              | 740          | 550          | 430                | 260          | 180            | 140            |

| r [mm], inner                                                                               | ring       | 34              | 35                    | 36                         | 37           |                                               | 2327.16            | 37       |              | 810          | 600          | 470                | 280          | 200            | 160            |

|                                                                                             | -          |                 |                       |                            |              |                                               |                    | 36       | 1160         | 870          | 640          | 500                | 280          | 200            | 160            |

|                                                                                             |            |                 |                       |                            |              |                                               | 2227.80            | 35       | 1230         | 930          | 690          | 530                | 300          | 220            | 180            |

| 2179.20                                                                                     | h24        |                 |                       |                            |              |                                               | 2179.20            | 34       | 1300         | 990          | 730          | 570                | 320          | 220            | 200            |

|                                                                                             |            |                 |                       |                            | 1760         |                                               | 2132.67            | 33       | 1380         | 1050         | 780          | 600                | 340          | 240            | 220            |

|                                                                                             |            |                 |                       | 2210                       | 1810         |                                               | 2086.15            | 32       | 1450         | 1120         | 820          | 640                | 340          | 260            | 220            |

|                                                                                             |            |                 | 2630                  | 2220                       | 1860         |                                               | 2041.61            | 31       | 1530         | 1180         | 880          | 670                | 380          | 280            | 260            |

|                                                                                             | L          |                 | 2640                  | 2260                       | 1940         |                                               | 1997.08            | 30       | 1610         | 1250         | 930          | 720                | 400          | 300            | 280            |

|                                                                                             |            | 3140            | 2690                  | 2330                       | 2020         |                                               | 1954.44            | 29       | 1700         | 1330         | 1000         | 760                | 420          | 320            | 300            |

|                                                                                             |            | 3210            | 2780                  | 2420                       | 2130         |                                               | 1911.80            | 28       | 1810         | 1410         | 1060         | 810                | 460          | 340            | 340            |

|                                                                                             |            | 3340            | 2910                  | 2540                       | 2250         |                                               | 1870.99            | 27       | 1920         | 1510         | 1140         | 870                | 480          | 380            | 360            |

| 1830.17                                                                                     | h12        | 3510<br>3740    | 3080<br>3280          | 2700<br>2880               | 2390 2560    |                                               | 1830.17            | 26       | 2050         | 1610<br>1730 | 1230<br>1320 | 930<br>1000        | 540<br>580   | 400            | 400            |

|                                                                                             |            | 4020            |                       |                            |              |                                               | 1791.10            | 25       | 2190         |              |              | 1000               |              | 440            | 440            |

|                                                                                             |            | 4020 4360       | 3530<br>3820          | 3100<br>3350               | 2750<br>2970 |                                               | 1752.03<br>1714.62 | 24<br>23 | 2350<br>2530 | 1860<br>2010 | 1430<br>1550 | 1080<br>1170       | 630<br>690   | 480            | 480            |

|                                                                                             |            | 4300            | 4150                  | 3640                       | 3220         |                                               | 1677.22            | 23       | 2730         | 2170         | 1690         | 1280               | 760          | 600            | 600            |

|                                                                                             |            | 5230            | 4130                  | 3980                       | 3500         |                                               | 1641.41            | 21       | 2960         | 2360         | 1840         | 1390               | 840          | 660            | 660            |

|                                                                                             |            | 5770            | 4990                  | 4360                       | 3830         |                                               | 1605.60            | 20       | 3230         | 2570         | 2010         | 1530               | 930          | 740            | 720            |

|                                                                                             |            | 6390            | 5500                  | 4790                       | 4190         |                                               | 1571.33            | 19       | 3520         | 2810         | 2210         | 1680               | 1040         | 820            | 800            |

| 1537.05                                                                                     | h0         | 7090            | 6080                  | 5290                       | 4600         |                                               | 1537.05            | 18       | 3850         | 3080         | 2430         | 1850               | 1150         | 920            | 900            |

|                                                                                             |            |                 |                       |                            |              |                                               | 1504.23            | 17       | 4220         | 3380         | 2680         | 2050               | 1290         | 1040           | 990            |

|                                                                                             |            |                 |                       |                            |              |                                               | 1471.42            | 16       | 4650         | 3720         | 2960         | 2270               | 1440         | 1170           | 1100           |

| (1): BV Current Sum per Tileboard, μA, 10°                                                  |            | 13200           | 16730                 | 16680                      | 16160        |                                               | 1440.00            | 15       | 5120         | 4110         | 3270         | 2520               | 1620         | 1320           | 1220           |

| (2): BV Current Sum per Tileboard, μA, 10°                                                  |            | 41370           | 35890                 | 31390                      | 27620        |                                               | 1408.59            | 14       | 5650         | 4540         | 3620         | 2800               | 1820         | 1480           | 1350           |

| (3): Sum (10°, μA), OLD Granularity                                                         | L          | 54570           | 52620                 | 48070                      | 43780        |                                               | 1378.52            | 13       | 6250         | 5020         | 4020         | 3130               | 2040         | 1680           | 1500           |

|                                                                                             |            |                 |                       |                            |              |                                               | 1348.45            | 12       |              |              | 4470         | 3490               | 2300         | 1890           | 1660           |

| (1) * 2.25                                                                                  |            | 29700           | 37643                 | 37530                      | 36360        |                                               | 1319.66            | 11       |              |              | 4970         | 3900               | 2590         | 2140           | 1840           |

| (2) * 2.25                                                                                  |            | 93083           | 80753                 | 70628                      | 62145        |                                               | 1290.87            | 10       |              |              | 5530         | 4360               | 2920         | 2420           | 2040           |

| (3) * 2.25, NEW Granularity                                                                 | L          | 122783          | 118395                | 108158                     | 98505        |                                               | 1263.31            | 9        |              |              | 6150<br>6850 | 4890<br>5470       | 3290<br>3710 | 2740<br>3110   | 2260<br>2500   |

| Number of ALDOv2 per Tileboard                                                              | Г          | 1               | 1                     |                            | 1            |                                               | 1235.75<br>1209.37 | °,       |              |              | 7630         | 6130               | 4190         | 3520           | 2500           |

| Number of ALDOV2 per Tileboard                                                              |            | 2               | 1                     | 1                          | 1            |                                               | 1182.99            | é        |              |              | 8500         | 6860               | 4190         | 3980           | 3070           |

| Number of ALBOV2 per Thebbara                                                               |            | 2               | -                     | -                          | -            |                                               | 1157.73            | 5        |              |              | 8500         | 0000               | 4720         | 4500           | 3400           |

|                                                                                             |            |                 |                       |                            |              |                                               | 1132.48            | 4        |              |              |              |                    |              | 5080           | 3770           |

|                                                                                             |            |                 |                       |                            |              |                                               | 1108.30            | 3        |              | 10 degree-   |              |                    |              | 5740           | 4170           |

| own here: Old Setup for J/K Boards                                                          | Г          | 10 degree-      |                       | not assembled              |              |                                               | 1084.12            | 2        |              | Tileboard,   |              |                    |              | 6480           | 4620           |

| to tab "Layer_Overview" for actual setup                                                    |            | Tileboard,      |                       |                            |              |                                               | 1060.98            | 1        |              | 1.25° tiles  |              |                    |              | 7310           | 5110           |

|                                                                                             |            | 0.834° tiles    |                       | Connector/HGC              | ROC Pos.     |                                               | 1037.83            | 0        |              |              |              |                    |              | 8230           | 5650           |

|                                                                                             | _          |                 |                       |                            |              |                                               |                    |          |              |              |              |                    |              |                | _              |

|                                                                                             |            |                 |                       | A6 - Board Type            |              |                                               |                    |          |              |              |              |                    |              |                |                |

|                                                                                             |            |                 |                       |                            |              | BV Current Sum per Tileboard                  |                    |          | 3690         | 4340         | 4180         | 3550               | 2160         | 1520           | 980            |

| lumber of ALDOv2s per Tileboard" defines the                                                |            |                 |                       | 4mm <sup>2</sup> SiPM, cas |              | BV Current Sum per Tileboard                  |                    |          | 13450        | 10460        | 7840         | 6000               | 3360         | 2520           | 2380           |

| umber of ALDOv2s with the BV section enabled                                                |            |                 |                       | 4mm <sup>2</sup> SiPM, mo  |              | BV Current Sum per Tileboard                  |                    |          | 23360        | 18590        | 14480        | 10980              | 6620         | 5200           | 5140           |

| rith the big capacitors). The ALDOV2 for the VPA                                            |            |                 |                       | 9mm <sup>2</sup> SiPM, cas | st tiles     | BV Current Sum per Tileboard                  |                    |          | 25890        | 20770        | 60650        | 47870              | 31930        | 26490          | 22300          |

| .5V) has the BV outputs disabled! So each<br>eboard has one more ALDOv2 than in this table. |            |                 |                       |                            |              | BV Current Sum per Tileboard<br>Sum (10°, μΑ) | , μA, 10°          |          | 0<br>66390   | 0<br>54160   | 0<br>87150   | 0<br>68400         | 0<br>44070   | 37340<br>73070 | 26720<br>57520 |

| ere only BV is shown!!                                                                      |            |                 |                       |                            |              | Sum (10°, μA)                                 |                    |          | 66390        | 54160        | 8/150        | 68400              | 44070        | /30/0          | 57520          |

|                                                                                             |            |                 |                       |                            |              | Number of ALDOv2 per Tile                     | board              |          | 1            | 1            | 1            | 1                  | 1            | 1              | 1              |

| New: Only 4mm <sup>2</sup> in design. BV currents of former                                 |            |                 |                       |                            |              | Number of ALDOV2 per Tile                     |                    |          | 1            | 1            | 1            | 1                  | 1            | 1              | 1              |

| 2mm <sup>2</sup> fields have been doubled                                                   |            |                 |                       |                            |              | Number of ALDOV2 per Tile                     |                    |          | 1            | 1            | 1            | 1                  | 1            | 1              | 1              |

|                                                                                             |            |                 |                       |                            |              | Number of ALDOv2 per Tile                     |                    |          | 1            | 1            | 2            | 2                  | 2            | 2              | 2              |

|                                                                                             |            |                 |                       |                            |              |                                               |                    |          |              |              |              |                    |              |                |                |

Number of ALDOv2 per Tileboard

1\*: ALDO current limit is 25mA per BV channel, 2 BV channels per ALDOV2 . There is no space on A6 for 2nd BV ALDOV2. 1 ALDO should be ok.

1\*

0

0

New: Higher Granularity and 9mm<sup>2</sup> SiPMs in FH

section. We assume that BV current only scales with number of channels: Factor 2.25

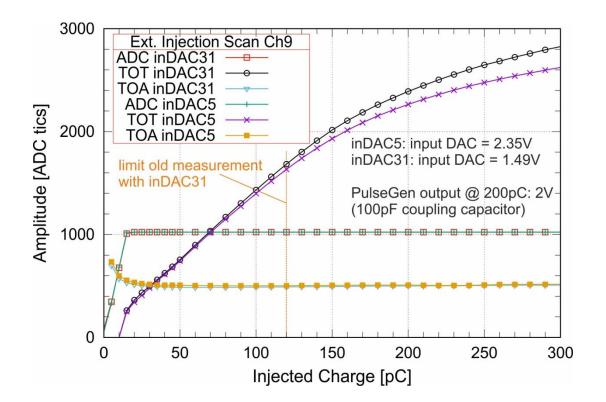

## **Tileboard 3 – Dynamic Range**

- Test of maximum expected charge (design value: 300pC) by charge injection and HGCROCv2:

- Sufficient dynamic range?

- Do the HGCROC input protection diodes fire on huge input signals and cause sharp cut-off?

- Some saturation on TOT, but no cut-off and 300pC possible.

- Dynamic range for 9mm<sup>2</sup> SiPMs: Difference to 4mm<sup>2</sup> SiPMs can be compensated by conveyor gain (HGCROC input). To be verified.

- New in upcoming HGCROCv3b: Timing for ADC and TOT/TOA can be set separately.

Dynamic Range (Charge Injection), TOT, TOA behaviour

### **Tileboard 3 – Powering Environment**