# Design and Testing of a Readout Chip with Integrated Sensor for High Energy Physics

Roua BOUDAGGA – CPPM, Aix Marseille Université, CNRS/IN2P3, Marseille, France

Supervisors : Marlon BARBERO & Patrick PANGAUD

**3rd year PhD Student Seminar, CPPM** December 19, 2024

boudagga@cppm.in2p3.fr

- 1. The Belle II Experiment

- 2. The VTX Upgrade Proposal

- 3. The TJ-Monopix2 chip

- 4. The OBELIX sensor : Optimized Belle2 pIXel sensor

- 5. Summary and next steps

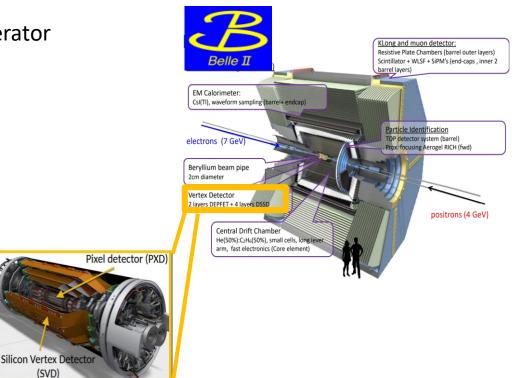

## **The Belle II Experiment**

• Located at the SuperKEKB collider in Tsukuba, Japan electron (7 GeV) • Asymmetric  $e^+$ -  $e^-$  collider at 4 / 7 GeV and  $\sqrt{s}$  = 10.58 GeV positron Target instantaneous luminosity of 6x10<sup>35</sup> cm<sup>-2</sup>s<sup>-1</sup>, currently 0.47x10<sup>35</sup> cm<sup>-2</sup>s<sup>-1</sup> Ο (4 GeV) Target integrated luminosity of **50 ab<sup>-1</sup>**, currently **0.43 ab<sup>-1</sup>** Ο Machine related beam background will increase with high luminosity Ο Interaction Belle II detector Region Efficiency, resolution and performance of data tracking could degrade with Ο higher occupancy from background Extrapolation to this target luminosity has large uncertainty and limited safety Ο margins positron ring electron / positron linear injector positron damping ring

- An upgrade of the machine elements and the detector's interaction region (IR) is required:

- $\circ$  To cope with the higher luminosity provided by the SuperKEKB accelerator

- To improve detector robustness against high backgrounds

- To provide larger safety factors for running at higher luminosity

- To increase longer term subdetector radiation resistance

- To improve overall physics performance

- $\circ$  Two different technologies compose the current Vertex Detector VXD:

- Two layers of DEPFET Pixel Detector (PXD)

- Four layers of Silicon Vertex Detector (SVD)

• A long shutdown is foreseen around early 2030 and provides the opportunity to install an upgraded detector

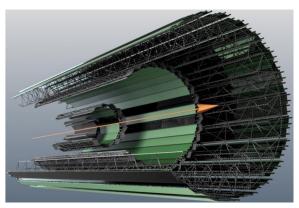

## The VTX Upgrade proposal

- A new fully pixelated CMOS detector to replace the VXD **V**X

- Improved tracking resolution and space-time granularity

- Reduced material budget  $\approx 2\%X0$  instead of 3.8%X0 (sum of all layers)

- o 5-6 straight layers with Depleted Monolithic Active CMOS Pixel Sensors (DMAPS) process

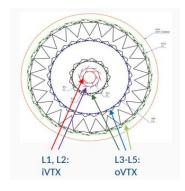

- $\circ~$  L1 and L2 (iVTX)

- All silicon ladders

- Air cooling (constrains power)

- $\circ~$  L3 to L5 (oVTX)

- Carbon fiber support frame

- Cold plate with liquid cooling

| _ |                   |      |      |      |      |               |                     |

|---|-------------------|------|------|------|------|---------------|---------------------|

|   |                   | L1   | L2   | L3   | L4   | L5            | Unit                |

| ſ | Radius            | 14.1 | 22.1 | 39.1 | 89.5 | 140.0         | mm                  |

|   | # Ladders         | 6    | 10   | 17   | 40   | 31            |                     |

|   | # Sensors         | 4    | 4    | 7    | 16   | $2 \times 24$ | per ladder          |

|   | Expected hitrate* | 19.6 | 7.5  | 5.1  | 1.2  | 0.7           | MHz/cm <sup>2</sup> |

| 1 | Material budget   | 0.2  | 0.2  | 0.3  | 0.5  | 0.8           | % X <sub>0</sub>    |

• A same monolithic CMOS pixel sensor chip for all layers : Optimized BELLE II pIXel sensor (OBELIX)

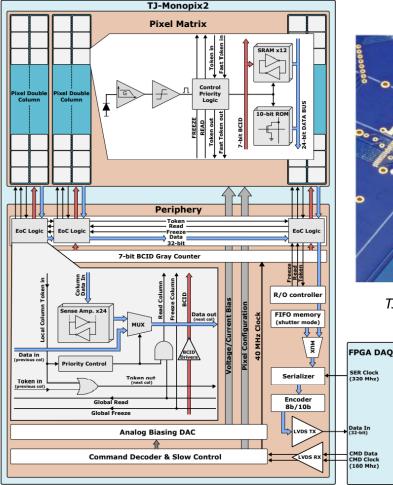

# The TJ-Monopix2 (TJM2) as prototype

TJ-Monopix2 sensor bonded on a test board

- Developed for ATLAS experiment

- FE derived from ALPIDE

- 4 FE flavors

- Column-drain R/O architecture

- DMAPS Tower Semiconductor 180 nm CMOS

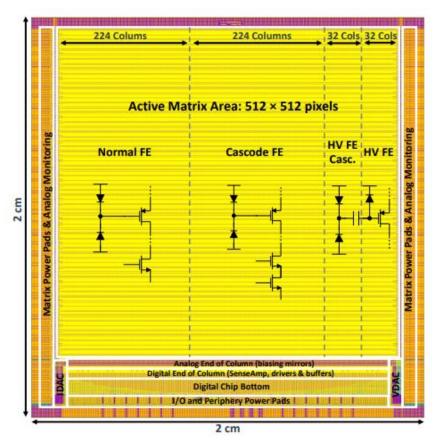

- $\circ$  2×2 cm<sup>2</sup> chip: 512×512 pixels

- $\circ~$  Pixel pitch: 33.04×33.04  $\mu m^2$

- Expected from design (simulations):

- $\circ~\sim$  100 e– min. threshold

- 5-10 e– threshold dispersion (tuned)

- $\circ$  >97% efficiency at 10<sup>15</sup>  $n_{eq}$ /cm<sup>2</sup>

- $\circ \sim 5 e-noise$

- Fully efficient with hit rate 120 MHz/cm<sup>2</sup>

- $\circ$  Power: ~ 1  $\mu$ W/pixel

### **Base-line option for OBELIX design**

## The TJM2 Testing

- Characterisation of TJ-Monopix2 (all FE) to validate key performance crucial for OBELIX design

- Full characterisation on bench:

- Threshold scans (lowest value, dispersion)

- $\circ$  Noise testing

- ToT (Time Over Threshold) calibration

- Control and data acquisition system based on the BDAQ53 setup

TJM2 setup DAQ inherited from RD53 collaboration

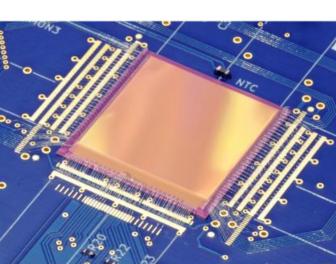

- Typical settings for operational threshold:

- $\circ$  Thresholds between 200 to 300 e-

- Average noise varies from 7 to 8 e-

- Time Over Threshold (ToT) calibration, Fe55

- Comparison with measurement and simulations

- Measurement from monitoring pixels of the analog output signal after the FE amplifier

## The TJM2 Testing

### • Full characterisation@DESY:

- Efficiency/Resolution measurements

- Radiation hardness (NIEL and TID irradiation campaigns in progress)

### • Several test beam campaigns (3-5 GeV e-)

- July 2022: Non-irradiated chips

- High threshold (500 e-)

- $\circ~$  Hit efficiency  $\sim$  99.54%, Cluster position residuals  $\sim$  9  $\mu m$

- $\circ$  July 2023: Irradiated chips at 5x10<sup>14</sup> n<sub>eq</sub>/cm<sup>2</sup>

- $\circ~$  Lower threshold  $\sim$  250-300 e-

- Good performance and high efficiency

- $\circ$  July 2024: Irradiated chips at 5x10<sup>14</sup> n<sub>eq</sub>/cm<sup>2</sup>, TID of 100 Mrad

- Good efficiency but temperature influence

Another test beam planned for 2025

Setup for testbeam – @Desy

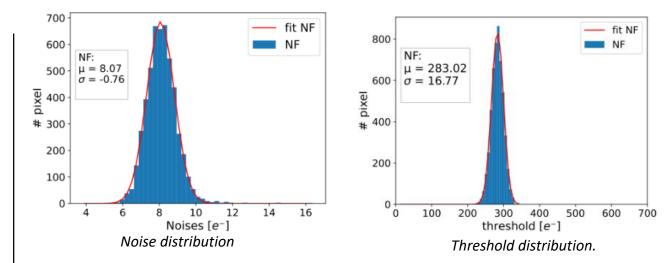

### **The OBELIX Sensor**

### Aix Marseille Universi

### **Sensor specifications:**

- Tower Semiconductor 180 nm CMOS

- Hit rate up to 120MHz/cm<sup>2</sup>

- TID tolerance: 100 MRad

- $\circ$  NIEL tolerance: 5x10<sup>14</sup> n<sub>eq</sub>/cm<sup>2</sup>/year

- $\circ$  Spatial resolution < 15 $\mu$ m

- Power < 200 mW/cm<sup>2</sup>

- Time precision < 100 ns

- $\circ~$  Trigger at 30kHz average frequency with 5-10  $\mu s$  latency

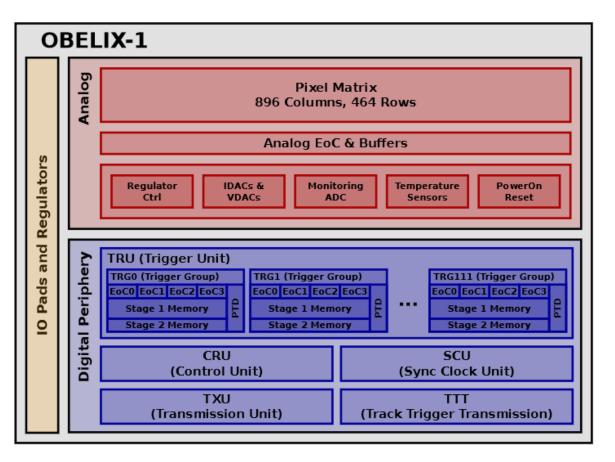

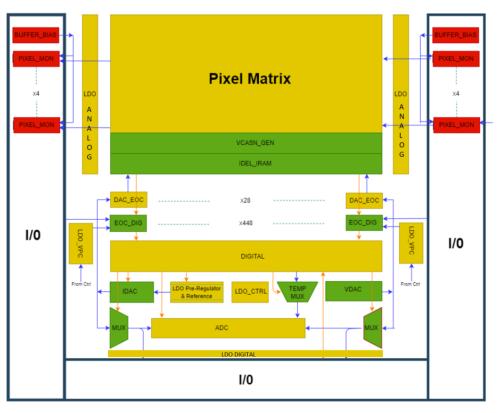

- 464 rows and 896 columns

- Overall sensor dimensions around 30.2x18.8 mm<sup>2</sup>

- $\circ~$  Pixel pitch 33x33  $\mu m^2$

- Main design is based on the TJM2 chip

### Analog

- Pixel matrix adapted from TJM2

- o Column drain architecture

- Monitoring ADC

- Temperature sensors

### **Power pads**

- Power regulators added

- Simplified system integration

### **Digital Periphery**

- Main clk-in: 170MHz

- New end-of-column adapted to Belle II trigger

- Timestamped hits stored in memories

- Read-out when timestamp matched with trigger

- Single output at 340 MHz average bandwidth

- RD53 control/readout protocol

- The OBELIX sensor inherits the performance of the pixel matrix from TJM2 sensor

- $\circ~$  The same pitch, 33  $\times$  33  $\mu m^2$ , with the same layout for the analog and digital parts

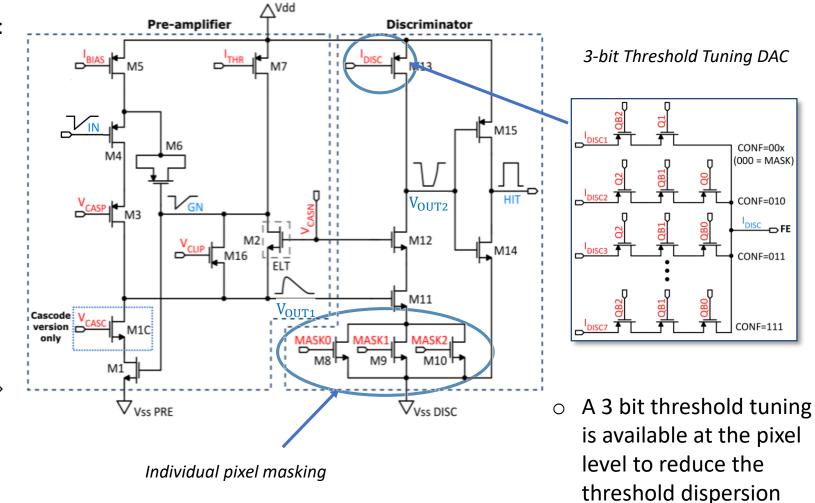

- The Matrix pixel of TJM2 is composed of 4 pixel flavors with differences in the Front-End (FE) amplifier and detector input coupling (AC or DC):

- Normal FE / Cascode FE

- HV Cascode FE / HV FE

- Based on current characterization and simulation results, 2 FE flavors are chosen for OBELIX on equal area:

- $\circ$  Cascode FE

- HV Cascode FE

#### Floorplan of TJM2 sensor

## The analog FE design

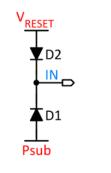

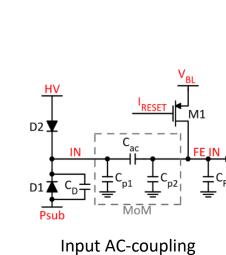

- $\circ$   $\;$  Two flavors with a cascode pre-amplifier :

- With an input DC-coupling using a forward biased diode (Cascode FE)

- With an input AC-coupling allowing higher bias voltage above 30V (HV Cascode FE)

Input DC-coupling

## The OBELIX Power management

- Power distribution is a major concern as OBELIX is larger than TJM2, leading to performance degradation

- Long linear ladders voltage drop across ladder

- On chip regulators are being developed in OBELIX to compensate the voltage drop and minimize the material budget dedicated to power distribution:

- Two analog LDO (Low Dropout) regulators will be implemented to supply the matrix from both sides

- A digital LDO in the bottom side of the chip to supply the digital blocs

- $\circ~$  A preregulator to supply LDO references generator

- A VPC (Voltage pre-charge) LDO to reset and recharge bit-lines between each read cycle

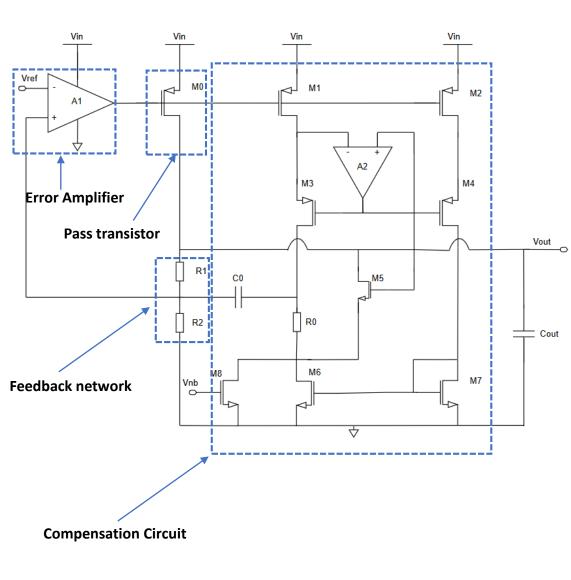

## The LDO regulator design

- Wide input supply voltage range of 2V to 3V

- Each LDO generates the output voltage of 1.8V ± 10% necessary for the technology to power the chip through the pass transistor M0

- Maximum load current of 500mA

- A compensation circuit is designed to ensure a stable output voltage

Circuit is working within specifications

Z Layout is done

Final verifications are on going

- The SuperKEKB collider is considering a major upgrade to reach a high luminosity

- Reaching the target peak luminosity requires an upgrade of the interaction region and the Vertex Detector

- A new DMAPS VTX is foreseen to improve the performance of the Belle II vertex detector

- The OBELIX sensor based on TJM2 chip with TJ180 nm technology is under development with additional features all on-chip

- Lab testing and TB campaigns on TJM2 to validate key performance crucial for OBELIX design: Good agreement between the measurements and simulations

#### • Next steps:

- Continuation of LDO design, verification and integration into the OBELIX chip which will be submitted in 2025

- Involvement in characterization and testing of the TJM2 Chip

- Participation in Beam Tests related to the TJM2 chip, scheduled in 2025

# Thanks for your attention

boudagga@cppm.in2p3.fr

a