# Development of the muon beam monitor for COMET experiment using SiC detector

OMET

K. Okabe<sup>1</sup>, Y. Fukao<sup>2</sup>, Y. Fujita<sup>2</sup>, E. Hamada<sup>2</sup>, Y. Igarashi<sup>2</sup>, T. Kishishita<sup>3</sup>, K. Kojima<sup>4</sup>, R. Kosugi<sup>4</sup>, S. Mihara<sup>2</sup>, H. Nishiguchi<sup>2</sup>, M. Shoji<sup>2</sup>, Y. Tanaka<sup>4</sup>, and Y. Yamaguchi<sup>5</sup>

SOKENDAI

<sup>1</sup>SOKENDAI, <sup>2</sup>KEK, <sup>3</sup>Univ. of Bonn, <sup>4</sup>AIST, <sup>5</sup>Univ. of Tsukuba

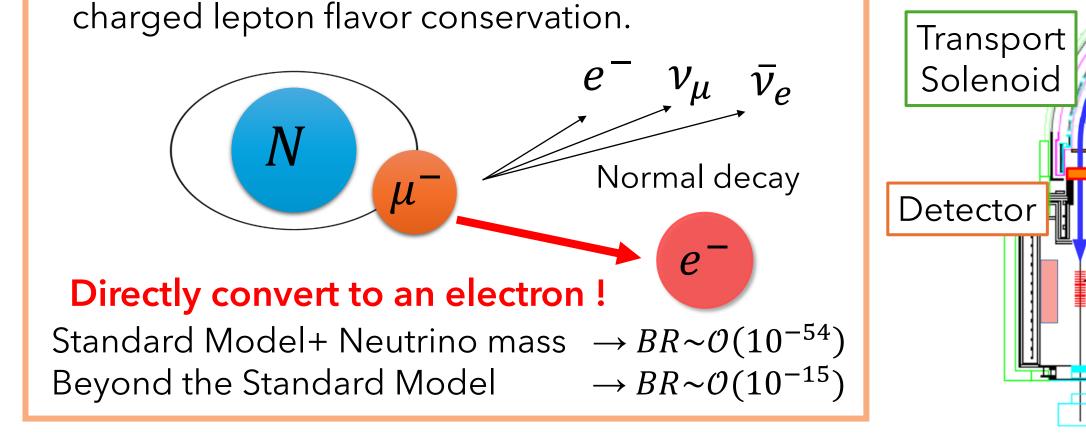

### **COMET** Experiment

- COherent Muon to Electron Transition

- $\succ$  Search for  $\mu$ -e conversion process at J-PARC Hadron Facility

- Establishing a new COMET beamline and conducting exploration using pulsed muon beam

- Experiment will be conducted in two stages, Phase-I & II

Phase-I  $\mathcal{O}(10^{-15})$ Target Experiment Sensitivity (Single event sensitivity) Phase-II  $\mathcal{O}(10^{-17})$  $\mu$ -e conversion One of the processes that violates the law of

Pulsed proton beam Prompt beam Muon lifetime Time window Signal 1.17 <sub>[us]</sub> 0.7 Time structure of COMET beamline Previous Experiment (SINDRUM-II) Upper Limit of  $7.0 \times 10^{-13}$  [1] Branching Ratio Proton Beam Transport

Pion Production Target

Muon Beam Monitor

Muon Stopping Target

Phase-I Setup

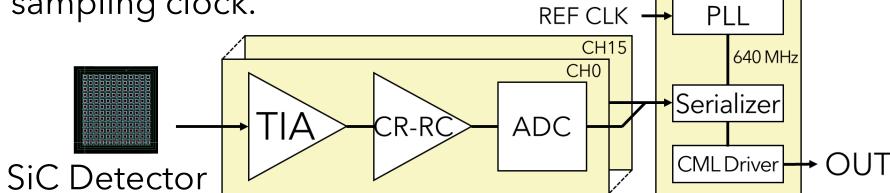

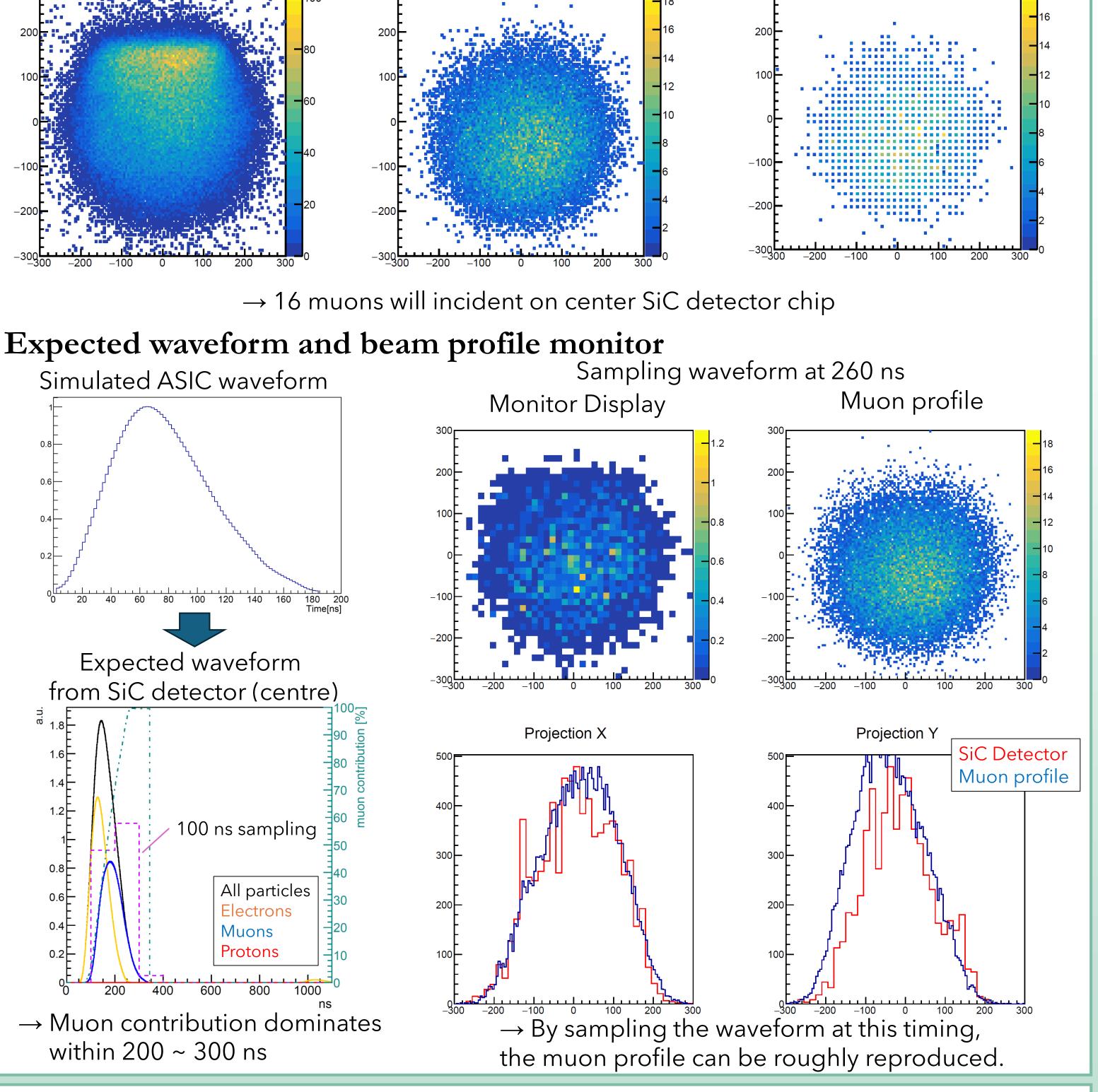

### **Readout ASIC**

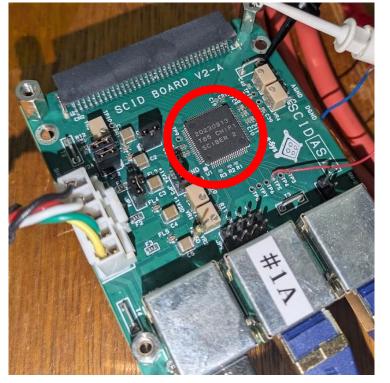

- SCIBER(Silicon Carbide readout IC for muon-BEam monitoR)

- ASIC will be used for readout electronics of the SiC detector.

- The second prototype had already been developed by KEK.

#### **Specifications**

- Consists of 16 channels per chip.

- Each channel consists of trans-impedance amplifier, CR-RC bandpass filter, and 8bit SAR ADC with 10 MHz sampling clock.

Readout board with SCIBER2 ASIC

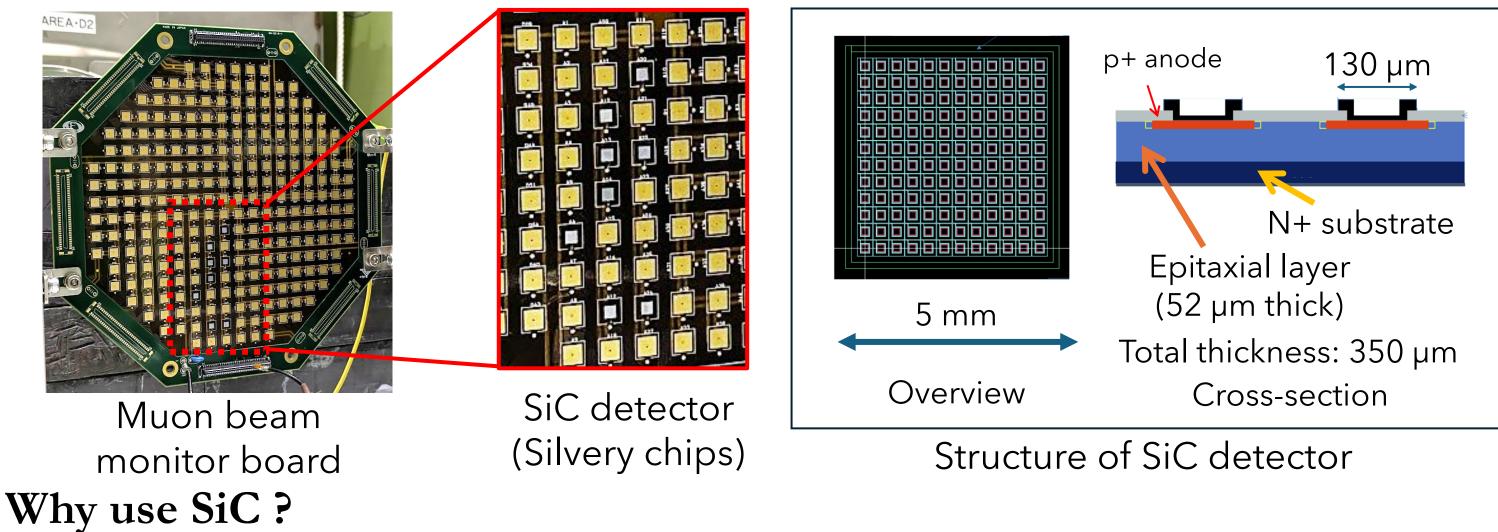

## SiC Muon Beam Monitor

#### Muon Beam Monitor

**Objects**: Measure the intensity and stability of the muon beam.

**Detector**: Made of silicon carbide (SiC) and jointly developed by KEK and AIST [2].

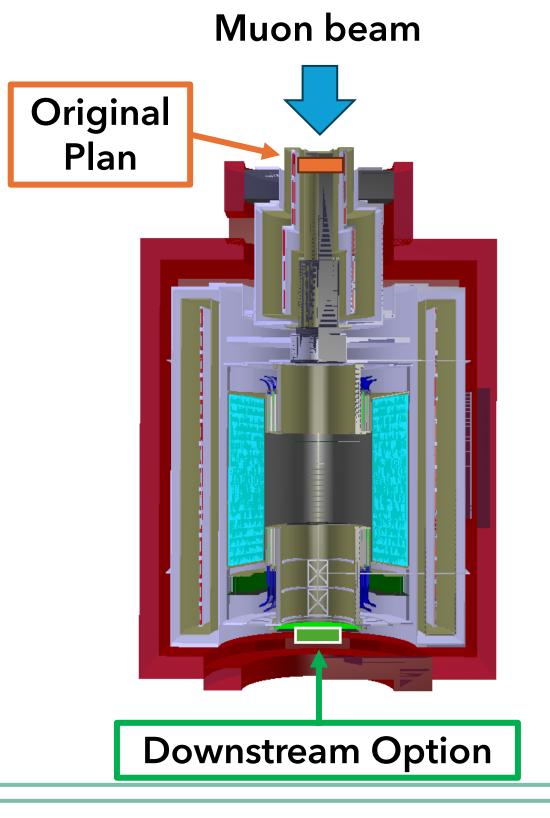

# Installation Plan

#### Original: Upstream

- Installing at the transport solenoid exit

- Sufficient pulse height

- $(\sim 57 \text{ muons / chip(centre) / bunch})$

- Small beam size, small detector size

- High radiation level

- Hard to access the beam monitor system

- Reduced muon yield

#### **Option: Downstream**

All particles

1. The second s second se second s

- Installing downstream of the primary detector system

- Low radiation level

- Easy to access the beam monitor system

- Does not affect the muon yield

- Smaller pulse height, worse S/N

- $(\sim 16 \text{ muons / chip(centre) / bunch})$

- Larger beam size, larger detector size (twice the size)

using SiC detector

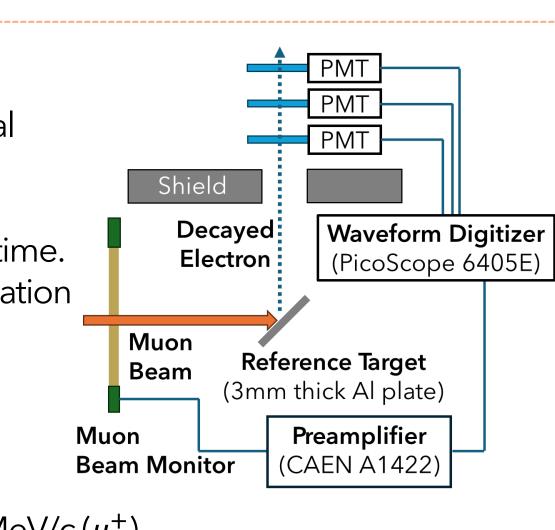

#### Simulation Study of Downstream Installation Investigation of muon beam profile and expected waveform using Geant4 based

Muons

simulation framework for COMET Experiment. Beam Profile (1 bunch =  $1.6 \times 10^7$  Protons on target) Muon profile

Muon beam monitor will be directly exposed to a high-intensity muon beam.  $\rightarrow$  Resulting in 1.6 × 10<sup>13</sup>  $n_{1MeV}$  / cm<sup>2</sup> and 1.2 MGy.

Higher Radiation tolerance is required than standard n-type silicon sensor !

Wide bandgap semiconductors have high radiation tolerance.  $\rightarrow$  SiC is an optimal choice !

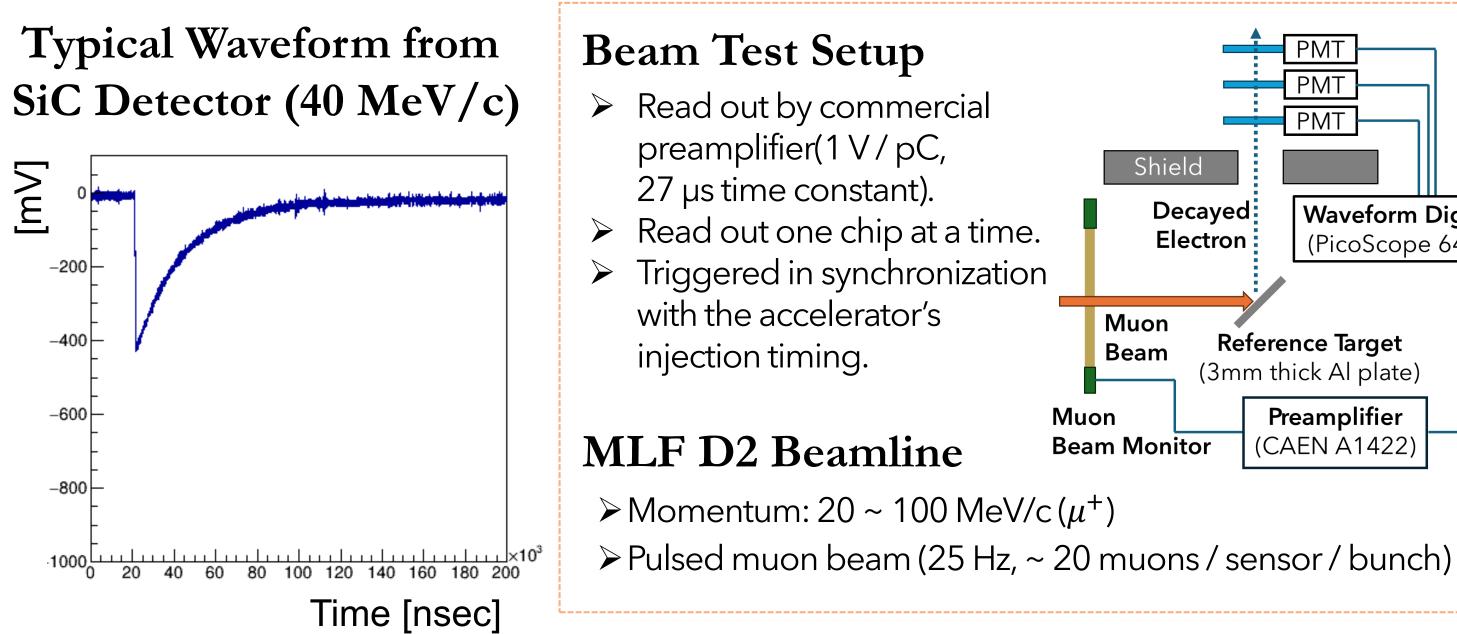

### Beam Test at MLF

Goal: Check the performance with a pulsed muon beam

- Pulse height for a single incident muon → **Detector response**

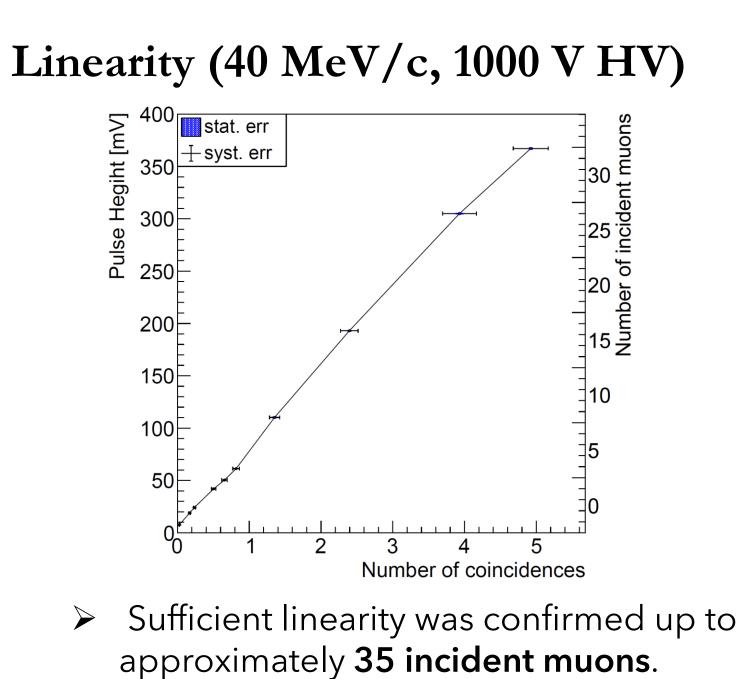

- Correlation of the number of incident muons and pulse height  $\rightarrow$  Linearity

- → Beam test was performed at MLF D2 line in June 2024.

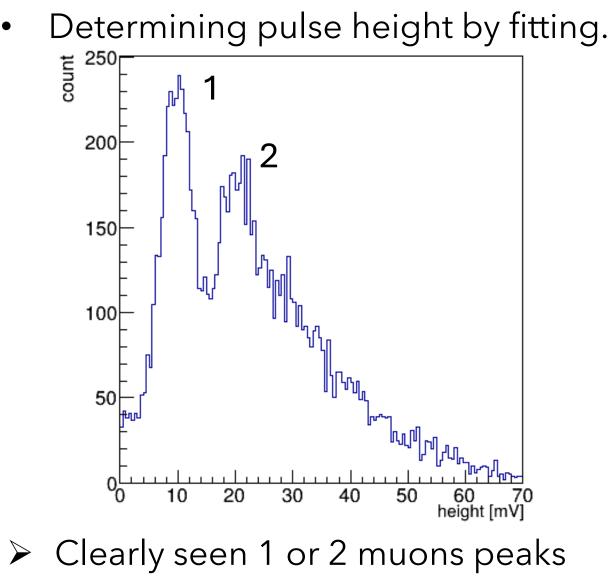

#### **Pulse Height Distribution**

### Summary

- A beam test was performed to check the performance of SiC detector, confirming sufficient linearity up to around 35 incident muons.

- Simulation study of downstream installation option revealed that approximately 16 muons are incident on center chip, and the output waveform is dominated by muons in the range of 200~300 ns.

- Determining the installation location and producing the monitor board for Phase-I. Evaluation of the next prototype ASIC will be conducted, followed by the production of the final version, aiming for the overall system completion.

[1] Wilhelm H. Bertl, et al., Eur. Phys. J. C, Vol. 47, pp. 337–346, 2006. [2] T. Kishishita et al., IEEE Trans.Nucl.Sci. 70(2023)6, 1210-1214.

This work was supported by JSPS KAKENHI Grant Numbers JP21H01117, 22H00139, JP22H01255, JP22K03657, JP25K07348.

7<sup>th</sup> – 11<sup>th</sup> July 2025 EPS-HEP 2025@ Palais Du Pharo