# A small area 11-bit SAR ADC for integrating pixel detectors at high repetition rate XFELs

Z. Ji<sup>1,2</sup>, S. Lu<sup>1,2</sup>, S. Liu<sup>4,5</sup>, T. Sun<sup>1</sup>, X. Ju<sup>3</sup>, S. Zhang<sup>3</sup>, Z. Sheng<sup>1</sup>, F. Gan<sup>1</sup>,

Z. Liu<sup>3</sup>, T. Wang<sup>4\*</sup>

- 1 Shanghai Institute of Microsystem and Information Technology (SIMIT); 2 University of Chinese Academy of Sciences;

- 3 ShanghaiTech University; 4 Shanghai Optoelectronics Science and Technology Innovation Center; 5 Fudan University

## 1. Introduction

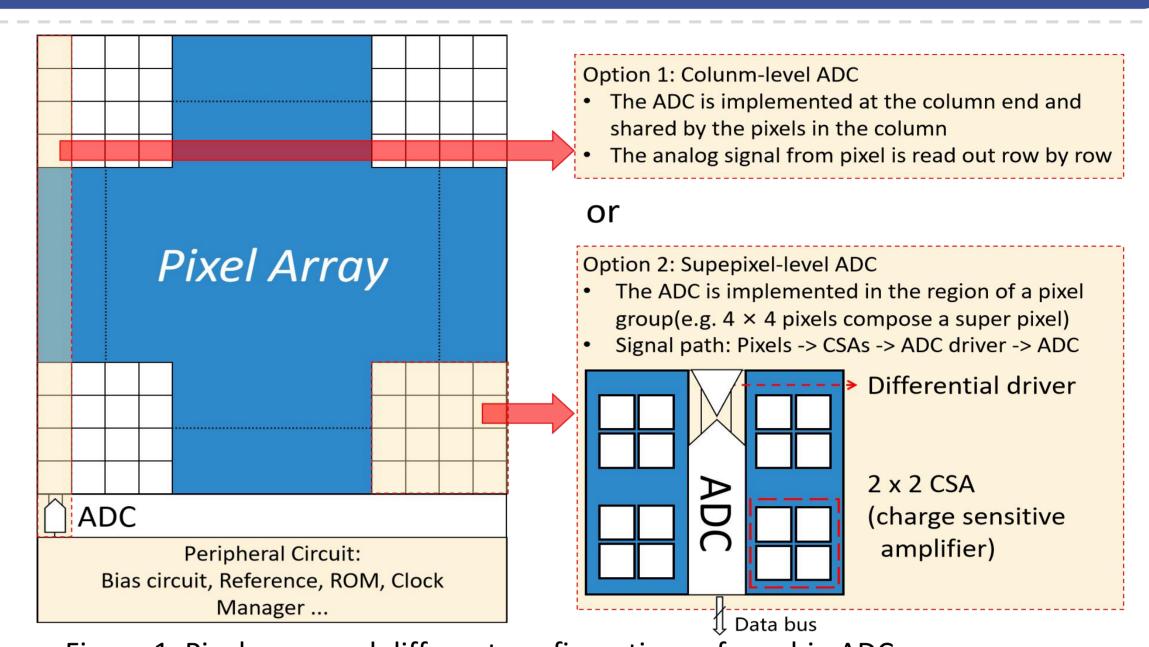

- > The charge-integrating pixel detector is one of the major enablers of new science at X-ray free electron laser (XFEL) facilities. In order to improve the frame rate of the pixel detector to match the repetition rate of the laser machine, a digital readout architecture is essential<sup>[1]</sup>, which necessitates an ADC with high speed and high resolution to satisfy the requirements of frame rate and dynamic range. As illustrated in Figure 1, there are commonly two ways for on-chip digitization: column-level ADC<sup>[2]</sup> and superpixel-level ADC<sup>[3]</sup>.

- Since successive approximation register(SAR) ADC is characterised by small area and low power consumption, this work proposes a SAR ADC designed for next generation X-ray pixel detectors, which can be implemented as either a column-level ADC or a superpixel-level ADC.

#### Figure 1. Pixel array and different configurations of on-chip ADC

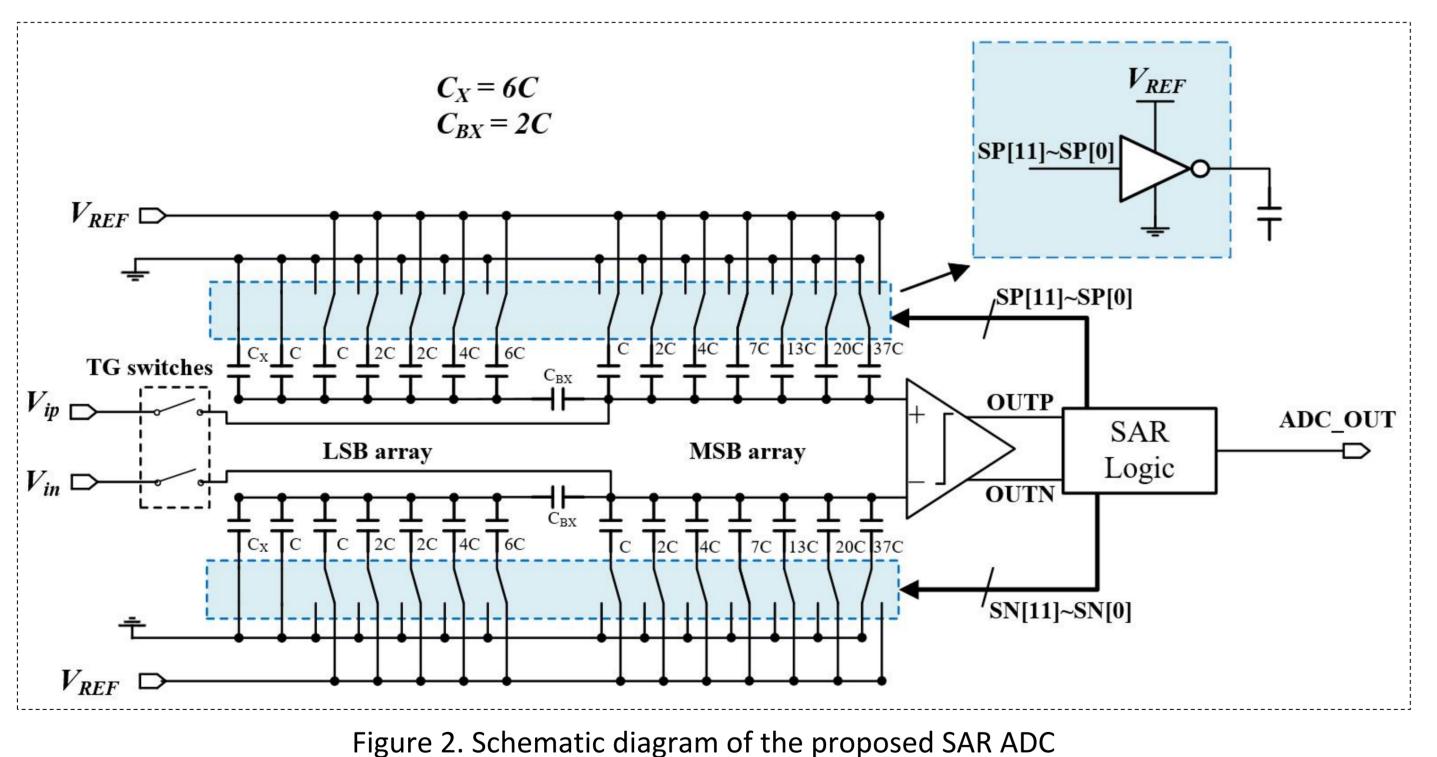

## 2. ADC Design

- Resolution: 11-bit Architecture: SAR ADC

- A bridge capacitor splits the CDAC and attenuate the weights of LSB (least significant bit) array, which can reduce the core area significantly

- The attenuation factor  $\beta$  can be expressed as:

$$\beta = \frac{C_{BX}}{C_X + C_{LSB} + C_{BX}}$$

A non-binary radix with redundancy, allowing for correction of the missing level errors

| Table 1. CDAC implementation |     |     |     |    |    |    |    |                 |   |   |   |   |   |                |

|------------------------------|-----|-----|-----|----|----|----|----|-----------------|---|---|---|---|---|----------------|

| Bit                          | 11  | 10  | 9   | 8  | 7  | 6  | 5  | C <sub>BX</sub> | 4 | 3 | 2 | 1 | 0 | C <sub>x</sub> |

| Number of unit capacitors    | 37  | 20  | 13  | 7  | 4  | 2  | 1  | 2               | 6 | 4 | 2 | 2 | 1 | 6              |

| Weight                       | 444 | 240 | 156 | 84 | 48 | 24 | 12 | -               | 6 | 4 | 2 | 2 | 1 | 6              |

- A custom-made Metal-Oxide-Metal (MOM) unit capacitor of  $\sim$  10 fF

- A StrongArm latch as the comparator

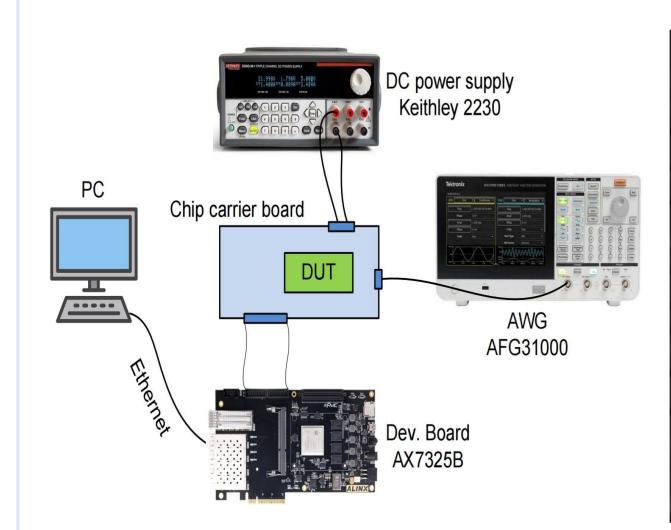

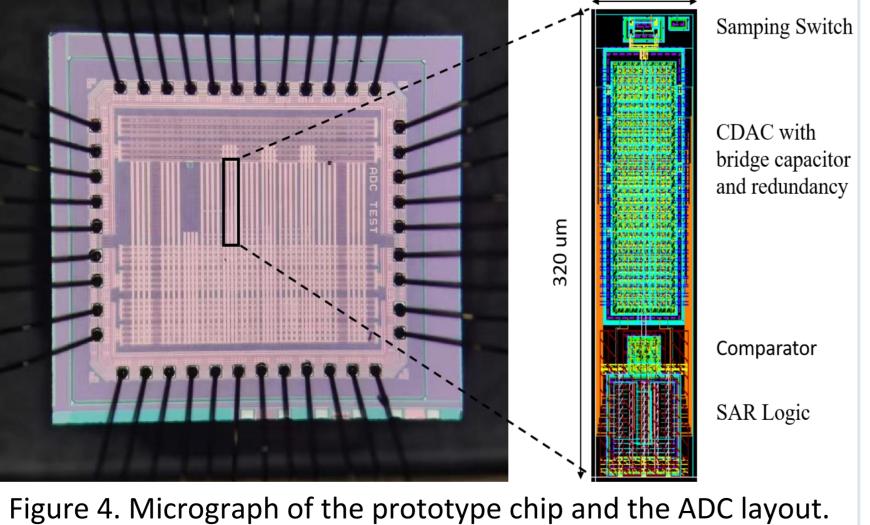

## 3. Setup and ADC core

Figure 3. The measurement setup.

- Core power supply: 1.2 V

- Reference voltage: 1.2 V

- > Technology: 130 nm CMOS process

- $\rightarrow$  ADC core dimension: 320  $\times$  80  $\mu$ m<sup>2</sup>

### 4. Results

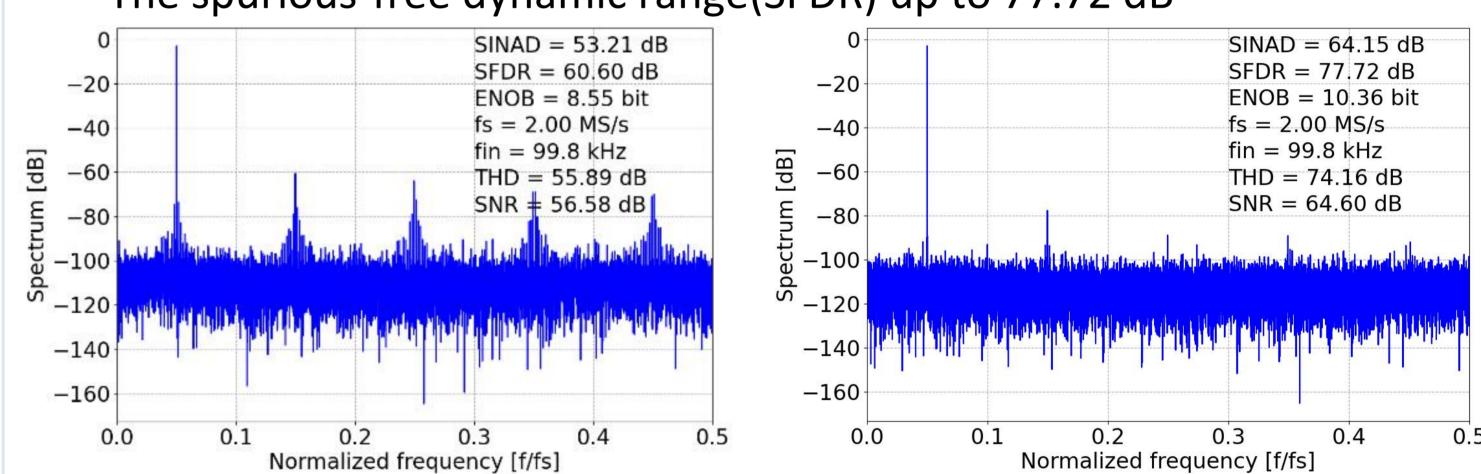

- > The result before calibration:

- The bridging CDAC structure is sensitive to capacitor mismatches and parasitics

- The mesured effective number of bit (ENOB) is 8.55-bit

- ➤ Use a simple calibration<sup>[4]</sup> to correct the missing level errors:

- This calibration is statistically-based and no-additional circuit is needed

- The ENOB up to 10.36-bit

- The spurious-free dynamic range(SFDR) up to 77.72 dB

Figure 5. Measured spectra and dynamic performance before (left) and after (right) the calibration.

- Dynamic performance has been measured at sampling rates ranging from 0.5 MS/s to 2 MS/s at an input frequency of ~ 100 kHz

- Core power consumption is estimated to be 53 µW at a sampling rate of 2 MS/s, figure-of-merit (FoM) to be 20.2 fJ/conversion-step

Table 2. Measured dynamic performance after calibration and power consumption versus sampling rate

| Characterization<br>Fs [MS/s] | SINAD [dB] | ENOB [bit] | SFDR [dB] | -THD [dB]            | SNR [dB] | Power [uW] |

|-------------------------------|------------|------------|-----------|----------------------|----------|------------|

| 0.5                           | 65.57      | 10.60      | 79.27     | 75 <mark>.</mark> 82 | 66.00    | 13.36      |

| 1.0                           | 64.44      | 10.41      | 78.33     | 74.88                | 64.85    | 26.47      |

| 2.0                           | 64.15      | 10.36      | 77.72     | 74.16                | 64.60    | 52.61      |

## 5. Conclusion and Outlook

- > The prototype chip has a small area and a high power efficiency, and the ENOB achieves 10.36-bits at a sampling rate of 2 MS/s.

- > The calibration requires only a reference input, with no need for additional circuit, making it suitable to correct the ADC in pixel array.

- > The chip with a sampling rate of 2 MS/s is able to enhance the readout frame rate up to 125 kHz for the superpixel structure (one ADC is shared by a  $4 \times 4$  pixel group).

#### References

- 1. D. Doering et al., DOI: 10.1109/NSS/MIC42677.2020.9507754

- 2. G. Blaj, et al., DOI: https://doi.org/10.1063/1.4952884

- 3. A. Marras et al., DOI: https://doi.org/10.1016/j.nima.2022.167814

- 4. A.H.T. Chang, Ph.D. thesis, http://dspace.mit.edu/handle/1721.1/7582