# caeleste (

# Survey of sub-electron noise CMOS image sensors

Prayag Wakale<sup>1,2</sup>, Bart Dierickx<sup>1</sup>, Filip Tavernier<sup>2</sup>

Presented at PIXEL2024

November 2024 Strasbourg

<sup>&</sup>lt;sup>1</sup> Caeleste, Mechelen, Belgium

<sup>&</sup>lt;sup>2</sup> MICAS, KU Leuven, Belgium

## Outline

caeleste

- Motivation: why ultra-low noise?

- Ultra-low noise non-{CMOS image sensors}

- Introduction to CMOS image sensors

- Read noise to reach photon counting performance

- Which optimizations are needed?

- Low noise readout techniques

- Literature survey

- Floating Transfer Gate (FTG) pixel

- Overview table

- References

## Motivation: why ultra-low noise?

#### Astronomy

- Observation of distant faint planets and stars in dark background.

- Ground-based spectroscopy of distant bodies, exoplanets.

#### Medical and Life science

- Study cells, genes and micro-organisms with fluorescence microscopy.

- Analysis of chemical compounds with Raman spectroscopy.

#### Quantum sensors

- Measurement of spatial correlation in-between photons.

## Ultra low noise non-{CMOS image sensors} 10

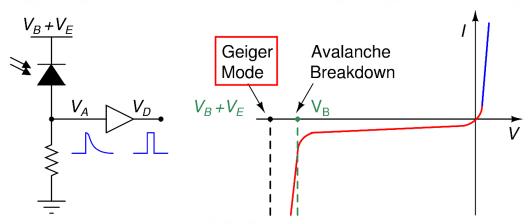

#### **SPAD (Single Photon Avalanche Diode)**

SPAD frontend circuit and I-V curve

#### Pros:

- Single photon detection

- Very high timing resolution (pico-sec)

#### Cons:

- Dark counting and after-pulsing

- Dead time of a few nsec to 100 nsec

- High voltage is needed for operation (20-25 V)

- Large pixel and low fill factor

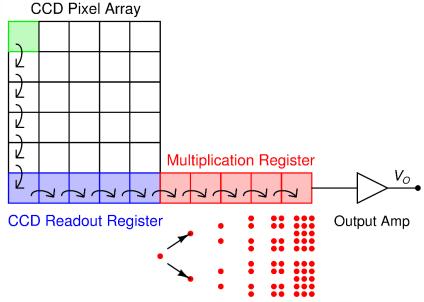

#### **EMCCD (Electron Multiplication Charge Coupled Devices)**

Pros:

- EMCCD block diagram

- High gain before Q-V conversion (usually up to 1000x)

- Excess noise due to the stochastic multiplication process

- Multiplication gain aging

- High voltage is needed for electron multiplication (50 V)

- Extra cooling to reduce the dark current

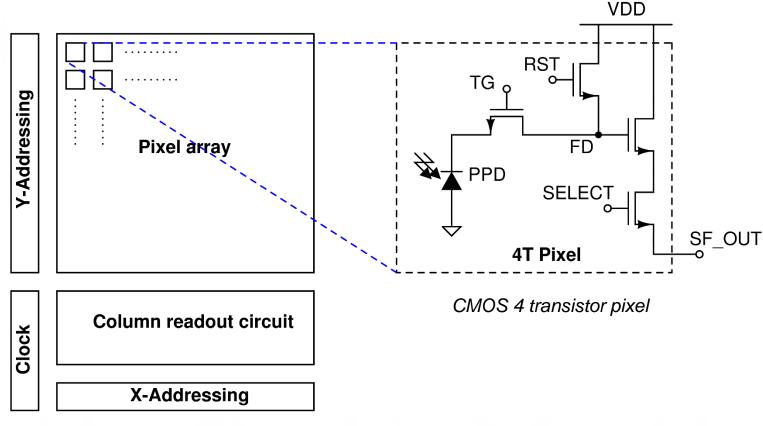

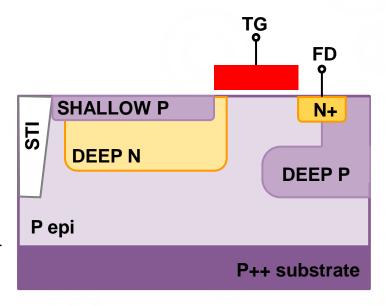

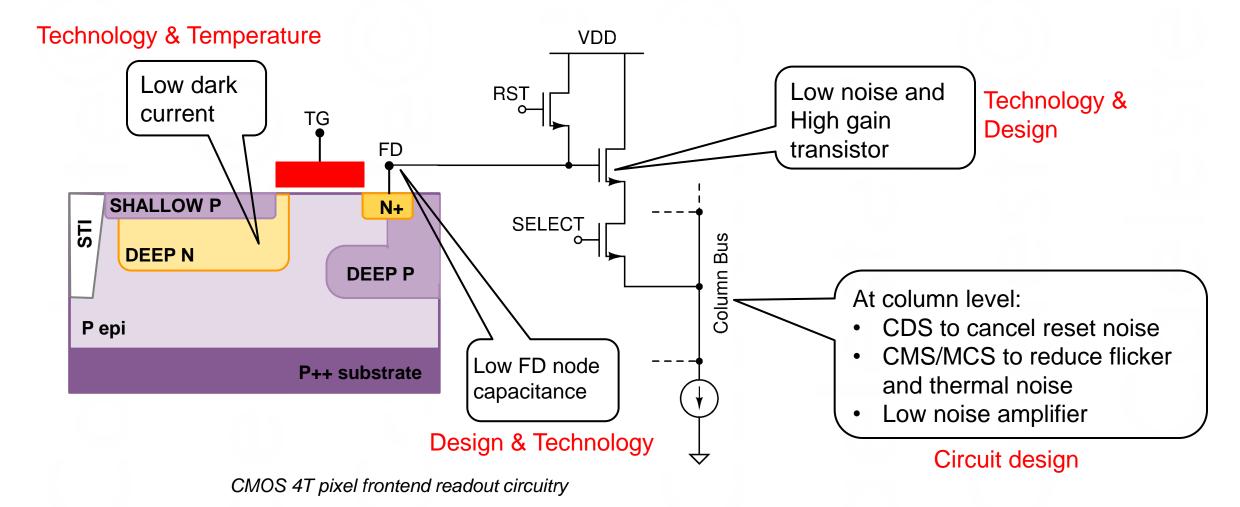

## CMOS image sensors

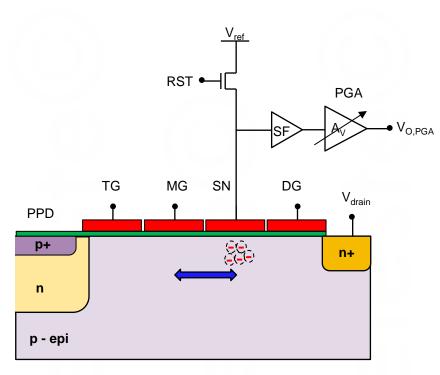

Pinned photo-diode device structure

CMOS image sensor block diagram

Typical measures to reduce noise:

- 1. Low dark current for low Dark Current Shot Noise (DCSN)

- 2. Correlated Double Sampling (CDS) for reset noise cancellation

- 3. High Charge to Voltage conversion Factor (CVF)

PPD - Pinned Photodiode

TG - Transfer Gate

RST - Reset

FD - Floating Diffusion

SF - Source Follower

4T - 4 Transistor pixel

STI - Shallow Trench Isolation

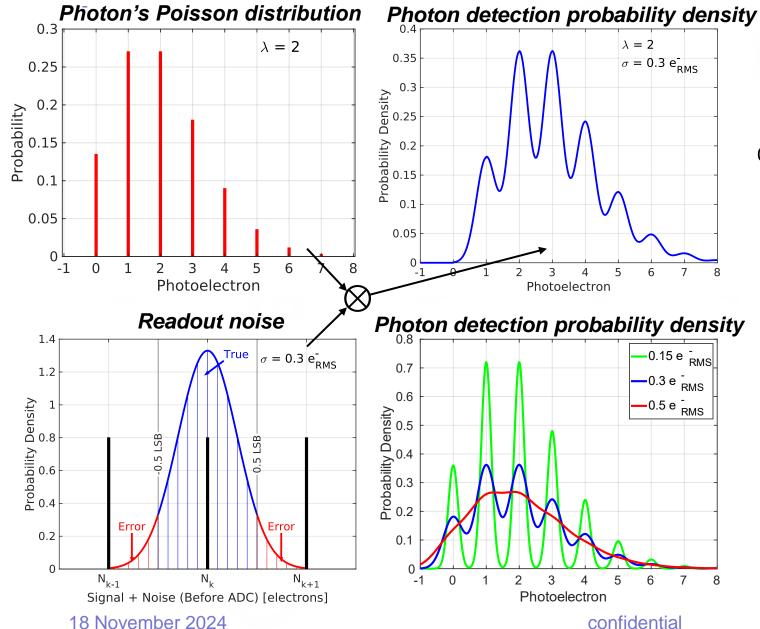

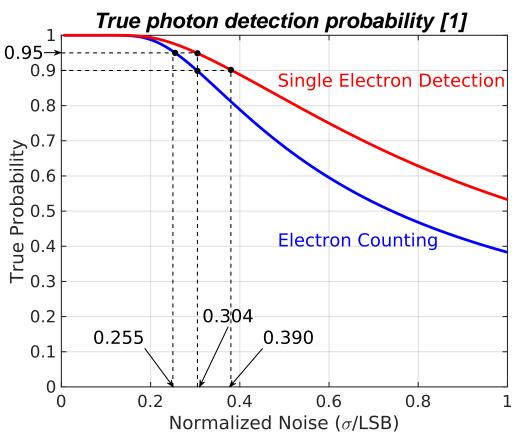

## Read noise to reach photon counting performance

$\lambda$  – average no. of incoming photons  $\sigma$  – readout noise standard deviation in  $e_{RMS}^-$

18 November 2024

## Which optimizations are needed?

CDS - Correlated Double Sampling

CMS - Correlated Multiple Sampling

MCS - Multiple Correlated Sampling

FD – Floating Diffusion

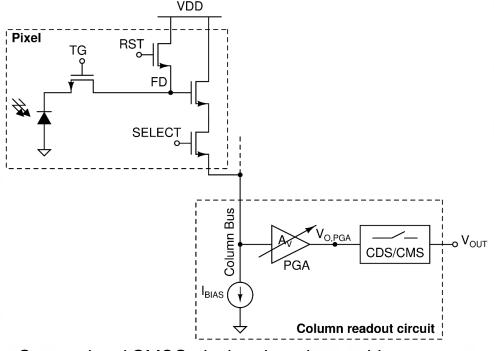

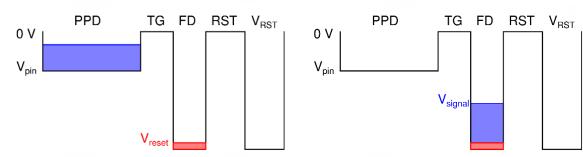

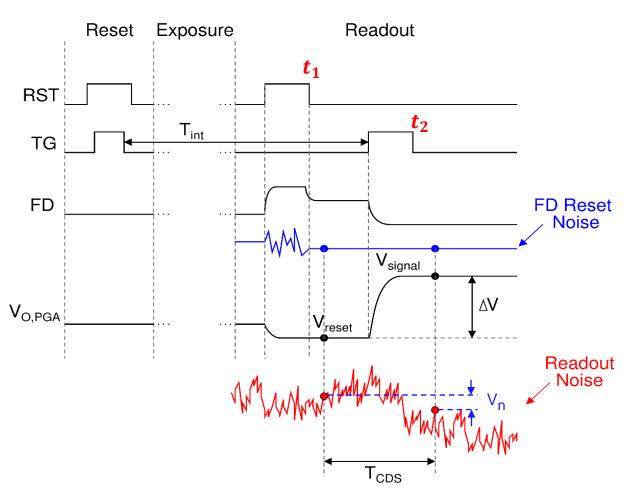

## Correlated Double Sampling (CDS) Caeleste

Conventional CMOS pixel and readout architecture

(a) Integration and FD node reset  $(t_1)$

(b) Photocharge transfer  $(t_2)$

Potential diagram during CMOS pixel photo-charge readout

Timing diagram for CMOS pixel CDS readout [11]

FD - Floating Diffusion

PGA – Programmable Gain Amplifier

CDS - Correlated Double Sampling

CMS - Correlated Multiple Sampling

18 November 2024 confidential

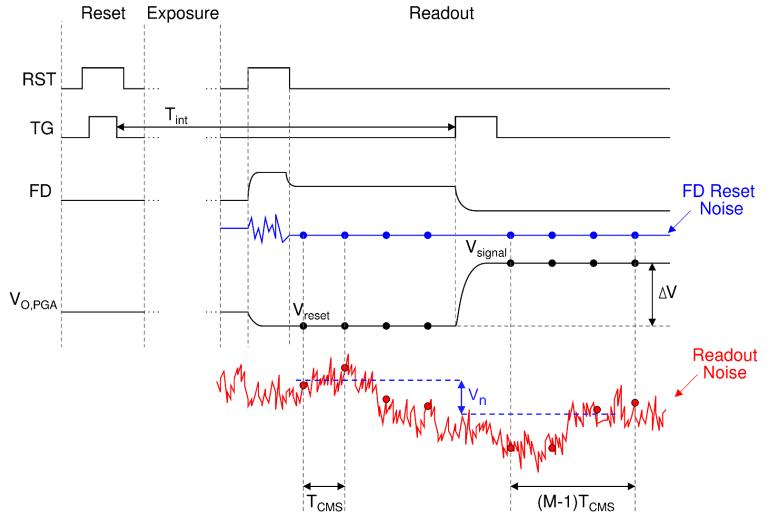

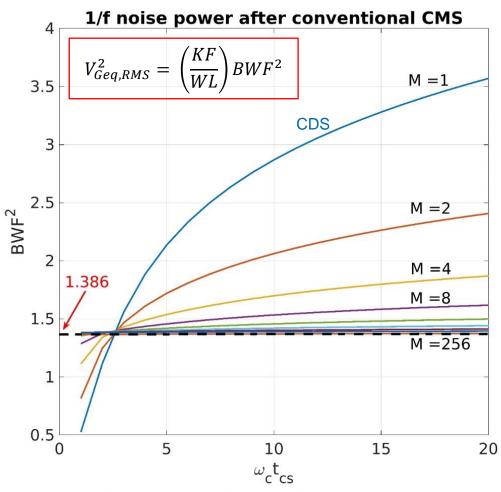

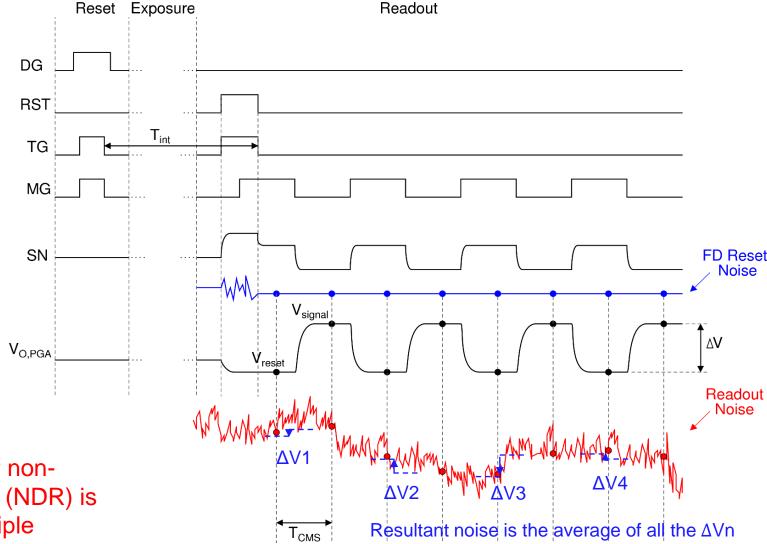

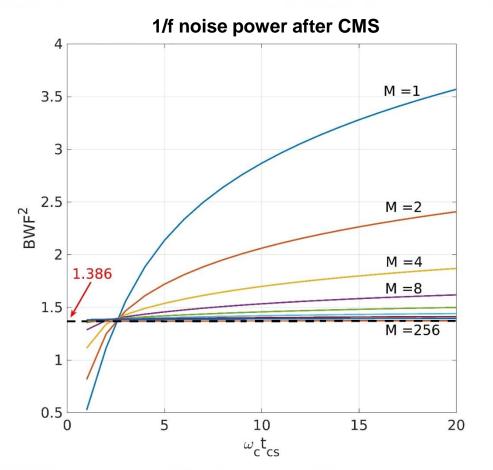

## Correlated Multiple Sampling (CMS) Caeleste

confidential

Timing diagram for CMOS pixel CMS readout [11]

Normalized flicker noise power after CMS [12]

BWF - Bandwidth Factor

$\omega_c$  – Cutoff frequency

$t_{CS}$  - Sampling time period  $(T_{CMS})$  9

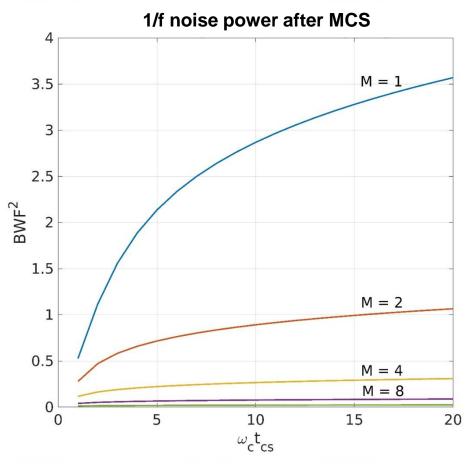

## Non-Destructive Readout / Multiple Correlated Sampling

CCD inspired CMOS skipper pixel [8]

PPD - Pinned Photo Diode

CCD - Charge Coupled Device

TG - Transfer Gate

MG - Modulation Gate

SN - Sense Node

DG - Drain Gate

RST - Reset Gate

SF - Source Follower

PGA - Programmable Gain Amplifier

NOTE: This form of nondestructive readout (NDR) is referred to as "Multiple Correlated Sampling" (MCS) in further slides

Timing diagram for CMOS skipper pixel non-destructive readout

## Literature Survey

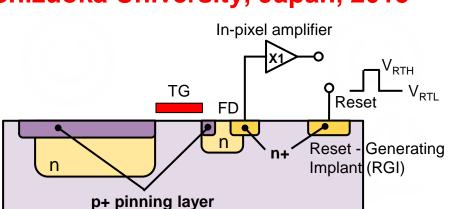

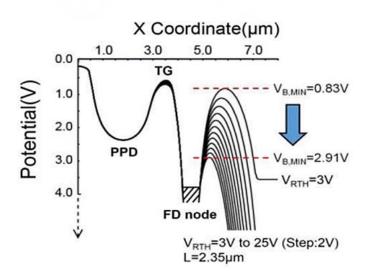

#### Reset Gate less CIS (0.27 $e_{RMS}^-$ ) Shizuoka University, Japan, 2015

p - epi

Pixel device structure [2]

Potential profile during punch-through reset [2]

## caeleste

| Optimization area      | Technique used           | Impact                        |  |

|------------------------|--------------------------|-------------------------------|--|

| Technology             | 110 nm CIS with PPD      |                               |  |

| $C_{FD}$ reduction     | Reset generating implant | CVF: 220<br>µV/e <sup>-</sup> |  |

| Temperature            | -10 °C                   | Low I <sub>dark</sub>         |  |

| Transistor selection   | N.A.                     |                               |  |

| Column readout circuit | CMS                      | Low read noise                |  |

#### **Pros:**

Reduced coupling capacitance at FD node (High CVF)

- High voltage (25 V) required for reset

- Possibility of image lag due to p+ implant near to FD n implant

- Slow reset operation

- Low pixel fill factor

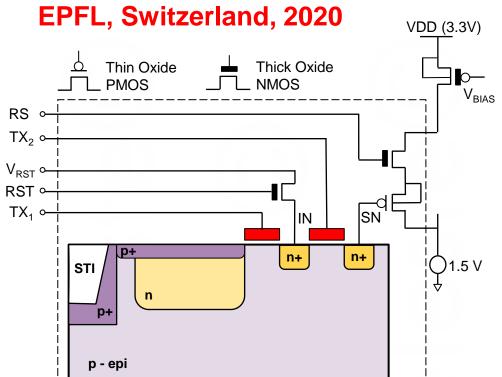

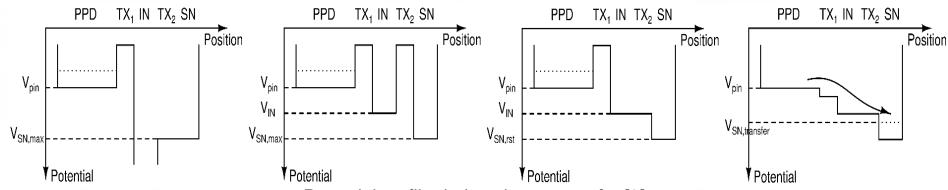

Pixel device structure and schematic [3]

| Optimization area      | Technique used               | Impact                     |

|------------------------|------------------------------|----------------------------|

| Technology             | 180 nm CIS with PPD          |                            |

| $C_{FD}$ reduction     | Reset with additional $TX_2$ | CVF: 250 µV/e <sup>-</sup> |

| Temperature            | 27 °C                        |                            |

| Transistor selection   | Thin oxide PMOS as SF        | Cap: 0.4 fF                |

| Column readout circuit | CMS (Digital,4)              | Low read noise             |

#### **Pros**:

- Reduced coupling capacitance at FD node (High CVF)

- Prone to image lag due to intermediate potentials

- Low fill factor (PMOS inside pixel)

Potential profile during charge transfer [3]

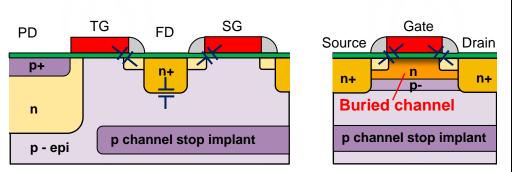

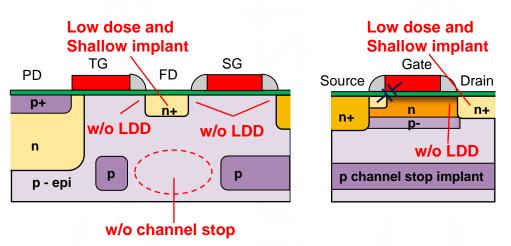

#### A linear response CIS (0.46 $e_{rms}^-$ ) Tohoku University, Japan, 2015

Conventional PPD and SF cross-section [4]

Optimized PPD and SF cross-section [4]

| Optimization area      | Technique used                        | Impact                        |  |  |

|------------------------|---------------------------------------|-------------------------------|--|--|

| Technology             | 180 nm CIS with PPD                   |                               |  |  |

| $C_{FD}$ reduction     | Low implant dose & shallow FD w/o LDD | CVF: 232<br>µV/e <sup>-</sup> |  |  |

| Temperature            | 27 °C                                 |                               |  |  |

| Transistor selection   | Buried channel NMOS as SF             | Low 1/f noise                 |  |  |

| Column readout circuit | Floating capacitor load               | Low read noise                |  |  |

#### **Pros**:

- Overall reduction in FD node capacitance

- Lower flicker noise due to buried channel NMOS as SF

- Low noise due to switched capacitor load at SF output

- Possibility of image lag due to removed LDD

- Prone to FD leakage due to removed channel stop beneath

- Settling error due to sampling time jitter

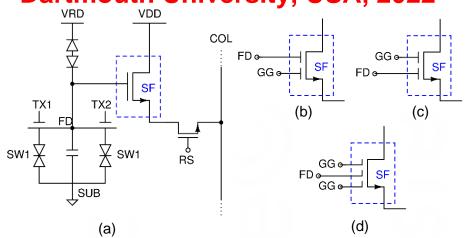

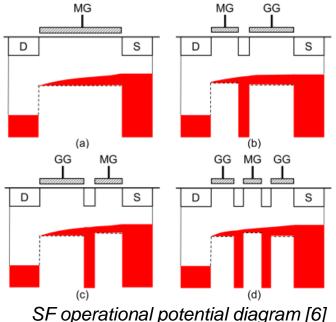

#### Multi-Gate Source Follower QIS (0.17 $e_{rms}^-$ )

caeleste

#### **Dartmouth University, USA, 2022**

| Optimization area      | Technique used             | Impact                     |  |

|------------------------|----------------------------|----------------------------|--|

| Technology             | 45/65 nm stacked BSI CIS   |                            |  |

| $C_{FD}$ reduction     | Small Modulation Gate (MG) | CVF: 700 μV/e <sup>-</sup> |  |

| Temperature            | -                          |                            |  |

| Transistor selection   | Buried channel devices     | Low 1/f noise              |  |

| Column readout circuit | CDS + Amplification        | Low read noise             |  |

Low 1/f noise High W\*L

High CVF

Lower  $C_{FD}$

Lower W\*L

**VS**

Jot device structure [13]

Results based on TCAD simulations and spectrum analyzer data.

Pixel characterization is needed!

#### **Research Questions:**

- 1. Physics behind obtained results?

- 2. Optimum gap size between gates?

- 3. Optimum value of GG bias?

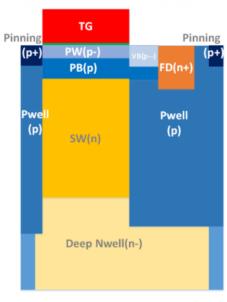

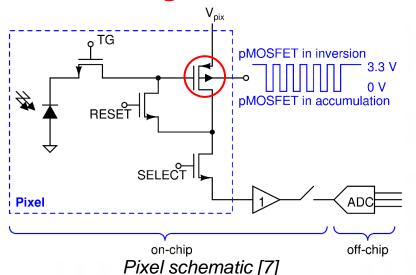

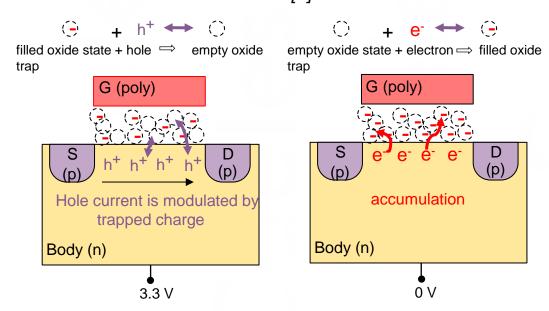

#### Inversion-Accumulation cycling CIS (0.34 $e_{RMS}^-$ )

Caeleste, Belgium, 2015

| Optimization area    | Technique used                               | Impact                        |  |

|----------------------|----------------------------------------------|-------------------------------|--|

| Technology           | 180 nm CIS with PPD                          |                               |  |

| $C_{FD}$ reduction   | -                                            |                               |  |

| Temperature          | - 40 °C                                      | Low I <sub>dark</sub>         |  |

| Transistor selection | PMOS as CS amplifier                         | Low 1/f noise                 |  |

| Readout circuit      | CTIA while modulating inversion-accumulation | CVF: 400<br>µV/e <sup>-</sup> |  |

caeleste

#### **Pros**:

- Flicker noise reduction with inversion-accumulation cycling

- High CVF due to CTIA gain

#### Cons:

- Very high number of samples required (Low FPS)

- Cooling is needed to lower the dark current

- Low pixel fill factor (PMOS inside pixel)

Inversion-Accumulation cycling [7]

18 November 2024 confidential 16

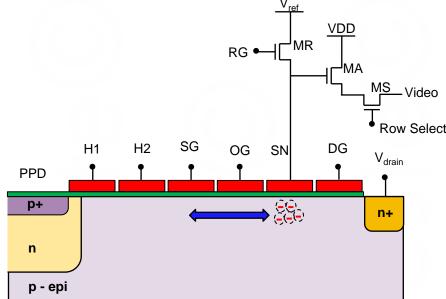

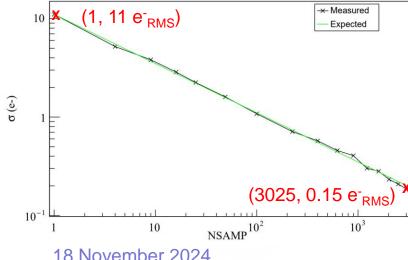

### Skipper in CCD - CMOS CEI, Open University, UK 2020

caeleste

Skipper in CCD - CMOS ,NU South CONICET, Argentina, 2024

| Optimization area      | Technique used | Impact                |

|------------------------|----------------|-----------------------|

| Technology             | CIS with CCD   | Skipper CCD           |

| $C_{FD}$ reduction     | -              |                       |

| Temperature            | -155 °C        | Low I <sub>dark</sub> |

| Transistor selection   | NMOS           | High SF Gain          |

| Column readout circuit | NDR + MCS      | Low noise             |

Pixel device structure and schematic [8]

#### **Pros:**

- CCD originating non-destructive readout in CMOS

- Readout noise can be reduced to very low levels with multiple correlated samples

#### Cons:

- Low fill factor due to multiple poly-silicon gates

- Very high number of samples to reach desired noise level (Low FPS)

- Cooling is required to lower the dark current

18 November 2024 confidential

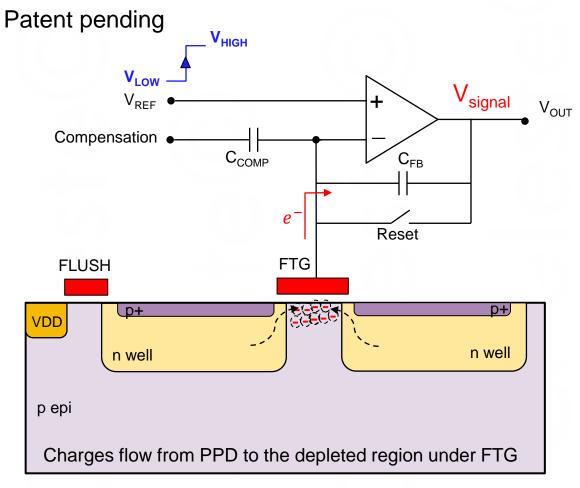

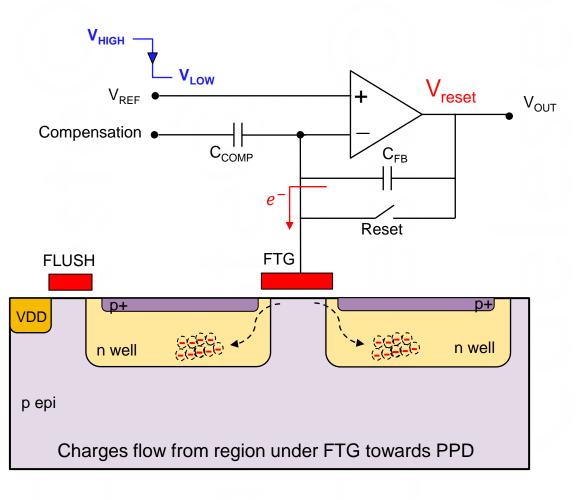

## Floating Transfer Gate CIS Caeleste, Belgium, 2024

- By modulating the reference voltage in multiple cycles, taking multiple samples for reset and signal voltages in a non-destructive manner and averaging, the noise can be reduced to a sub-electron level with no lower limits.

- Compensation capacitor and voltage are required to compensate the crosstalk of CTIA output and reference input

## Overview table

| Reference             | [2]             | [4]         | [7]             | [3]           | [5]          | [6]           | [8]         | [Ongoing work]    |

|-----------------------|-----------------|-------------|-----------------|---------------|--------------|---------------|-------------|-------------------|

|                       | Shizuoka        | Tohoku      | Caeleste        | EPFL          | CEI          | Dartmouth     | CONICET     | Caeleste          |

| Year of               | 2015            | 2015        | 2015            | 2020          | 2020         | 2022          | 2024        | 2024              |

| publication           |                 |             |                 |               |              |               |             |                   |

| Noise ( $e_{rms}^-$ ) | 0.27            | 0.46        | 0.34            | 0.32          | NA           | 0.17          | 0.15        | Not available yet |

| Pixel circuit         | Reset           | SF readout  | CTIA with       | 5T pixel with | CCD          | Pixel shared  | CCD skipper | Floating Transfer |

| topology              | gateless pixel  |             | modulated bulk  | SF readout    | skipper with | FD with SF    | with SF     | Gate (FTG) pixel  |

|                       | with SF         |             |                 |               | SF readout   | readout       | readout     |                   |

|                       | readout         |             |                 |               |              |               |             |                   |

| Circuit               | High CG         | High CG     | Switched bulk   | High CG       | NDR (MCS)    | Multi-gate SF | NDR (MCS)   | NDR (MCS)         |

| operation             | pixel           | pixel       | biasing of in-  | pixel         |              | with high CG  |             |                   |

| technique             |                 |             | pixel amplifier |               |              | pixel         |             |                   |

| Device /              | Reduction in    | Low doping, | Standard CIS    | Additional TX | CCD          | Low FD        | CCD skipper | Floating TG       |

| technology            | C <sub>FD</sub> | Shallow FD  |                 | gate for the  | skipper in   | Capacitance,  | in CMOS     | island in PPD     |

| optimizations         | capacitance     | junction    |                 | reset         | CMOS         | and SF        |             |                   |

|                       |                 |             |                 |               |              | modification  |             |                   |

| technology            | $Low V_{th}$    | Buried      | PMOS as         | Thin oxide    | CCD-CMOS     | Buried        | CCD-CMOS    | 4T CIS            |

|                       | NMOS            | channel     | CS amplifier    | PMOS          |              | channel       |             |                   |

|                       |                 | NMOS        |                 |               |              | NMOS          |             |                   |

| Oversampling          | N.A.            | N.A.        | 1600 (CMS)      | 4 (CMS)       | 34 (MCS)     | N.A.          | 3025 (MCS)  | MCS               |

### References

- [1] N. Teranishi, "Required Conditions for Photon-Counting Image Sensors," in IEEE Transactions on Electron Devices, vol. 59, no. 8, pp. 2199-2205, Aug. 2012, doi: 10.1109/TED.2012.2200487

- [2] Min-Woong Seo, Shoji Kawahito, Keiichiro Kagawa, and Keita Yasutomi, "A 0.27 e<sub>rms</sub> Read Noise 220 μV/e<sup>-</sup> Conversion Gain Reset-Gate-Less CMOS Image Sensor With 0.11-um CIS Process", IEEE Electron Device Letters, December 2015, Vol. 36, No. 12

- [3] A. Boukhayma, A. Caizzone and C. Enz, "A CMOS Image Sensor Pixel Combining Deep Sub-Electron Noise with Wide Dynamic Range," IEEE Electron Device Letters, June 2020, vol. 41, no. 6, pp. 880-883, doi: 10.1109/LED.2020.2988378

- [4] S. Wakashima, F. Kusuhara, R. Kuroda, and S. Sugawa, "A linear response single exposure CMOS image sensor with 0.5 e<sup>-</sup> readout noise and 76 ke<sup>-</sup> full well capacity," Symposium on VLSI Circuits (VLSI Circuits), 2015, Kyoto, Japan, pp. C88-C89, doi: 10.1109/VLSIC.2015.7231334.

- [5] Stefanov, K.D.; Prest, M.J.; Downing, M.; George, E.; Bezawada, N.; Holland, A.D. Simulations and Design of a Single-Photon CMOS Imaging Pixel Using Multiple Non-Destructive Signal Sampling. Sensors 2020, 20, 2031. https://doi.org/10.3390/s20072031

- [6] Wei Deng and Eric R. Fossum, "Deep Sub-Electron Read Noise in Image Sensors Using a Multigate-Source-Follower," IEEE Transactions on Electron Devices, June 2022, Vol. 69, No. 6

- [7] Qiang Yao, Bart Dierickx, Benoit Dupont, and Gerlinde Ruttens, "CMOS Image Sensor reaching 0.34  $e_{rms}^{-}$  read noise by inversion-accumulation cycling", Proceedings of the International Image Sensor Workshop, June 2015

- [8] Lapi, Agustin J. et al. "Skipper-in-CMOS: Nondestructive Readout With Subelectron Noise Performance for Pixel Detectors." IEEE Transactions on Electron Devices 71 (2024): 6843-6849.

- [9] M. -W. Seo, T. Wang, S. -W. Jun, T. Akahori and S. Kawahito, "A 0.44  $e_{rms}^-$  read-noise 32 fps 0.5 Mpixel high-sensitivity RG-less-pixel CMOS image sensor using bootstrapping reset," IEEE International Solid-State Circuits Conference (ISSCC), 2017, pp. 80-81, doi: 10.1109/ISSCC.2017.7870270

- [10] M. Sato et al., "A  $0.50~e_{rms}^{-}$  Noise 1.45  $\mu$ m Pitch CMOS Image Sensor with Reference-Shared In-Pixel Differential Amplifier at 8.3 Mpixel 35 fps," IEEE International Solid-State Circuits Conference (ISSCC), 2020, San Francisco, CA, USA, pp. 108-110, doi: 10.1109/ISSCC19947.2020.9063017

- [11] Ultra Low Noise CMOS Image Sensors, Boukhayma Assim, Springer Theses, ISBN 9783319687742, 2017

- [12] Nobuhiro Kawai, Shoji Kawahito, Effectiveness of a correlated multiple sampling differential averager for reducing 1/f noise, IEICE Electronics Express, 2005, Volume 2, Issue 13, Pages 379-383. <a href="https://doi.org/10.1587/elex.2.379">https://doi.org/10.1587/elex.2.379</a>

- [13] Jiaju Ma, D. Hondongwa and E. R. Fossum, "Jot devices and the Quanta Image Sensor," 2014 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 2014, pp. 10.1.1-10.1.4, doi: 10.1109/IEDM.2014.7047021.

## Thank you for your attention!

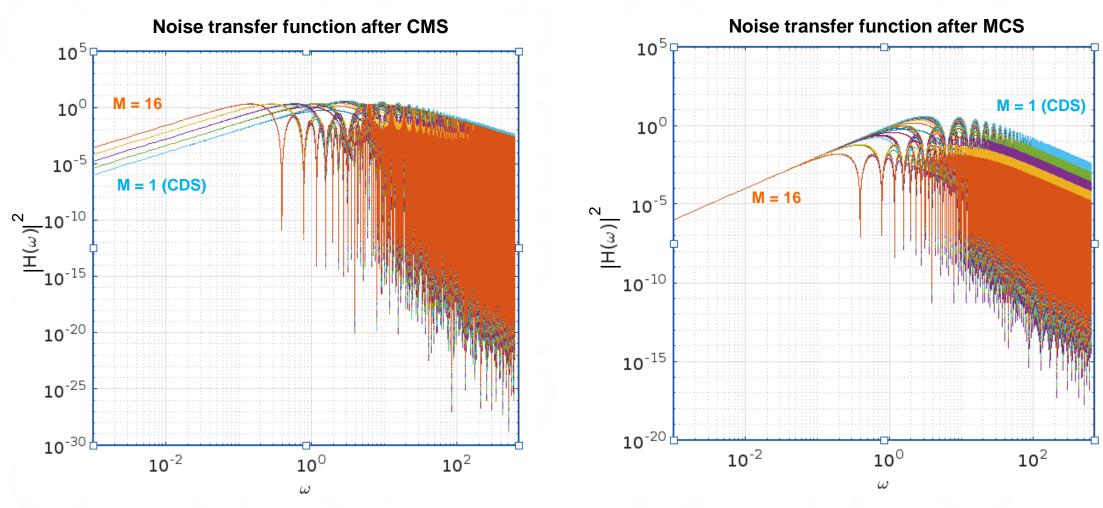

## Comparison of NTF after CMS and McSleste

• With increase in number of samples, in CMS, correlation between reset and signal samples reduces as time gap increases, and hence flicker noise doesn't reduce further and saturates at a level.

# Comparison of flicker noise power after CMS and MCS

# caeleste

- For settling of voltage signal with accuracy of 99%,  $\omega_c t_{cs}$  must be higher than 4.6.

- Two samples in MCS are more effective than infinite samples in CMS.