## Asynchronous design

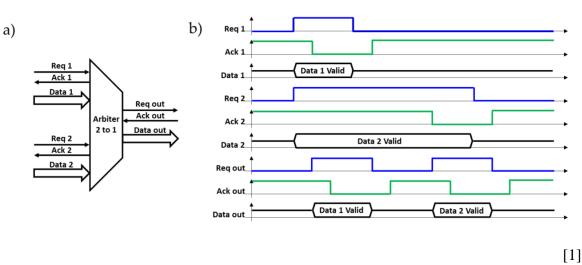

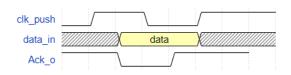

First, an asynchronous controller is build with a request signal to ask for a data to be saved, an acknowledge signal to give a feedback and the data. The request is close to the rising edge on a synchronous design, and the acknowledge is there to reset the request signal (falling edge) as follow with 2 controller input and one output:

E. Aguénounon *et al.*, « Design and Characterization of an Asynchronous Fixed Priority Tree Arbiter for SPAD Array Readout », *Sensors*, vol. 21, juin 2021, doi: <u>10.3390/s21123949</u>.

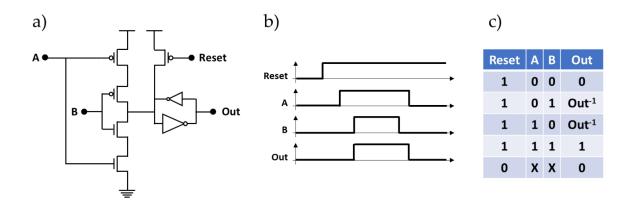

To synchronize the request and acknowledge signals, a special gate is used called Müller gate or Celement and act as a memory or "rendez-vous" function. When A and B is equal the output change to the same state as follow:

E. Aguénounon *et al.*, « Design and Characterization of an Asynchronous Fixed Priority Tree Arbiter for SPAD Array Readout », *Sensors*, vol. 21, juin 2021, doi: 10.3390/s21123949.

[1]

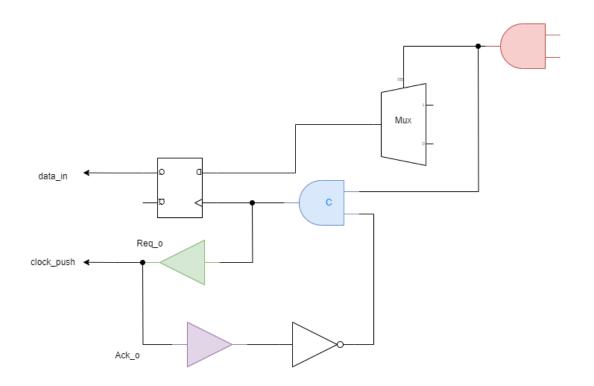

The last controller close to the FIFO is build as follow (C element in blue):

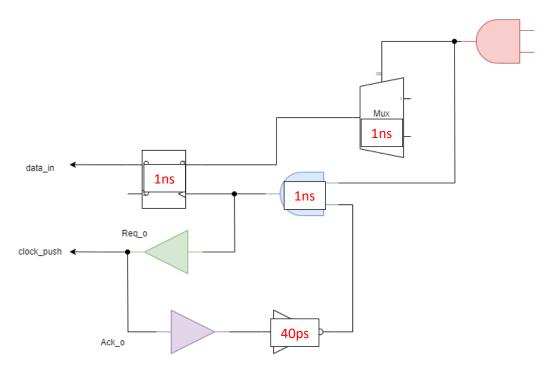

The red and gate is the starting common point of the request for both upper controllers. It controls the data from the upper or downer controller before and activate the C element. The timings are presented bellow:

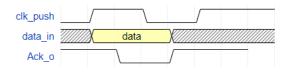

Without delay cells, the data has a delay of 1ns to the clock\_push signal. The UP time of the clock is the Tup = Tblue + Tgreen and the DOWN time is Tdown = Tpurple + 40ps + Tblue + Tgreen. Adding delay cells will degrade the asynchronous readout speed (green or purple). The green delay will compensate the delay on the data but is counted 2 time as it is also in the Tdown. The best way is to add delay with the purple and a data delay of 1ns. The chronogram is the following:

| clk_push |     |       |  |  |  |

|----------|-----|-------|--|--|--|

| data_in  | dat | a)/// |  |  |  |

| Ack_o    |     |       |  |  |  |

No delays (data valid for 1ns), best case

With 1ns purple delay (data valid for 3ns)

With 1ns green delay (data valid for 3ns)

So the constraints on the input clock are:

- Possible 500MHz

- Min\_pulse\_width at 1ns ⇔ duty cycle of 60/40% max

- Data only valid for 1ns (can be changed)

- Transitions time of 200ps

- Uncertainty of 200ps

- Max corner values 🗇 timing changed for TYP and MIN corners to lower values.

MAX: max\_c, max\_rc, skew2\_c, skew2\_rc

TYP: typ

MIN: min\_c, min\_rc, skew1\_c, skew1\_rc

An other solution is to add a C element in the FIFO to synchronize the fifo ready and the request ?

Constraints on the pop\_clock:

- 25 MHz

- Transitions time of 200ps