# **Digital on Top methodology**

#### **Prospectives IP2I 2023 sur Futur Collisionneurs FCC**

14 - 09 - 2023

B. Nodari

#### why DoT methodology?

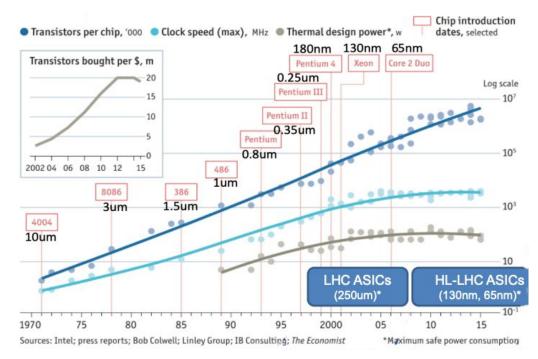

source: https://ep-news.web.cern.ch/chips-new-ep-ese-service-hep-community

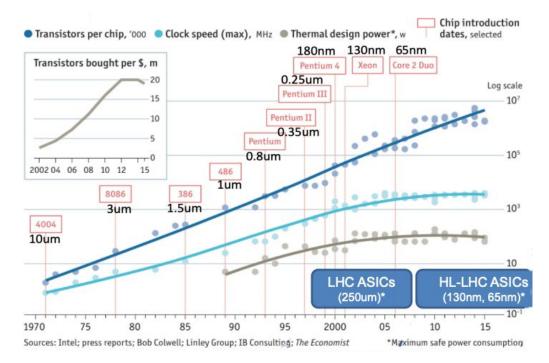

With the **decrease in the size of the technology**, accompanied by a proportional saving in power consumption, the number of transistors that can be integrated on a single chip largely increases.

Reliably manufacturing multi-billion fully-functional transistors per chip requires many more processing steps.

This increased complexity in technology also affects circuit design.

Designs might be confronted with the tangible **risk of failure or delay** with potentially severe consequences on the physics programme.

The new and more sophisticated design tools and design flows that are now available to chip designers must be used in these technologies.

#### why DoT methodology?

source: https://ep-news.web.cern.ch/chips-new-ep-ese-service-hep-community

Chip designers have to face the challenges associated with the new level of design and verification complexity.

This means developing and following scrupulously the **Digital-on-Top design methodology**.

The **DoT design implementation** and System level verification methodologies must be adopted systematically to avoid expensive and time-consuming errors even if this implies a significant increase in design time and resources.

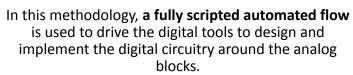

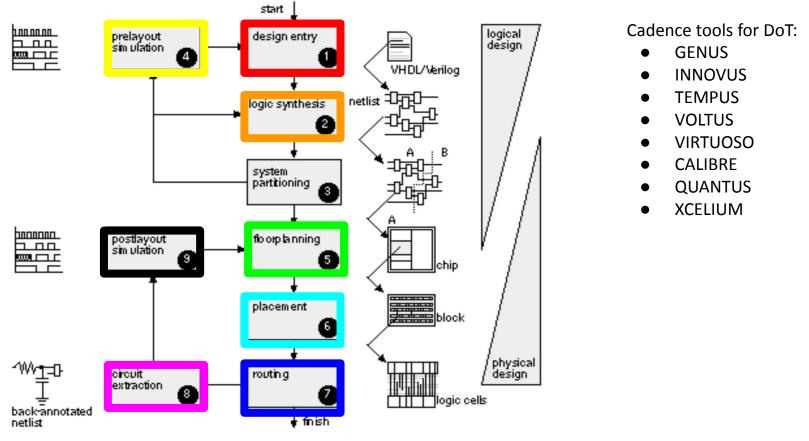

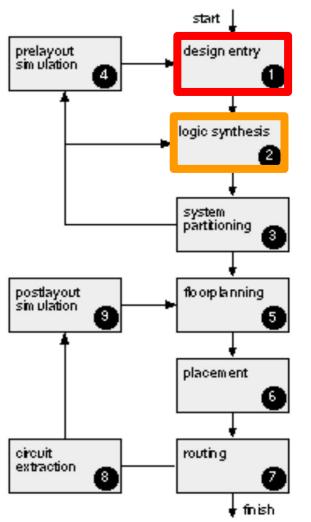

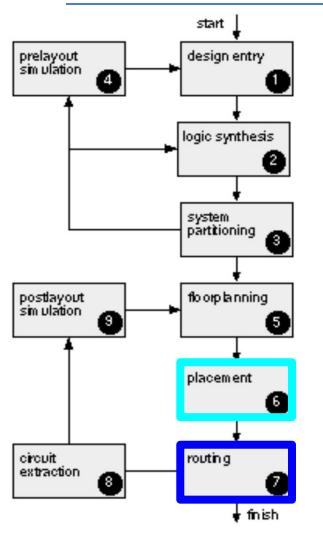

A **design flow** is the sequence of the steps to design an ASIC following the DoT methodology: based on a series of scripts it permits to reach the final file (GDS) for the Tape-out phase (final step before the ASIC fabrication) starting from the behavioral description of the architecture (RTL).

source: "ASICs" Michael J.S. Smith Addison-Wesley '97

4

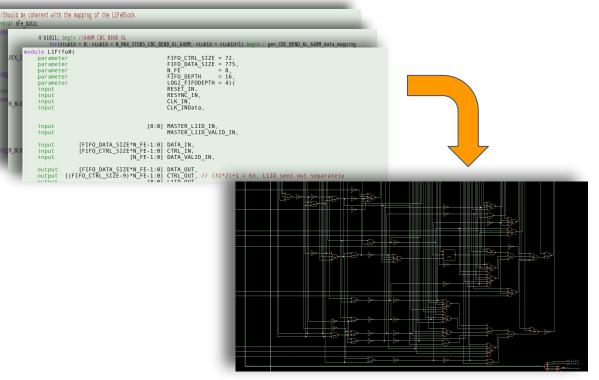

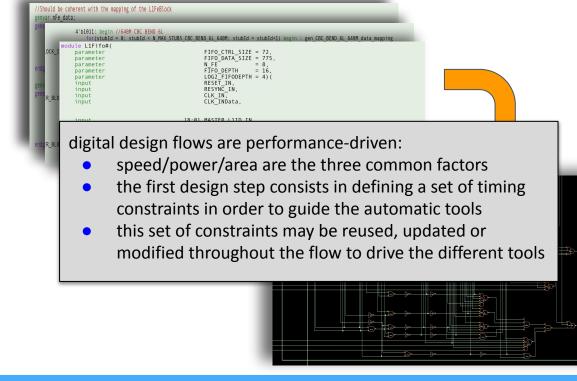

**1. Design entry**: input description of the circuit (RTL) given through a hw description language (VHDL or Verilog/SystemVerilog).

**2.** Logic synthesis: the process that converts RTL into a technology-specific gate-level <u>netlist</u>, optimized for a set of pre-defined constraints. [GENUS]

CIC RTL code in SystemVerilog language:

**1. Design entry**: input description of the circuit (RTL) given through a hw description language (VHDL or Verilog/SystemVerilog).

**2. Logic synthesis:** the process that converts RTL into a technology-specific gate-level <u>netlist</u>, optimized for a set of pre-defined constraints. [GENUS]

CIC RTL code in SystemVerilog language:

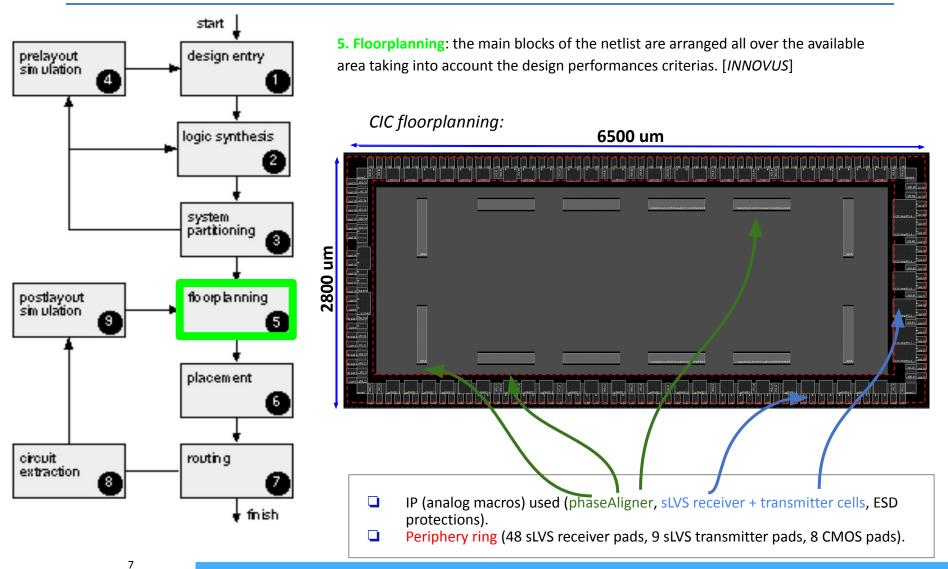

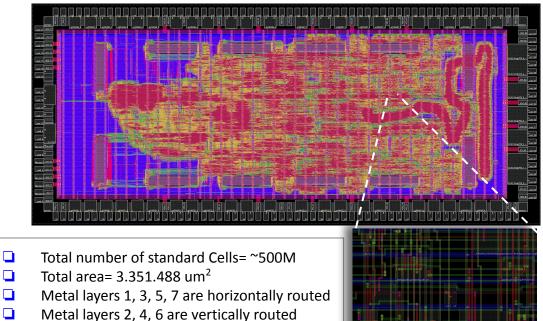

**6. Placement:** the standard cells and any other macro block are placed following the design constraints. [*INNOVUS, TEMPUS, VOLTUS*]

**7. Routing**: the physical interconnections between cells are traced in the available metal layers. [*INNOVUS*]

#### CIC placement and routing:

- power routing in M7, AP layers

- clock tree routing in M5, M6

All functionalities and timing constraints are often checked during the design flow by simulations with testbenches: the goal is to test design functionalities within a script-based framework (python) or UVM.

**4. Pre-layout simulation**: functionality of the netlist is checked and timing constraints are verified. [*XCELIUM*].

**8. Circuit extraction**: the parasitics created by the metal interconnections are evaluated and written back into the netlist (back-annotation). [*QUANTUS*]

**9.** Post-layout simulation: functionality and timing constraints are again checked this time including all available physical informations.

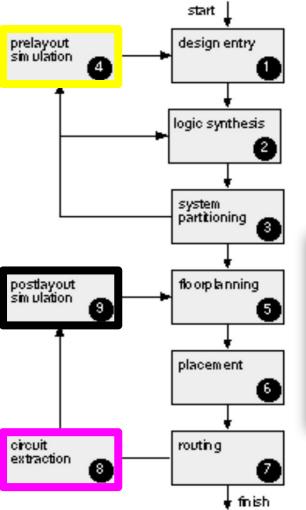

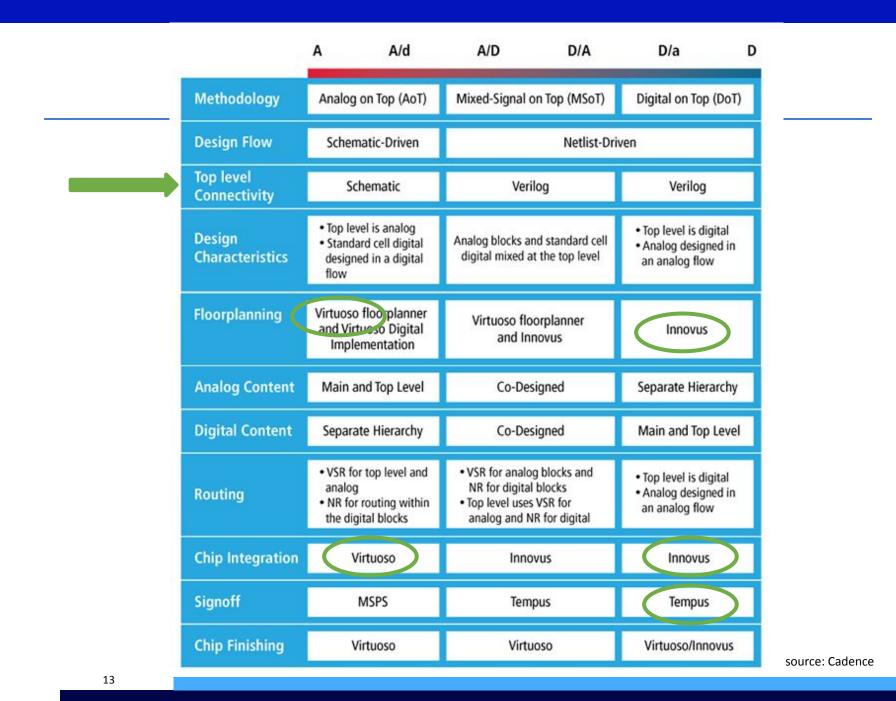

## Digital vs Analog on Top flows

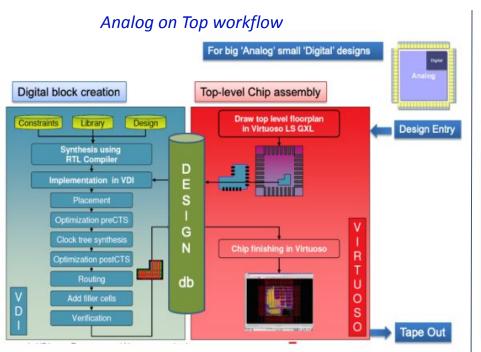

Analog on Top (historical design flow):

- refers to the design flow where the top level of the design is represented as a <u>schematic</u>.

- *Virtuoso* tool is typically the environment where the entire top level design is assembled.

- Blocks are prepared separately then added one-by-one to the design.

- Ok for small designs but extremely risky for complex ASICs.

Digital on Top workflow

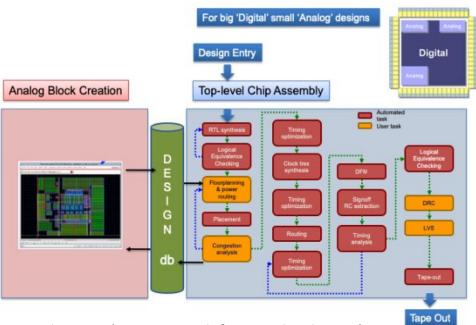

Digital on Top (new approach for complex designs):

- refers to the design flow where the top level of the design is represented as a <u>Verilog/SystemVerilog netlist</u>.

- *Innovus* tool is typically the environment used for assembling the entire top level design.

- High level simulation and verification throughout design requires different skill set and generally more resources

- strong mitigation of risk if all steps are fully followed

10

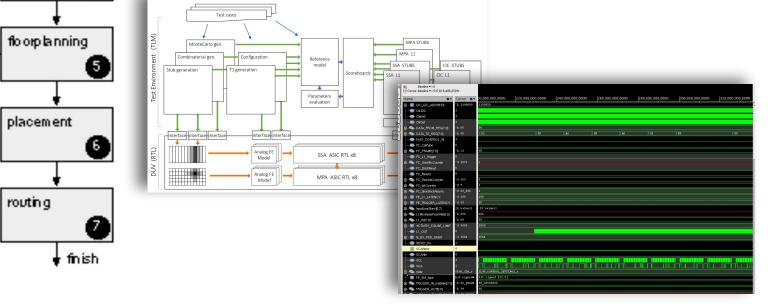

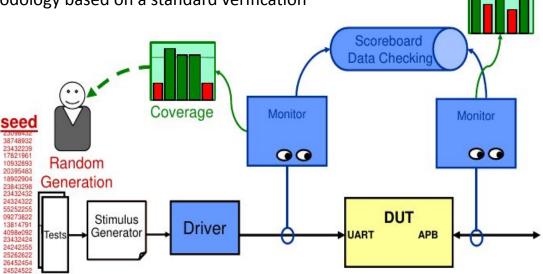

#### System level verification

- Verification: the key to unlocking quality and innovation in future ASICs for HEP experiments.

- Verification accounts to 70% of overall design costs and total ASIC design time.

- Reasons for verification:

- complex designs will have complex bugs;

- cost of prototyping will be higher in future so we need to reduce the number of prototyping runs (typically 2 or more engineering runs before production);

- System level verification framework :

- build a realistic world (= verification environment) around a design ( =Design Under Test)

- exercise the DUT in all possible ways

source: Cadence

- check all the outcomes of the DUT are as expected

- what is UVM (Universal Verification Methodology)?

A class library of verification building blocks

- A proven verification methodology based on a standard verification component architecture

Coverage

Components of a MDV environment

- Automated Stimulus Generation

- Independent Checking

- Coverage Collection

#### Vocabulary

- **SOS**: integrated natively tool into Virtuoso to manage design data including IPs, PDKs etc from concept-to-tapeout.

- LVS (= Layout vs Schematic): one of the final step of DoT and AoT flow in order to verifies the connectivity and ensures the functionality of the layout.

- DRC (= Design Rule Checks): one of the final step of DoT and AoT flow in order to verifies that the given layout satisfies the design rules provided by the fabrication unit.

- SDC (= Synopsis Design Constraints): timing constraints (for DoT methodology) based on clock definitions (time period, duty cycle,..) and timing exceptions (false paths, asynchronous paths,..).

- **CTS (=Clock Tree Synthesis):** is one of the most important stage in PnR. It's the process of distributing the clock and balancing the load.

- **RTL**: descriptive code written in hw format (VHDL, Verilog, SystemVerilog).

#### ASICs ? FPGAs? I'm confused!

ASIC: an Integrated Circuit designed for a particular system or end-use

- Broad definition including analog, digital or memory circuits as long as custom designed

- In contrast to standard IC (memories, controllers, microprocessors)

- The designer is (often) the customer

- It's both a class of IC products and a design methodology

- (some) types of ASICs:

- Full-Custom: some or all of the cells, circuits or layouts are specifically designed

- **Standard-Cell Based**: predesigned logic cells are placed and interconnected

**FPGA/(or PLD)**: standard IC that may be configured or programmed for a specific application

• It provides the customizability of a digital ASIC without the need to design and fabricate a new device for each application