# Timing at Belle-II Vertex Detector (VXD)

**Yitong Liu**

Supervisor: Jérôme Baudot

Support from: Christian Finck & Ajit Kumar

PSA M2 Defense 22/06/2023

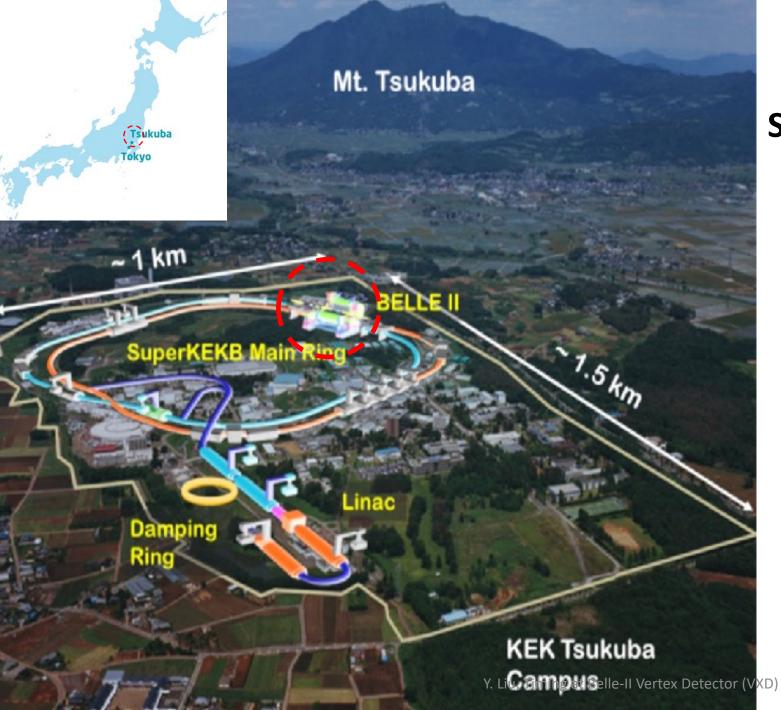

#### SuperKEKB is an $e^-e^+$ collider:

- Asymmetric energy:

- 7GeV  $e^-$  + 4GeV  $e^+$

- Center of mass energy: 10.5 GeV

- Bunch crossing: 4 ns

- Continuous background

- Luminosity goal:  $6 \times 10^{35} cm^{-2} s^{-1}$

- Rare events & high precision

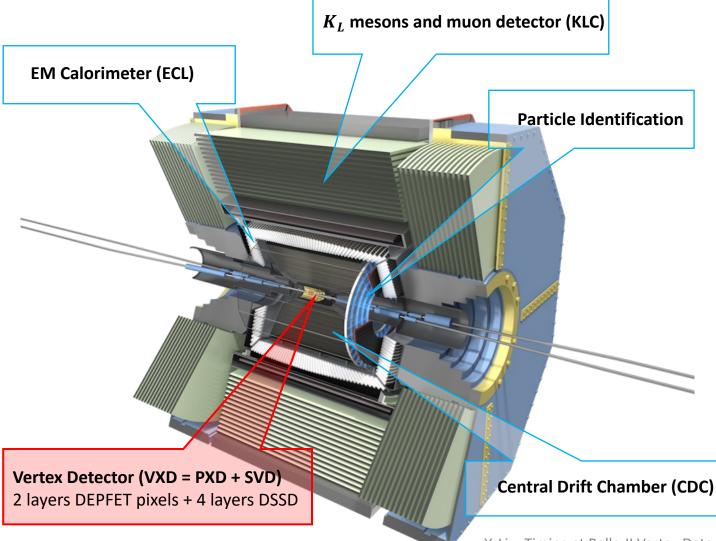

### Belle-II detector

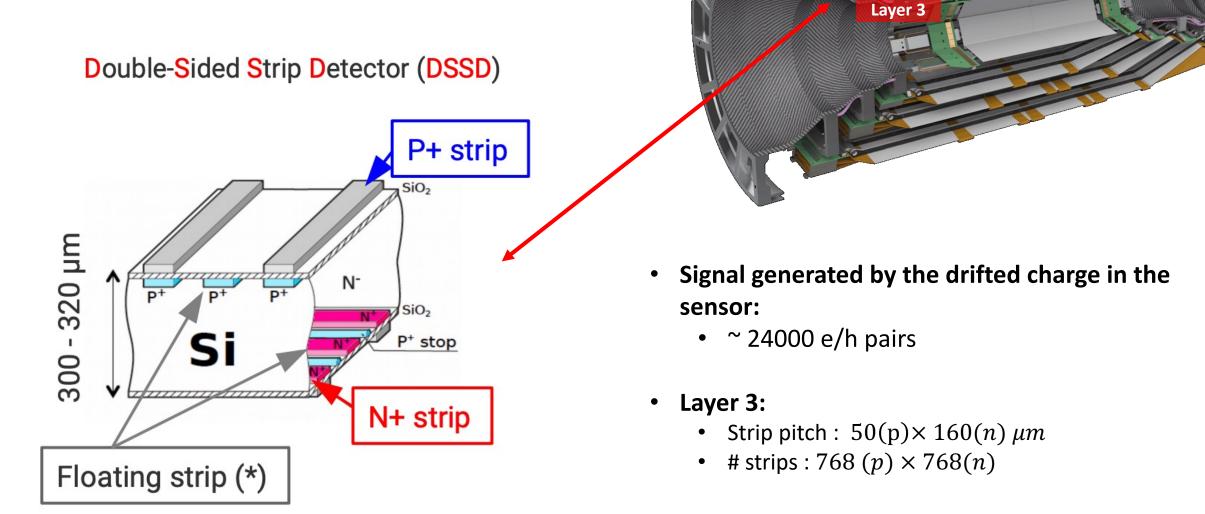

#### • Silicon Vertex Detector (SVD):

- 4 outer layers of the VXD

- Strip detectors

Track reconstruction for low momentum charged particles & decay vertex reconstructions

### Timing stratigies to high-luminosity conditions

Layer 6

aver 5

Layer 4

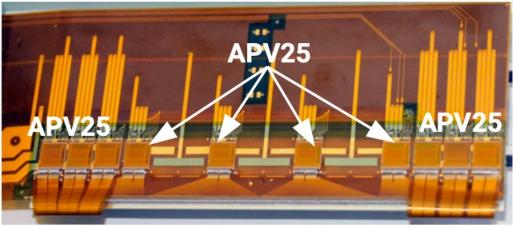

#### Readout system: APV 25

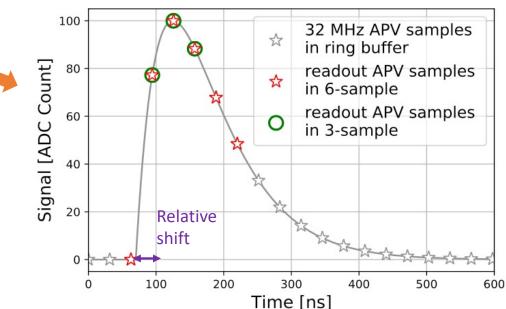

- APV 25 is connected to the strip sensor for signal readout:

- Clock frequency: ~ 32 MHz

- After a trigger is specified, the chip will go back in time to search for the samples in the buffer that match the trigger

- Currently, 6-sample mode is being used:

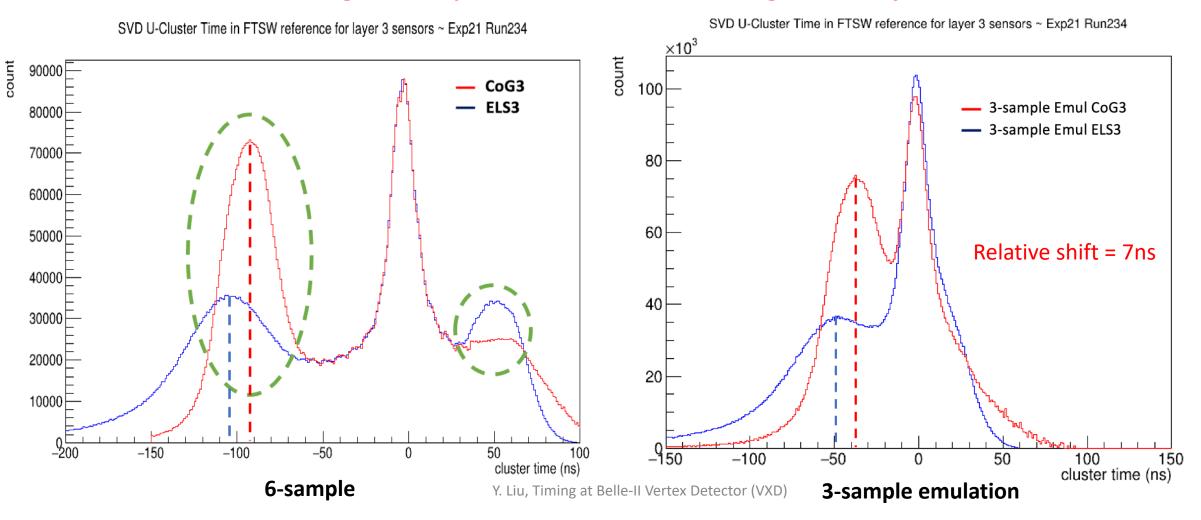

- 3-sample is emulated from the 6-sample by doing a **relative shift**

#### **Readout front-end on a sensor**

**APV 25 readout**

#### SVD cluster time reconstruction

- Sum APV outputs: 3 best summed consecutive samples

- **Two main algorithms** for *t cluster* reconstruction:

- CoG3: center of gravity

$$T_{\text{SVD;raw}} = \frac{\sum_{i=0}^{2} a_i \cdot i\Delta t}{\sum_{i=0}^{2} a_i}.$$

• ELS3: approximate pulse shape + least square

$$a(t) = A \frac{t - T_{\text{SVD;raw}}}{\tau} \exp\left(1 - \frac{t - T_{\text{SVD;raw}}}{\tau}\right)$$

- Currently, CoG3 is the default

- However, ELS3 might be better for high luminosity

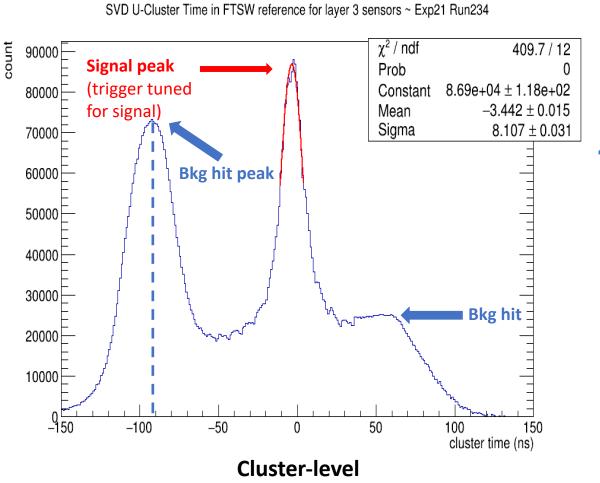

#### SVD 6-sample CoG3 cluster time

The background arrival time is not synchronous to the trigger time.

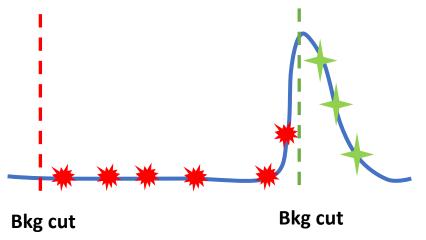

#### The distorted bkg time estimation leads to the bkg hit peak

#### SVD algorithm comparison

#### Hard to tell which algorithm performs better in background rejection

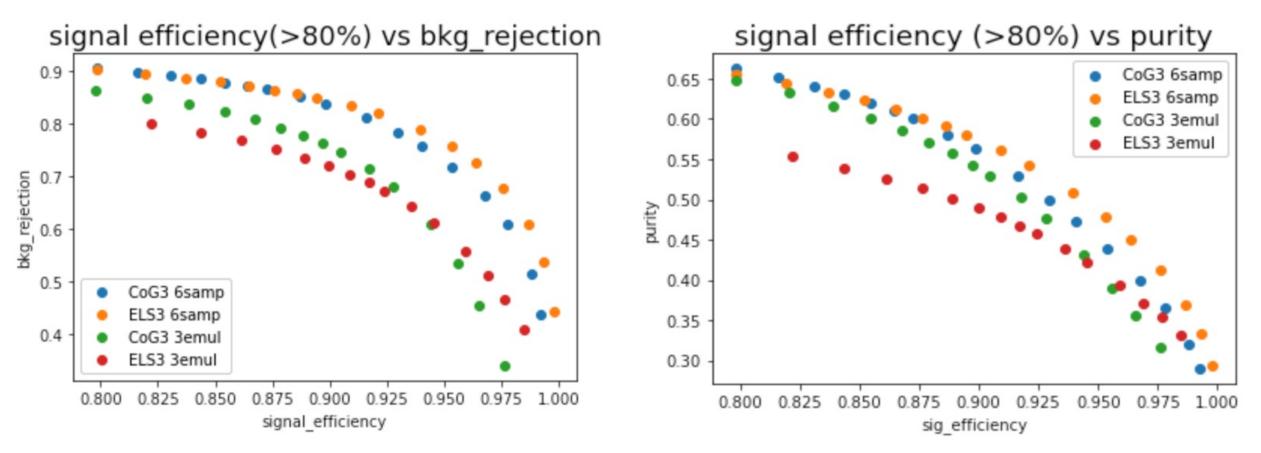

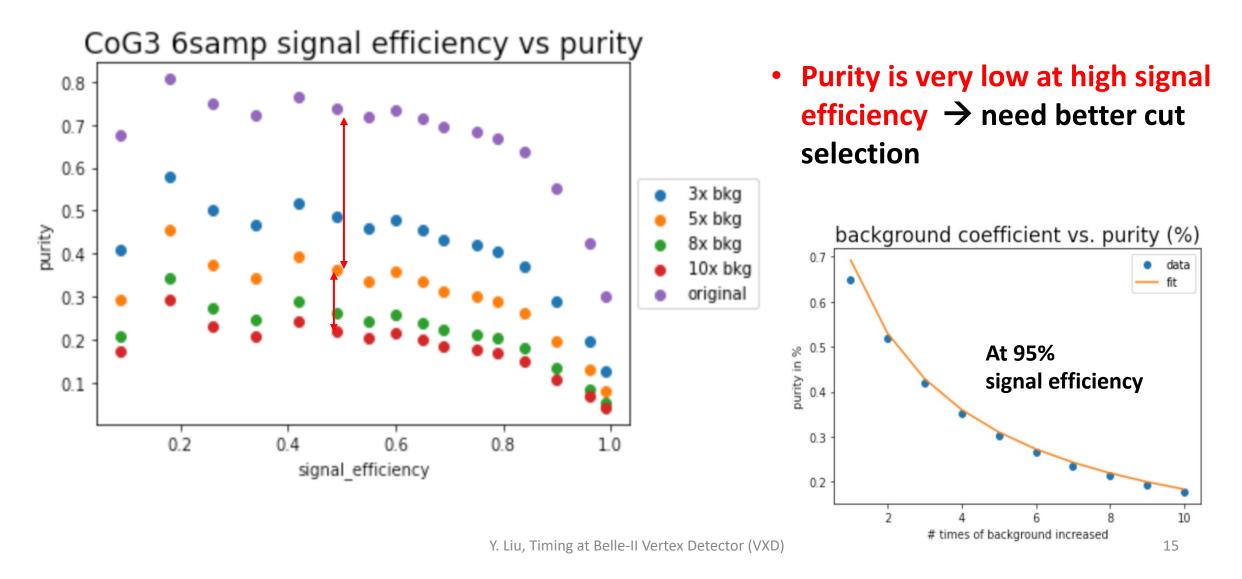

# **ROC** (Receiver Operating Characteristic)

### Parameter settings

Using ROC curve to compare the performance of 4 different cases (CoG3 & ELS3 6-sample, CoG3 & ELS3 3-sample) with different cluster time threshold cuts:

#### • Define variables

- **S**<sub>total</sub> = total # of signal hits (no constraints)

- **B**<sub>total</sub> = total # of background hits (no constraints)

- $S_{sel}$  = # of signal hits selected within certain time cut

- **B**<sub>sel</sub> = # of bkg hits selected within certain time cut

#### • For different time cuts:

•

$$S_{eff} = \frac{S_{sel}}{S_{total}}$$

•  $B_{rej} = 1 - \frac{B_{sel}}{B_{total}}$

• Purity  $= \frac{S_{sel}}{S_{sel} + B_{sel}}$

Build S<sub>eff</sub> vs B<sub>rej</sub> & Purity vs S<sub>eff</sub> curves

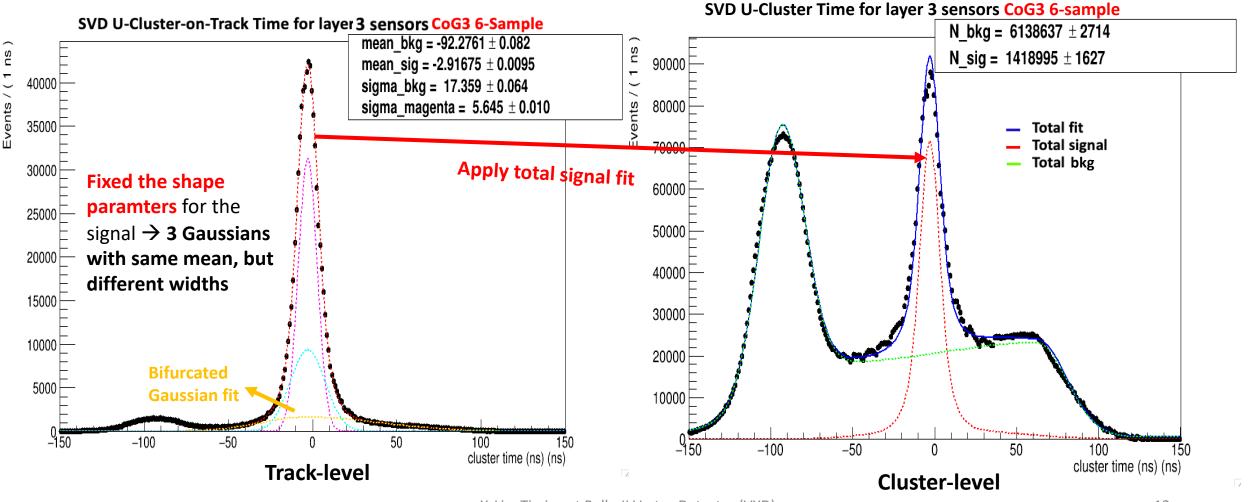

Need to fit the cluster time plot to get these parameter values

### CoG3 6-sample cluster time fit

\*Same method to fit other three cases. Tune on the parameter.

Y. Liu, Timing at Belle-II Vertex Detector (VXD)

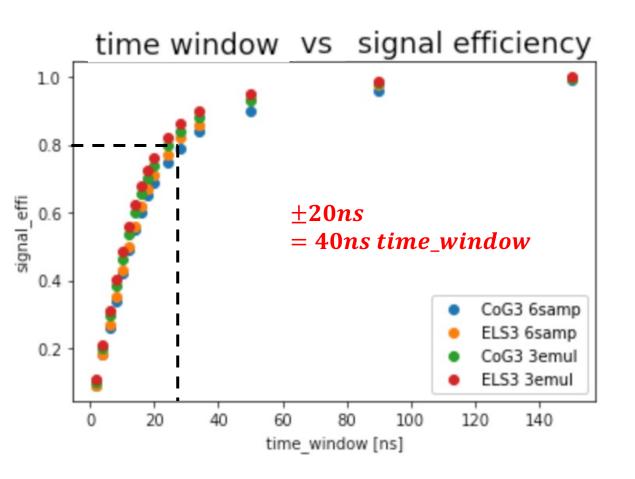

#### General time window scan

- General time window scan:

- From 0 *ns* to 150 *ns*

- ROC curve is rougly the same for four different cases

- Similar signal distribution

- Physics analysis usually focus on high signal efficiency (> 80%)

- Time window ~ **28** *ns* (±14 *ns*)

#### ROC curve: high signal efficiency

- For *B<sub>rej</sub>* : 6-sample is better than 3–sample

- For *purity*: 6, 3-sample perform about the same at high S<sub>eff</sub>

### S\_efficiency vs Purity with increasing bkg

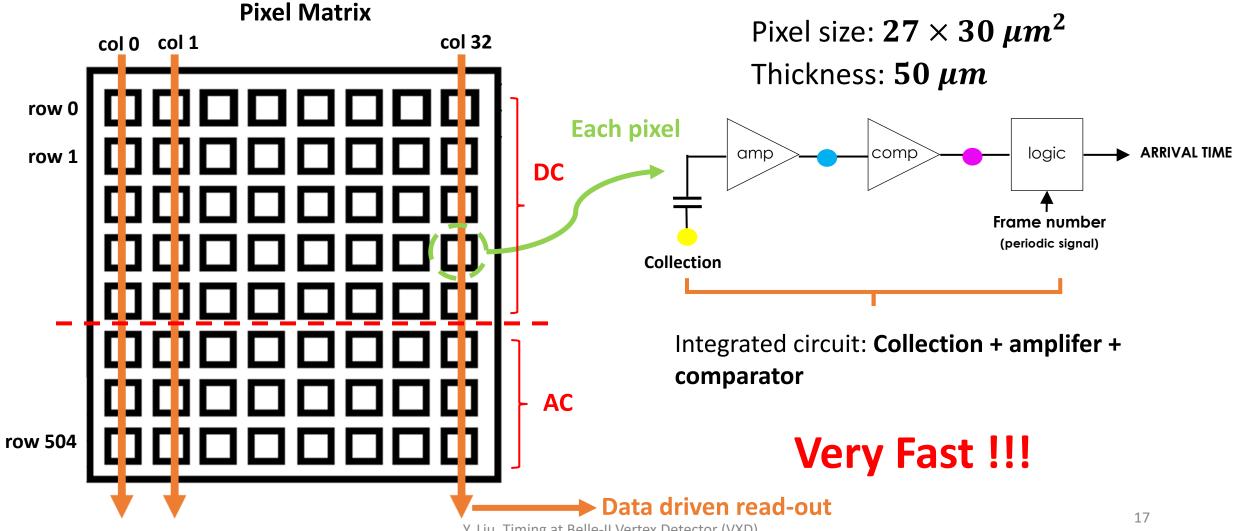

# **CMOS Sensor** (Complementary Metal Oxide Semiconductor)

#### **Basic MIMOSIS-Fast architecture**

Y. Liu, Timing at Belle-II Vertex Detector (VXD)

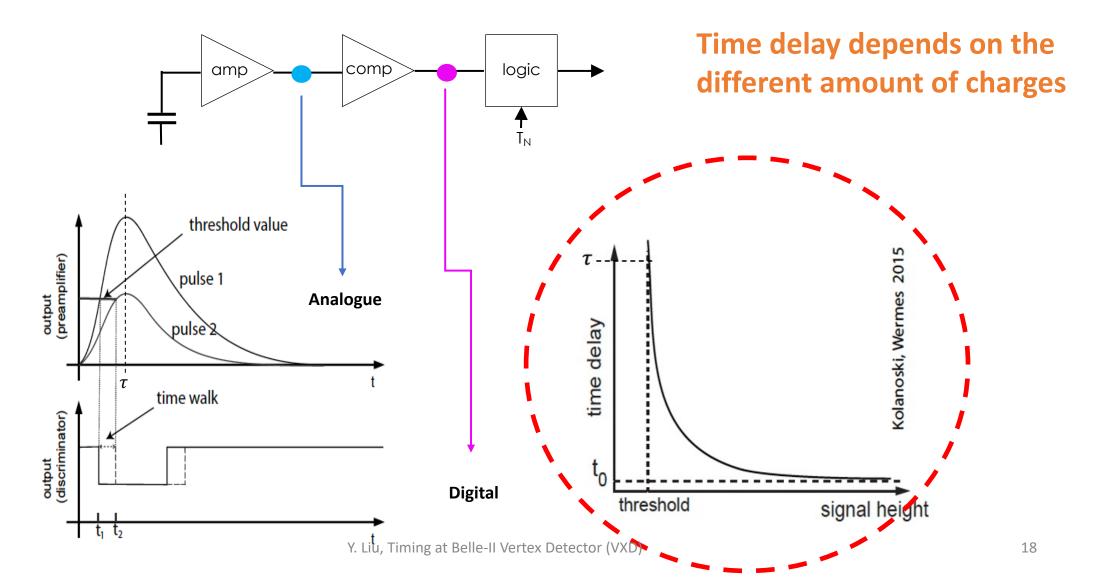

#### Time walk

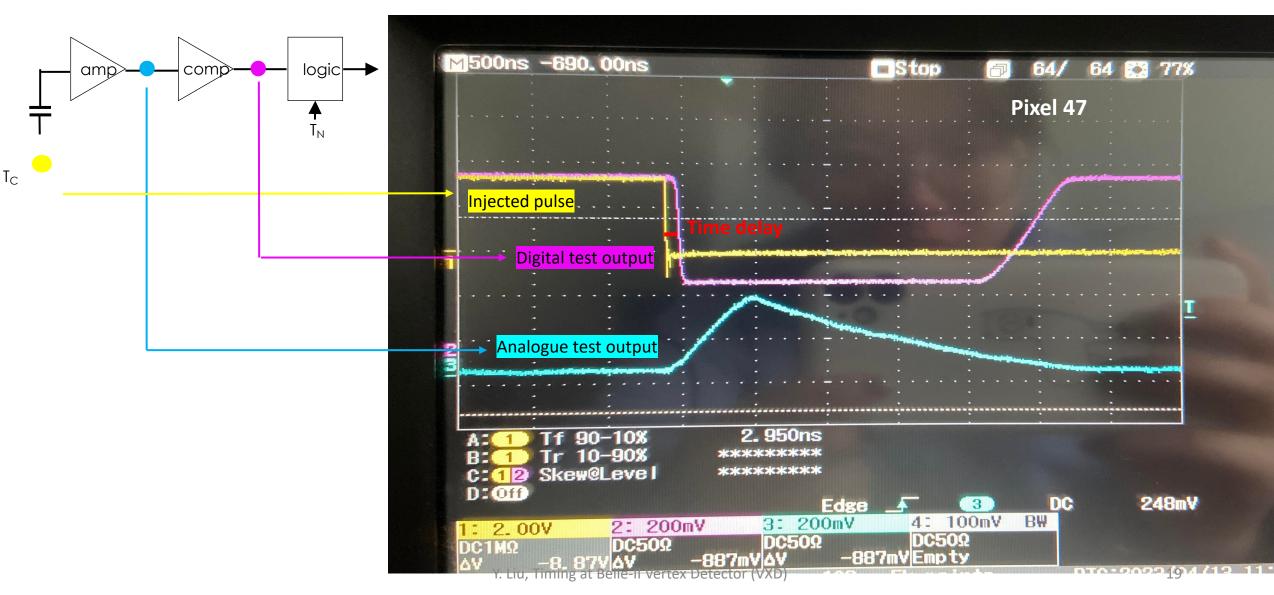

#### Oscilloscope output

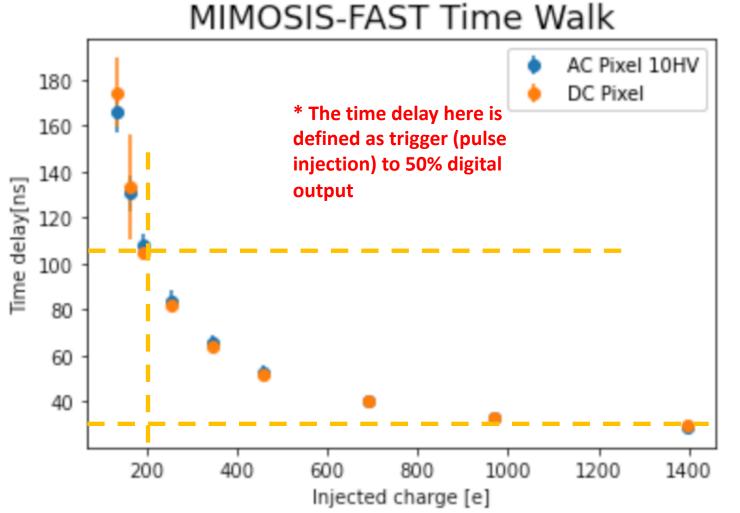

#### MIMOSIS-Fast time walk

- Average values of the DC, AC pixels

- No difference in the DC & AC pixles:

- ~30ns at 1400 e charges

- **Time walk:** 75 *ns* from 200 e to 1400 e charges

- Test only electronic behaviors with injected charges. Further test on ionization charges needed.

### Summary

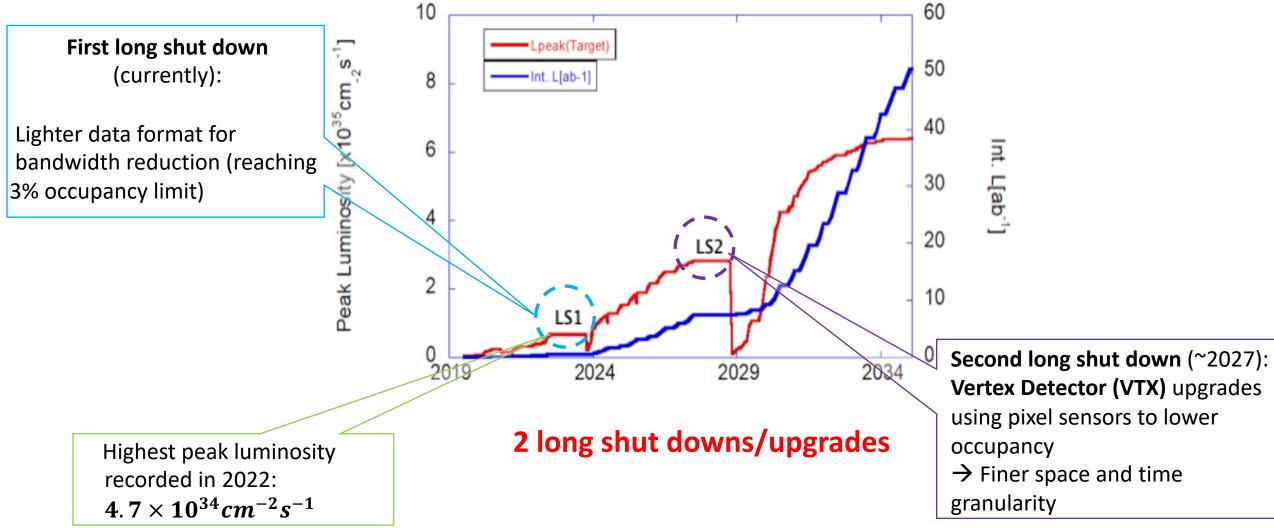

- The high-luminosity anticipated at Belle-II will create high occupancy in the future

- Simple cut down on the readout sample gives worse purity & bkg rejection.

- Machine learning algorithms are currently under development

- The charge injection only tests the electronics behavior of the CMOS sensor (~75ns time from 200 e ~ 1400 e charges)

- Laser with precise time of arrival to test the ionisation charge collection time

# Back-up

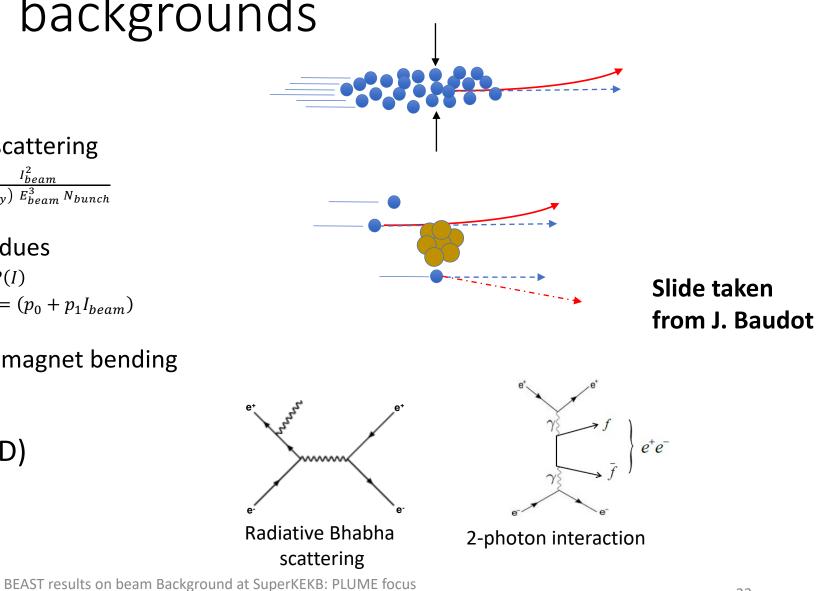

### Beam induced backgrounds

- Single beam effects

- Touschek intra-beam scattering

• rate  $\propto \frac{I_{bunch}^2 N_{bunch}}{(\sigma_x \sigma_y) E_{beam}^3} = \frac{I_{beam}^2}{(\sigma_x \sigma_y) E_{beam}^3 N_{bunch}}$

- Beam gas vacuum residues

- rate  $\propto I_{\text{bunch}} \times N_{\text{bunch}} \times P(I)$

- Dynamic pressure  $P(I) = (p_0 + p_1 I_{beam})$

- Synchrotron radiation magnet bending

- rate  $\propto I_{\text{beam}}$

- Beam-beam effects (QED)

- rate  $\propto$  Luminosity

- J. Baudot - PIXEL 2018

## VTX upgrade

- Replacing the whole VXD with a new vertex detector (VTX), composed with 5-layers of Monolithic Active Pixel Sensors (MAPS) based on the CMOS technology

- The occupancy level with VTX is expected to be below  $1e^{-4}$  in any background level conditions.

- The proposed MAPS has a **25 to 100ns integration time**

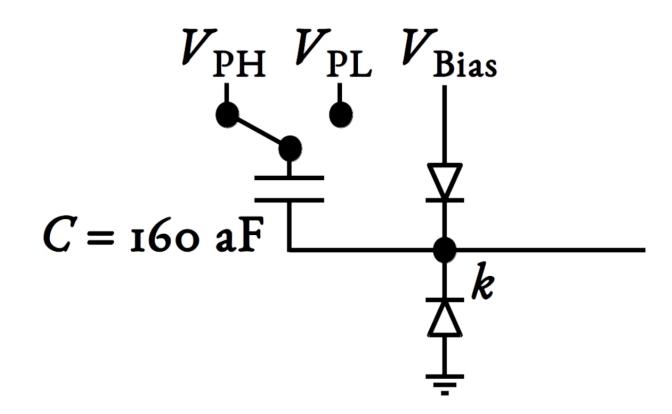

## Charge injection

- The injected voltage is first set to  $V_{PL}$  with  $V_{Bias}$  set to the working voltage of a diode.

- Once the charge is injected, the injection voltage will be set to  $V_{Ph}$  .

- The quick change of voltages induces the charge to the node k with  $Q = C \cdot (V_{PH} V_{PL})$ .

- The capacitance is set to be 160aF so that 1mV voltage difference corresponds to 1e charge generated on the electrodes

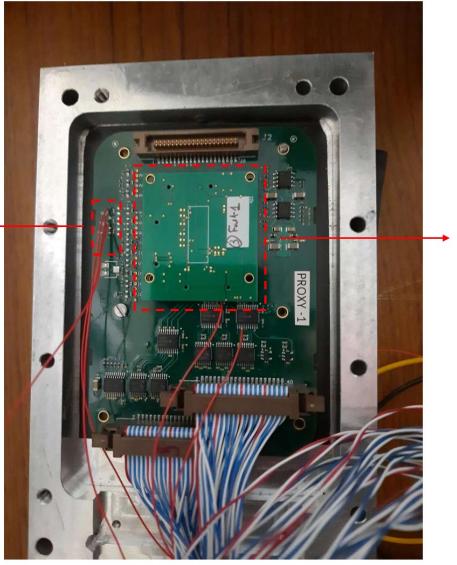

### Proxy board

VPulseHigh & VPulseLow test ← connection output

MIMOSIS-Fast chip