## **ITS3 IPHC Meeting – Sensor Developments**

Gianluca AR, Walter S

**ER1** Submission

EP R&D WP1.2 new phase

Concepts for the ER2 stitched sensor

51 instances of Test Chips per Reticle

## ER1 Tape-Out

Last p 14 O

|            | 24 Sept       | WK38 | ER1 MOCK submission                     | Known DRC violations and residual issues.                            |

|------------|---------------|------|-----------------------------------------|----------------------------------------------------------------------|

|            | 6 Oct         | WK40 | MOSS design release                     | Density and residual DRCs on MOSS fixed.                             |

| <u>)ct</u> | 31 Oct        | WK43 | MOST design release                     | Density and residual DRCs on MOSS fixed.                             |

|            | 4 Nov         | WK44 | Chiplets design release                 | Various density issues on multiple chips.                            |

|            | 14 Nov        | WK46 | ER1 TRUE tape-out                       | Extensive and intensive checks on full wafer gds and virtual dicing. |

|            | 1 Dec         | WK48 | Submission of modified implant geometry | Split on gaps in the buried low-dose n-type layer.                   |

|            | 5 Dec         | WK49 | Mask views available                    | Foundry.                                                             |

|            | 11 Dec        | WK49 | Mask views approved                     | By us (via a slow remote GUI only inspection tool).                  |

|            | 12 Dec        | WK50 | Mask fabrication STARTED                |                                                                      |

|            | 23 April 2023 | WK16 | Expected wafer shipment date            |                                                                      |

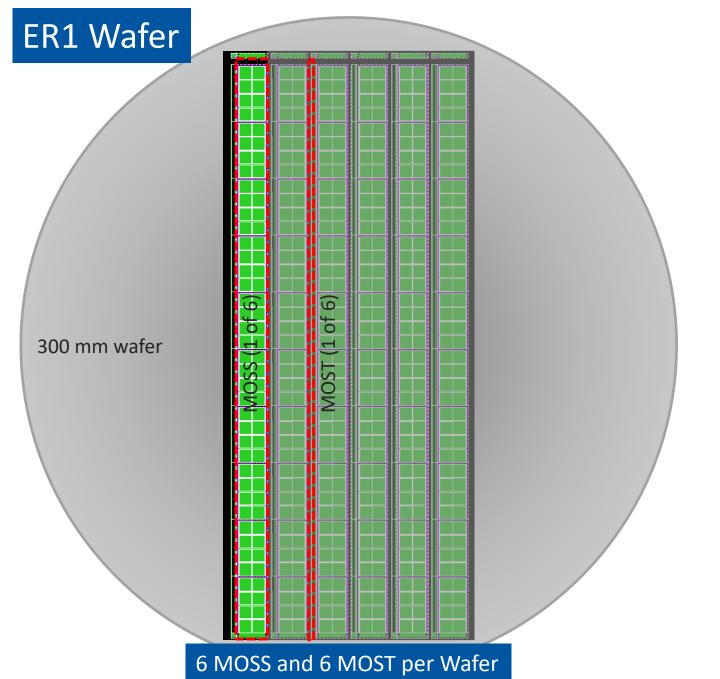

### • Wafers production plan

- 18 wafers with ER1 base mask set

- 6 wafers with variant mask (split) concerning the *buried n-type implant*

- Removed in MOST. Increase of gap width in APTS, DPTS, MOSS pixels

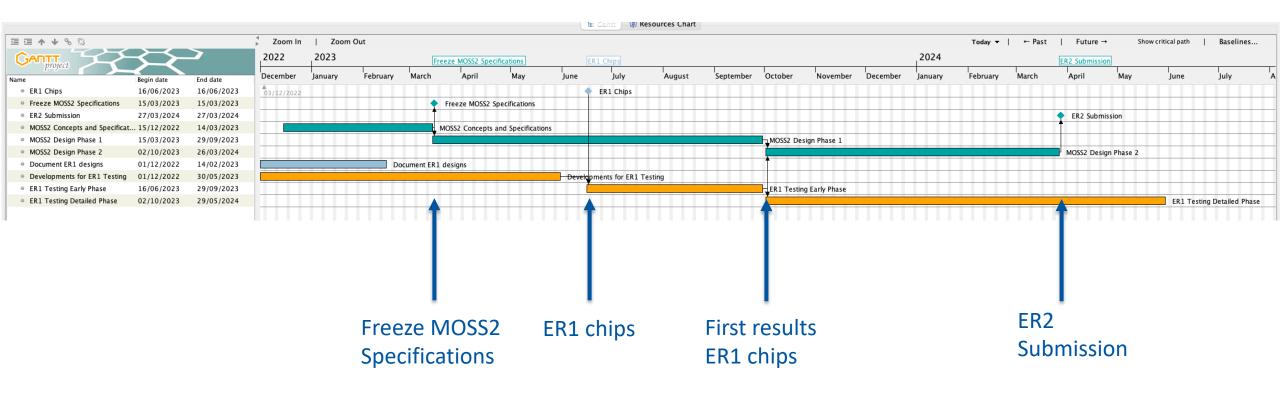

#### Tentative timeline 2022 MOSS

- Development and design

- Stitched sensor chip MOSS2 targeting all ITS3 requirements and functions

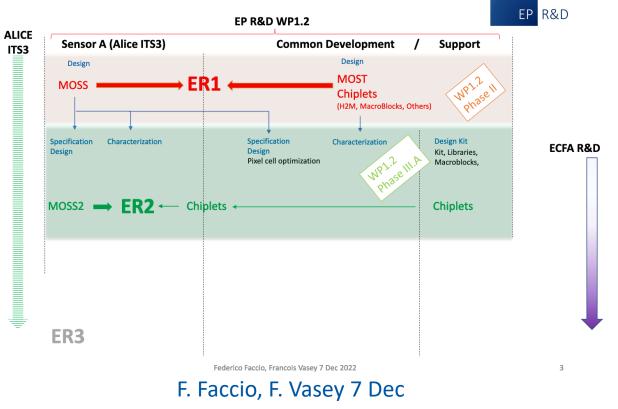

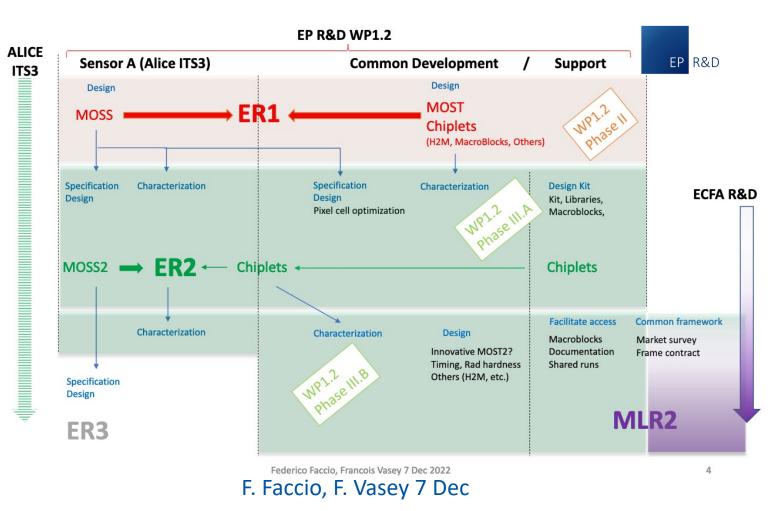

ER1 completes WP1.2 Phase II and starts

- Pixel development structures compatible with  $MOSS2^{22}$

- Macro blocks and cell libraries for ER2

- Characterization

- ER1 sensors and chips

#### Timeline

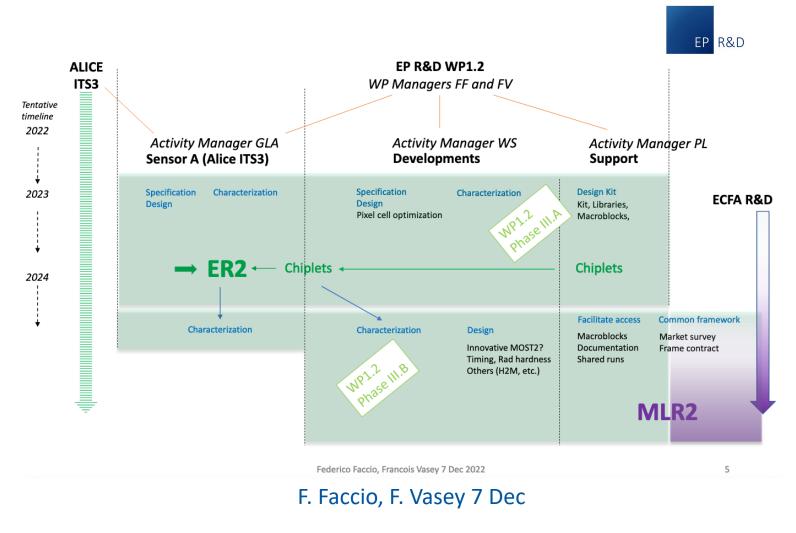

Phase III.A

Scope

Dec 2022 -> Q1-2024 (ER2 submission)

2023

## Outlook EP R&D WP1.2 Phase III.B

Tentative

### Split of ITS3 final sensor design

cycle

Design for ER3 submission of the<sup>2022</sup> final chip planned to be in the scope of ALICE ITS3

### Phase III.B scope

Characterization of ER2 designs <sup>202</sup> Developments from ER1 (timing, + radiation hardness, H2M)

#### Timeline

Q2 2024 -> MLR2 submission

## **Structured as Collaborating Activities**

#### Sensor A – ITS3

Gianluca

**Developments**

Walter

Support

Pedro

#### WP1.2 Coordination

F. Faccio (ESE-ME SL), F. Vasey (ESE GL)

## Outlook WP2

## **ER2 STITCHED SENSOR**

20230117 ITS3 IPHC | ER2 Sensor Concepts

## **MOSS2** Design Concepts and Specifications

### Next stitched sensor chip is **not** a direct evolution of MOSS +/- MOST

Goals are different

MOSS and MOST are true exploratory designs for proof of principles and learning methodology and yield MOSS2 is the **first attempt to cover ITS3 requirements**

Existing circuits need substantial redesign

New features to be added

#### Studies and discussions started

Architectural options

Identifying requirements, trade-offs, MOSS/MOST commonalities, differences Gathering lists of design questions and development needs Plan to assess and address them by simulation studies in Jan-Feb First look into early simulations of readout capabilities and requirements Started identifying areas of responsibility and discussing design assignments

## **Power distribution**

### Power distribution remains major challenge

IR drops

Investigate additional metal and redistribution layer options

Carefully looking into power domain partitioning and on-chip power regulation

Could allow to cope with IR drops, but llarger thermal dissipation

Promote power to top concern for every block specification, design, validation from the beginning

## Yield and DFM

### Yield remains major unknown

- Keep improving design for yield

- Explored in ER1, compromised in certain design blocks

- Need to handle yield more quantitatively and systematically in ER2

- Use the available tools (interesting early stage exploration from Frederic)

- Seek data from foundry

- Further develop Custom Design rules

Early studies of Leonardo, Thanu. Simulations on Digital Pixel by Geun Hee

MOSS and MOST analysis revealed large potential impact of leakage currents

Limits density of transistors and gates

Needs consideration from early stages

#### Recent updates

- Detailed studies of sub-threshold conduction leakage

- Activity recently resumed, Geun Hee, Gianluca, Szymon, Frederic

- Identifying mitigation techniques to keep the leakage under control

## Major themes

#### Leakage

#### Concept

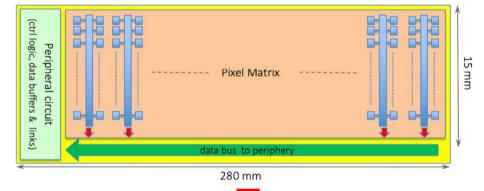

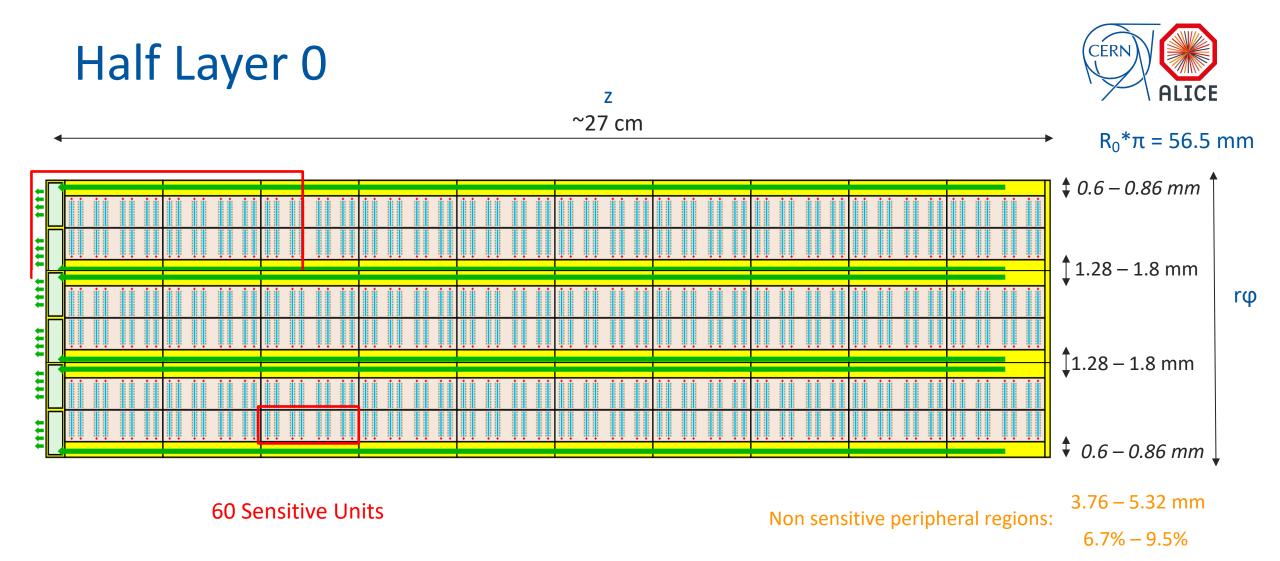

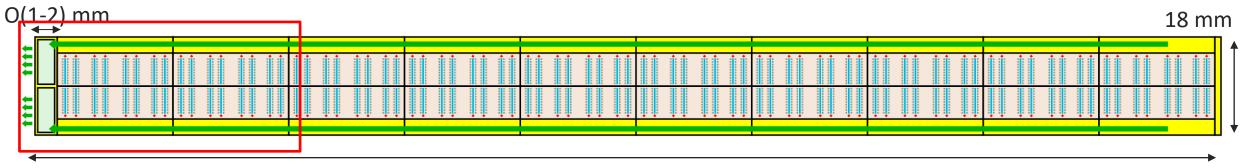

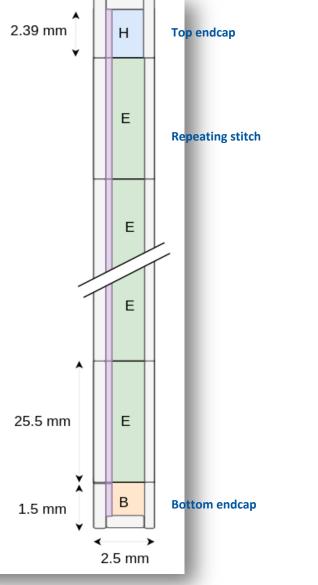

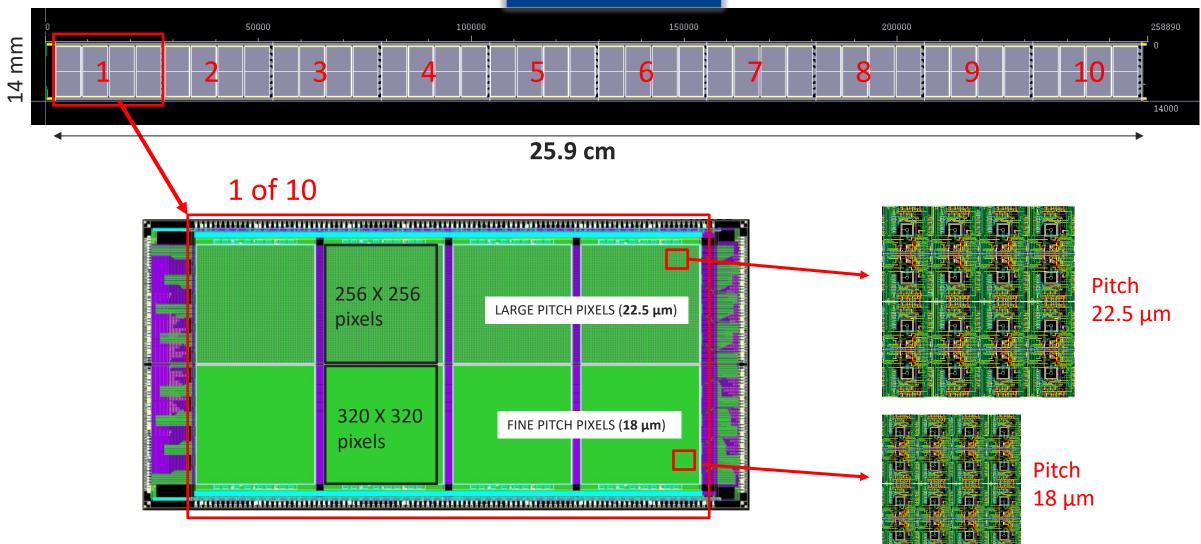

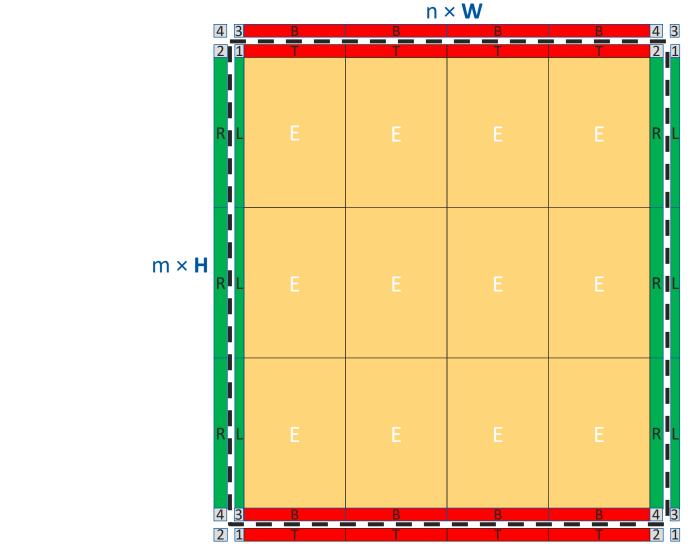

### Use stitching to implement *abutted arrays of sensors on the same die*

Include know-how from ALPIDE, MLR1, MOSS and MOST and other designs

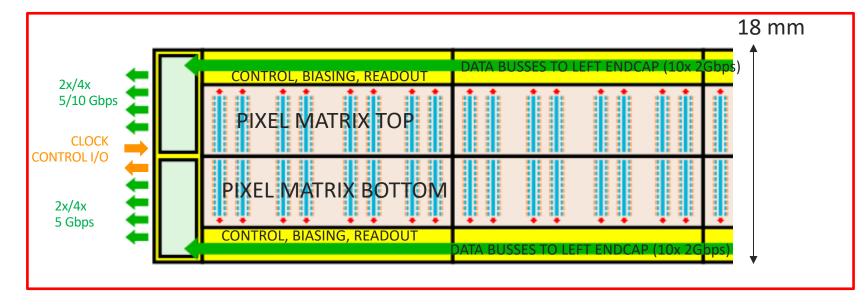

#### Two peripheral regions on the long edges

Data collected in long edge peripherys and transmitted at high rate over on-chip fast data busses (concept 1)

#### ITS3 Letter of Intent

# Stitched backbone busses and fast serial outputs

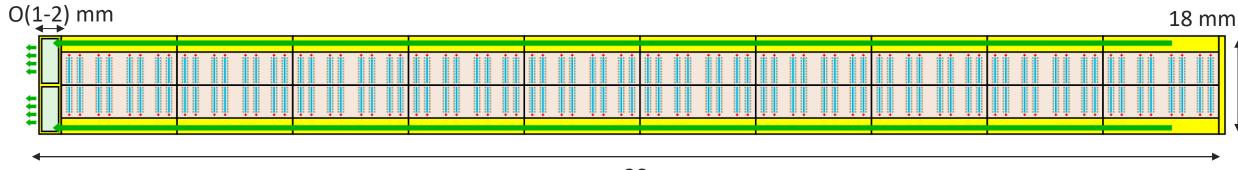

~28 cm

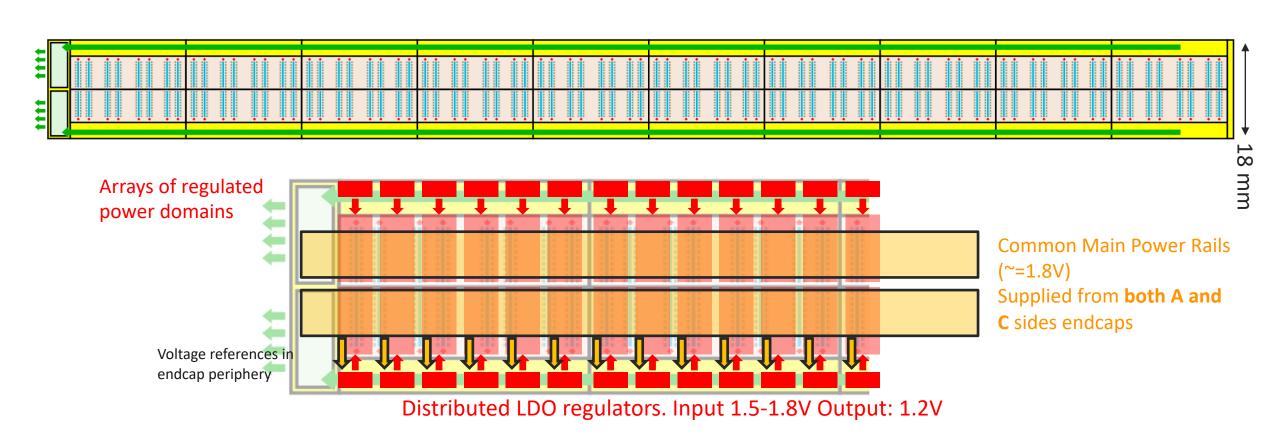

## **On-chip power regulation**

#### ~28 cm

Very preliminary concepts, many questions to study. If power density stays below 15 mW/cm<sup>2</sup> then effective *total* ~= 20 mW/cm<sup>2</sup>

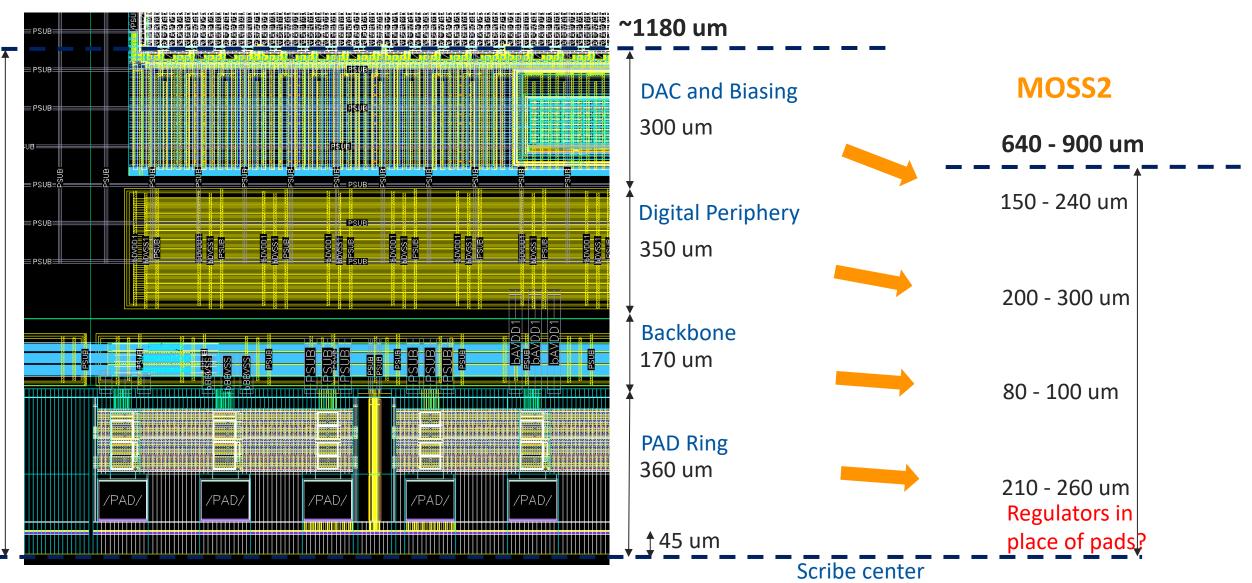

## **Periphery developments**

MOSS

<sup>20230117</sup> ITS3 IPHC | ER2 Sensor Concepts

## Summary and Outlook

#### ER1 tape-out DONE. Production started

ETA: May 2023

#### Need to prepare for timely testing

Documentation of ER1 chips, developments of test infrastructure and test plans

#### Starting new sensor design phase

- ALICE ITS3 Sensor Development framed in EP R&D WP1.2

- Started capturing and categorizing ideas and questions to study (Jan-Feb)

- Review and freeze major chip specifications by mid-March 2023 (Review)

### **REFERENCE MATERIAL**

20230117 ITS3 IPHC | ER2 Sensor Concepts

## MOSS Matrix readout power densities

**Pixel Matrix only**

$[mW/cm^2]$

#### 7 Summary of power values for the modeling of MOSS macros consumption

The following tables provides a summary of the key figures calculated in the other sections to provide a reference for the power analysis on the MOSS chip design.

For hit rate dependent figures, a particle hit flux of  $\Phi = 2.2 \,\mathrm{MHz/cm^2}$  is assumed.

| Analog Power Density          | Pitch 18 µm     | Pitch 22.5 µm         |

|-------------------------------|-----------------|-----------------------|

| $(\mathrm{mW}/\mathrm{cm}^2)$ |                 |                       |

| Static                        | 11              | 7                     |

| Pixel hits                    | 0.001           | 0.001                 |

|                               |                 |                       |

| Digital Power Density         | Pitch $18\mu m$ | Pitch $22.5\mu{ m m}$ |

| $({ m mW/cm^2})$              |                 |                       |

| Leakage (typ.)                | 0.48            | 0.31                  |

| Leakage (abs. max.)           | 25              | 16                    |

| Pixel hits                    | 0.004           | 0.004                 |

| Strobe $(100  \mathrm{kHz})$  | 0.163           | 0.120                 |

| Readout (to periphery)        | 0.025           | 0.025                 |

#### Most pessimistic leakage scenario Analysis needed

## MOSS2 new features

On chip power regulation of sub-regions and common power rail High speed differential on-chip backbone busses High speed output links in endcap Differential I/Os

ADC, Temperature sensors

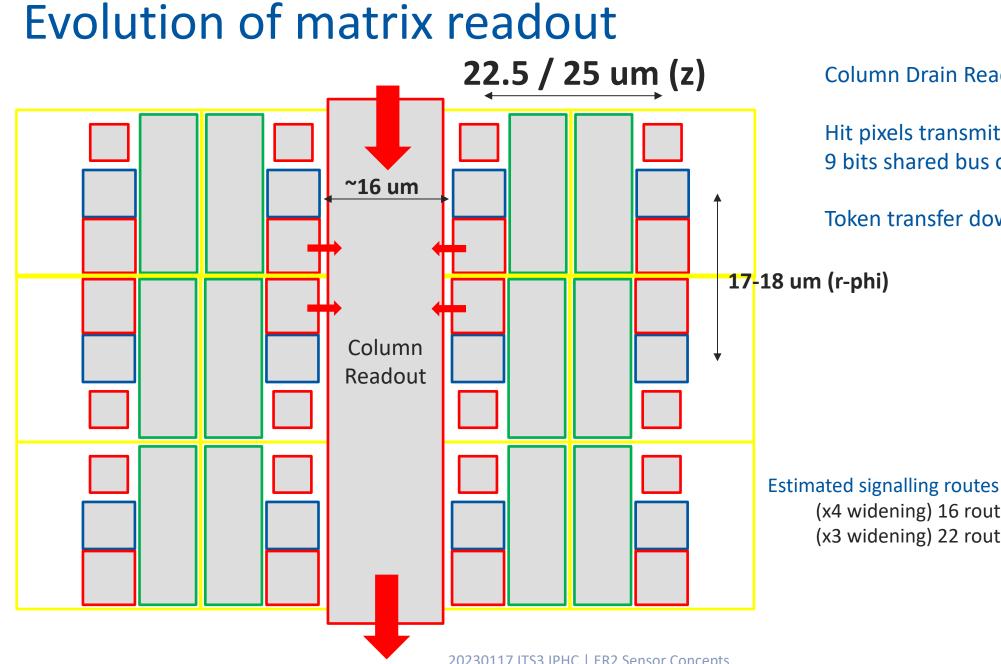

**Column Drain Readout**

Hit pixels transmit their address on 9 bits shared bus one at the time

Token transfer down the column

Estimated signalling routes in 16 µm

(x4 widening) 16 routes M2, 8 ? routes M4 (x3 widening) 22 routes M2, 11 ? routes M4

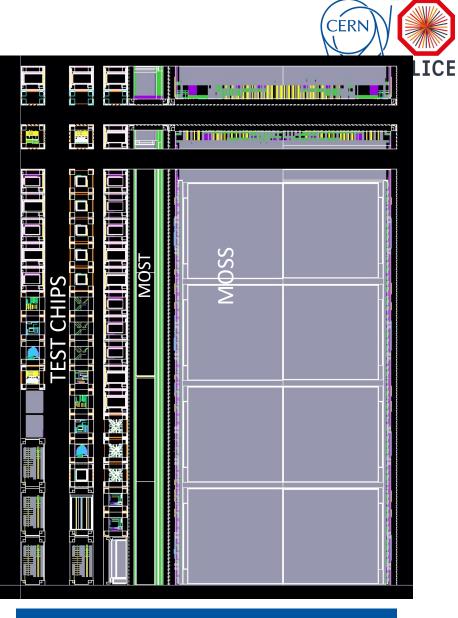

## **MOST** layout snapshots

Detail of the top periphery (biasing generation, slow control, test pulsing)

Detail of the pixel matrix

Detail of the bottom periphery core with the 4 CML outputs

Detail of the stitched backbone buffers

## **MOSS** layout snapshots

#### 6.72 Mpixels

20230117 ITS3 IPHC | ER2 Sensor Concepts

## Towards ER1 – Stitching Interlude

#### Circuits on wafer

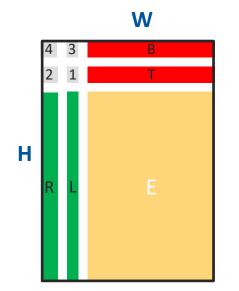

#### Design Reticle (typ. 2×3 cm)