# TRIGGER & DATA CONCENTRATOR MODULE

## REFERENCE MANUAL

**D.** Calvet

Version 1.22

### TABLE DES MATIERES

| 1 | Gen  | eral Overview                                                       | 7  |

|---|------|---------------------------------------------------------------------|----|

| 2 | Boa  | rd Description                                                      | 9  |

|   | 2.1  | Mercury ZX1 FPGA Module                                             | 9  |

|   | 2.2  | Mercury PE1 Evaluation Kit                                          | 9  |

|   | 2.3  | TDCM Carrier Card                                                   | 12 |

|   | 2.4  | Multi-SFP Mezzanine Card                                            | 14 |

| 3 | Har  | dware Features and Installation                                     | 16 |

|   | 3.1  | Power Supply Requirements                                           | 16 |

|   | 3.2  | Primary Clock Selection                                             | 16 |

|   | 3.3  | Boot Mode Selection                                                 | 16 |

|   | 3.4  | Multi-SFP Mezzanine Card                                            | 17 |

|   | 3.5  | Ethernet Connection                                                 | 17 |

|   | 3.6  | Connection of a RS232 Terminal                                      | 17 |

|   | 3.7  | Reset Means                                                         | 18 |

|   | 3.8  | LEDs                                                                | 18 |

|   | 3.9  | NIM I/O's                                                           | 19 |

|   | 3.10 | TTL I/O's                                                           | 20 |

| 4 | Soft | ware Installation                                                   | 22 |

|   | 4.1  | Embedded Firmware and Software                                      | 22 |

|   | 4.2  | The Mini-BIOS Configuration Utility                                 | 23 |

|   | 4.3  | Embedded Software Compilation                                       | 25 |

|   | 4.4  | Migration to Newer Versions of Vivado                               | 25 |

|   | 4.5  | Project portability across location and host computer               | 31 |

|   | 4.6  | Dual CPU version of TDCM embedded software                          | 32 |

|   | 4.7  | Embedded Linux on the TDCM                                          | 33 |

| 5 | Mas  | ster Trigger/Clock Module Interface (PandaX-III specific interface) | 35 |

|   | 5.1  | Physical Layer                                                      | 35 |

|   | 5.2  | Message Format                                                      | 37 |

|   | 5.3  | Line Fncoding                                                       | 39 |

|    | 5.4  | Bit I  | Error Rate Tester                                                    | 39  |

|----|------|--------|----------------------------------------------------------------------|-----|

| 6  | Inte | erface | e to T2K Slave Clock Module (T2K specific interface)                 | 41  |

|    | 6.1  | Phy    | sical Layer                                                          | 41  |

|    | 6.2  | Mes    | ssage Format                                                         | 42  |

| 7  | Inte | erface | e to a Front-end Unit                                                | 45  |

|    | 7.1  | Phy    | sical Layer                                                          | 45  |

|    | 7.   | 1.1    | Optical Transceiver and Optical Fiber Interface                      | 45  |

|    | 7.   | 1.2    | Copper Interface Using a RJ45 Cable                                  | 45  |

|    | 7.2  | TDC    | CM – FE Communication Principles                                     | 45  |

|    | 7.3  | Mes    | ssage Format – Virtual Channel A                                     | 47  |

|    | 7.4  | Mes    | ssage Format – Virtual Channel B                                     | 49  |

|    | 7.5  | Mes    | ssage Format – Virtual Channel C                                     | 50  |

|    | 7.6  | Link   | Clocking and Global Clocking                                         | 53  |

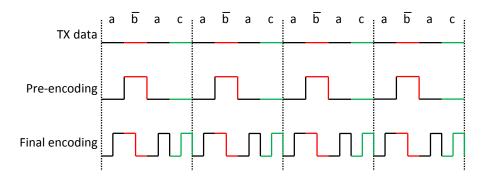

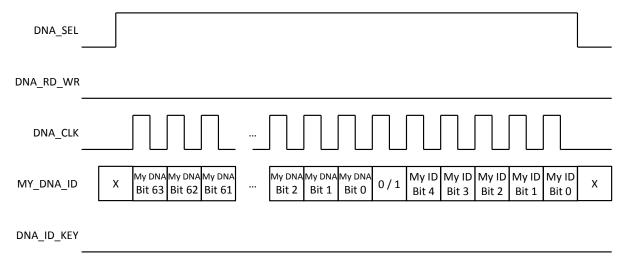

|    | 7.7  | Line   | Encoding                                                             | 55  |

|    | 7.   | 7.1    | Link from the TDCM to the FEs                                        | 55  |

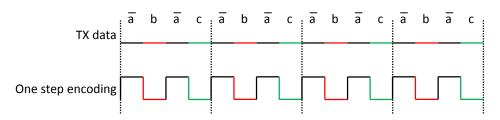

|    | 7.   | 7.2    | Link from the FE to the TDCM                                         | 57  |

|    | 7.8  | Esta   | ablishing TDCM-FE communication and handling loss of synchronization | 58  |

|    | 7.9  | TDC    | CM to FE Link Bit Error Rate Tester                                  | 60  |

|    | 7.10 | FI     | E to TDCM Link Bit Error Rate Tester                                 | 62  |

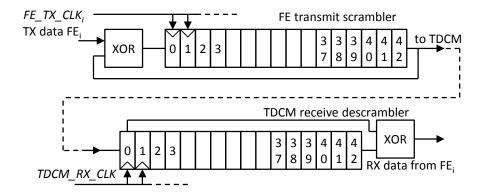

|    | 7.11 | Fı     | ront-End Identification and Enumeration Procedure                    | 64  |

| 8  | TD   | CM Lo  | ocal Register and Memory Map                                         | 68  |

|    | 8.1  | Con    | figuration Registers                                                 | 68  |

|    | 8.2  | Ring   | g Buffer Interface                                                   | 94  |

|    | 8.3  | Dua    | Il-ported Memory Blocks                                              | 98  |

| 9  | Fro  | nt En  | d Node Resource Map1                                                 | .00 |

|    | 9.1  | Inte   | rnal Configuration Registers1                                        | .00 |

|    | 9.2  | Dua    | l-ported Memory Blocks1                                              | .21 |

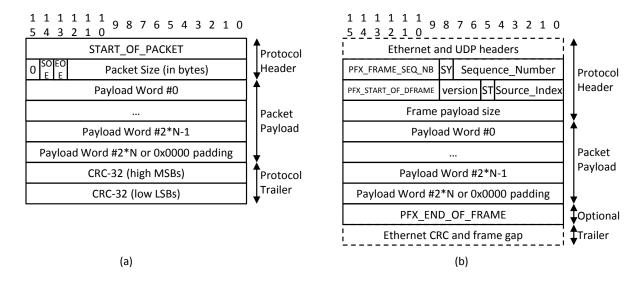

| 1( | ) F  | orma   | at of Messages and Data Packets1                                     | .24 |

|    | 10.1 | Р      | refix-code Format1                                                   | .24 |

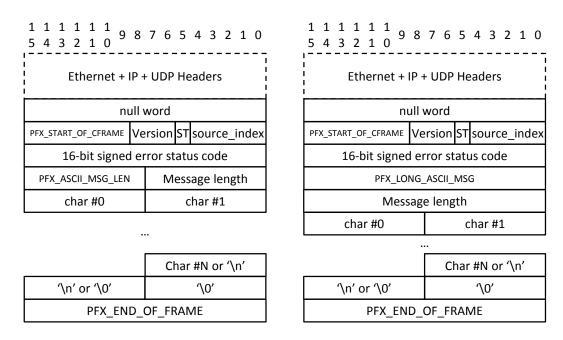

|    | 10.2 | Fı     | rame Encoding for Configuration Command Replies1                     | .27 |

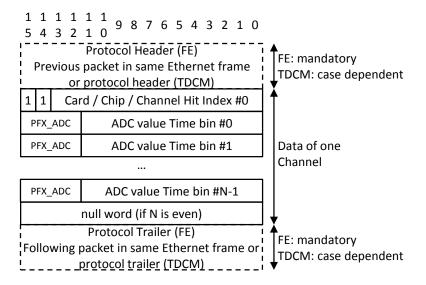

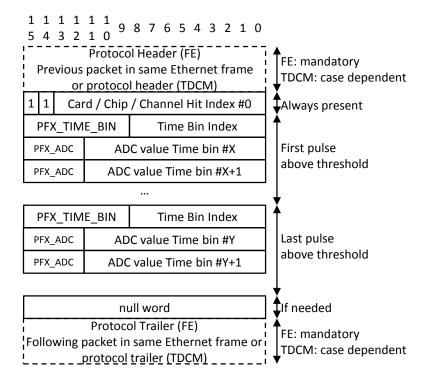

|    | 10.3 | E۱     | vent Data Encoding1                                                  | 28  |

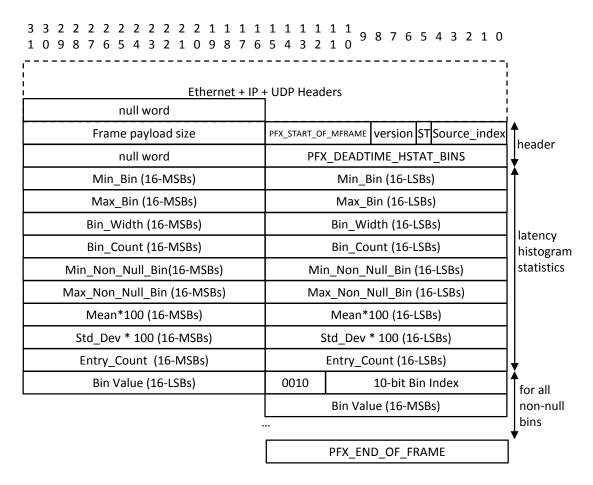

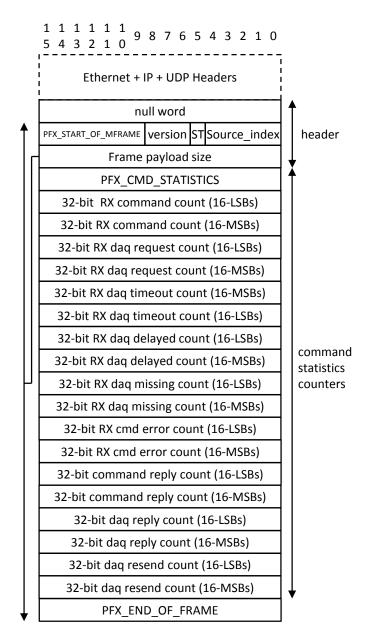

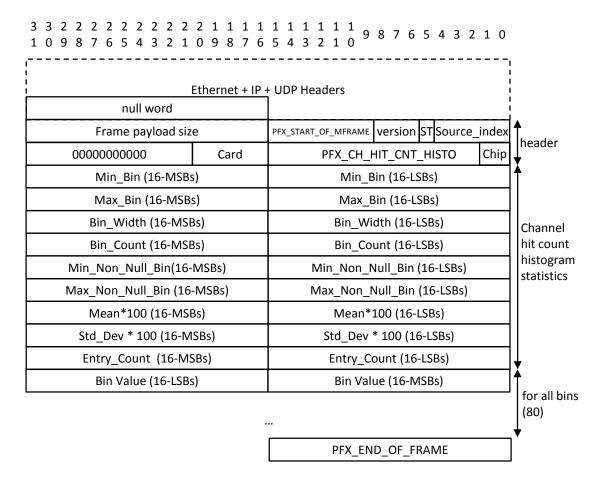

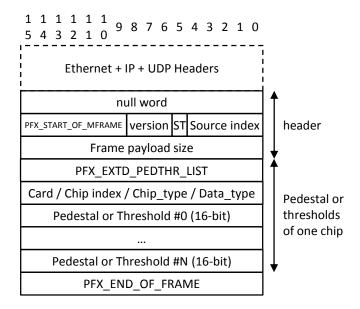

| 1  | 0.4 End | coding of Frames for Monitoring Information Data                | 136 |

|----|---------|-----------------------------------------------------------------|-----|

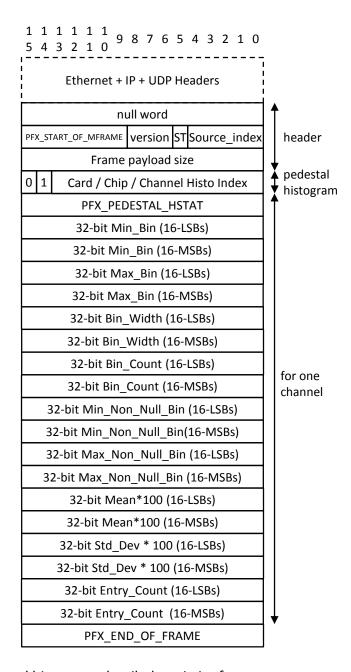

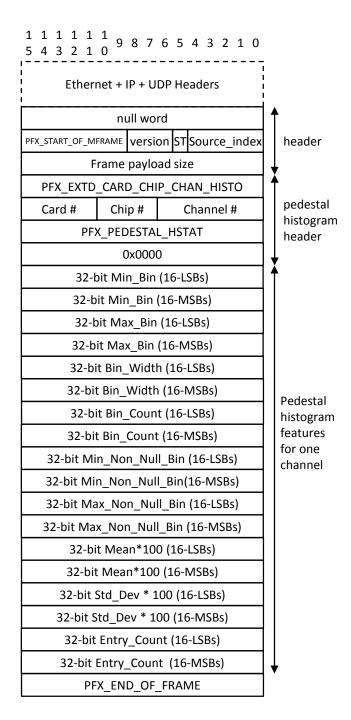

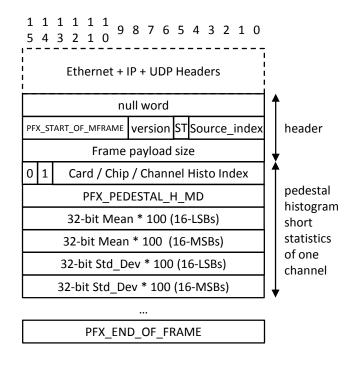

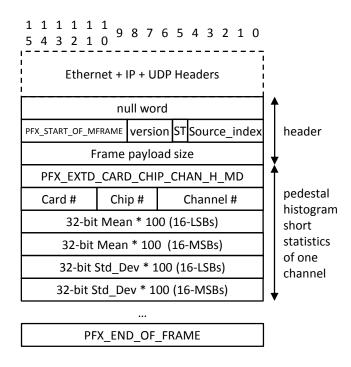

|    | 10.4.1  | Pedestal Histograms                                             | 136 |

|    | 10.4.2  | Dead-Time Histograms                                            | 141 |

|    | 10.4.3  | Inter-Event Time Histogram                                      | 142 |

|    | 10.4.4  | Command Statistics                                              | 143 |

|    | 10.4.5  | Per ASIC Channel Hit Count Histogram                            | 143 |

|    | 10.4.6  | Pedestal Equalization Constants and Zero Suppression Thresholds | 144 |

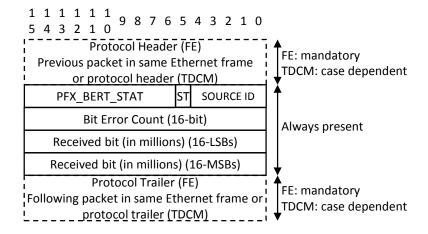

|    | 10.4.7  | Bit Error Rate Tester Statistics                                | 145 |

| 11 | Comma   | nd Server Reference                                             | 147 |

| 1  | 1.1 Cor | mmands that apply to the TDCM                                   | 147 |

|    | 11.1.1  | General Control of the TDCM                                     | 147 |

|    | 11.1.2  | Control of communication links with front-end                   | 148 |

|    | 11.1.3  | Commands for the assignment of indexes to the FEs               | 150 |

|    | 11.1.4  | Message counters                                                | 151 |

|    | 11.1.5  | Front-end presence and state                                    | 152 |

|    | 11.1.6  | Synchronous signal fanout                                       | 152 |

|    | 11.1.7  | TDCM finite state machines                                      | 153 |

|    | 11.1.8  | Trigger generator and trigger control                           | 155 |

|    | 11.1.9  | Data pump                                                       | 158 |

|    | 11.1.10 | Event Builder and Packet Framer                                 | 158 |

|    | 11.1.11 | Commands for Data Acquisition                                   | 159 |

|    | 11.1.12 | Control of the ring buffer of the TDCM                          | 164 |

|    | 11.1.13 | Commands related to communication with the Master TCM           | 165 |

|    | 11.1.14 | Devices controlled by the TDCM over I2C                         | 167 |

|    | 11.1.15 | Commands for the embedded event data generator                  | 169 |

|    | 11.1.16 | Dead-time and inter-event time histograms                       | 170 |

|    | 11.1.17 | Board serial ID and Monitoring                                  | 171 |

|    | 11.1.18 | Commands for the embedded flash memory                          | 172 |

|    | 11.1.19 | SD Memory Card                                                  | 172 |

|    | 11.1.20 | Commands related to non-volatile TDCM settings                  | 173 |

| 1  | 1.2 Cor | mmands that apply to the FE                                     | 174 |

|    | 11.2. | 1 FE Firmware Version, FE index and DNA                      | 175 |

|----|-------|--------------------------------------------------------------|-----|

|    | 11.2. | 2 Direct access to the virtual memory space of the FE        | 175 |

|    | 11.2. | 3 Commands related to the communication link with the TDCM   | 176 |

|    | 11.2. | 4 General FE control commands                                | 178 |

|    | 11.2. | 5 Hit Channel Register Commands                              | 179 |

|    | 11.2. | 6 Commands for pedestal equalization and zero-suppression    | 180 |

|    | 11.2. | 7 Commands for the configuration of front-end ASIC registers | 182 |

|    | 11.2. | 8 Commands related to the configuration of the trigger       | 186 |

|    | 11.2. | 9 SCA Related Commands                                       | 186 |

|    | 11.2. | 10 Synchronization Commands                                  | 187 |

|    | 11.2. | 11 Pulse Generator Control Commands                          | 188 |

|    | 11.2. | 12 Multiplicity Processing                                   | 190 |

|    | 11.2. | 13 Test Data Pattern Generator                               | 190 |

|    | 11.2. | 14 Front end ADC configuration                               | 192 |

|    | 11.2. | 15 ADC deserialization logic settings                        | 192 |

|    | 11.2. | 16 Pedestal Histograms, Equalization and Threshold Setting   | 194 |

|    | 11.2. | 17 Channel Hit Count Histograms                              | 196 |

|    | 11.2. | 18 Dead-time histograms                                      | 196 |

|    | 11.2. | 19 Miscellaneous Monitoring Commands                         | 197 |

|    | 11.2. | 20 Commands Related to SPI Flash Memory of the Front-End     | 197 |

|    | 11.2. | 21 Front-End XADC Configuration and Read-back Commands       | 198 |

| 12 | Clie  | nt Program                                                   | 199 |

| 1  | 2.1   | Installation                                                 | 199 |

| 1  | 2.2   | Using pclient                                                | 199 |

| 1  | 2.3   | Command Reference                                            | 200 |

| 1  | 2.4   | Data Acquisition Commands                                    | 203 |

| 1  | 2.5   | File I/O Commands                                            | 204 |

| 1  | 2.6   | Decoding the Binary Files Recorded by Pclient                | 206 |

| 13 | Ref   | erence Documents                                             | 211 |

| 14 | Doc   | ument history                                                | 212 |

TDCM Reference Manual – Version 1.22 Last revised: September 22, 2022

#### 1 GENERAL OVERVIEW

The Trigger and Data Concentrator Module – TDCM – is a versatile electronic backend module for detector readout systems based on the AFTER [1], AGET [2], ASTRE [3] family of chips. It performs the following functions: 1) distribution of a primary reference clock to a set of front-end cards or modules, 2) distribution of a common trigger signal and global synchronization of the front-ends, 3) configuration and read-back of the front-end and back-end sides, 4) data collection from the front-end, 5) slow control and monitoring of the front-end and back-end sides.

The TDCM is primarily designed for the neutrino-less double beta decay experiment PandaX-III, but it is also intended to use it for other applications that have comparable requirements.

The TDCM can be used as a master device where it uses its own local reference clock, or it can be used as a slave device where it receives the primary clock and trigger from another master device, e.g. another TDCM or some other module. Master and slave TDCMs are noted M-TDCM and S-TDCM respectively. A system may include at most one M-TDCM, and can have one or several S-TDCMs.

Depending on hardware configuration, a TDCM can control up to 32 front-end units. In PandaX-III, the basic front-end unit is a front-end card, FEC, which is equipped with 4 AGET chips and FPGA logic to communicate with the TDCM. In T2K-II, the elementary front-end unit can be a front-end card, called the ARC, which is equipped with 4 AFTER or AGET chips and FPGA logic for communication with the TDCM, but it can also be a front-end module, which is composed of two front-end cards, also called FEC, equipped with 8 AFTER chips each, and a front-end mezzanine card, FEM, which includes the FPGA logic for controlling the two FECs and communicating with the TDCM.

In this document, each front-end unit is referred to as a "front-end', noted FE", although the underlying hardware may be a (PandaX-III) FEC, an ARC, or a (T2K-II) FEM and its (T2K-II) FECs. There are nonetheless some differences between the different FEs, and specific features are mentioned when appropriate. Using PandaX-III FEC (256 channels), a TDCM can read out up to 8192 channels. In T2K-II, the maximum channel count per TDCM is 9216 and 36,854 using the ARC (288 channels) and the FEM and its two FECs (576 channels each) respectively.

The TDCM has a number of interfaces to connect to its partner devices. Four NIM level inputs are available to input a reference clock, a baseband trigger signal, and two other signals (e.g. timestamp reset and clock synchronization). Two NIM level outputs are provided to output a busy signal and a user defined signal. Three general purpose TTL level input and three outputs are also available. Alternatively, the primary clock,

trigger and synchronization signals can be provided over a RJ45 cable carrying serially encoded information over LVDS, or an optical interface can be used. Both the RJ45 electrical interface and optical port use a proprietary protocol and encoding. Multiple TDCMs can be cascaded using their master and slave RJ45 port. The TDCM has four high speed transceivers connected to SFP cages. One of these SFP ports is normally used to interface to a control and DAQ PC over Gigabit Ethernet (optical, or electrical using a GBIC – Gigabit Ethernet Interface Converter). The three other SFPs have no specifically assigned function and are available to the user. A second Gigabit Ethernet port (RJ45) is also available. A PCI-Express (Gen 2 x 4 lanes), is also present on the TDCM, but it is not supported by default (and even it is currently untested).

The interface to the front-end devices normally uses optical media, although a physical layer based on copper may also be developed in the future if it is needed.

#### 2 BOARD DESCRIPTION

The TDCM is a composite assembly made of three types of electronic boards:

- An FPGA module. For a fast and cost effective development, a commercially available FPGA module was selected: the Mercury ZX1 from Enclustra [4].

- A main carrier board. This custom made board is designed to carry a Mercury ZX1 FPGA module and up to two physical layer mezzanine cards. For development, it is also possible to use the evaluation platform sold by Enclustra, the Mercury PE1. With this platform, some of the interfaces of the full size TDCM are not available, and only one physical layer mezzanine card can be used. This configuration is intended for tests and development only.

- Physical layer mezzanine cards. This card is also a custom design. It houses the

physical layer part of the interface to the front-ends, for example optical

transceivers. Other types of physical layer mezzanine cards may be designed

in the future if some application require copper media, or some specific type

of optical transceiver. A physical layer mezzanine card can have up to 16

transceiver/interface ports.

#### 2.1 MERCURY ZX1 FPGA MODULE

A complete description of the Mercury ZX1 FPGA Module is available in [4]. The model that has initially been used for the development of the TDCM is ME-ZX1-45-2C-D10-P or ME-ZX1-45-2I-D10-P. Later versions have switched to a cheaper model from the same family: ME-ZX1-30-2I-D10 or ME-ZX1-30-2C-D10. The main difference between the XC7z030 and the XC7z045 part is that only 4 MGT transceivers at up to 6.6 Gbps are available instead of 8 MGT at up to 10 Gbps. Consequently, the PCIE interface is not available on the TDCM equipped with a ME-ZX-30 FPGA module.

Alternatively, the ME-ZX1-35-1C-D10 or ME-ZX1-35-1I-D10 may also be adequate – although this has not been checked.

#### 2.2 MERCURY PE1 EVALUATION KIT

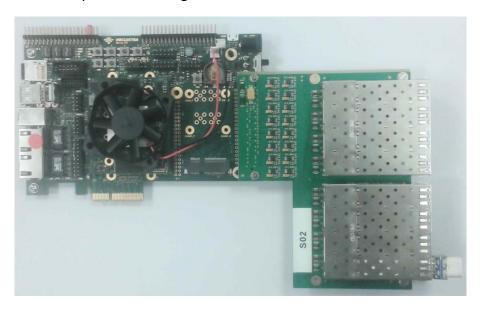

A development version of the TDCM is implemented on the commercially available Mercury PE1 Evaluation kit made by Enclustra. This hardware configuration can be equipped with only one physical layer mezzanine card and it cannot be interfaced to a master trigger and clock distributor. This setup is normally only used for firmware and software development. A picture of the TDCM mock-up built with the Enclustra PE1 evaluation kit is shown in Fig. 1. Connection to the data acquisition PC can be done with the Gigabit Ethernet port of the Mercury PE1 board but this configuration does not support Jumbo frames. Alternatively, an adapter board that converts the PCI Express connector into several SFP+ and SMA connectors can be purchased from Enclustra. This hardware allows the implementation of Gigabit Ethernet using 1000-baseX physical

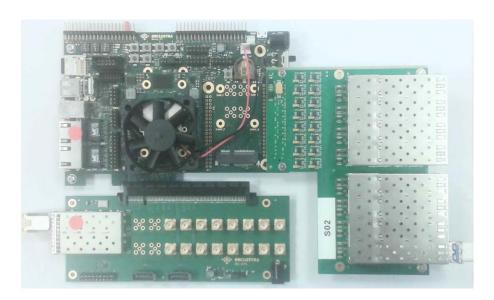

layer and can support Jumbo frame with the appropriate MAC device. This configuration of the TDCM mock-up is shown in Fig. 2.

Fig. 1. TDCM mock-up on Enclustra PE1 evaluation kit.

Fig. 2. TDCM mock-up on Enclustra PE1 evaluation kit with the PCIe breakout.

The physical layer mezzanine card is not mandatory, but in this case, no FE can be connected. If present, the physical layer mezzanine card must be screwed on the PE1 evaluation kit using M2.5 screws and 8 mm standoff. On the front side of the physical layer mezzanine card, M3 screws and 18 mm standoff shall be used. A heat sink and a fan is required for the FPGA module. When using the on-board Ethernet, connect the host to the RJ45 port closest to the USB connector on the front panel side of the PE1 evaluation kit (marked with a red sticker on the picture in Fig. 1). When the PCIe breakout board is used, a GBIC should be used, in the SFP cage closest to the PCIe

connector (see Fig. 2). Also, in this configuration, the board must be powered from the circular jack on the PCIe breakout board instead of the power jack of the PE1 board.

For both hardware variants, jumper VSEL\_A should be set to position "A" while jumper VSEL\_B should be set to position "B". Switches CFG\_A should be set OFF; OFF; OFF; ON. This corresponds to a default boot from the MicroSD flash. Switches CFG\_B should be set OFF; OFF; ON; ON. The PE1 evaluation kit contains 4 user defined DIP switches and 4 push buttons. Their usage is shown in Table 1.

| Table 1 . Usage of PE1 card user DIP switches and push button | Table 1 | . Usage of PE1 | card user DIP | switches and | push buttons |

|---------------------------------------------------------------|---------|----------------|---------------|--------------|--------------|

|---------------------------------------------------------------|---------|----------------|---------------|--------------|--------------|

| Resource       | TDCM mock-up usage |

|----------------|--------------------|

| User switch #1 | DBG_SEL<0>         |

| User switch #2 | DBG_SEL<1>         |

| User switch #3 | DBG_SEL<2>         |

| User switch #4 | BIOS_N             |

| Push button #0 | RESET_N            |

| Push button #1 | MAN_TRIG_N         |

| Push button #2 | MAN_SYNCH_N        |

| Push button #3 | MAN_CLR_N          |

For proper operation of the TDCM mock-up on the PE1, a jumper must be installed between pin #35 and pin #36 of connector IOA. This connects and internally generated 25 MHz clock to the primary external clock input of the TDCM mock-up.

The firmware of the TDCM mock-up defines 16 debug output pins that can be used to spy-on internal signals with an external oscilloscope or logic analyzer. Up to 8 groups of 16 signals can be observed according to the position of user switches DBG\_SEL<3..0>. The observable signals are mapped to FPGA I/O pins connected to connector IOA as shown in Table 2.

Table 2 . Location of debug output pins (connector IOA).

| Resource | Pin# | Pin# | Resource |

|----------|------|------|----------|

| DBG<0>   | 31   | 32   | DBG<1>   |

| DBG<2>   | 29   | 30   | DBG<3>   |

| DBG<4>   | 27   | 28   | DBG<5>   |

| DBG<6>   | 25   | 26   | DBG<7>   |

| DBG<8>   | 21   | 22   | DBG<9>   |

| DBG<10>  | 19   | 20   | DBG<11>  |

| DBG<12>  | 17   | 18   | DBG<13>  |

| DBG<14>  | 15   | 16   | DBG<15>  |

The observable internal signals are defined in the VHDL source code of the TDCM mock-up and is changed as needed during firmware development.

Connection to a RS232 terminal console is done through a USB converter on-board the PE1 evaluation kit. A micro-USB cable should be connected on the connector close to the power supply input. It may be necessary to install the FTDI drivers for the USB-RS232 bridge. Console settings are 115.000 bauds, 8 bit, no parity. Note that the USB section of the PE1 board and some other logic is powered from USB. In some cases, it can be necessary to power off the PE1 board and disconnect it from the USB to entirely reset the board.

The TDCM mock-up on the PE1 evaluation kit requires a specific version of the TDCM firmware and software (note also that it is different depending on whether the PCIe breakout board is used or not), but besides this, the mock-up supports almost exactly the same set of commands, and uses the same tools and methods as the full-size TDCM.

#### 2.3 TDCM CARRIER CARD

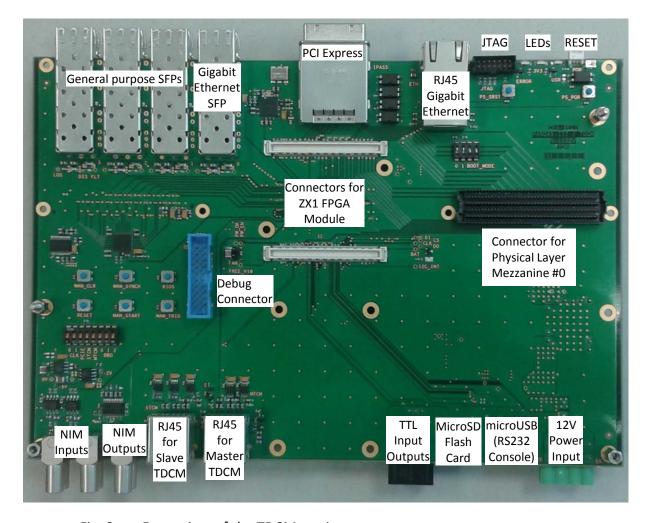

The TDCM carrier card is a 6U form factor electronic board designed to accommodate a Mercury ZX1 FPGA module, one or two physical layer mezzanine cards (with up to 16 links each). The width of TDCM assembly with a physical layer mezzanine on each side is 8 cm (i.e. 16 HP or the equivalent of 4 slots in a Eurocard chassis). The TDCM carrier receives an external 12V power input and distributes the adequate power voltages to the FPGA module and the mezzanine cards. The TDCM carrier includes a large variety of I/O's to interface to a data acquisition and control PC, to connect to a master trigger and clock distributor module, and to optionally cascade several TDCMs.

Fig. 3. Front view of the TDCM carrier.

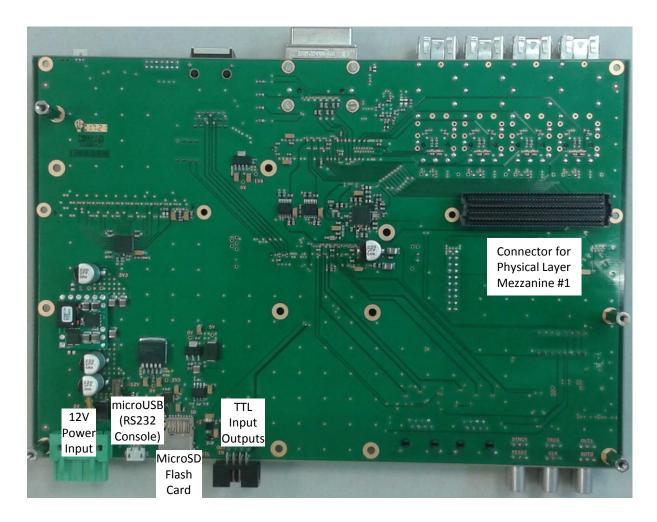

A picture of the rear side of the TDCM is shown in Fig. 4.

Fig. 4. Rear side view of the TDCM carrier.

#### 2.4 MULTI-SFP MEZZANINE CARD

The multi-SFP Mezzanine Card is a custom made board that can house up to 16 small form factor pluggable optical transceivers (SFP) as specified in the Multi-Source Agreement (MSA) document signed by many manufacturers in 2000 and that has become a de-facto standard.

The host side of the multi-SFP Mezzanine Card uses LVDS signaling for the 16 transmit and 16 receive differential transceiver signals. The card also contains some peripheral I/O components controllable via I2C. These are used to control front-panel LED's (two per transceiver), drive the TX disable pin of each transceiver, and read-back the LOS indicator of each transceiver. In addition, it is also possible to access through an I2C multiplexer the Digital Diagnosis Monitoring interface of each transceiver.

The multi-SFP Mezzanine card uses a low pin count FMC connector as defined in VITA 57.1 standard. However, the card is **not compatible with this standard**, and its form factor is also different. Do not connect a multi-SFP Mezzanine Card to a carrier platform others than those recommended without checking in advance that it is compatible.

Fig. 5. Front view of the multi-SFP Mezzanine Card.

A front view picture of the multi-SFP Mezzanine Card is shown in Fig. 5. Each of the 16 slots can accept a SFP transceiver. A port number is used to identify each SFP. If two multi-SFP Mezzanine Cards are connected to a carrier board, the port number of the second multi-SFP Mezzanine are offset by 16. During the procedure of detection and enumeration of the FEs connected to the TDCM, each FE is assigned the ID that corresponds to the port number where it is connected.

There are two front-panel LEDs associated with each transceiver. The green (or yellow) LED indicates the following:

- Permanently OFF: the corresponding port is not active

- Slow blinking: communication is not established with the partner FE

- Permanently ON: communication with the partner FE is established

The yellow (or green) LED illuminates during 100 ms whenever a data packet is received on the corresponding port. The functions of the LED may be changed in the future.

#### 3 HARDWARE FEATURES AND INSTALLATION

#### 3.1 Power Supply Requirements

The TDCM requires a single +12 V power supply. Without any mezzanine card, the typical current drawn by the TDCM carrier and FPGA module is 1 A. Each mezzanine cards (without the optical transceivers) draws an additional 0.5 A. Each optical transceiver is expected to draw ~250 mA from 3.3V, i.e. the equivalent of ~100 mA from 12V. Assuming that 32 transceivers are used, these will draw ~3.2 A from 12 V. In total, a power supply rated 6 A should be adequate (to be confirmed).

The power dissipation of the FPGA module is rather high and it is mandatory that both a heat sink and a fan are used on the TDCM. The fan takes power (12 V) directly from the TDCM carrier board.

#### 3.2 PRIMARY CLOCK SELECTION

The embedded processor of the TDCM and Ethernet communication rely on internal oscillators. Communication with the front-ends is synchronous to a 100 MHz reference clock that is derived from three possible sources selected by clock selection switches as shown in Table 3. When the NIM clock input or the local generator are selected, the 25 MHz supplied clock is multiplied by a PLL to produce the final 100 MHz reference clock.

Table 3 . Reference clock selection switches.

| CLK < 10> | Reference clock source              |

|-----------|-------------------------------------|

| OFF - OFF | Master TCM RJ45 connector (100 MHz) |

| OFF - ON  | NIM Clock input (25 MHz)            |

| ON - OFF  | Local clock generator (25 MHz)      |

| ON – ON   | Illegal                             |

When the primary clock is provided by the Master TCM, the DIP switch MTCM must also be ON.

#### 3.3 BOOT MODE SELECTION

The TDCM is programmed via JTAG during the debugging and development phase. For self-configuration at power up, the board can boot from the micro-SD flash memory card, or the SPI card embedded on the FPGA module. Booting from the flash NAND memory should be possible but was not tested so far. The BOOT\_MODE switches determine which boot device is used as indicated in Table 4.

Table 4 . Boot mode selection switches.

| BOOT_MODE < 10> | Boot device   |

|-----------------|---------------|

| OFF - OFF       | Micro SD card |

| OFF - ON        | QSPI flash    |

| ON - OFF | NAND flash |

|----------|------------|

| ON - ON  | JTAG       |

#### 3.4 MULTI-SFP MEZZANINE CARD

For some development and debugging tasks, it is possible to use the TDCM without any physical layer mezzanine card. However, communication with some front-ends require at least one of the physical layer mezzanine cards. Either the top or the bottom mezzanine card can be installed, or both of them. When only one mezzanine card is installed it is however preferable to connect it to the connector on the top side of the TDCM for reasons of compactness. However, on the first prototype TDCM, only the mezzanine on the bottom side can be plugged due to a connector orientation error for the layout of the PCB.

#### 3.5 ETHERNET CONNECTION

The TDCM has several Ethernet ports. The RJ45 copper port on the front panel of the TDCM is connected to the Ethernet MAC embedded in the ZYNQ processor sub-system of the FPGA module. This device supports 10/10/1000 Mbps speeds but it does not support Jumbo frames. This Ethernet port is therefore disabled by default in the firmware of the TDCM. Instead of the basic ZYNQ MAC, a Xilinx TEMAC coupled to a GTP serial transceiver is used. The translation from the Ethernet 1000-BaseX interface to RJ45 copper requires a GBIC. The device used is AVAGO ABCU-5730ARZ, but other compatible devices should also work. Alternatively, an optical SFP transceiver can be installed if Ethernet over fiber is used. On the TDCM, SFP location #0 is reserved for the SFP/GBIC of the second Ethernet port. Note that the jumper next to SFP location #0 must be installed to enable that SFP port.

Most configurations will use a direct point-to-point connection between the Ethernet SFP/GBIC port and the PC used for DAQ and control, or a connection through a switch if the same PC is used to control multiple TDCMs. Note that the TDCM may not be directly connected to a large Ethernet network, but should reside in a small local private network.

#### 3.6 Connection of a RS232 Terminal

The use of a RS232 terminal is optional except for the first time when a blank FPGA module is used on a TDCM. Several parameters (MAC and IP address, card ID, etc) must be set in the flash memory of the FPGA module before a TDCM becomes operational. Setting these parameters require a RS232 terminal connection. Settings are the following: speed = 115.200 bauds, 8 bits, no parity, no hardware flow control. Locally typed characters must be echoed and outgoing CR characters should be mapped to CR-LF. The TDCM uses a Microchip 2221 USB to RS232 converter. The corresponding drivers may need to be installed on the control PC. A micro-USB cable is required for the

connection. Note that on TDCM version 0, it is necessary that the card is powered ON in order for the PC to detect the new USB device properly. When the TDCM is turned OFF, the connection will need to be restored at the next power ON phase. On TDCM version 1 and beyond, the USB bridge of the TDCM is powered via the USB cable to the host. Hence the device is detected when the cable is plugged and the connection persists independently of the power ON/OFF state of the TDCM itself.

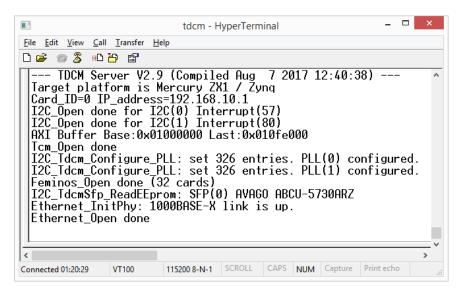

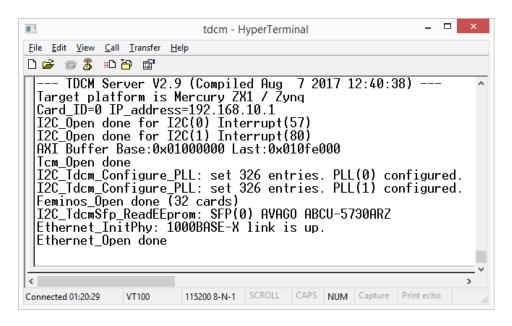

At power-up, messages are displayed on the RS232 console. During operation, fatal error messages may be printed in case of failure. An example of a normal startup is shown in Fig. 6.

Fig. 6. Example of terminal printout after a normal boot.

#### 3.7 RESET MEANS

In addition to the power-on reset, the TDCM has several other means for reset. The "PS\_SRST" push button is a software reset for the embedded processor only. It does not reload or re-program the FPGA part of the TDCM. In practice, this button is seldom used. The "PS\_POR" push button is equivalent to the power-on reset for the processor system: pressing this button reloads the embedded software, re-programs the FPGA and starts the execution of the main TDCM application program. A second push button with the same function is accessible on the front panel of the TDCM, and alternatively a small connector for a remote contactor is available. Note that these last two are not operational on the first prototype of the TDCM. The "RESET" push button is used to reset the user logic part of the FPGA part of the TDCM. Only experienced users may have to press this button.

#### 3.8 LEDs

The FPGA module contains four yellow LEDs. These LEDs are not visible when the TDCM is placed inside a crate. These LEDs are used for development and debugging only.

The TDCM carrier has four LEDs, among these, three are visible from the front panel. A green LED (not visible from the front-panel) is connected to the DONE pin of the FPGA. It indicates that the FPGA part of the system on module has been programmed correctly. If the TDCM boots successfully, this LED will be ON. The green LED on the front panel illuminates when the 3.3V on-board converter is ON.

The yellow LED visible from the front panel is controlled by the FPGA logic. It normally indicates the presence of the primary clock and it should be blinking at ~1 Hz. If this LED stays still or blinks at a different rate, a missing or inappropriate primary clock may be the cause. Note that the function of this LED may be changed in the future.

The red LED visible from the front-panel is connected to an error signal of the application logic. Currently it is used to signal that the TDCM and one or several FEs have lost their common synchronization. When this error LED illuminates, the TDCM will not accept or forward any triggers to the front-ends until the error condition is cleared and some re-synchronization is performed. Note also that the signification of this LED indicator may be changed in the future.

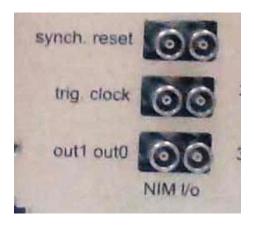

#### 3.9 NIM I/O's

The TDCM carrier has 4 NIM level inputs and 2 NIM level outputs. These I/O's are accessible on standard LEMO connectors at the rear of the board as shown on Fig. 7.

Fig. 7. NIM level I/O's.

The SYNCH input is used to send a signal to all FE for setting to the same phase each local divisor that produces the clock used for sampling detector signals. The RESET input is used to clear event counters in the TDCM and all FEs. The TRIGGER input is one of the possible external trigger sources of the TDCM. The CLOCK input is used to provide an external master reference clock to the TDCM instead of the local oscillator. Currently the external clock must be 25 MHz and it is multiplied locally by 4 to produce the 100 MHz reference clock used by the TDCM. If the external clock input is used, the appropriate switch must be set for the correct selection of the primary clock. NIM

outputs are currently assigned to some internally divided clock signal but may be assigned some particular function in future releases of the firmware. From TDCM firmware version 1.1.7, NIM\_OUT(0) is assigned to an active low BUSY signal. This signal is also available on TTL OUT(0).

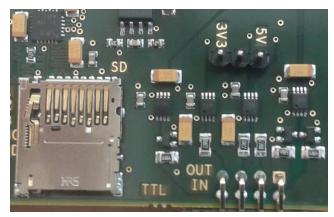

#### 3.10 TTL I/O's

The TDCM carrier has 3 TTL level outputs and 3 inputs. These I/O's are accessible on an 8-pin, dual row, 2.54 mm pitch right angled male header (Amphenol T821108A1R100CEU, Farnell: 2215289) placed next to the Micro-SD memory card, at the rear side of the board. This is shown on the left side of Fig. 8. Inputs are on the left column of pins on the picture (closest to the PCB), while outputs are on the right column of pins (elevated from the PCB).

Fig. 8. TTL I/O connector (left), and voltage selector (right).

The I/O voltage can be selected between 3.3V LVTTL or standard 5V TTL by setting the appropriate jumper between the central pin of the header shown on Fig. 8, right, and the 3V3 or 5V pin. Inputs have a parallel 50  $\Omega$  resistor connected to ground and clamp diodes to ground and the supply voltage (3.3V or 5V). It is recommended that the source driving any of these TTL inputs has 50  $\Omega$  impedance. It is recommended to check that the source can adequately drive a 50  $\Omega$  load, i.e. the high level voltage remains above 2 V when the load is connected. TTL outputs have an additional 22  $\Omega$  series resistor with the standard buffer.

Connections to the TTL I/O's can use discrete wires with crimped contacts (e.g. AMPMODU MODII 181270-2, Farnell: 1772721) or an 8-pin female socket with soldered coaxial cables. Possible references include: TE Connectivity 215308-8 (Farnell: 186-3520), SAMTEC SSW-104-01-G-D or SSW-104-02-S-D (Farnell: 166-8340 or 166-8346), Multicomp 2214S-08SG-85 (Farnell: 1593489), Harwin M20-7830446 (Farnell: 799-1991).

Pin usage is shown in Table 5. Note that pins may be assigned to some other functions in future releases of the firmware.

Table 5 . TTL I/O pin usage.

| Pin        | Function                     |

|------------|------------------------------|

| TTL IN<0>  | CLR_EVENT_COUNT (active Low) |

| TTL IN<1>  | WCK_SYNCH (active Low)       |

| TTL IN<2>  | TRIGGER (active Low)         |

| TTL OUT<0> | BUSY (active Low)            |

| TTL OUT<1> | MULT_TRIG (active Low)       |

| TTL OUT<2> | reserved                     |

The signal CLR\_EVENT\_COUNT is a synchronous clear for the event counter of the TDCM and all FE. The signal WCK\_SYNCH is a synchronous signal sent to all FE for setting to the same phase each local divisor that produces the clock used for sampling detector signals. The TRIGGER signal is obviously used as an external trigger input by the TDCM. System dead-time is reflected on the BUSY pin. The MULT\_TRIG signal is only available with FE that can produce self-trigger primitives and when the TDCM is set to elaborate a trigger signal, called "multiplicity trigger". The bit that result from the processing of multiplicity trigger primitives sent by the FEs can be internally looped back in the TDCM to self-trigger, or it can be forwarded to an external unit for additional processing, combination with other sources, global distribution, etc.

#### 4 SOFTWARE INSTALLATION

#### 4.1 Embedded Firmware and Software

During exploitation, the TDCM will normally boot from the external micro-SD card or from the SPI memory on-board the FPGA module. A bootable file comprises a First Stage Boot Loader (FSBL) for the ZYNQ device on-board the FPGA module, the configuration bitstream for the FPGA, and the executable application program.

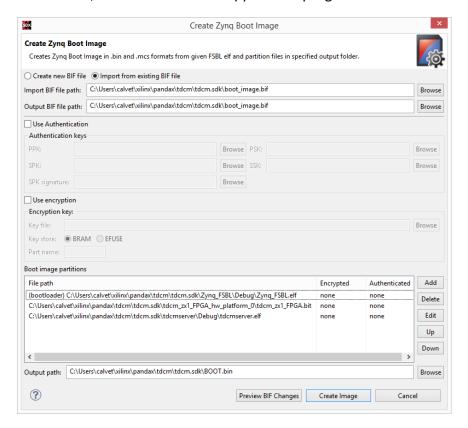

Fig. 9. Window for creating a boot image file.

The bootable file is generated with Xilinx SDK tool (menu "Xilinx Tools" -> "Create Boot Image"). After loading the existing BIF file, the pop-up window shown on Fig. 9 should be displayed. Press the "Create Image" button to generate a new image file. The boot image file can then be copied to the Micro SD card. Note that the file name must be "BOOT.BIN" and cannot be changed. The file must also reside in the root directory of the card, although the card may contain other files and directories.

The "BOOT.BIN" file can also be copied to the SD Card remotely from the client PC program. This is accomplished in pclient (see section 12) by the commands below:

```

be sd mount

be sd wena 1

rcp <boot version data> BOOT.BIN

```

After mounting the SD card, the user must enable write access to the SD card. Then, he can perform a remote copy of the bitstream file to the SD Card with the corresponding command. To keep track of versions, the local copy normally has the target FPGA, board version and revision date contained in the name of the file. However, the target file must always be called "BOOT.BIN" exactly. The transfer takes ~1,5 minute (for a binary file of 15 Mbytes). Take extreme care when doing the copy because the original boot file of the TDCM will be erased. If a corrupted file is loaded, or if the upload fails, the TDCM will no longer boot. If such situation occurs, the micro SD memory card will need to be removed from the TDCM and some proper boot file be restored.

Alternatively the BOOT.BIN file can be programmed in the on board SPI device of the FPGA module via JTAG. This can be accomplished using Xilinx SDK via the menu "Xilinx Tools" -> "Program Flash". Note that if the SPI flash memory is entirely erased, the MAC address, the IP address and other settings of the TDCM will also be erased.

#### 4.2 THE MINI-BIOS CONFIGURATION UTILITY

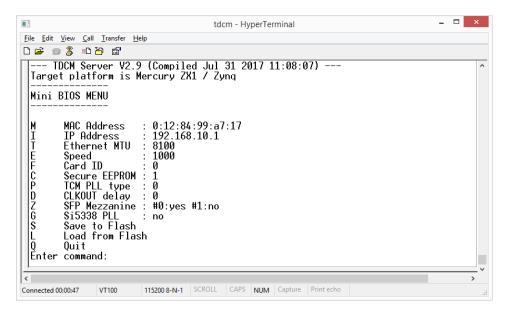

When a TDCM is boot for the first time, its IP address, MAC address and some other parameters must be set. This operation is accomplished via a RS232 terminal using the "mini-BIOS" utility. To enter mini-BIOS, hold the push button "BIOS" down and power ON the TDCM until the menu of mini-BIOS shown on Fig. 10 appears.

The options M, I, T and E are used to set the MAC address, IP address, Maximum Transfer Unit (MTU), and speed of the Ethernet connection to the DAQ and control PC. The TDCM must reside on a private network. The maximum transfer unit should be set to 1500 bytes at most if Jumbo frames are not supported, and can be set to a maximum of 8100 bytes. Note that the native Ethernet controller of the ZYNQ does not support Jumbo frames but the MAC that drives the SFP Ethernet port does. It is recommended to set the speed to 1000 Mbps, although 100 Mbps and even 10 Mbps should work.

The card ID should be set in a way that each TDCM in the system has a different ID. The allowed range is from 0 to 31.

The PLL type and output clock delay should be left to 0.

The SFP mezzanine parameter should be set to 0, 1, 2 or 3 depending on whether no, one, or the two SFP mezzanine cards are installed. Note that on the TDCM prototype, mezzanine #0 is the one that plugs on the bottom side while on subsequent models, mezzanine #0 refers to the one on the top side.

Different types of secure EEPROM may be installed on the FPGA module. Refer to the documentation provided by Enclustra for details. The TDCM does not use the MAC address and other information stored in the secure EEPROM.

The Si5338 PLL is only present on the Enclustra PE1 evaluation kit. This option must not be enabled on the TDCM.

After all the desired changes have been made, they must be saved in the on-board flash memory with the command "S". To exit mini-BIOS and boot the TDCM, press "Q".

An example of a successful boot of the TDCM is shown in Fig. 11. After displaying the version number and compilation date, various peripheral circuits and devices are configured. Finally, the Ethernet port is configured. At this time, the TDCM shall respond to ping commands and to the commands sent by the DAQ PC following the protocol and syntax defined in the relevant sections of this document.

Fig. 10. Mini-BIOS menu.

Fig. 11. Console messages after a normal boot.

#### 4.3 EMBEDDED SOFTWARE COMPILATION

The embedded software of the TDCM has originally been developed using Xilinx SDK release 2015.4. Migration to more recent versions of the tool is described in the next section.

Selecting which Ethernet MAC is used (hard IP in the ZYNQ of the FPGA module or Xilinx TEMAC synthetized in FPGA logic) is defined at the compilation time and cannot be changed at run-time. Normally, the TDCM software is compiled in the Xilinx TEMAC flavor because it supports Jumbo frames while the hard IP of the ZYNQ does not. However, both options are supported. The firmware instantiates both types of controller and need not be changed to select which controller is used. However, producing the desired flavor of the software requires a few changes in the TDCM SDK project itself. Those changes are listed in Table 6.

| Table 6 | . Software ger | neration se | ttings for | Ethernet | MAC selection. |

|---------|----------------|-------------|------------|----------|----------------|

|---------|----------------|-------------|------------|----------|----------------|

| Item                      | ZYNQ hard IP                        | TEMAC soft IP        |

|---------------------------|-------------------------------------|----------------------|

| Include search path       | /network/zynq                       | /network/temac       |

| Pre-processor definitions | USE_EMAC_PS<br>ETHERNET_PHY_KSZ9031 | USE_AXI_ETHERNET_DMA |

| Source files              | ethernet_xemac.c                    | ethernet_axidma.c    |

|                           | ksz9031.c                           | 1000baseX.c          |

Note that on TDCM version 0, the micro SD memory card interface can operate at 6.25 MHz maximum instead of the default value of 25 MHz which is set in Xilinx support library. The speed must be reduced from 25 MHz to 6.25 MHz and the speed of the bus must not be changed to high speed. The modifications to perform in the board support package file xsdps.c are the following:

```

InstancePtr->BusSpeed = 6250000; //SD_CLK_25_MHZ;

...

//Status = XSdPs_Change_BusSpeed(InstancePtr);

```

The modification persists until the BSP source files are re-generated. The SD memory card interface for TDCM version 1, and beyond, can operate at the nominal 25 MHz rate. No modification to the BSP provided by Xilinx is needed.

#### 4.4 MIGRATION TO NEWER VERSIONS OF VIVADO

The migration from the original Vivado 2015.4 release requires that both the firmware side and the embedded software sides are upgraded. Unfortunately, the update is not smooth. The following tips were used. This may not be the optimal way, and it may not work in all cases.

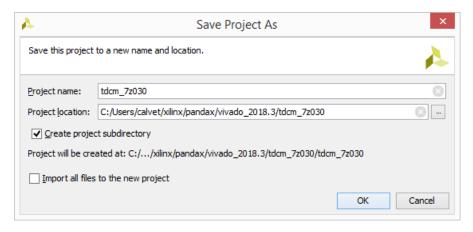

To migrate a complete project while keeping the original version, the first step is to open the original project and save it as a new project in a different directory. This step is shown in Fig. 12. It is assumed that the VHDL source files are not included in the project. After this step is done, the original Vivado (2015.4) tool is exited and the project is re-open with the newer target version of Vivado (e.g. 2018.3). Vivado detects that project was created with an older version and asks the user what to do. Click on "Automatically upgrade to the current version".

Fig. 12. Safe way to copy a Vivado project.

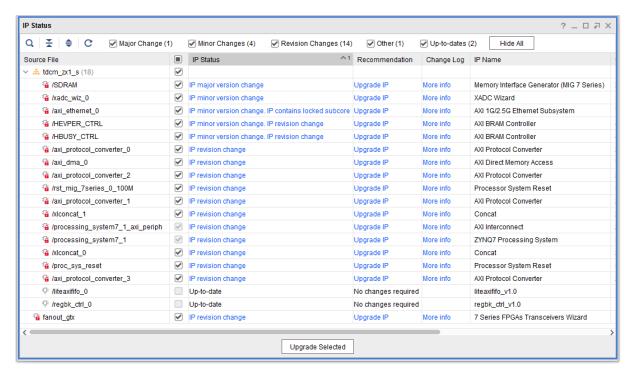

At the next step, Vivado suggest to make a status report on IP changes. Perform this operation and update all the IPs as it is suggested by the tool. An example is shown in Fig. 13.

Fig. 13. IP status when starting the migration procedure.

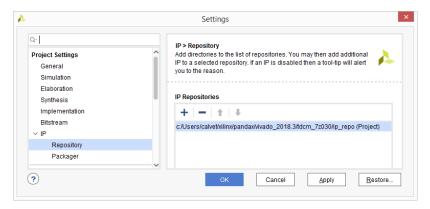

The custom made IP liteaxififo does not run properly on Vivado 2018.3. It has been rewritten. The correct files have to be referenced in the upgraded project. This IP also relies on a FIFO IP from Xilinx catalog. This IP also needs to be upgraded. It is recommended to copy the custom IP in the project directory. Make sure the project references the correct location. An example is shown in Fig. 14.

Fig. 14. Example setting for custom IP location.

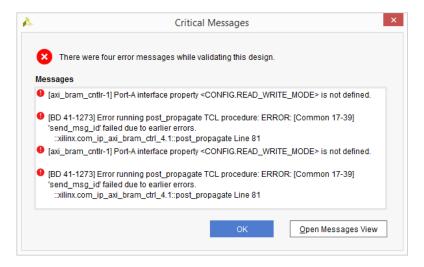

The update of all IPs may work smoothly, or there may be some critical warning messages where Vivado request manual intervention for the update. Actually there were 3 critical warnings at this step when migrating the TDCM from Vivado 2015.4 to 2018.3. The block design that contains the embedded processor shall be opened automatically after the IP migration step. Run the "Validate Design (F6)" step. In the present case, the errors shown in Fig. 15 occurred.

Fig. 15. Block design migration errors.

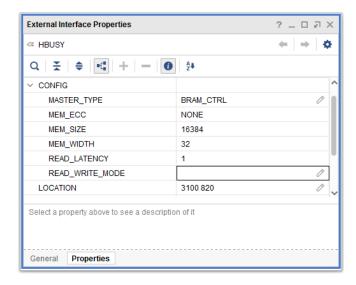

To solve these errors, select the interface port that caused the error and add the missing property "READ\_WRITE" at the place shown on Fig. 16.

Fig. 16. Missing port property after migration.

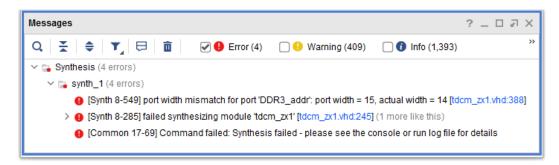

Save the block design and re-run the validation step. There are a few other warning messages, but it seems acceptable to ignore them. Re-run the validation of the block until it passes successfully. Then close the block design. Re-run the IP status update procedure to make sure that all IP are now up to date. Then rerun the usual steps of synthesis, place and route, and bitstream generation. Most probably, synthesis will fail because the PL SDRAM controller was not successfully generated. The typical message that occurs in this case is shown in Fig. 17.

Fig. 17. PL SDRAM controller synthesis failure.

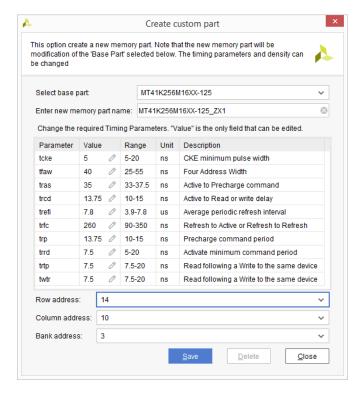

For some unclear reason (to me), every time the block design is modified, it seems necessary to rerun MIG from scratch. Re-open the Block Design, and re-customize the SDRAM controller. A custom SDRAM part must be created from the closest template. Refer to Enclustra ZX1 User Manual for PL SDRAM settings. The number of address lines must be set to 14 instead of the default value 15. Recommended settings are shown in Fig. 18.

Fig. 18. PL SDRAM recommended settings.

Proceed with subsequent steps in MIG leaving suggested values. Re-validate the pinout (do not create a new one), and re-generate the IP. Re-validate the Block Design, save it and close it. Then re-run synthesis, place and route and bitstream generation. Hopefully, these steps will complete without failure and serious warning.

After the bistream has been exported to SDK and SDK has been launched, it is necessary to configure the BSP correctly. The device drivers must be set to "generic" for the custom IP "liteaxififo 0" and "regbk crtl 0".

Changes in the Xilinx FAT file system library from Vivado 2015.4 to Vivado 2018.3 require to manually change the header file ffconf.h on each BSP concerned to enable the use of functions f\_chmod() and f\_utime(). The relevant line should be as follows:

```

#define FF USE CHMOD 1.

```

Note that this change is lost whenever the source files of the BSP are re-generated, unless that change is made in the repository files of the Vivado tool itself.

It is possible that the migration of the BSP from one version of Vivado to a newer release does not work, or that a new BSP is automatically created when opening SDK. One way to handle this situation – may be not the optimal way – is to delete the old BSP and rename the newly created one to the same name as the old one.

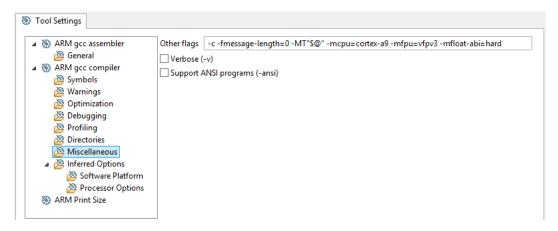

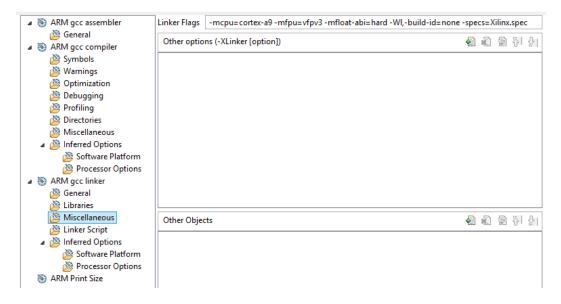

From Vivado 2015.4 to Vivado 2018.3, the compiler for the ARM processor has been changed. While the original projects use "arm-xilinx-eabi-gcc" newer versions of Vivado

use "arm-none-eabi-gcc". The change must be applied for the assembler, compiler, linker and "Print size" program called at the end of build. A number of compilation options must also be changed. The recommended compiler and linker options for Vivado 2018.3 are shown in Fig. 19 and Fig. 20 respectively.

Fig. 19. Recommended compiler options for Vivado 2018.3.

Fig. 20. Recommended linker options for Vivado 2018.3.

Note that a new file, Xilinx.spec, is required. This was not needed with Vivado 2015.4. This additional file is generated automatically by Vivado SDK when a new application project is created, but it is not created when migrating a project from an older version of Vivado. It must be copied manually. In the end, software projects migration should be accomplished successfully. However, the icon that displays if project compilation succeeded or failed currently always indicate a failure, even when compilation was successful.

The above instructions should allow porting all applications, but it may be necessary to delete and re-create the FSBL for the embedded Zynq processor(s). If the FSBL is

deleted and re-created, software changes in the code of the original FSBL must be redone in the newly created BSP.

#### 4.5 Project Portability across location and host computer

Besides a Vivado license, the compilation of the firmware of the full-size TDCM and TDCM mockup with the Ethernet on the PCIe breakout board of the Enclustra PE1 evaluation require the following license: Xilinx LogiCORE, Tri-mode Ethernet Media Access Controller. In principle, this license is not needed for the TDCM mockup that use the embedded Ethernet controller of the Zynq SoC.

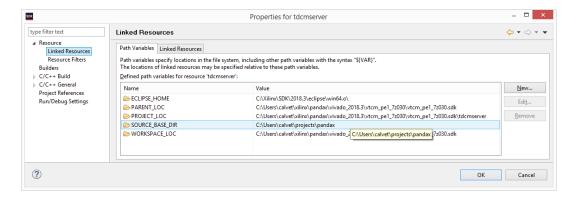

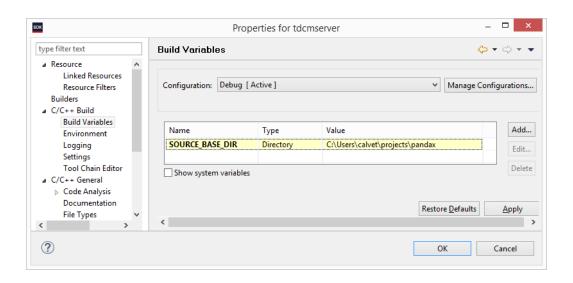

The compilation of the embedded software for all flavors of the TDCM only requires a Vivado license without any license for some IP core. The core of the source files for the embedded software of the TDCM is located in a directory which is separate from the bulk of the project files required by Xilinx tools. When the code is moved to another directory on the same computer, a different disk, or a different machine, the appropriate variables must be updated to point to the correct location. The settings to modify are shown in Fig. 21 and Fig. 22.

Fig. 21. Defining the base directory of the source code files.

Fig. 22. Setting the required build variable.

Note that the source base directory and the C/C++ build variable have to be defined for each application because their scope is not global within the SDK project.

#### 4.6 DUAL CPU VERSION OF TDCM EMBEDDED SOFTWARE

The original embedded software of the TDCM is a command interpreter that runs in bare metal mode on the ARM processor CPU#0 of the on-board Zynq SoC. A new software architecture has been developed to support a dual CPU mode of operation.

In the dual CPU core flavor of the embedded software of the TDCM, the command interpreter is split into two different programs:

- A network bridge program that handles communication via Ethernet with the external world of the TDCM. This task runs on CPU#0.

- A command interpreter program that decodes and executes on the hardware the commands relayed by the network bridge. This task runs on CPU#1.

The two tasks and CPU core communicate with each other via shared memory regions. A set of bi-directional FIFO's, shared variables, and buffers are placed in the On-Chip Memory (OCM) of the Zynq SoC used on-board the TDCM. A pool of 8 buffers of 8 Kbyte is allocated in the OCM for communication in the CPU#0 to CPU#1 direction and a second pool of the same size is reserved for communication in the opposite direction.

A communication FIFO is allocated for communication in each direction. These FIFO's exchange buffer descriptors that point to the buffers that contain the actual message or data payloads. In the CPU#0 to CPU#1 direction, received commands are copied from the Ethernet buffer to a buffer taken in the OCM pool which is posted to the CPU#0 to CPU#1 FIFO. Because commands have a small size, this data copy does not incur a significant penalty. This scheme is simpler to implement than zero-copy transfers. However, in the CPU#1 to CPU#0 direction, zero-copy transfers over the Ethernet have been implemented. Responses configuration or monitoring commands are filled by CPU#1 using buffers taken from the OCM pool. Messages that contain event data reside in the external SDRAM as it is explained in section 8.2. These messages are transferred over Ethernet by CPU#0 in zero-copy mode after they have been posted by CPU#1 in the CPU#1 to CPU#0 FIFO. After a buffer has been consumed by either CPU#0, CPU#1, the Ethernet controller or the AXI Ring Buffer DMA controller (see section 8.2), it must be returned to its original owner for later re-use. A FIFO in the CPU#0 to CPU#1 direction is used to return to CPU#1 and AXI ring buffer DMA controller the buffers that can be recycled. These belong to one of these two pools: the OCM pool of CPU#1 (used to store responses to configuration and monitoring commands), or the SDRAM pool of the AXI Ring Buffer used for storing event data received from the hardwired logic part of the TDCM. Another FIFO, in the CPU#1 to CPU#0 direction, is used to post to CPU#0 the buffers of its OCM pool that have been processed by CPU#1 and can now be recycled to store the future commands that CPU#0 will receive over the Ethernet connection.

In the dual CPU software model of the TDCM, the external SDRAM of the Zynq SoC is split into three regions:

- The lower 1 MB are not accessible,

- the following 511 MB are allocated to CPU#0 exclusively,

- the next 448 MB are allocated to CPU#1 exclusively,

- the upper 64 MB are shared between the hardware based AXI DMA, and the two CPUs.

Note that modifications to the FSBL provided by Xilinx are needed to start the execution of CPU#1 after the transfer of the image program for the two CPUs has been completed by CPU#0 after booting from the SD-card. For a reason that is not understood yet, CPU#1 cannot access the SD-card after CPU#0 has accessed it during the boot process. Hence it is currently not possible to copy any file to the SD-card using the command interpreter in the dual-CPU flavor of the TDCM after the card has boot from the SD-card. But after booting via JTAG, the SD-card is accessible by CPU#1. The previous issue has not been solved yet.

#### 4.7 EMBEDDED LINUX ON THE TDCM

The next planned evolutions of the TDCM embedded software are to install Linux on the ZYNQ SoC. This work is under progress at the Lpnhe group for the upgrade of the T2K experiment. The original single CPU baremetal command interpreter model will nonetheless be developed and maintained for the current usage of the TDCM in various projects – including parts of the T2K experiment (e.g. equipment used for test benches, or detector test beams).

The Linux versions of the TDCM may exist in the following flavors:

- A dual CPU model where CPU#1 runs in baremetal mode the command interpreter program described in the previous section and CPU#0 runs the Linux kernel as well as a MIDAS front-end program for the integration of the TDCM in a global DAQ system based on MIDAS.

- A generic model where Linux runs on both CPU cores and the MIDAS front-end program and the command program are applications that run simultaneously.

The current command interpreter command will need to be adapted so that it can compile and run on Linux.

For either model, inter-process or inter-CPU communication is needed. The scheme via the OCM described in the previous section could be used, or some other mechanism may be implemented. In addition to the MIDAS front-end program, a network bridge

program will also be required to run concurrently so that the command interpreter program (running on CPU#1 or as an oridinary Linux application) can be accessed indifferently via MIDAS or via the "pclient" client application for system development, debugging and remote fault diagnosis.

# 5 MASTER TRIGGER/CLOCK MODULE INTERFACE (PANDAX-III SPECIFIC INTERFACE)

#### 5.1 PHYSICAL LAYER

When the TDCM is used as a slave device of a master device, e.g. in PandaX-III a Master Trigger Clock Module, M-TCM, it is called a S-TDCM. The interface between the S-TDCM and the M-TCM uses a four-pair standard category 6 shielded twisted pair (STP) RJ45 cable. This type of cable is commonly used for Fast/Gigabit Ethernet networking. One pair is split into two wires that carry unipolar 3.3V LVTTL signals while the three other pairs use LVDS. The signals from the M-TCM to the S-TDCM are:

- TCM\_CLK: this signal is a free running 100 MHz reference clock (LVDS).

- TCM\_MOSI (Master Out, Slave In): this signal transports the serially encoded trigger and other synchronous control signals (LVDS).

- TCM\_ENAREM (ENAble REMote): this is an active high 3.3V LVTTL signal to indicate to the S-TDCM that the M-TCM is present and requests the S-TDCM to respond.

The signals from the S-TDCM to the M-TCM are:

- TCM\_REMDET (REMote DETected): this is an active high 3.3V LVTTL signal asserted by the S-TDCM to signal its presence and readiness to the M-TCM.

- TCM\_MISO (Master In, Slave Out): this signal carries serially encoded synchronous data (e.g. trigger acknowledge, busy/release, etc.) from the STDCM to the M-TCM (LVDS).

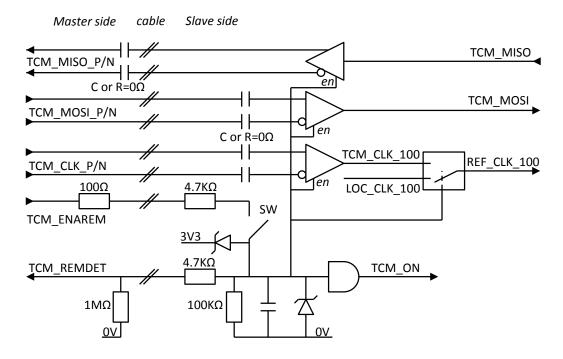

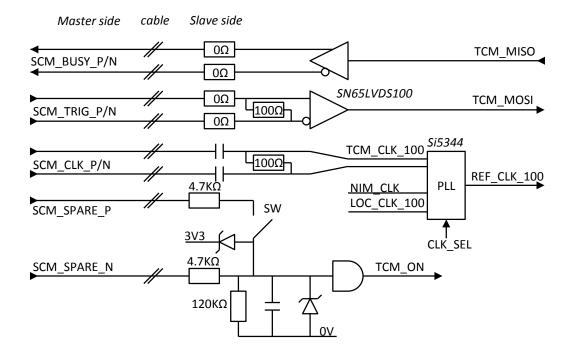

A schematic view of the M-TCM to S-TDCM interface is shown in Fig. 23.

Fig. 23. M-TCM – S-TDCM electrical interface.

The M-TCM de-activates communication with the S-TDCM when it detects a low level on the TCM REMDET line. This happens in the following situations:

- The M-TCM sets a low level on TCM\_ENAREM to voluntary disable communication with the S-TDCM,

- The M-TCM has set a high level on TCM\_ENAREM but no S-TDCM is connected

at the other extremity of the cable, or an S-TDCM is connected but it is

currently not powered, or it is present and powered but SW is open meaning

that it is desired that the S-TDCM operates on its own local clock.

When SW is closed, the S-TDCM takes its locally generated clock as a reference if the M-TCM is not present or if TCM\_ENAREM is low, which happens if the M-TCM is present but not powered, or present and powered but TCM\_ENAREM is not activated. The S-TDCM takes TCM\_CLK\_100 as a reference when both SW is closed and the M-TCM has asserted TCM\_ENAREM high. The signal TCM\_ON indicates to the FPGA logic of the S-DTCM that the M-TCM is present and ready.

Differential pairs may use AC coupling or DC coupling by choosing between capacitors or  $0\Omega$  resistors at the receiving end. The TCM\_CLK\_P/N pair will preferably use AC coupling. Initially, it is proposed to use DC coupling for the TCM\_MOSI\_P/N and TCM\_MISO\_P/N pairs although this may choice may be changed in the future. All differential receivers must be terminated with a  $100\Omega$  differential impedance. This resistor may be integrated in the receiver or it may be external. A failsafe circuit may also be needed.

If DC coupling is used for differential pairs, the M-TCM is not allowed to actively drive any of its LVDS output lines unless a high level is detected on TCM\_REMDET. Similarly, the S-TDCM is not allowed to actively drive the TCM\_MISO\_P/N lines unless a high level is sensed on TCM\_REMDET. If AC coupling is used, the common mode voltage of the differential drivers will be blocked at the receiver end, and differential drivers can be enabled even when there are connected to a remote partner board that is not powered. It is however preferable that differential drivers transmit a constant logic level when no active receiver is detected. Because series resistors are placed on TCM\_ENAREM, limited current will flow from the M-TCM to the S-TDCM if the M-TDCM drives this line to a high level while the S-TDCM is present but not powered and SW is closed.

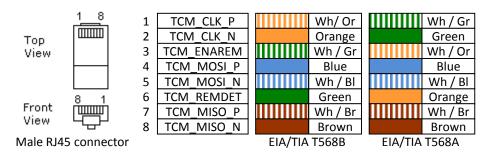

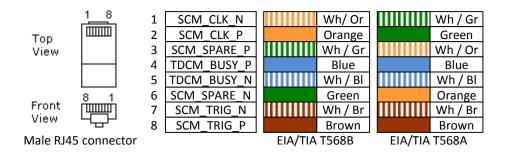

The pin assignment of the RJ45 cable between the M-TCM and the S-TDCM is shown in Fig. 24. Note that colors depend on compliance with one of two possible standards.

Fig. 24. M-TCM – S-TDCM cable pin assignment.

#### 5.2 Message Format

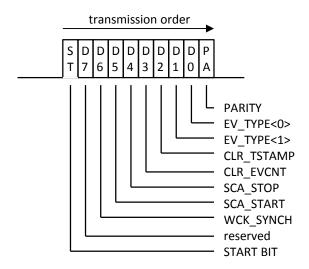

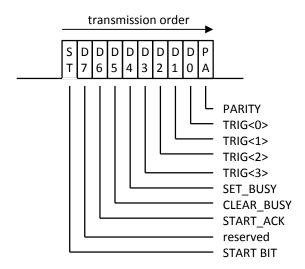

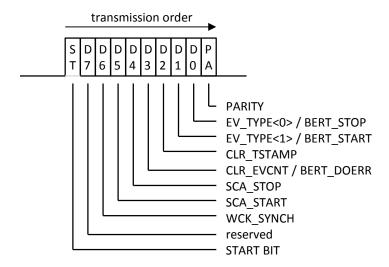

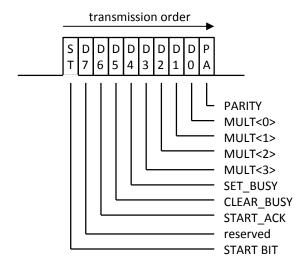

The format of the frames sent from the M-TCM to the S-TDCM before encoding is shown in Fig. 25.

Fig. 25. M-TCM to S-TDCM frame format.

The marking level of the TCM\_MOSI line is a low level. The START\_BIT is a high level. The PARITY bit is the exclusive OR of the START\_BIT and bit D0 to D7, i.e. the total number of bits equal to 1 in a message taken from the start bit to the parity bit (included) is always made even. The bit WCK\_SYNCH is used to synchronize the clock generator of the SCA write clock in each front-end card. The SCA\_START bit is used to synchronously start sampling in the SCA of the ASICs of the front-ends. The SCA\_STOP bit is the trigger. Four types of event can be distinguished by EV\_TYPE<1..0>. The CLR\_EVCNT bit and CLR\_TSTAMP bit are used to synchronously clear the event counter and time stamp counter of all slave cards simultaneously. The CLR\_TSTAMP bit actually performs a preset of the timestamp counter to an initial programmable value. After the last bit of data, the M-TCM must insert a gap of at least 6 symbols before transmitting the next frame. Consequently, the maximum frame rate sent by the M-TCM to the S-TDCM is 1/160 ns = 6.25 MHz. However, the absolute time of synchronization signals can be resolved with 10 ns resolution.

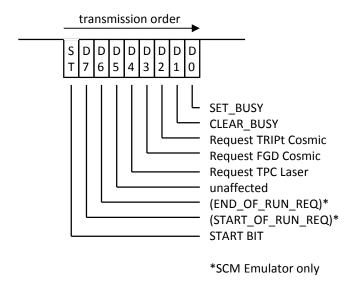

The format of the frames sent from the S-TDCM to the M-TCM before encoding is shown in Fig. 26.

Fig. 26. S-TDCM to M-TCM frame format.

The marking level of the TCM\_MISO line is a low level. The START\_BIT is a high level. The PARITY bit is the exclusive OR of the START\_BIT and bit D0 to D7, i.e. the total number of bits equal to 1 in a message taken from the start bit to the parity bit (included) is always made even. After the last bit of data, the S-TDCM inserts a gap of 6 bits before the next frame. Consequently, the maximum frame rate sent by the S-TDCM to the M-TCM is 1/160 ns = 6.25 MHz.

The bit START\_ACK indicates that the S-TDCM has successfully received the SCA START command from the M-TCM and that the ASICs on the front-end side are now

sampling data. The SET\_BUSY bit is used to acknowledge the reception of the current trigger and indicates that the S-TDCM cannot perform a SCA\_START command until it sends CLEAR\_BUSY. The bit CLR\_BUSY is used to indicate that the FEs have completed processing of the previous event and are now ready to resume the SCA write operation.

The TRIG<3..0> field is used to transfer self-trigger primitives from the S-TDCM to the M-TCM. This is not defined at present.

#### 5.3 LINE ENCODING

The TCM\_CLK\_P/N pair carries a free running 100 MHz clock. The TCM\_MOSI\_P/N and TCM\_MISO\_P/N lines carry 10-bit frames (1 start bit + 8 bit data + 1 parity bit) at 100 Mbps. The transitions on TCM\_MOSI\_P/N are phase aligned by the M-TCM with the transitions (rising edge or falling edge) of the primary clock TCM\_CLK\_P/N. The messages sent by the S-TDCM on TCM\_PISO\_P/N are synchronous to the clock supplied by the M-TDCM, but the phase on the M-TCM side is unknown. It depends on cable length and the various delays of the active components on the path. To recover the messages sent by the S-TDCM, the M-TCM must adjust locally the phase of the received signal with respect to its own local clock.

Operation without any line encoding is only possible using DC-coupling on the corresponding transport lines.

Optionally, a DC balanced protocol is also supported. This protocol can be used with either AC-coupled or DC-coupled lines. (Note: a trivial, almost DC-balanced encoding can be obtained by making a XOR between the non-encoded serial stream with a locally generated bit pattern of alternating 1 and 0's. A more sophisticated encoding scheme will be defined later if needed). The DC balanced protocol can be enabled independently for the S-TDCM to M-TCM link and for the M-TCM to S-TDCM link. Obviously, the settings must be consistent between the M-TCM and the S-TDCM for correct operation.

#### 5.4 BIT ERROR RATE TESTER

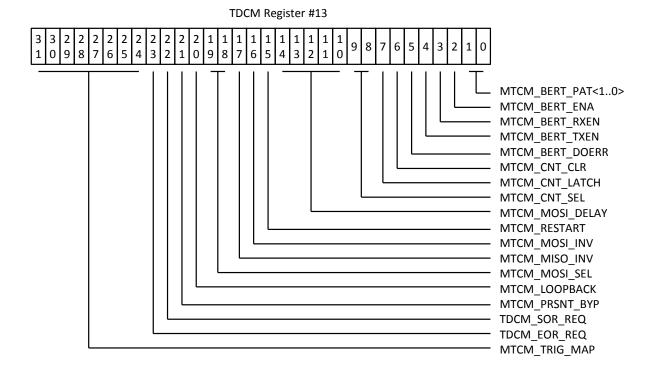

A bit error rate tester for checking the quality of the communication link between the M-TCM and S-TDCM is implemented. The bit error rate tester supports four different standard patterns: PRBS7, PRBS15, PRBS23 and PRBS31. Before any PRBS can be received or transmitted, the S-TDCM must be set first to operate in the bit error test mode by programming the MTCM\_BERT\_ENA bit to one. Once this is done, the bit error test mode can also be engaged on the M-TCM side.

When the bit MTCM\_BERT\_RXEN is set to 1, the S-TDCM tries to look on the received PRBS. As soon as lock is achieved, it compares the received bit stream with the expected pattern, which is generated locally, and counts the eventual errors. Note that the repetition period of the PRBS31 pattern at 100 Mbps is ~21 s. It may take up to this time to gain synchronization.

When the bit MTCM\_BERT\_TXEN is set to 1, the S-TDCM starts sending the selected PRBS to the M-TCM. On the rising edge of bit MTCM\_BERT\_DOERR, a single bit error is inserted.

The bit error rate tester can be run in either direction independently or both directions at the same time, for as long as it is desired. In the current implementation, the bit error counter of the receiver saturates at 255, and the received and transmitted bit counters roll over at 2<sup>24</sup> Mbit, which corresponds to approximately 2 days at 100 Mbps. At the end of a test, the receiver side should be disabled first to avoid that stopping the PRBS on the transmitter side is misinterpreted as bit errors by the receiver side. After the PRBS transmitter and receiver sides of the S-TDCM have been disabled, the bit MTCM\_BERT\_ENA should be cleared. This restores the normal operation of the link between the S-TDCM and the M-TCM.

# 6 INTERFACE TO T2K SLAVE CLOCK MODULE (T2K SPECIFIC INTERFACE)

The TDCM is planned to be used for the readout of the High Angle TPCs (HA-TPCs), in the upgrade of the near detector (nd280m) of the T2K neutrino oscillation experiment. In T2K nd280m, the global synchronization clock and trigger information are distributed in a tree structure starting from a root node which is called the "Master Clock Module – MCM". Synchronous signals are relayed via optical fibers to a certain number of "Slave Clock Modules – SCMs". There is normally one SCM per sub-detector in T2K nd280m. Each SCM makes a fanout of synchronous signals via RJ45 cables to the back-end electronics of its associated sub-detector. The back-end electronics of each sub-detector propagates synchronization signals to the front-end electronics as it is needed. The HA-TPCs require two TDCMs. Although it is called the "Slave Clock Module" the SCM is in reality a master device for the two TDCMs. Care must be taken because of the ambiguous naming of elements.

#### 6.1 PHYSICAL LAYER

The physical layer of the interface between the SCM and the TDCM for T2K is similar to that used in Pandax-III and is based on standard RJ45 cabling. Unfortunately, pin assignment is slightly different and the two interfaces **are not directly compatible** with each other. The first hardware version of the TDCM (N°1102V1) implement the PandaX-III pin assignment while the second hardware version of the TDCM (N°1102V2) uses the T2K-II pin assignment flavor. However, the external hardware interface is unchanged from the PandaX-III flavor to the T2K-II version. Only connector pin assignment is modified.

For T2K-II, the signals from the SCM to the TDCM are:

- TCM CLK: this signal is a free running 100 MHz reference clock (LVDS).

- TCM\_TRIG: this signal transports the serially encoded trigger and other synchronous control signals (LVDS). This is equivalent to TCM\_MOSI in the Pandax-III denomination.

- TCM\_SPARE: this signal should not be used. On some SCMs, it transports a pulse per second signal.

The signal from the TDCM to the SCM are:

• TCM\_BUSY: this signal carries serially encoded synchronous data (e.g. trigger acknowledge, busy/release, etc.) from the TDCM to the SCM (LVDS). It is equivalent to TCM\_MISO in the PandaX-III terminology.

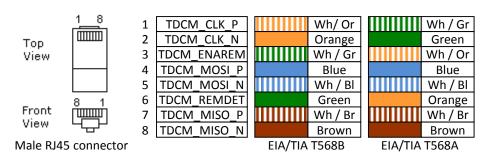

The assignment of these signals to a standard RJ45 connector is shown in Fig. 27.

Fig. 27. RJ45 pin assignment for SCM – TDCM interface (T2K flavor).

Besides a different pin assignment for the RJ45 connector, the main physical difference between the PandaX-III and T2K-II interface variants is that the T2K flavor does not implement means for enabling and detecting the remote partner (i.e. the unipolar signals TCM\_ENAREM and TCM\_REMDET signals). A schematic view of the SCM to TDCM interface is shown in Fig. 28.

Fig. 28. Schematic of SCM-TDCM interface (TDCM N°1102V2 variant).

The reference clock from the SCM is AC-coupled on the TDCM side and directly fed to one input of a Si5344 PLL. This PLL can also take as a input clock a locally generated clock or the external clock supplied via the NIM-LEMO connector on the front panel of the TDCM. Reference clock selection is done by DIP switches. The SCM\_SPARE\_P/N signals connect to the presence detection circuit but this will not operate with the SCM.

#### 6.2 Message Format

The format of the frames sent from the SCM to the TDCM is shown in Fig. 29.

|   |        | _   | i                           |   |                          |        |                          |   |   |

|---|--------|-----|-----------------------------|---|--------------------------|--------|--------------------------|---|---|

|   |        | 6 ( |                             | _ | _                        | 3<br>1 |                          | 0 |   |

| 1 | S<br>T | 0   | Trigger & Flags<br>(16-bit) |   | Spill Number<br>(16-bit) |        | Event Number<br>(32-bit) |   | 1 |

Fig. 29. SCM to TDCM frame format.

When no data are transmitted from the SCM to the TDCM, the line SCM\_TRIG\_P/N is set to a constant high level. A message is composed of 66 bits and starts by a start bit (set to 0), followed by one unused bit (also set to 0), 16 bits of trigger and flags, a 16-bit spill number and a 32-bit event number. The message does not include any parity bit. It is sent at 100 Mbps, MSB first, and it does not require further encoding because the corresponding transmission line between the SCM and the TDCM is DC-coupled.

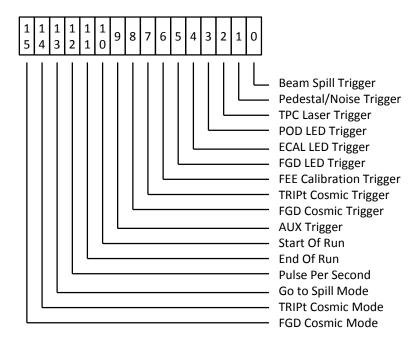

Trigger bits and flags is detailed in Fig. 30.

Fig. 30. SCM to TDCM message trigger bits and flags.

The flags Start Of Run and End Of Run are defined but not used by the SCM. The TDCM ignores the flags FGD Cosmic Mode, TRIPt Cosmic mode, and Go to Spill Mode. It also ignores the trigger bits FGD LED trigger, ECAL LED trigger and POD LED trigger. Other sources of trigger can be received but need to be enabled explicitly. The PPS (Pulse Per Second) flag is currently not used by the TDCM, but it may be used in the future.

The format of the frames sent from the TDCM to the SCM is shown in Fig. 31.

Fig. 31. TDCM to SCM message format.

The TDCM does not generate messages that contain the flags Request TRIPt Cosmic, Request FGD Cosmic and Request TPC Laser. Upon the reception of a valid trigger, the TDCM responds with one message where the SET\_BUSY flag is set. After the readout of the corresponding event and when the front-end electronics is ready to capture the next event, the TDCM sends a message where the CLEAR\_BUSY flag is set. Failure to return the messages with either the SET\_BUSY or CLEAR\_BUSY flag set within a given time frame is a fatal error that will cause the abort of the current run. For trigger sources that are either masked or ignored by the HA-TPCs, the TDCM will return to the SCM a message with the CLEAR\_BUSY flag set followed after a short amount of time by a message with the CLEAR\_BUSY flag set.

The flags START\_OF\_RUN\_REQ and END\_OF\_RUN\_REQ are non-standard in T2K and are only intended to be used with an emulator of the SCM during the development phase of the TDCM-SCM interface block firmware and embedded software.

### 7 INTERFACE TO A FRONT-END UNIT

#### 7.1 PHYSICAL LAYER

The interface between the TDCM (standalone of slave) and each FE normally uses an optical fiber media. Small Form factor Pluggable (SFP) transceivers in compliance with the Multi-Source Agreement (MSA) are a recommended choice. Alternatively, or for debugging purposes, a copper cable interface is also supported.

#### 7.1.1 OPTICAL TRANSCEIVER AND OPTICAL FIBER INTERFACE

The physical layer mezzanine card supports standard SFP transceivers, either single fiber bi-directional transceivers or common dual fiber transceivers. If bi-directional transceivers are used, it is recommended to use 1310 nm TX / 1490 nm RX transceivers on the TDCM side. These transceivers can operate with single mode or multimode fiber. Alternatively, dual-fiber transceivers at 850 nm wavelength are also adequate. These devices require multimode fiber. Other types of optical media (e.g. LED transceivers for plastic optical fiber) will be supported if this is needed.

#### 7.1.2 COPPER INTERFACE USING A RJ45 CABLE

The copper interface between the TDCM and a FE is physically almost identical to the interface between the M-TCM and the S-TDCM. The four pairs of an RJ45 cable are assigned the same functions. Cable usage is defined in Fig. 32.

Fig. 32. TDCM – FE cable pin assignment.

The same electrical schematic as the one shown in Fig. 23 can be used. However, it is recommended to use AC-coupling by default for all differential pairs. In this case, LVDS transceivers need not the tristate capability. The TCM\_CLK\_P/N carries the primary 100 MHz reference clock and the TCM\_MOSI-P/N serial stream is synchronous to that clock. Similarly, the serial stream sent by the FE to the TDCM on the TCM\_MISO\_P/N pair must be synchronous to the same 100 MHz reference clock. Message format and line encoding on TCM\_MISO and TCM\_MOSI for the S-TDCM — FE link are different from that used for communication between the M-TCM and S-TDCM.

#### 7.2 TDCM - FE COMMUNICATION PRINCIPLES

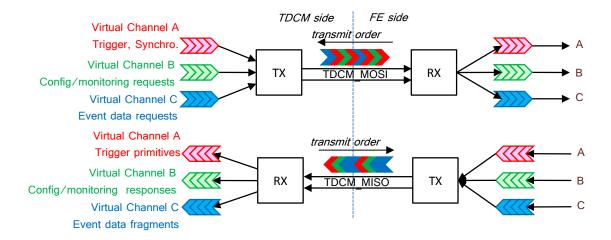

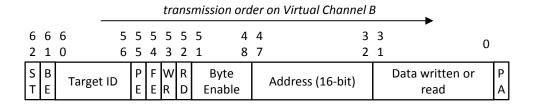

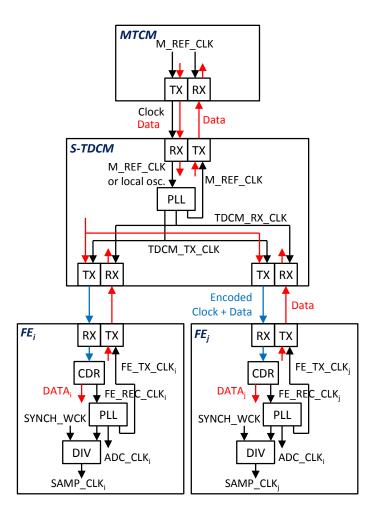

Communication between the TDCM and the FEs use an asymmetric network. In the TDCM to FE direction, a low-skew, multi-cast network is used. The same bit stream is sent by the TDCM to all FEs simultaneously. In the FE to TDCM direction, each FE has its own private point-to-point communication link with the TDCM.

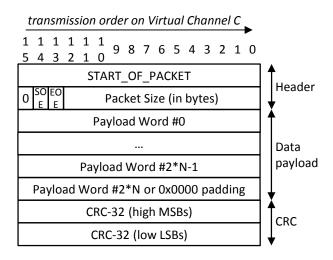

Communication between the TDCM and the FEs requires transporting different types of messages: isochronous information (trigger, time-stamp clear order), runtime configuration parameters, read-back parameters, periodic monitoring requests, responses with the value of the monitored variable, request for data, response messages containing event data fragments, etc. All these different types of messages are classified in three different categories. Using three virtual channels implemented over the physical links using time division multiplexing, messages from the three different classes are exchanged concurrently in both directions between the TDCM and the FEs. The following virtual channels are defined:

- Virtual Channel A is used to transport isochronous messages (mostly trigger information) from the TDCM to all FEs. In the opposite direction, it transports trigger primitives, trigger acknowledge and other synchronous information.

- Virtual Channel B is used for runtime parameter configuration and read-back as well as slow control monitoring of the variables measured by each FE (e.g. voltage, current, temperature).

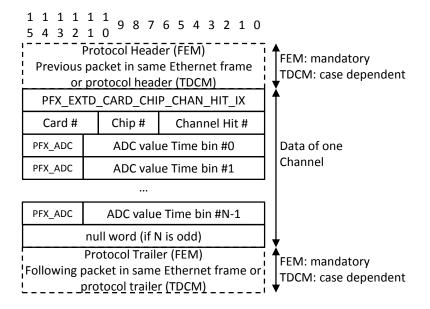

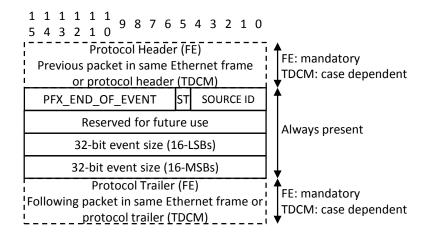

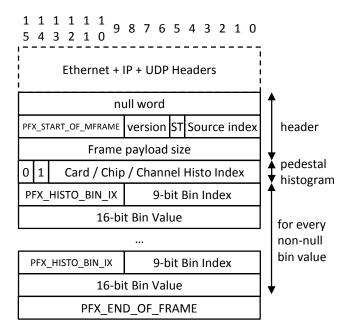

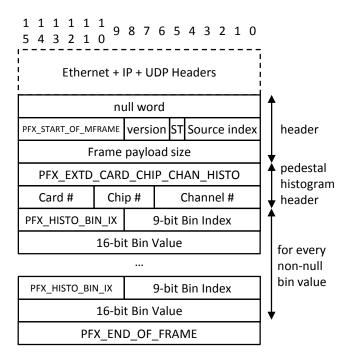

- Virtual Channel C is used for event data collection from the FEs under the control of the TDCM.