# CALICE Si ECAL

# Description du Demonstrateur Campagnes de tests et résultats/performances démontrées

Roman Pöschl

Revue IN2P3 – September 2022

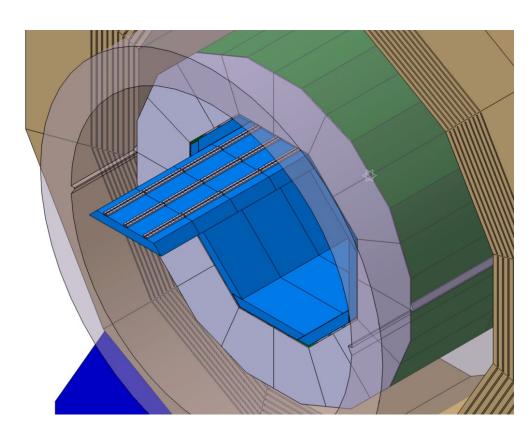

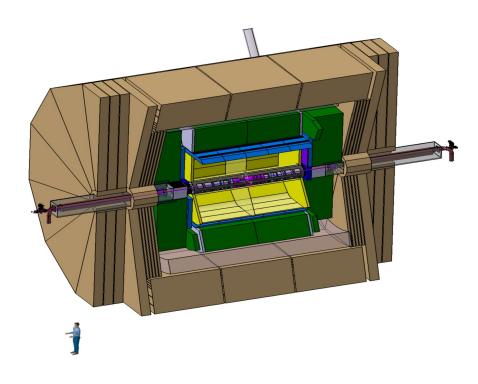

### Silicon Tungsten electromagnetic calorimeter

• Optimized for Particle Flow: Jet energy resolution 3-4%, Excellent photon-hadron separation

The SiW ECAL in the ILD Detector

- O(10<sup>8</sup>) cells

- "No space"

- => Large integration effort

#### Basic Requirements:

- Extreme high granularity

- Compact and hermetic

- (inside magnetic coil)

#### **Basic Choices:**

- Tungsten as absorber material

- $X_0=3.5$ mm,  $R_M=9$ mm,  $\Theta=96$ mm

- Narrow showers

- Assures compact design

- Silicon as active material

- Support compact design

- Allows for pixelisationRobust technology

- Excellent signal/noise ratio: 10 as design value

- All future e+e- collider projects feature at least one detector concept with this technology

- Decision for CMS HGCAL based on CALICE/ILD prototypes

### Steps of R&D

#### **Physics Prototype**

2005 - 2011

- Proof of principle of granular calorimeters

- Large scale combined beam tests

### **Technological Prototype**

2010 - ...

- Engineering challenges

- Higher granularity

- Lower noise

#### **LC** detector

- The goal

- Typically 10<sup>8</sup> calorimeter cells

- Compare:

- ATLAS LAr ~10<sup>5</sup> cells

- CMS HGCAL ~10<sup>7</sup> cells

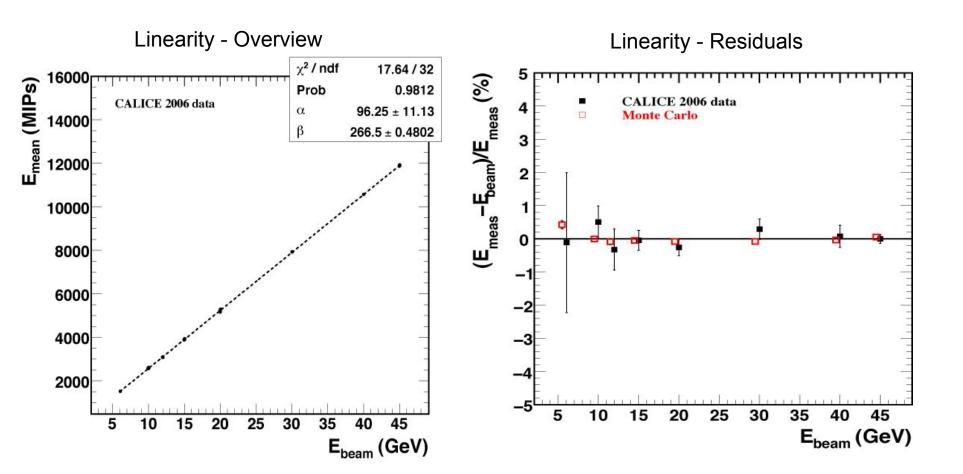

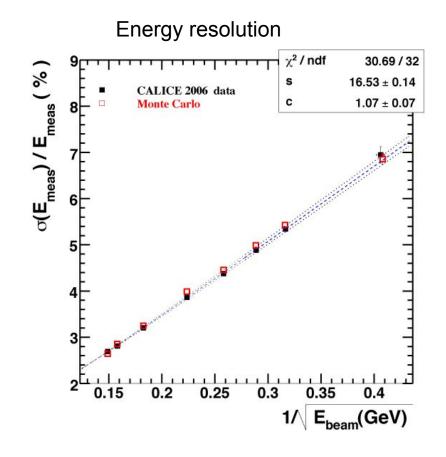

### Physics Prototype – Response to Electrons

- Highly linear response over large energy range

- Linearity well reproduced by MC MIP/GeV ~ 266.5 [1/GeV]

- Non-Linearity O(1%)

Resolution curve shows typical √E dependency

$$\frac{\Delta E_{meas.}}{E_{meas.}} = \left[ \frac{16.6 \pm 0.1 (stat.)}{\sqrt{E \text{ [GeV]}}} \oplus (1.1 \pm 0.1) \right] \%$$

C. Carloganu et al.

NIM A608 (2009) 372; e-print: arXiv:0811.2354

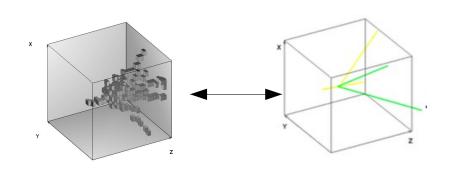

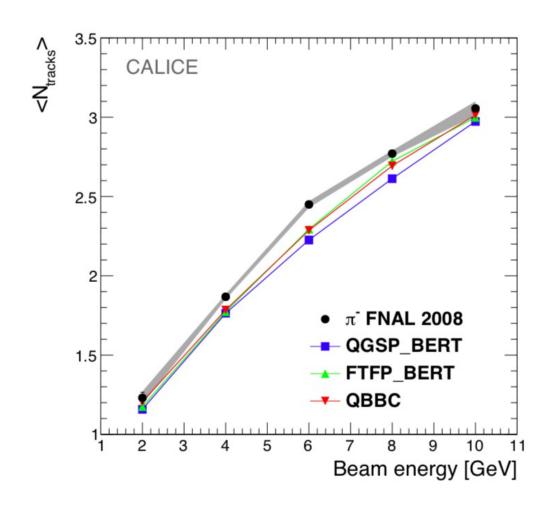

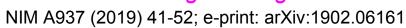

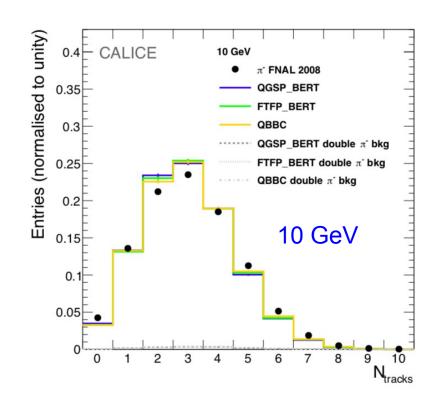

### Physics Prototype – Secondary Tracks in Si ECAL

PhD Thesis, S. Bilokin (LAL)

TYL-FJPPL Young Investigator Award

#### PhD Theses P. Doublet, (LAL, ) H. Li (LAL) P2IO PD N. v.d. Kolk (LLR/LAL)

NIM A794 (2015) 240-254; e-print: arXiv:1411.7215

- Mean number of secondary tracks increases with beam energy as expected from fixed target kinematics for π--tungsten scattering

- Good reproduction of data by simulation with GEANT4

- Study motivated inclusion of CALICE Si ECAL into G4 Validation Chain

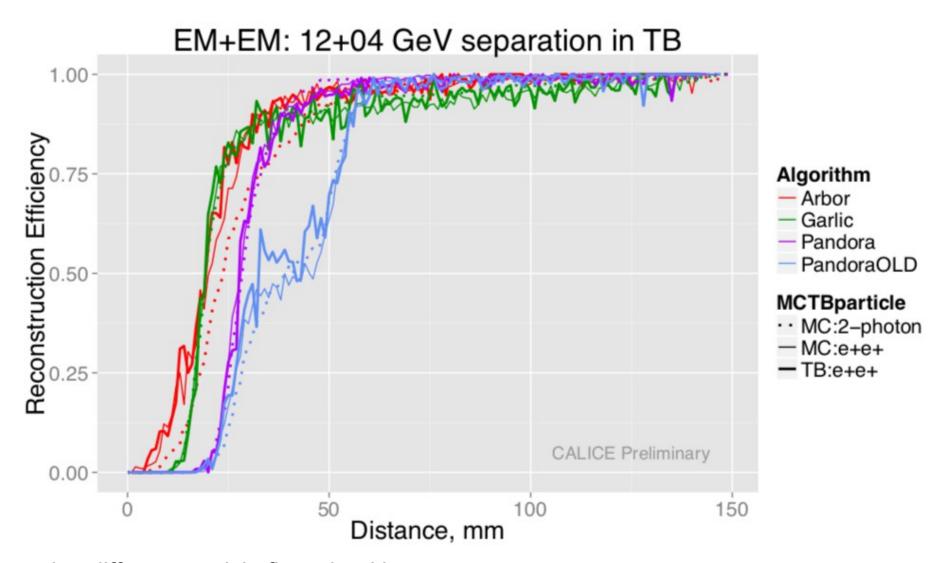

# Physics Prototype – Particle Separation

#### Photon-pion: Separation using beam test data

PhD Thesis K. Shpak (LLR) CALICE-CAN-2017-001

- Test of particle separation using different particle flow algorithms

- ARBOR, GARLIC developed by in2p3 (LLR, IPNL)

- Full separation power at around 30mm

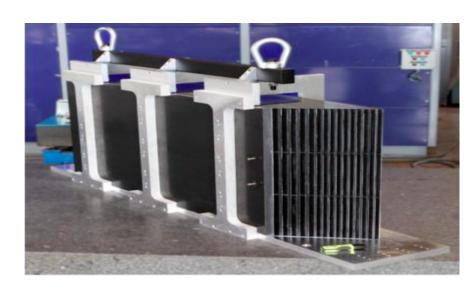

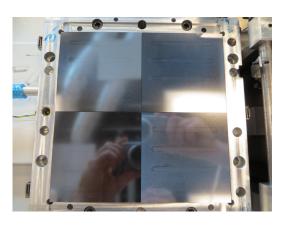

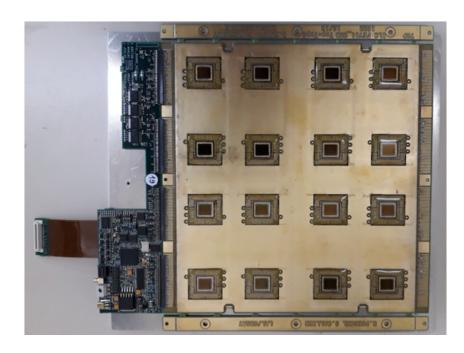

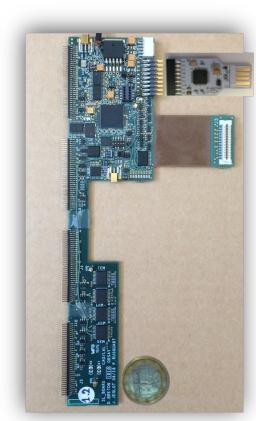

### SiW Ecal Technological prototype – Elements of (long) layer

ASIC+PCB+SiWafer

=ASU

Size 18x18 cm<sup>2</sup>

(IJCLab, Kyushu, OMEGA, LLR, SKKU)

ASIC SKIROC2(a)

(OMEGA)

Wire Bonded or

In BGA package

(IJCLab, Kyushu, LLR)

Interconnection

(IJCLab)

HV Supply

(IJCLab, LLR)

SL-Board (IJCLab)

SiWafers glued onto PCB Pixel size 5.5x5.5 mm<sup>2</sup> (LPNHE)

Note that an additional hub for hardware Development is being set up at IFIC/Valencia

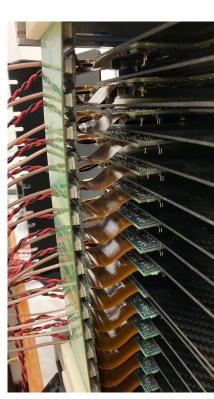

• The beam test set ups comprised mainly **short layers** consisting of one ASU and a readout card each

. 1500mm

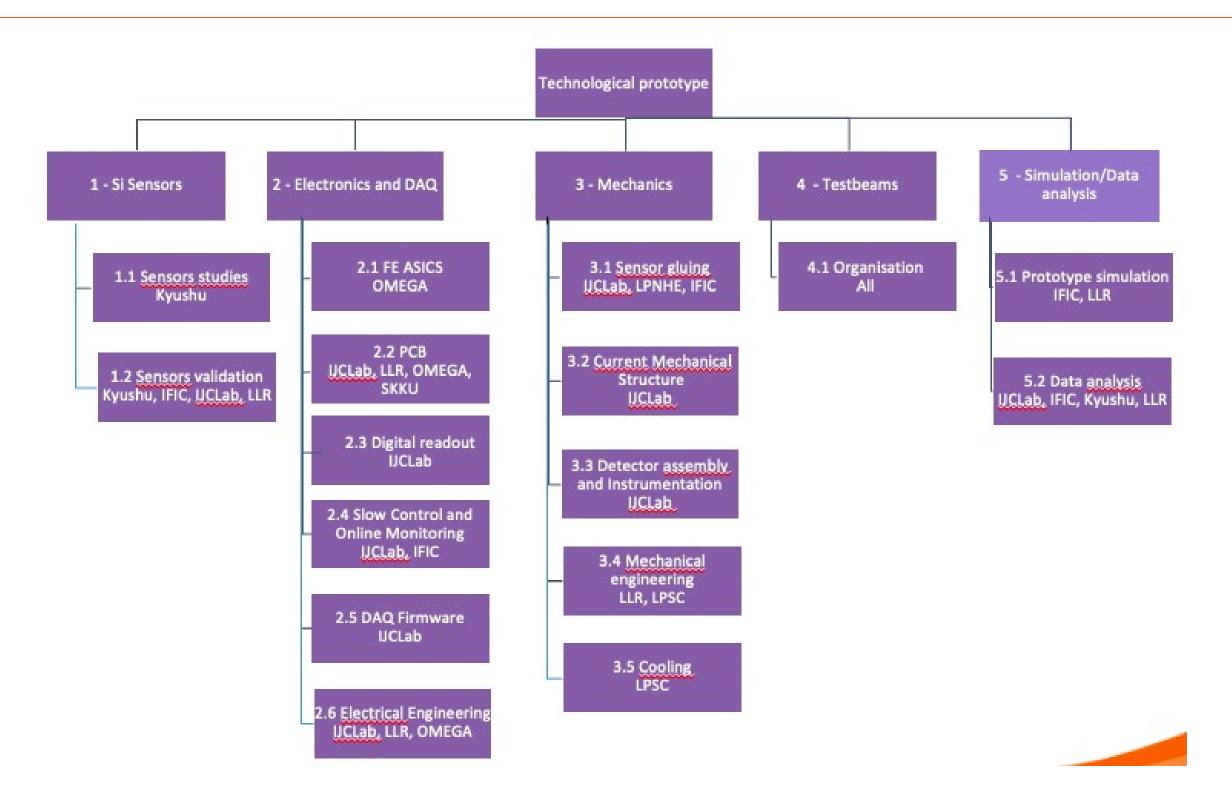

# SiW Ecal Technological Prototype – Organisation

8

### Prologue – "The FEV Zoo"

- In recent years the SiW ECAL has developed and used several PCB variants

- To make sure that you don't get lost, here comes an introduction

FEV10-12

FEV\_COB

FEV13

- ASICs in BGA Package

- Incremental modifications

From v10 -> v12

- Main "Working horses" since 2014

- ASICs wirebonded in cavities

- COB = Chip-On-Board

- Current version FEV11 COB

- Thinner than FEV with BGA

- External connectivity compatible with BGA based FEV10-12

- Also based on BGA packaging

- Different routing than FEV10-12

- Different external connectivity

Current prototype (see later) is equipped with all of these PCBs

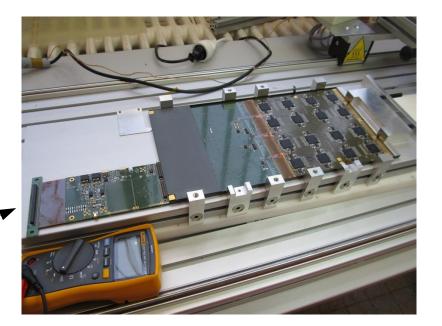

# Prototypes until ~2018

PCB FEV10-12

with long adapter card

Wafer thickness

325 µm

PCB FEV13

with small(er) adapter card

Wafer thickness

650 µm

- Total ~15 short layers constructed

- 1024 channels per layer

- Assembly chains in France and Japan

- Beam tests at DESY and CERN since 2016

- Main campaign 2017 with 7 layers

## Intermezzo – Test beam campaigns before 2017 CA

- DESY 2012 and 2013

- Simplified ASUs (four ASICS, one sensor)

- First thorough examination of SKIROC2 ASICs

IN2P3 PD T. Frisson (LAL), PhD Thesis J. Rouene (LAL), Nucl.Instrum.Meth. A778 (2015) 78-84

Event filtering 'Plane events???'

1 e- (5 GeV) 5 W plates between layers

Excellent Signal/Noise separation

- CERN 2015

- First ASUs with 1024 pads, temporary connection sensor <-> PCB

PhD Thesis K. Shpak (LLR)

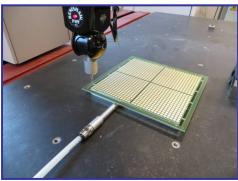

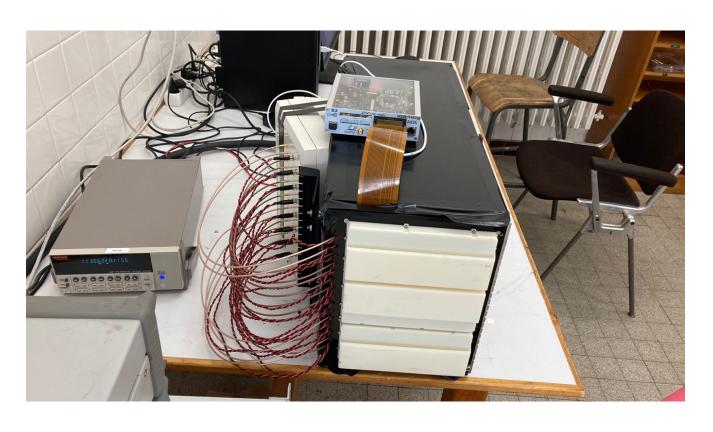

# **Assembly and QA Chain**

(In house) cabling and electronics tests with highly mobile DAQ system

Wafer Gluing with robot

Metrology of **PCBs**

Si sensor

tests

Detector assembly and commissioning

Deliverable of AIDA-2020

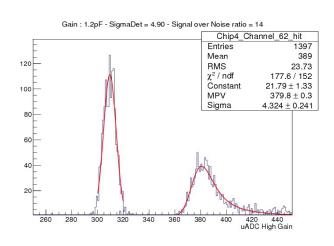

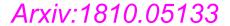

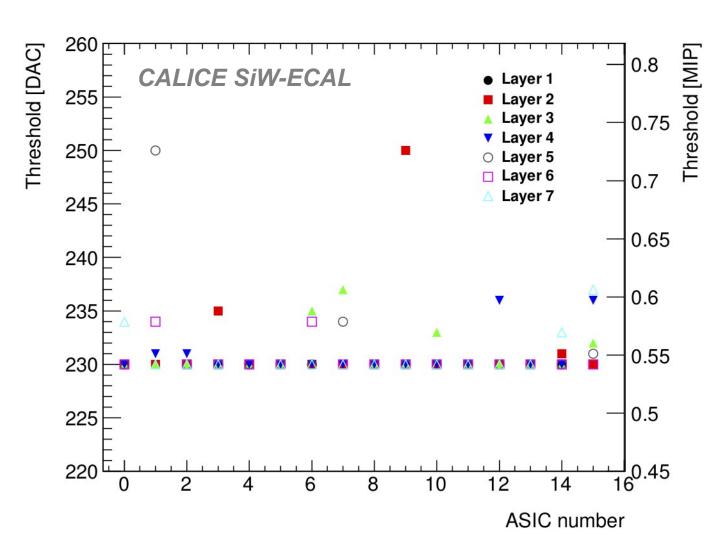

### Testbeam 2017 - Results

#### PFA requires:

- a) Access to small signals -> Low trigger thresholds 🗸

- b) Tracking in calorimeters -> High MIP detection efficiency ✓

MIP Detection efficiency ~100%

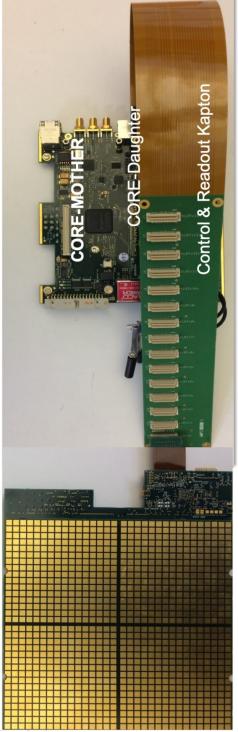

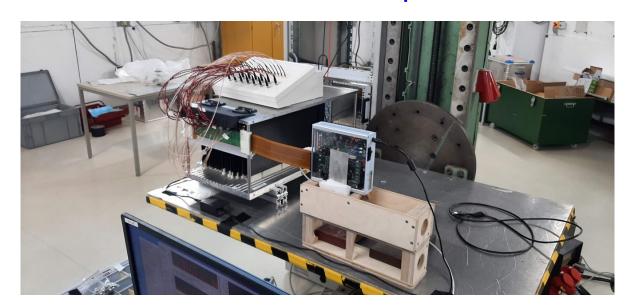

### **Compact readout**

# Current detector interface card (SL Board) and zoom into interface region

**SL Board**

- "Dead space free" granular calorimeters put tight demands on compactness

- Current developments in for SiW ECAL meet these requirements

- System allows to read column of 15 layers <-> to be expected in ILD

- Important that full readout system goes through scrutiny in beam tests

#### Complete readout system

For reference Comparison old/new r/o system

Deliverable of AIDA-2020 and HIGHTEC

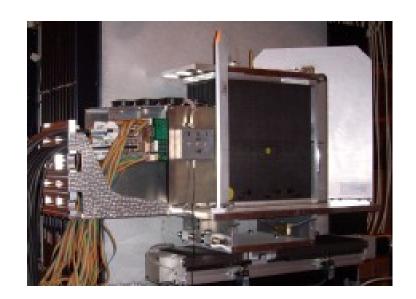

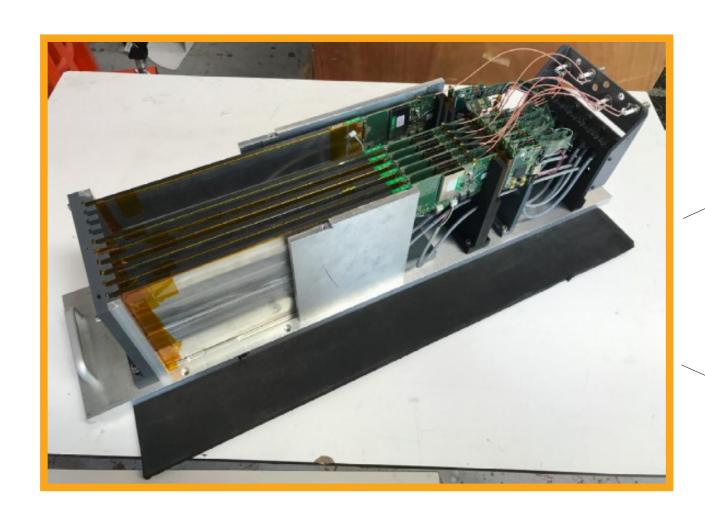

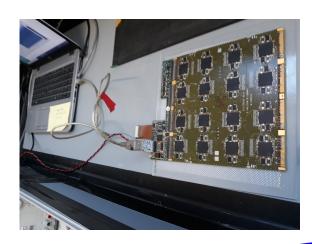

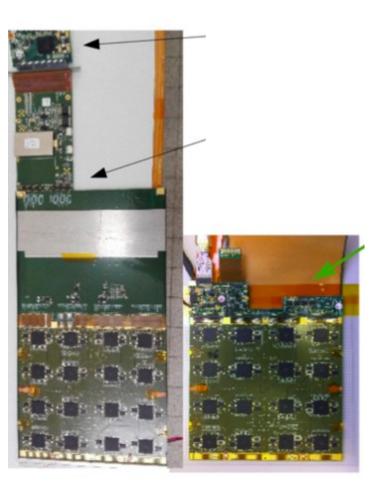

### SiW ECAL 2018 -> 2022

- 7 short layers (18x18x0.5cm<sup>3</sup>)

- 1024 channels per layer => 7186 cells

- Assembly chains in France and Japan

- Beam tests at DESY and CERN since 2016

- 15 short layers equivalent to 15360 readout cells

- Overall size 640x304x246mm³

- Commissioned in 2020 and 2021

- Partially by *recycling* of ASUs from 2016 stack

- Testbeams (finally) in November 2021 and during 2022

- 1.5 years in waiting loop due to pandemic

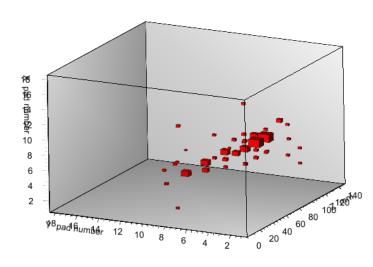

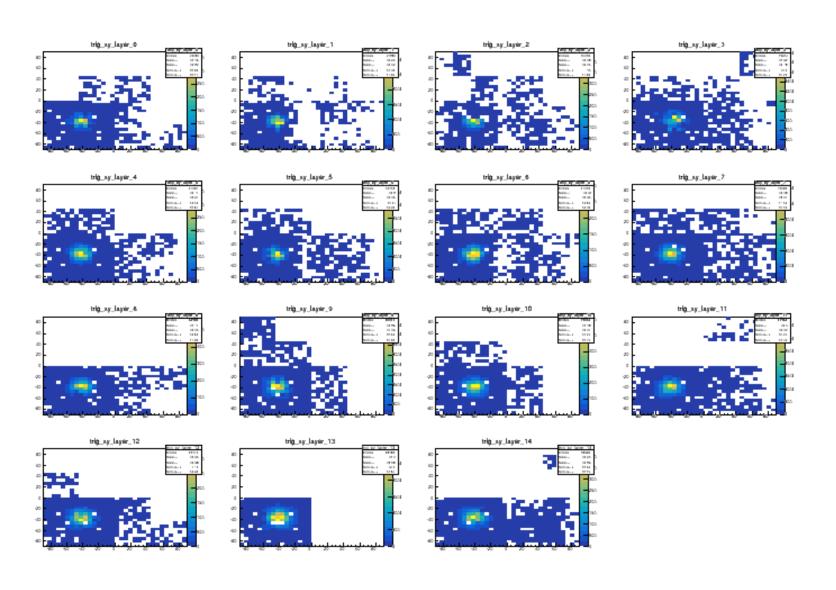

### SiW-ECAL in beam test @ DESY

### **Detector Setup**

Detector in beam position

• Beam spot in 15 layers

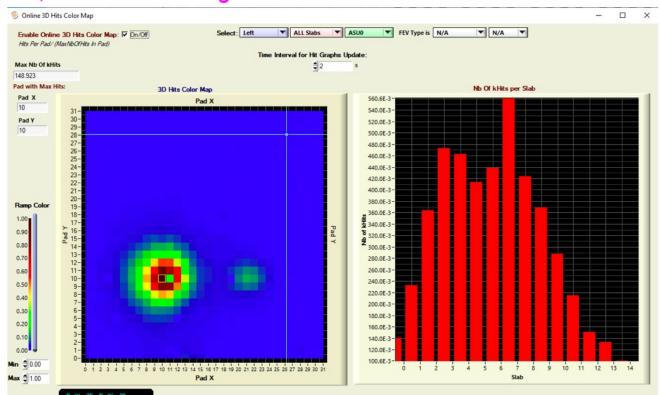

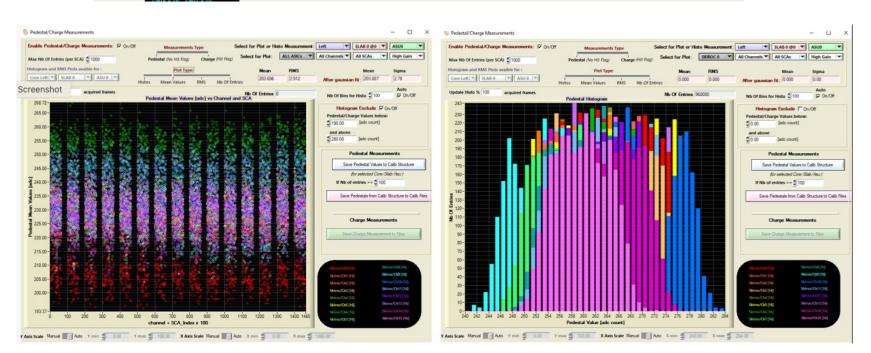

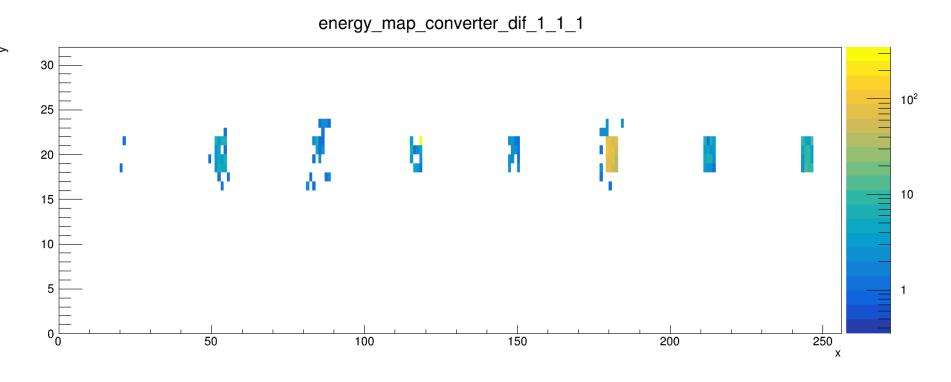

### SiW-ECAL Beam test – Online Monitoring

#### Jihane Maalmi, CALICE Meeting Valencia

- Online Hit Maps and shower profiles

- Allow for real time beam and detector tuning e.g. Adaptation of beam rates or thresholds

- Further online tools

- Pedestal measurement and subtraction

- Charge measurement and histogramming

- MIP gain correction

These are just a few examples from the powerful online suite

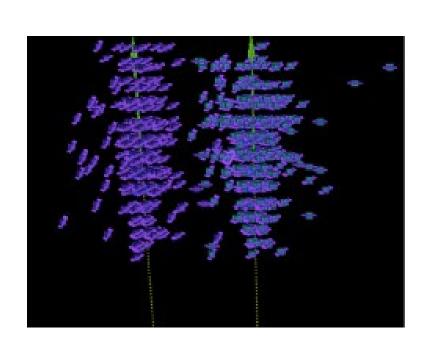

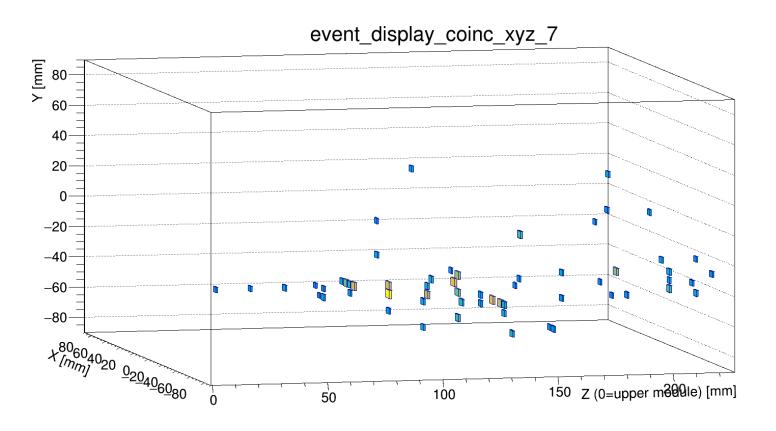

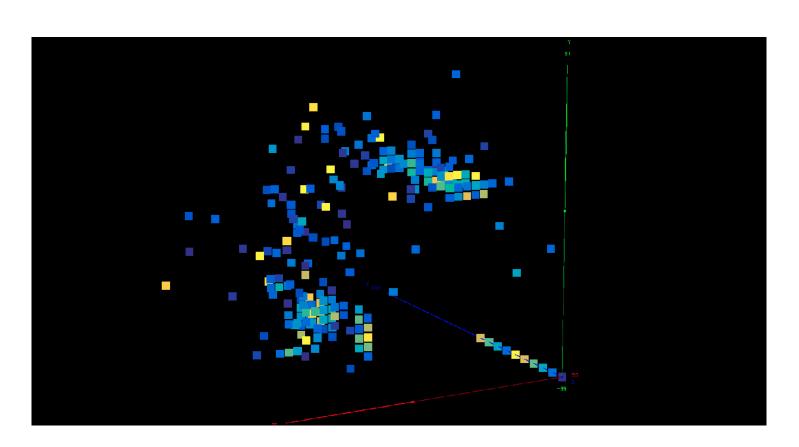

# SiW-ECAL Beam test – Onlline/Offline Event Displays

J. Kunath (LLR)

- Clear showers measured during beam test campaigns

- Require full event reconstruction

- These (and more) "high level" views are available already while a run is going on

Y. Okugawa (IJCLab)

- "Particle separation continued"

- Two electrons "seen" in 20 GeV e- run at CERN

### **SiW-ECAL** Beam test – Detector Simulation

One or two slides on simulation (Vincent, Fabricio

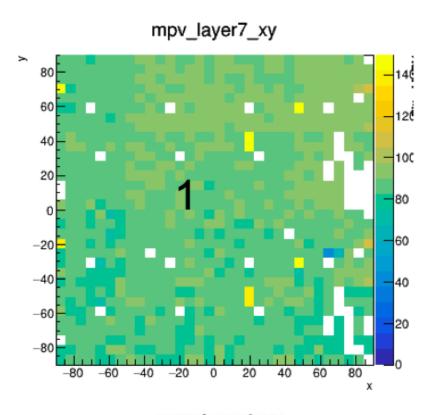

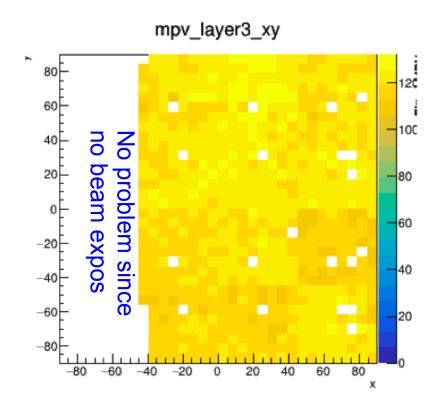

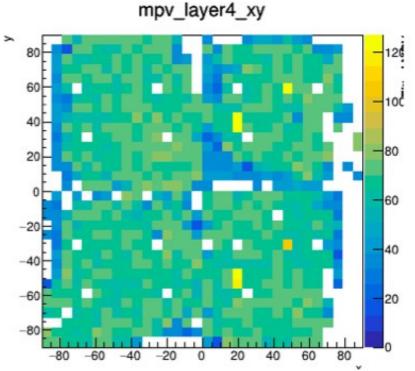

### SiW-ECAL Beam test 2022 – First feedback

- We have good layers ...

- Homogeneous response to MIPs over layer surface

- Here white cells are masked cells due to PCB routing

- Understood and will be corrected

#### ... and not so good layers

- Partially even no response at all, in particular at the wafer boundaries

- To be understood, will require dedicated aging studies

- Not seen in 2017, degradation observed during 2018/19

- Since Summer 2022 access to the different stages of the ASICs

- => analogue probes, <u>major</u> debugging tool

### **Common testbeams**

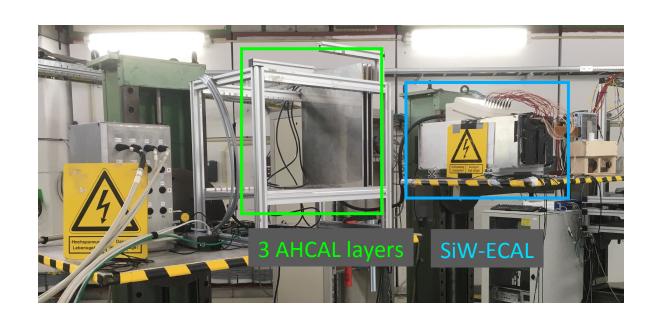

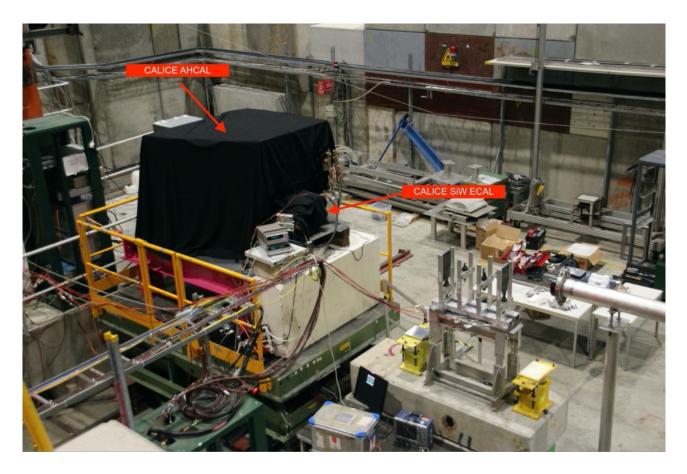

#### SiW-ECAL + AHCAL DAQ test @ DESY in March 2022

#### Common setup at CERN June 2022

- Successful synchronisation of data recorded with SIW-ECAL and AHCAL

- Common running makes full use of EUDAQ tools (developed within European projects)

### **Electrical long slab**

Chain of 8 detection elements ~3m

- Very encouraging results in first beam test in 2018

- Credibility for concept as foreseen for e.g. ILD

- Issues with signal drop towards extremities

- Long slab studies will be resumed with new FEV

- Adapted for power pulsing, will avoid voltage drop, etc ...

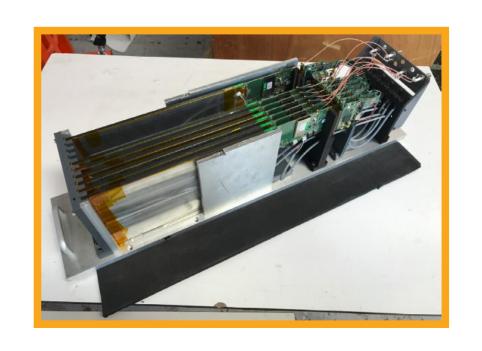

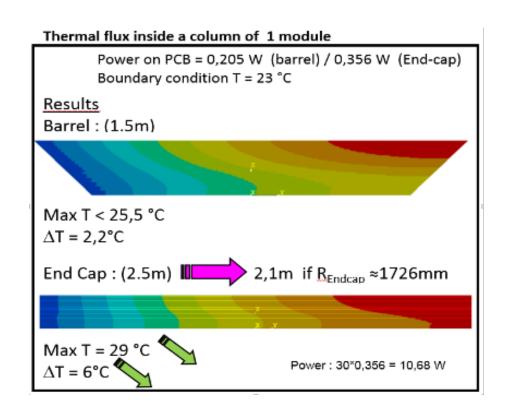

# **Cooling System**

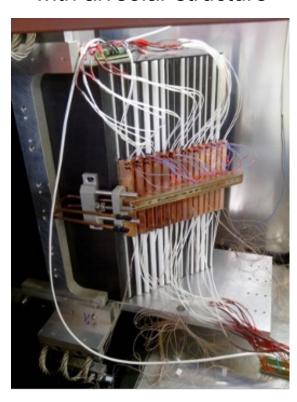

#### Thermal simulation within barrel module

Thermal tests with alveolar structure

Heat exchanger

SL Board design is adapted to Hea exchanger geometry

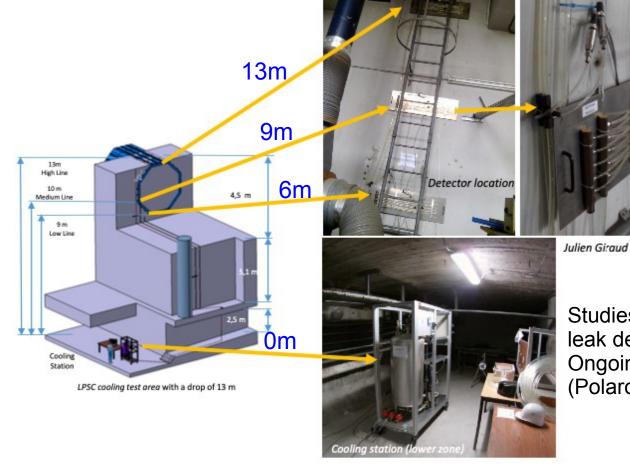

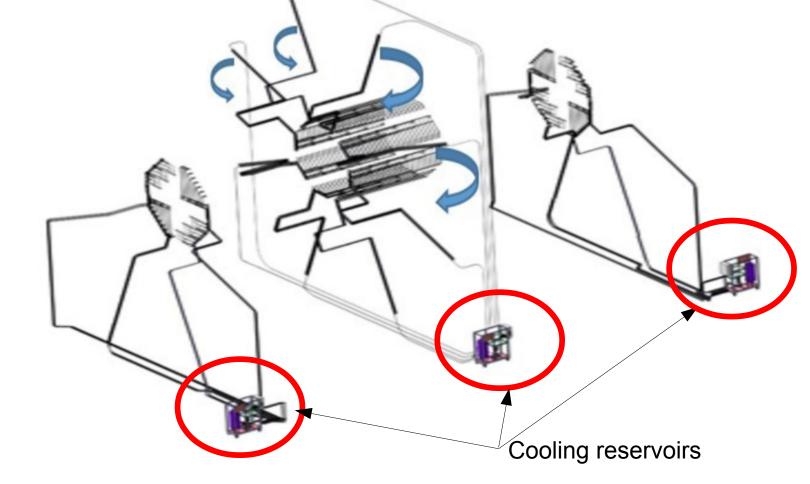

# Full Cooling System – ILD SiECAL

#### Demonstrator of large leakless loop for CALICE/ILD ECAL

Upper part of the experiment

- Thermal model as milestone

- Probes at different heights to establish full model of Cooling system for large detectors

a large leak-less cooling-loop

Studies for efficient leak detection Ongoing (Polarographic probe)

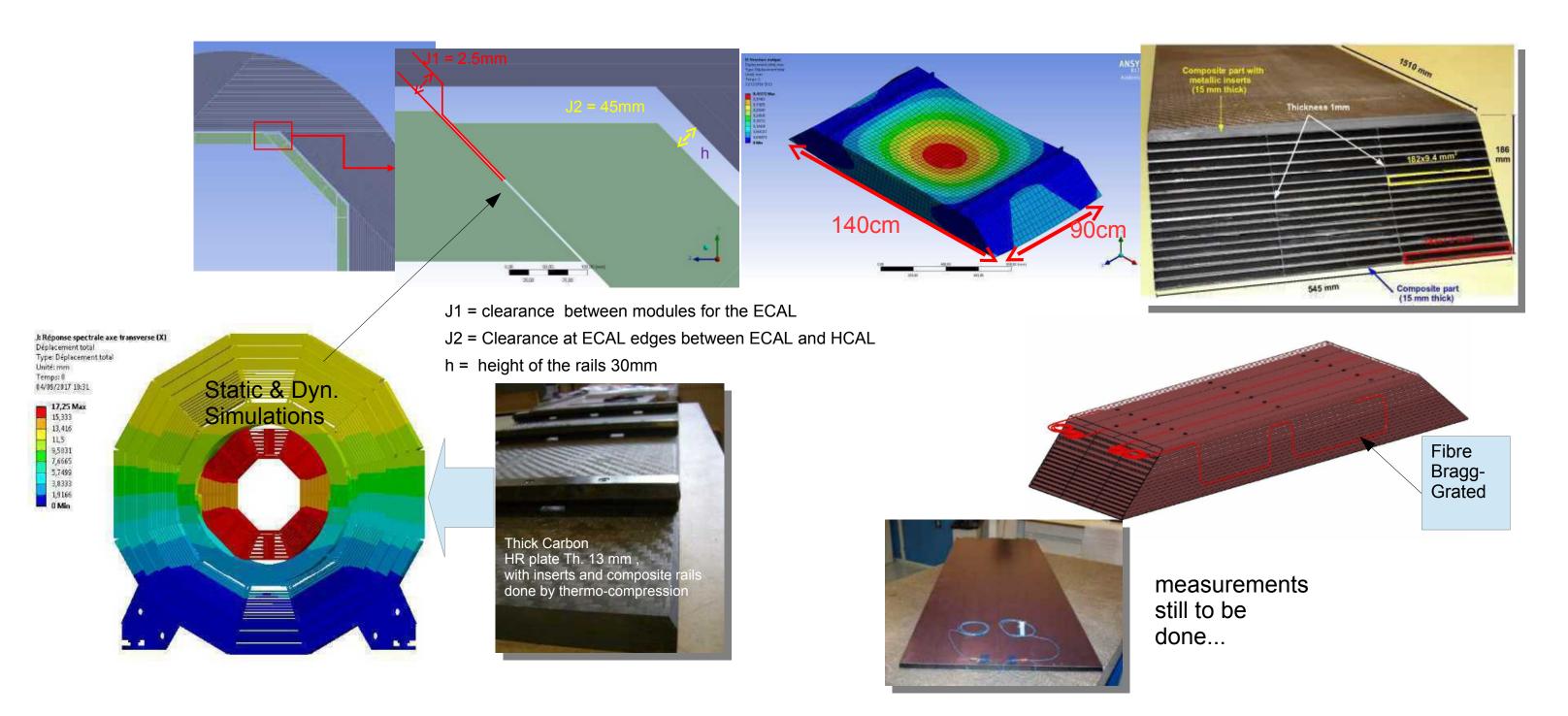

# ILD SiECAL – Mechanical structures and studies CALICO

# **ILD SiECAL – Endcaps**

# One slide on Endcaps!?

### **Summary**

- R&D and testbeam campaigns 2012 2018 allowed for studying individual aspects of technological prototype

- SKIROC ASIC

- ASUs with 1024 layers

- Different types of PCB

- Maximum of seven layers in stack

- Detector response at MIP Level

- · Elements of assembly chain

- Successful operation of a fifteen layer stack in beam tests at DESY and CERN in 2021 and 2022

- Major milestone for technological prototype

- Demonstration of performance of compact DAQ

- Rich set of data to study detector performance

- First "calorimeter" since physics prototype

- However, physics prototype had 30 layers

- 15 layers by partially recycling older ASUs

- Have already precious feedback on further work needed

- Powerful infrastructure to conduct conclusive system tests in coming years

- Advanced engineering studies accompany ongoing R&D activities

# **Backup**

### SiW Ecal – Wafer R&D I

#### Si Sensor (9x9cm² from 6" wafer)

N-type silicon Crystal Orientation: <100> or <111>

#### Wafer specs

| Tab 1 : Summary of the substrate characteristics |      |      |      |

|--------------------------------------------------|------|------|------|

|                                                  | Min. | Тур. | Max. |

| N type silicon                                   | -    | -    | -    |

| Resistivity (kOhms.cm)                           | 4    | 5    | -    |

| Thickness (μm), option T1                        | 310  | 320  | 330  |

| Thickness (µm), option T2                        | 490  | 500  | 510  |

| Width (mm), option S1                            | 89.7 | 89.8 | 89.9 |

| Width (mm), option S2                            | 44.7 | 44.8 | 44.9 |

Definition of specifications for different wafer types:

Resisitvity:  $> 5 \text{ k}\Omega\text{xcm}$

Price: Typically 1000-1500 EUR/wafer (when ordering small quantities)

- In addition we require small leakage current:s under full depletion a few nA/pixel but for cost reasons we tolerate a certain fraction of pixels with higher leakage currents

- Vendors: OnSemi (CZ) and Russian company for physics prototype (~2003)

Hamamatsu for technological prototype (since ~2010)

Contacts with other vendors (e.g. LFoundry) hibernating mainly for funding reasons

The drop-out of Infineon for the CMS HGCAL was/is bad news

### SiW Ecal – Wafer R&D II

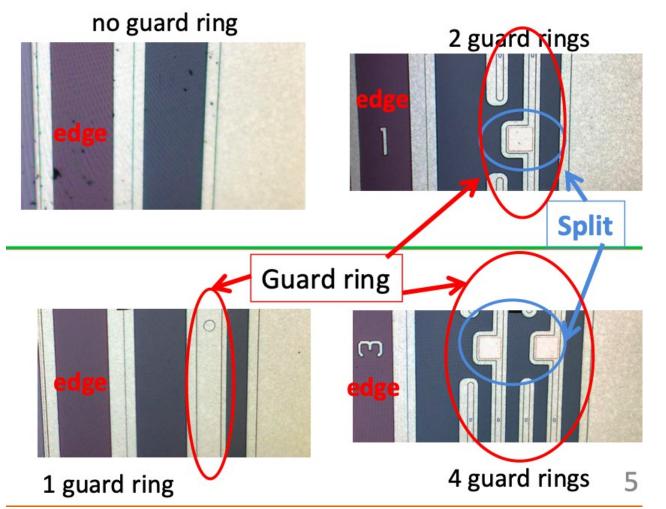

### We (i.e. Mainly Kyushu) have tested several wafer types in previous years

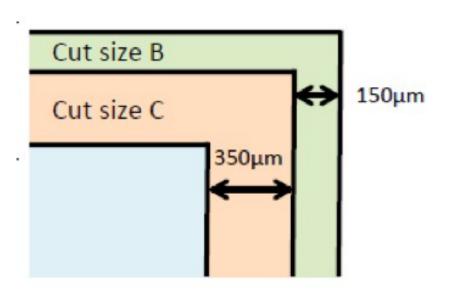

- Cut size determine the actual sensitive area of a wafer

- Different designs mainly on test samples of "baby wafers"

- The "Hamamatsu" standard is still 0 or 1 full guard ring

- 0 is "fake 0" guard ring, in fact there is still a small guard ring

#### Observations in recent years (see also backup for more details)

- Split or no guard ring lead to suppression of square events

- In prototype we still use full wafers with 0 or 1 guard ring

- General trend of reduction of bias voltage

- Can operate 500mum wafers at 60-80 V in full depletion

#### Towards 8" wafers?

- General trend (e.g. CMS) is to use 8" wafers

- Larger surface/wafer =>smaller cost

- Standard thickness 725mum

- Impossible to get access to HPK production

- Lines (CMS HGCAL Production)

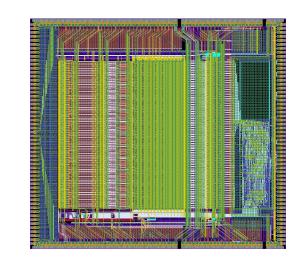

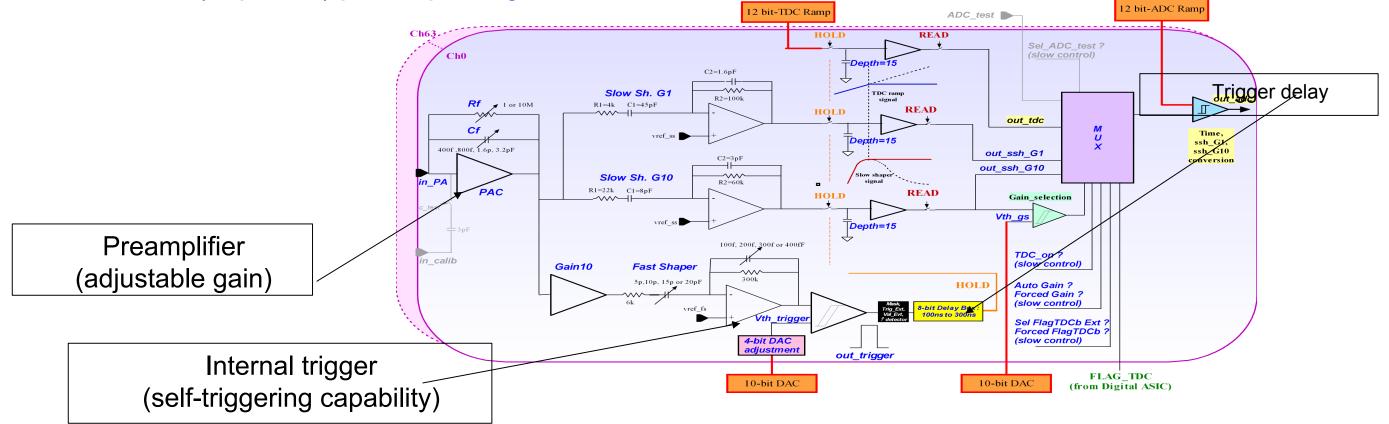

### SiW Ecal – Front end electronics

#### SKIROC (Silicon Kalorimeter Integrated Read Out Chip)

SiGe 0.35µm AMS, Size 7.5 mm x 8.7 mm, 64 channels

High integration level (variable gain charge amp, 12-bit Wilkinson ADC, digital logic)

Large dynamic range (~2500 MIPS), low noise (~1/10 of a MIP)

Auto-trigger at ½ MIP, on chip zero suppression

Low Power: (25µW/ch) power pulsing