Xiaochao Fang

- Introduction

- Wafer scale stitched sensors

- MOSS (MOnolithic Stitched Sensor) Prototype

- Contributions of IPHC

- MOSS2

- Conclusion

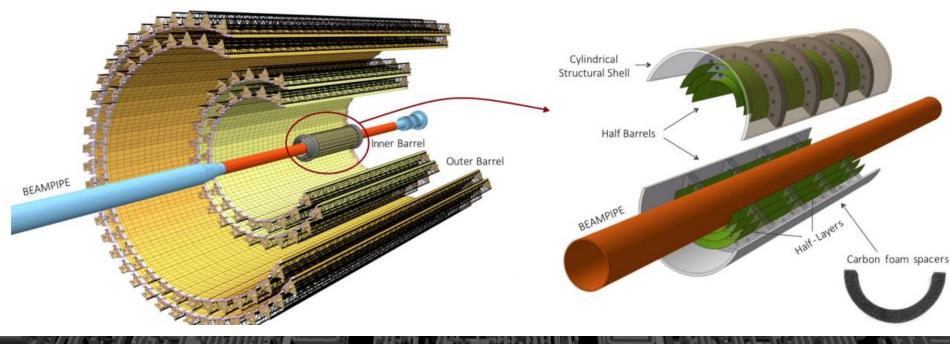

# ALICE ITS3 upgrade

#### ALICE ITS2 to ITS3 upgrade

- ↔ Replacing the barrels by real half-cylinders of bent, thin silicon

- ✤ Minimized material budget

- Only 1/7<sup>th</sup> of the material budget

- ✤ Minimized distance to interaction point

- Large improvement of vertexing precision and physics yield

- Less power consumption allows for air cooling

- b Onchip data transmission allows for no flex in the active area

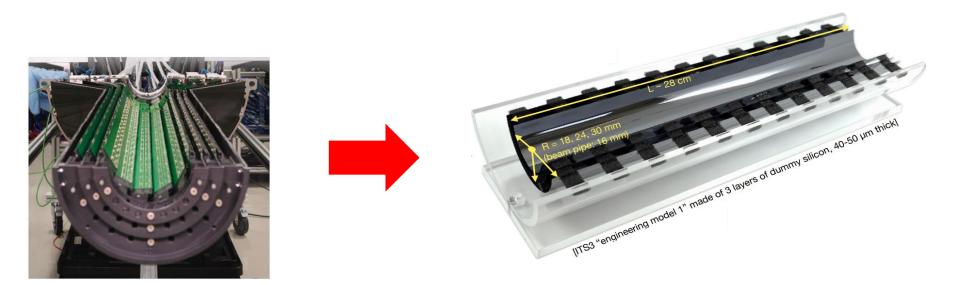

#### 3 Cylindrical layers

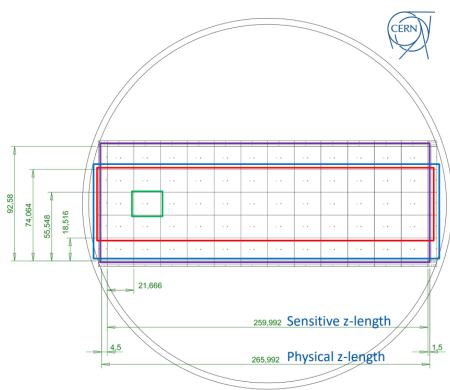

- ⇔ Rely on wafer-scale sensors (1 sensor per half-layer) in 65 nm technology

- Solution Made with 6 curved wafer-scale single-die Monolithic Active Pixel Sensors

- 🗞 Radii 18/24/30 mm, length 27 cm

- $\backsim$  Thinned down to <50  $\mu$ m

- $\clubsuit$  Position resolution ~5  $\mu$ m

- Pixels pitch 20 μm

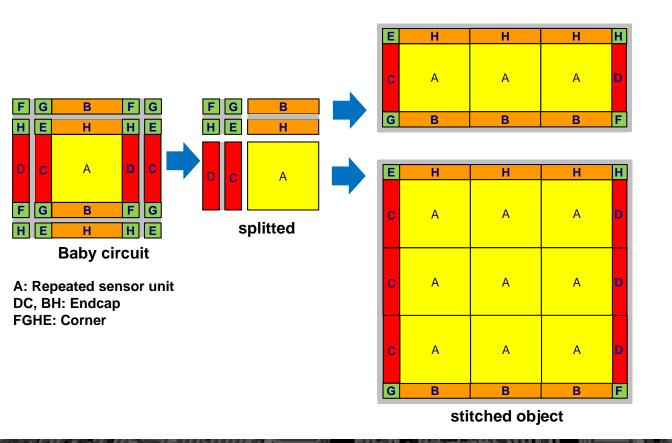

#### Wafer scale stitched sensors

- 3 design steps

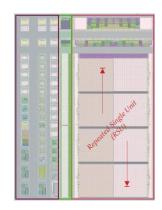

- ↔ Design a baby circuit composed by Endcap, Corner and Repeated sensor unit (RSU)

- ⇔ Split the endcap , the Corner and the repeated unit (send to foundry)

- ↔ By repeating the repeated units (and the endcaps), the foundry constructs the stitched objects

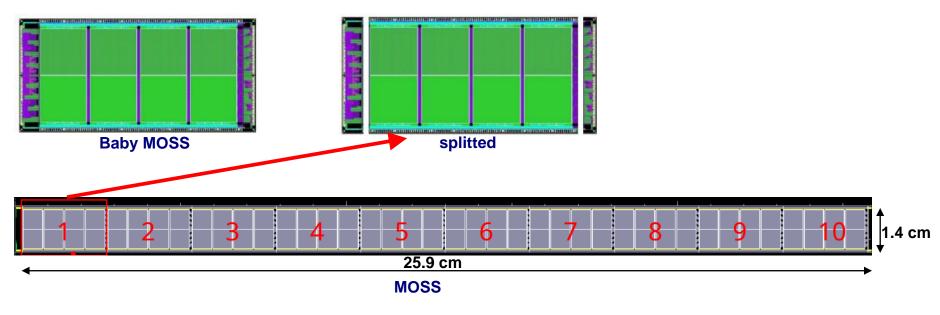

### **MOnolithic Stitched Sensor (MOSS)**

#### MOSS prototype is a proof-of-concept

- Solution To understand if we can design a stitched monolithic particle detector with satisfactory yield

- Primary goals:

- ✤ Learn stitching techniques

- ♥ Interconnects

- ✤ Learn about yield and design-for-manufacturing (DFM)

- ✤ Study power schemes, leakage, spread, noise and speed

- ✤ Develop inhouse stitching methodology

### **Contribution of IPHC in MOSS**

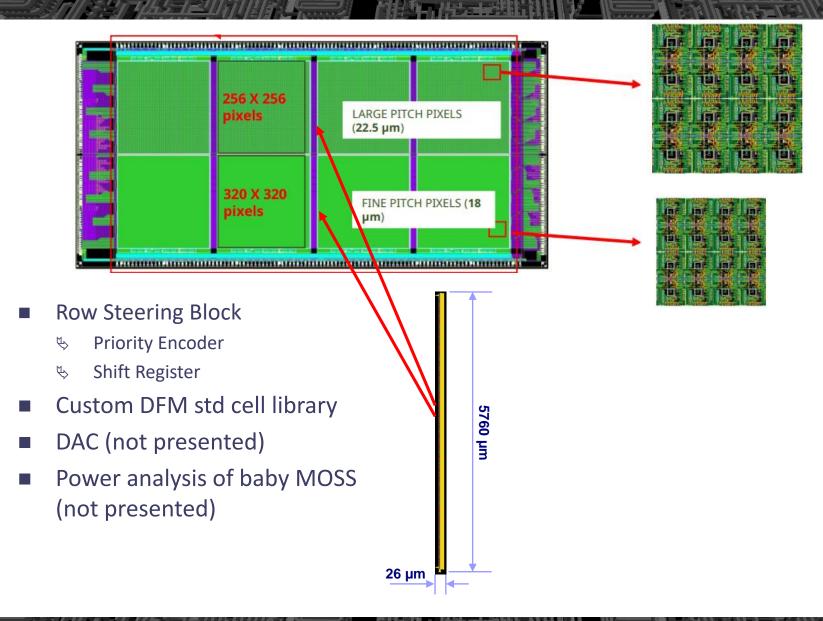

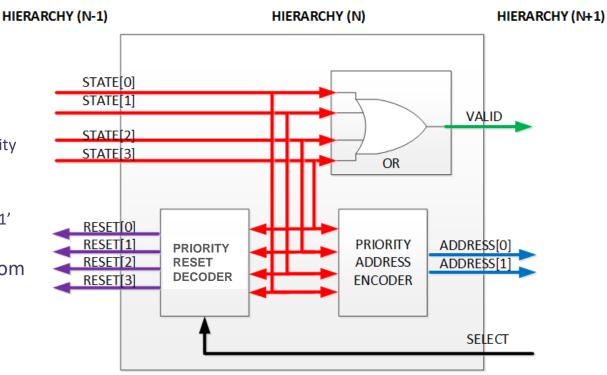

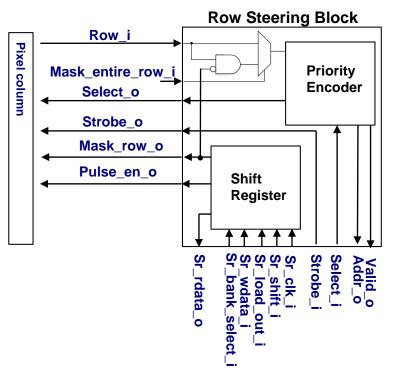

### **Row Steering Block**

#### Priority Encoder

- Solution Matrix readout

- ✤ Based on a 4 input sub-block

- ✤ Combination circuit

- 🗞 Priority Address Encoder

- Encode the address of a priority input

- 😔 🛛 Priority Reset Decoder

- Set only the priority reset to '1' after the address readout

- Configurable RTL (support from 65 rows to 2048 rows)

- Design with Flowkit environment

at discourse inter-

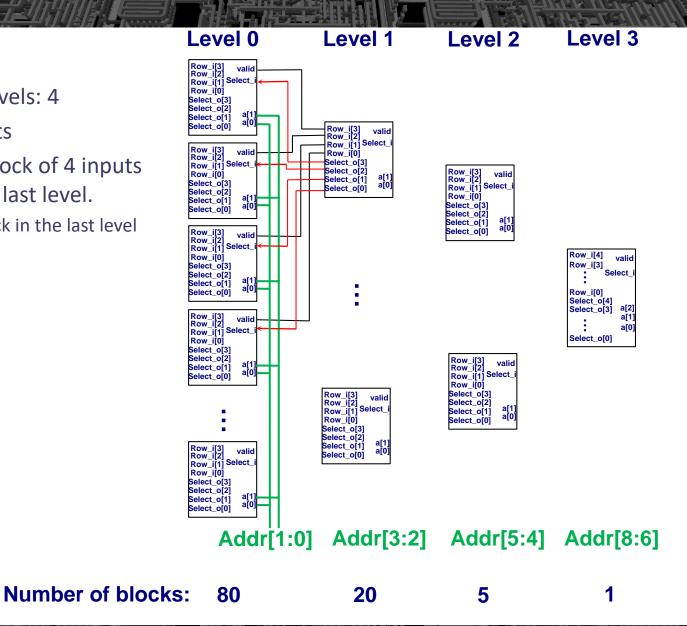

### PE for Bottom Row Steering

- Rows: 320

- Number of levels: 4

- Address: 9 bits

- Based on a block of 4 inputs except of the last level.

- 5 inputs block in the last level P

The second second second

STR. MA

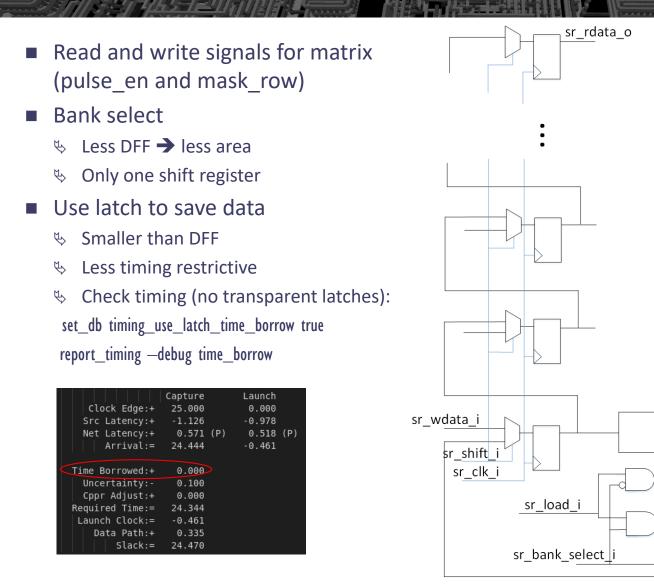

### **Shift-register control**

and have a lot of the

10

pulse\_en\_o[0]

mask\_row\_o[0]

latch

### Simulation results

#### Static timing analysis

#### 🗞 Post layout, MAX library, CWORST Corner

| Arc Source | Arc Destination | Delay[ns] |

|------------|-----------------|-----------|

| Strobe_i   | Strobe_o        | 1.791     |

| Select_i   | Select_o        | 2.946     |

| Row_i      | Select_o        | 5.055     |

| Row_i      | Valid_o         | 3.129     |

| Row_i      | Addr_o          | 6.221     |

#### Static power analysis

- ✤ Row\_i is controlled by a clock of 40 MHz

- ♥ With VCD file, TYPICAL Corner

- ♦ 1 hit/2 clocks

| Total | Power            |            |          |

|-------|------------------|------------|----------|

|       |                  |            |          |

| Total | Internal Power:  | 0.04975138 | 41.3350% |

| Total | Switching Power: | 0.05609608 | 46.6064% |

| Total | Leakage Power:   | 0.01451380 | 12.0585% |

| Total | Power:           | 0.12036127 |          |

|       |                  |            |          |

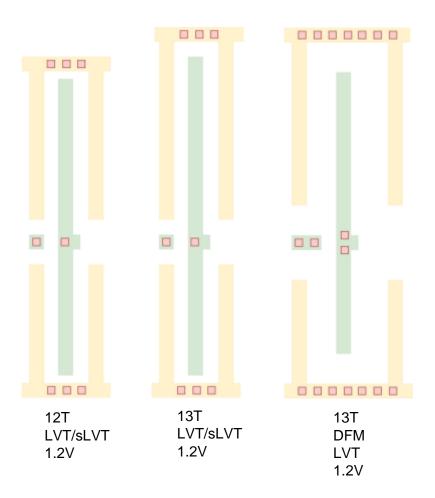

### DFM standard cells

- Customized DFM standard cells → to improve yield

- Add redundancy to single-cut contacts and vias → reduce probability of opens and bad contact

- $\checkmark$  Maximize spacing  $\rightarrow$  reduce shorts

- Solution Solution → Maximize width → reduce opens

- Based on the 12 Track standard cells

- ✤ Size of transistors remain unchanged

- Increase the height of the cells from 12T to 13T

### MOSS2 (ER2 Stitched Sensor)

- Layer 0: 12 x 3 repeated units+endcaps

- Layer 1: 12 x 4 repeated units+endcaps

- Layer 2: 12 x 5 repeated units+endcaps

- Repeated (Stitched) Sensing Unit

- ER2 Stitched Sensor is not a direct evolution of MOSS

- ER2 Sensor aims to satisfy ITS3 requirements

- ✤ Existing circuits need substantial redesign

- New features to be added

# Conclusion

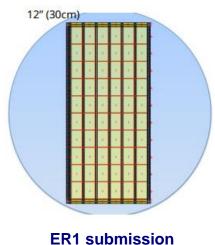

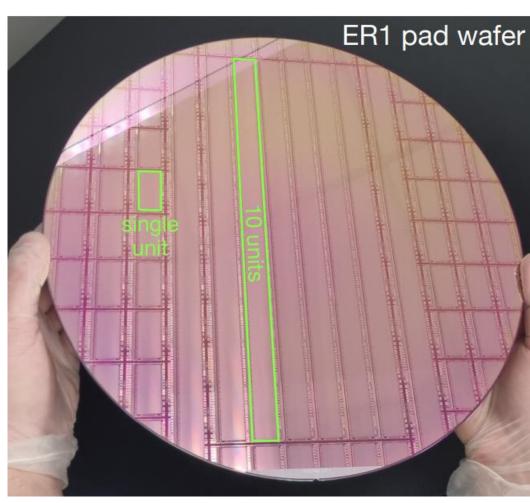

- The MOSS prototype tries to answer if a stitched monolithic particle detector is possible

- Yield improvements

- ✤ Power and data inter stitching connections

- Stitching methodology

- The MOSS Prototype has been submitted in Q4 2022 with ER1 in the WP1.2 framework

- The test of MOSS has started

We can read and write the baby MOSS

- The design of MOSS2 is on going

- Pre-studies are done

- ✤ Design will start soon

## Merci de votre attention