### **ABOUT US**

### Company

- Founded in 2015

- Headquarter in Paris, France

- 67 headcount (80 by end of 2023)

- Company backed by VC funds

- ISO 9001:2015 certified

### Team

- World class, trusted engineering team

- Highly-skilled team of application engineers

- Proven industrial track record in highspeed data conversion IC design & supply

## **Technology**

- Patented architecture & circuit

- Performance & power efficiency improvement enabled by proprietary calibration techniques

- Company holds several innovation awards

# **MARKET PERSPECTIVES** €2.3bn/y €2.9bn/y AUTOMOTIVE €200m/y Optical communications 5G/6G Wireless RAN 2028 Aerospace & Defense 5G/6G BACKHAUL **Test & Measurement** 2026 2025 2022 2018 **Current focus**

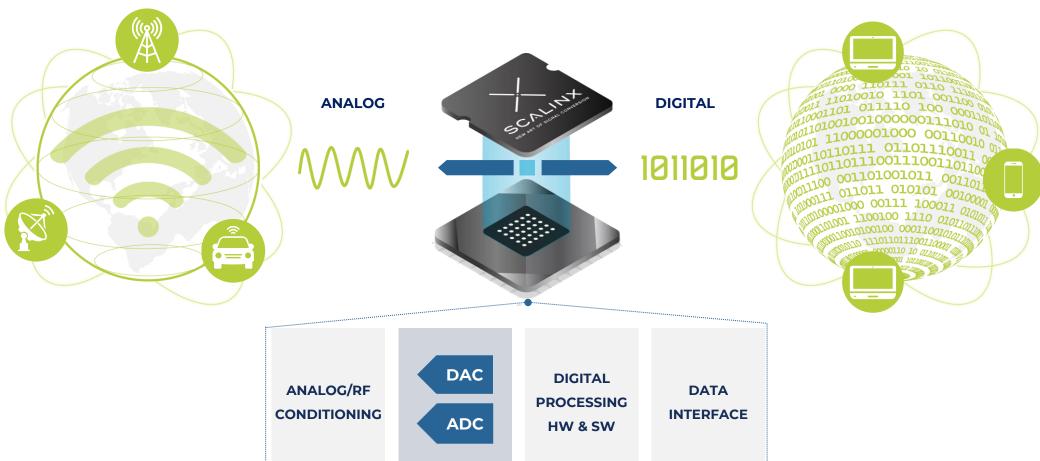

NEW ART OF SIGNAL CONVERSION

### **ABOUT US**

SCALINX is a fabless semiconductor company specializing in design and marketing of highly-integrated mixed-signal products,

connecting physical and digital worlds.

## **End-to-end offer**

### ASIC / ASSP Packaged or die

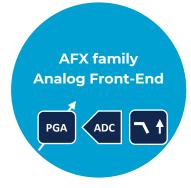

- Analog Front-End

- Mixed-Signal Front-End

- RF Receiver

- SoC Transceiver

#### **EVALUATION KIT**

- FMC evaluation board compatible with EK-V7-VC707-G FPGA mother board

- Software with user-friendly GUI

### **SUPPORT**

- Application team

- Customized web access to online documentation: data-sheet, application note, etc.

### PRODUCT PORTFOLIO TIMELINE: supported by our ADC & DAC IP cores roadmap

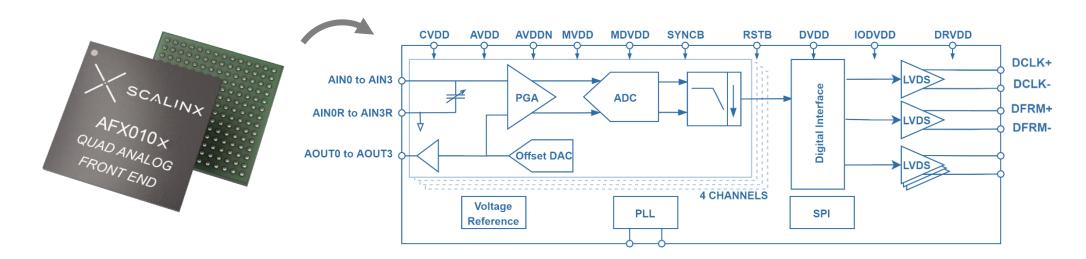

- Functions: PGA, ADC, offset-DAC, PLL, Digital FIR filters, Digital gain

- Up to 4 channels

- Resolution up to 16-bit

- Data-Rate up to 5 GS/s

- Bandwidth up to 300 MHz

- LVDS interface

- BGA package

- IPs: ΔΣ offset DAC Low-Pass  $\Delta\Sigma$  ADC

2023

- Functions: ADC, DAC, Quadrature NCO, DDC, **DUC, Digital FIR filters**

- Up to 4 channels

- Resolution up to 16-bit

- Data-Rate up to 208 MS/s

- Bandwidth up to 50 MHz

- JESD204B & LVDS interface

- BGA package

- IPs: Current-steering DAC + Band - Pass  $\Delta\Sigma$  ADC

2024

- Functions: RF Attenuator. RF ADC, PLL, Quadrature NCO, DDC, Digital FIR filters

- Up to 2 channels

- Resolution up to 16-bit

- Data-Rate up to 8 GS/s

- Bandwidth up to 400 MHz

- JESD204B/C interface

- BGA package

- IPs: Band Pass ΔΣ ADC

2025

ADPD MODEM µW/mmW **CPU SUBSYSTEM**

- Functions: ADC, DAC, NCO, DDC, DUC, MODEM, CPU sub-system, Data-Path

- Up to 4 μW channels and 2 mmW channels

- Resolution up to 14-bit

- Data-Rate up to 8 GS/s

- Bandwidth > 2 GHz

- ETHERNET interface

- BGA package

- IPs: Pipeline ADC current-steering DAC

2026

### AFX010x ANALOG FRONT-END FEATURES & KEY SPECIFICATION •

- Four channels of full PGA, Offset DAC, ADC and digital processor

- Sampling-rate up to 5 GS/s per channel

- ENOB up to 11-bit @f<sub>in</sub>=10 MHz

- THD as low as 78dBc@f<sub>in</sub>=10 MHz

- On-chip clock synthesizer and voltage reference

- Digitally-selectable bandwidth from 20 MHz up to 300 MHz

- Flexible power modes

- PGA with bipolar input voltage range from ±20 mV up to ±200 mV

- Programmable analog gain range: 5x, 10x, 20x

- 16-bit Offset-DAC with output range from -300mV to +300mV

- Programmable digital gain range: 1x, 2.5x, 5x, 10x, 25x, 50x

- Overshoot less than 0.5% for 300 MHz bandwidth

- Fast overload-recovery

- 425 mW/channel at 5 GS/s sampling-rate

# **KEY INDICATORS**

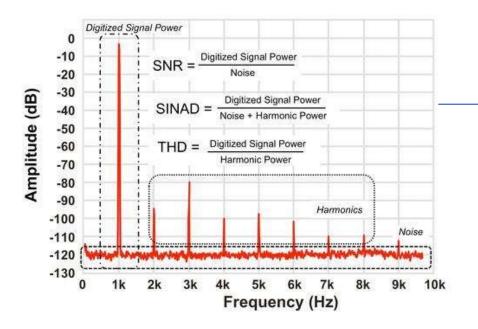

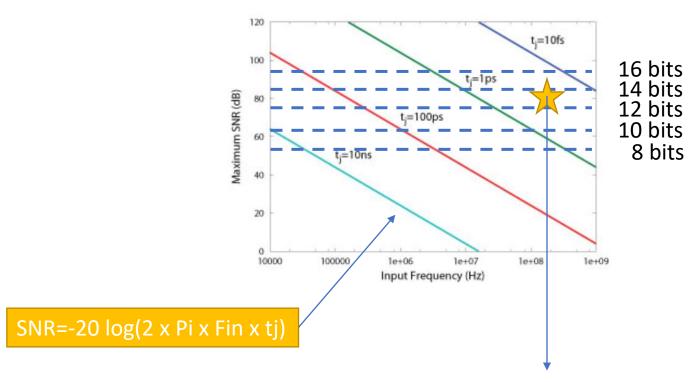

| Resolution | SNR max (dB) |

|------------|--------------|

| 8          | 50           |

| 10         | 62           |

| 12         | 74           |

| 14         | 86           |

| 16         | 98           |

$$SNR = 6.02 \times Nbits + 1.76 (dB)$$

$$ENOB = (SNR - 1.76) / 6.02$$

| SNR (dB) | ENOB  |

|----------|-------|

| 40       | 6.3   |

| 50       | 8.0   |

| 60       | 9.7   |

| 70       | 11.33 |

| 80       | 13    |

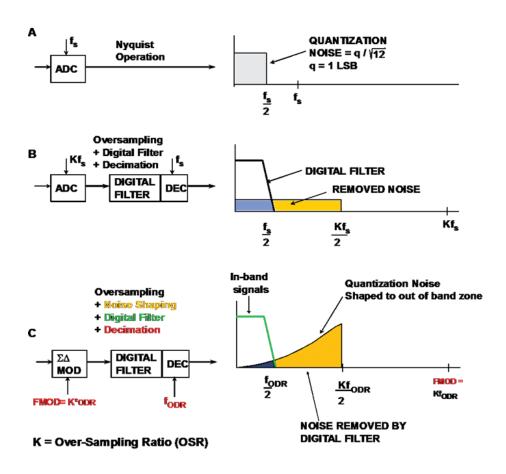

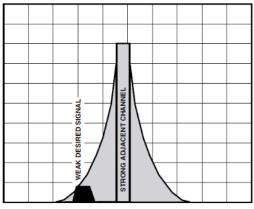

# **SIGMA-DELTA BENEFITS ON NOISE**

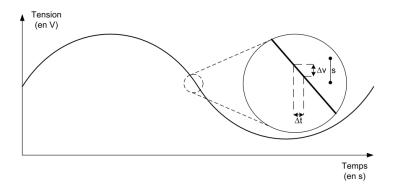

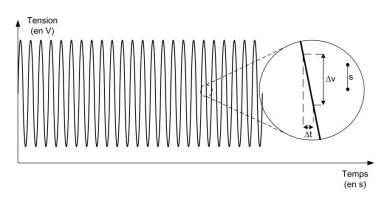

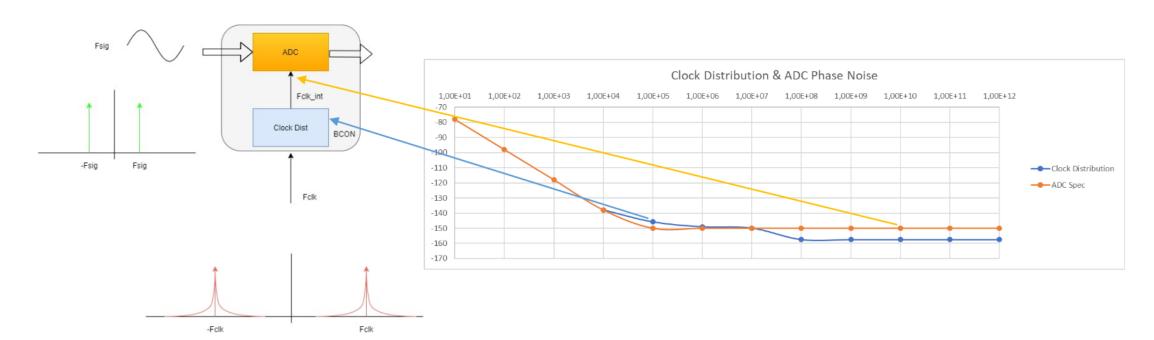

# **CLOCK JITTER IMPACT**

Performances could not be reached if clock is not good enough

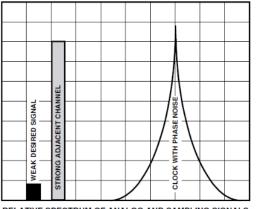

# **CLOCK PHASE NOISE IMPACT**

RELATIVE SPECTRUM OF ANALOG AND SAMPLING SIGNALS

RELATIVE EFFECTS OF SAMPLE CLOCK ON ANALOG SIGNAL.

RECIPROCAL IS ALSO TRUE

### **CONTACT & LEGAL INFO**

Main contact to discuss our products:

### Denis MARSAULT – Product Manager

denis.marsault@scalinx.com

+33 6 25 14 93 99

Company information

Registration n° 813 872 025 VAT FR 84 813 872 025 contact@scalinx.com www.scalinx.com

## **SCALINX OFFICES**

### **Design Center**

8 rue Commodore JH Hallet 14000 Caen - FRANCE

### Headquarter

18 rue des Belles Feuilles 75116 Paris - FRANCE

### **Design Center**

27 rue de la Vistule 75013 Paris - FRANCE

#### **Design Center**

155 Cours Berriat 38000 Grenoble - FRANCE

# THANK YOU •