## *Engagement du LPNHE dans l'Upgrade du détecteur ND280 / T2K-II*

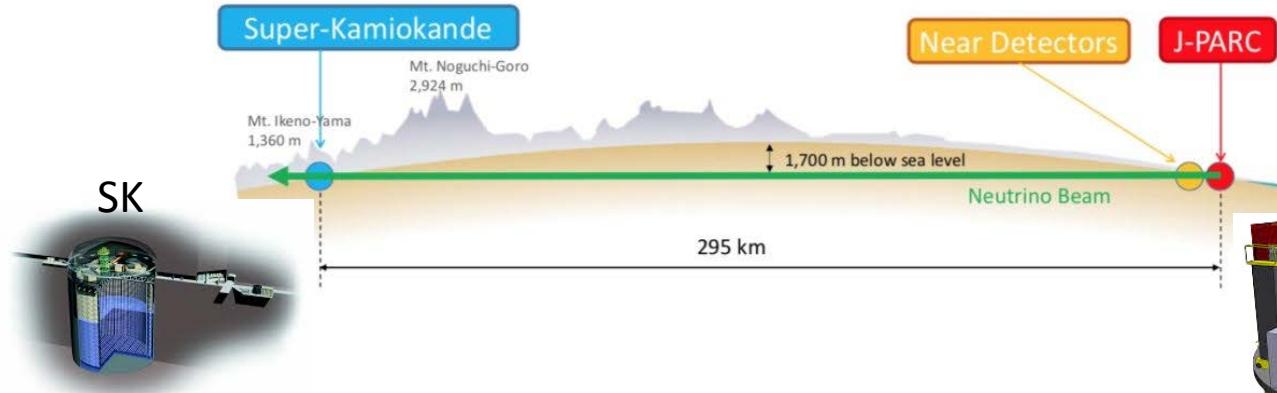

T2K : expérience implantée au Japon, en service depuis 2009

→ étude des *neutrinos*

- oscillation des neutrinos

- violation de CP/matière-antimatière

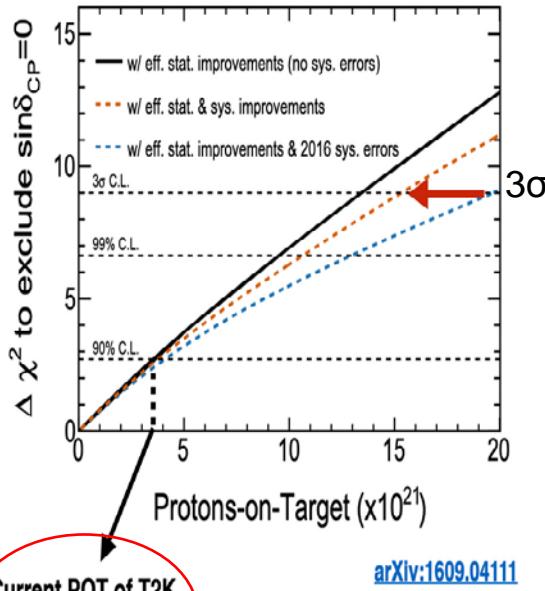

T2K : ~10 ans de prise de données à ce jour.

Pour obtenir des résultats statistiques probants pour la physique, il faudrait cumuler les données pendant de (trop) nombreuses années.

T2K-II → Upgrade du faisceau et du détecteur proche (ND280) : *diminution des incertitudes systématiques*.

Le cumul de données pourrait être suffisant au bout *de 4 à 5 ans*.

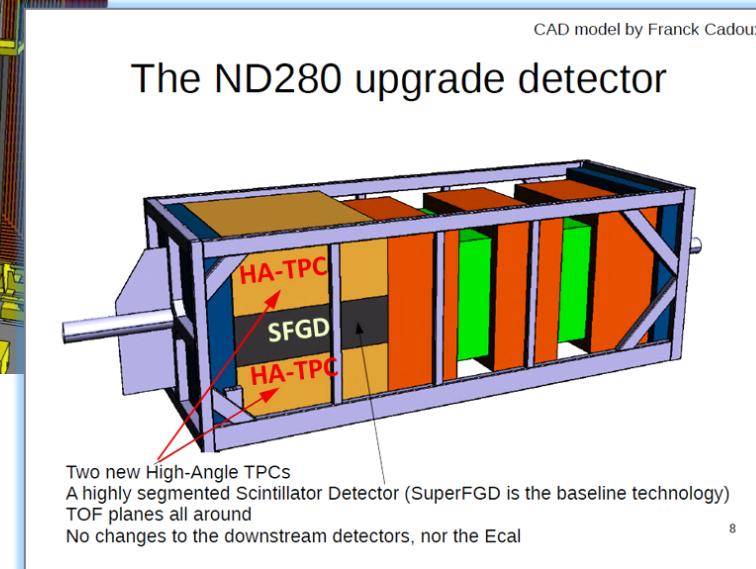

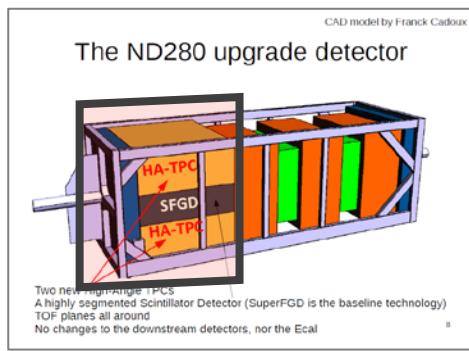

The ND280 upgrade detector

Slide de Diego

à traduire

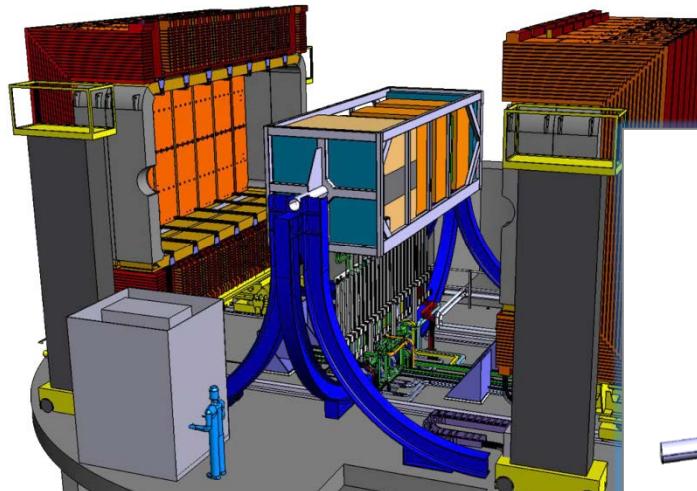

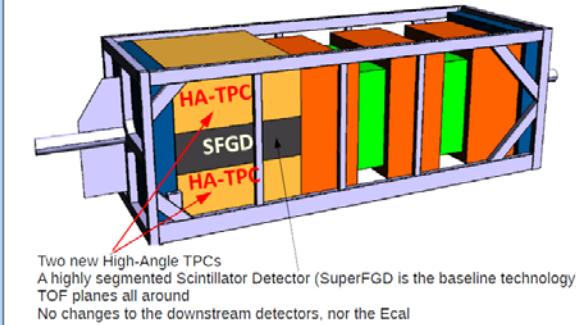

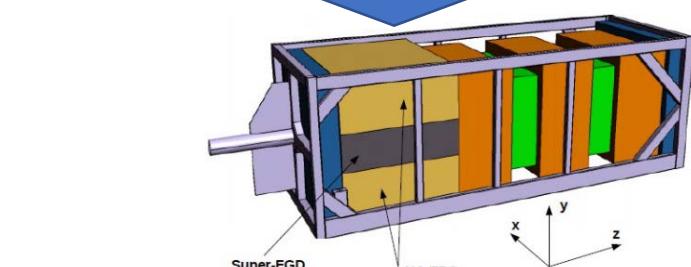

## T2K-II The upgrade ND280 Near detector

Detector operational since 2010 with LPNHE contribution

Roles :

- Monitoring of neutrino beam before oscillation

- Strongly constrain the expected rates at SK for precision oscillation analyses

- Measure the neutrino interaction rates

After upgrade :

- Beam power from 485 kW to 1.3 MW

- Remove the POD

- Replaced with new tracker system consisting of a Super Fine Grained Detector (**SuperFGD**),

- two new High-Angle TPCs

- Time-of-Flight (**TOF**)

- New electronics ...

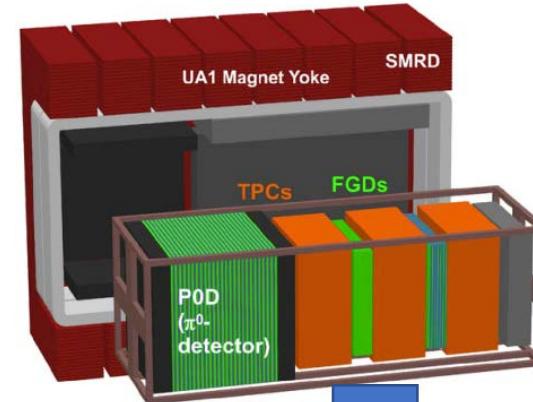

### ND280 COMPOSITION (Before Upgrade)

- Inside 0.2 T **magnet**

- Pi-Zero detector (**POD**)

- Two Fine-Grained detectors (**FGD**)

- Three Time Projection Chambers (**TPC**)

- Electromagnetic Calorimeter (**ECal**)

Slide de Diego

à traduire

# ND280

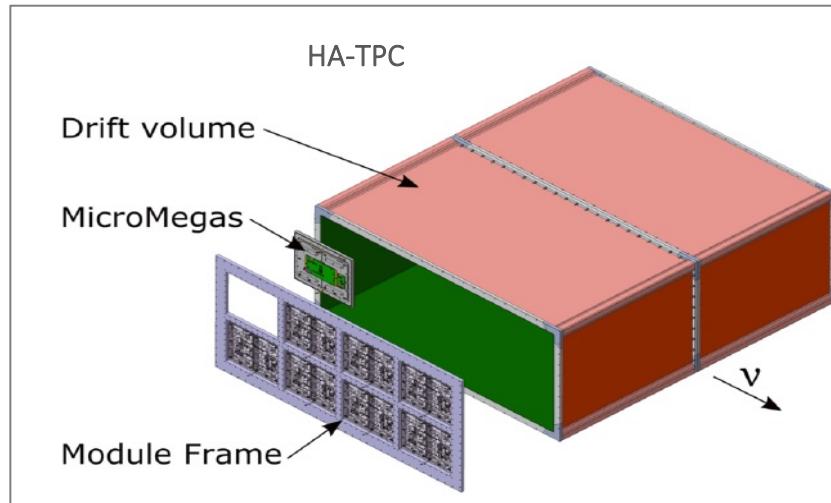

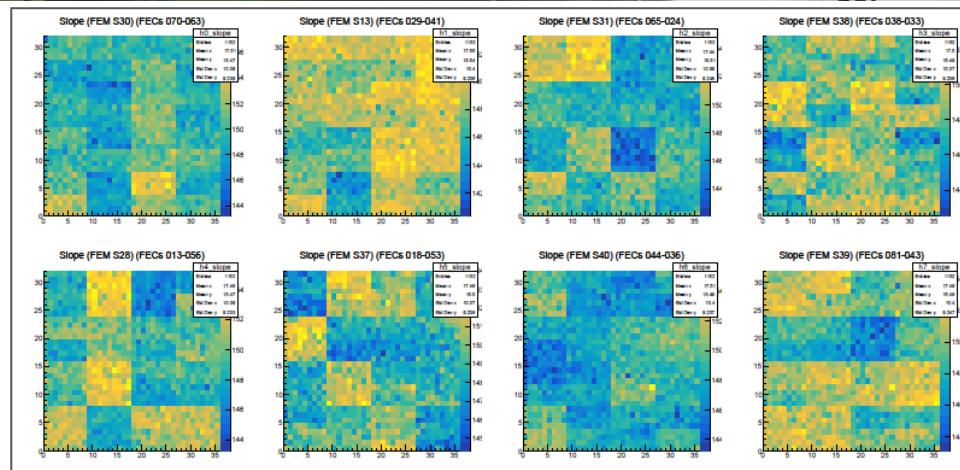

## Time Projection Chambers - TPC

- ✓ Sub-detector components in the tracker system

- ✓ ND280 upgrade will include 2 new HA-TPC and 3 old TPC

- ✓ Playing a key role in the study of the neutrino flux and interactions (charge, momentum and dE/dx PID)

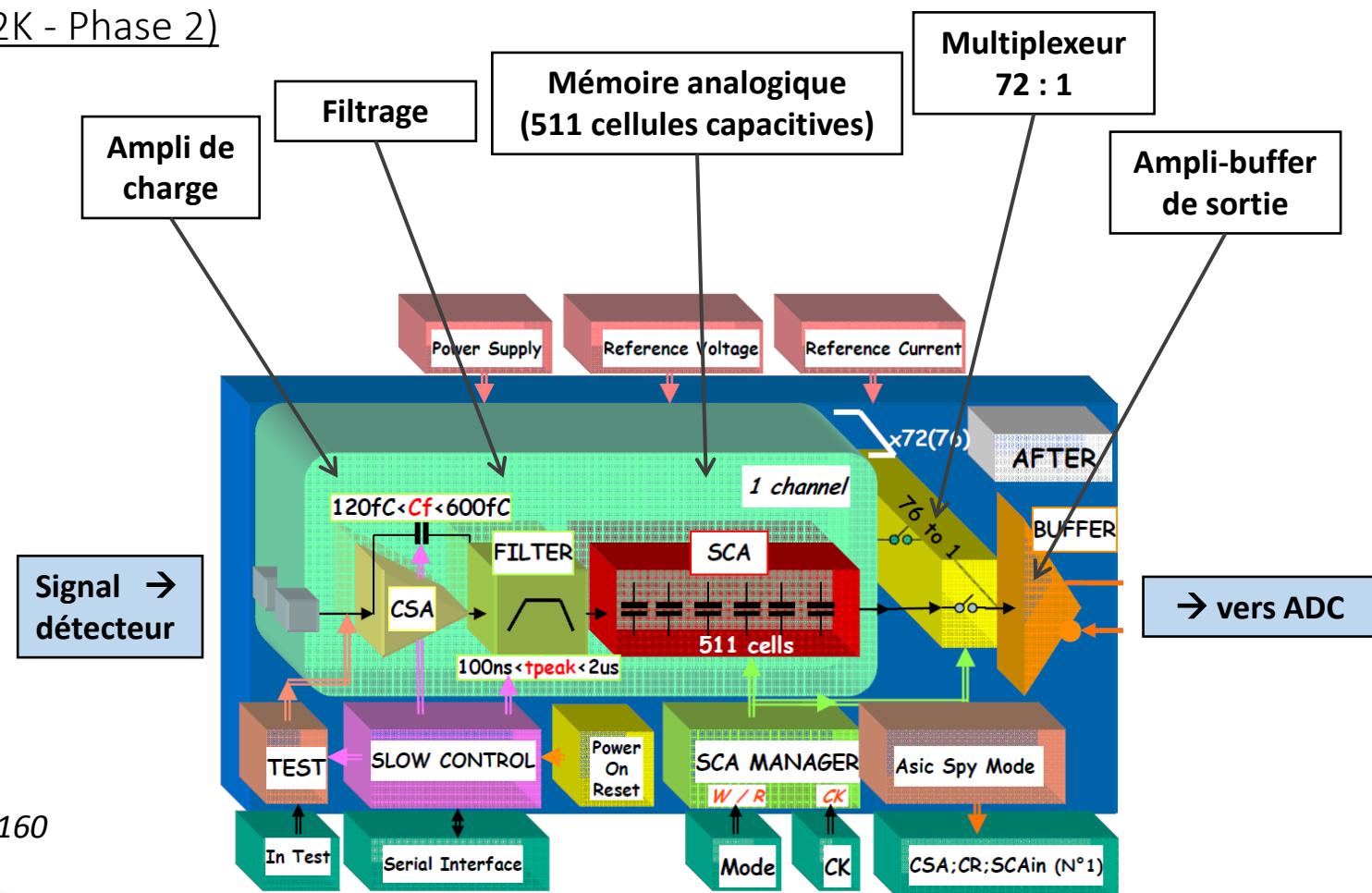

- ✓ Electronics: Readout ASIC based on the AFTER chip

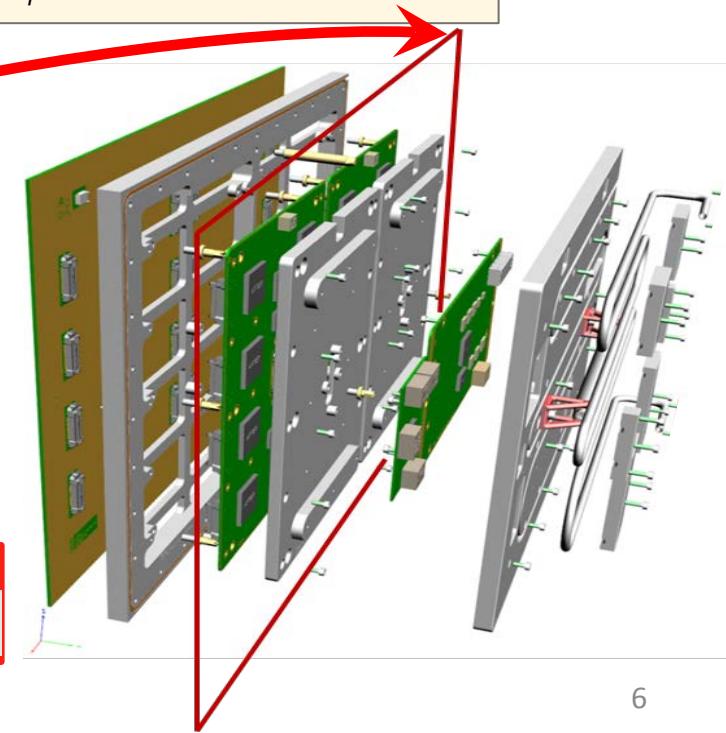

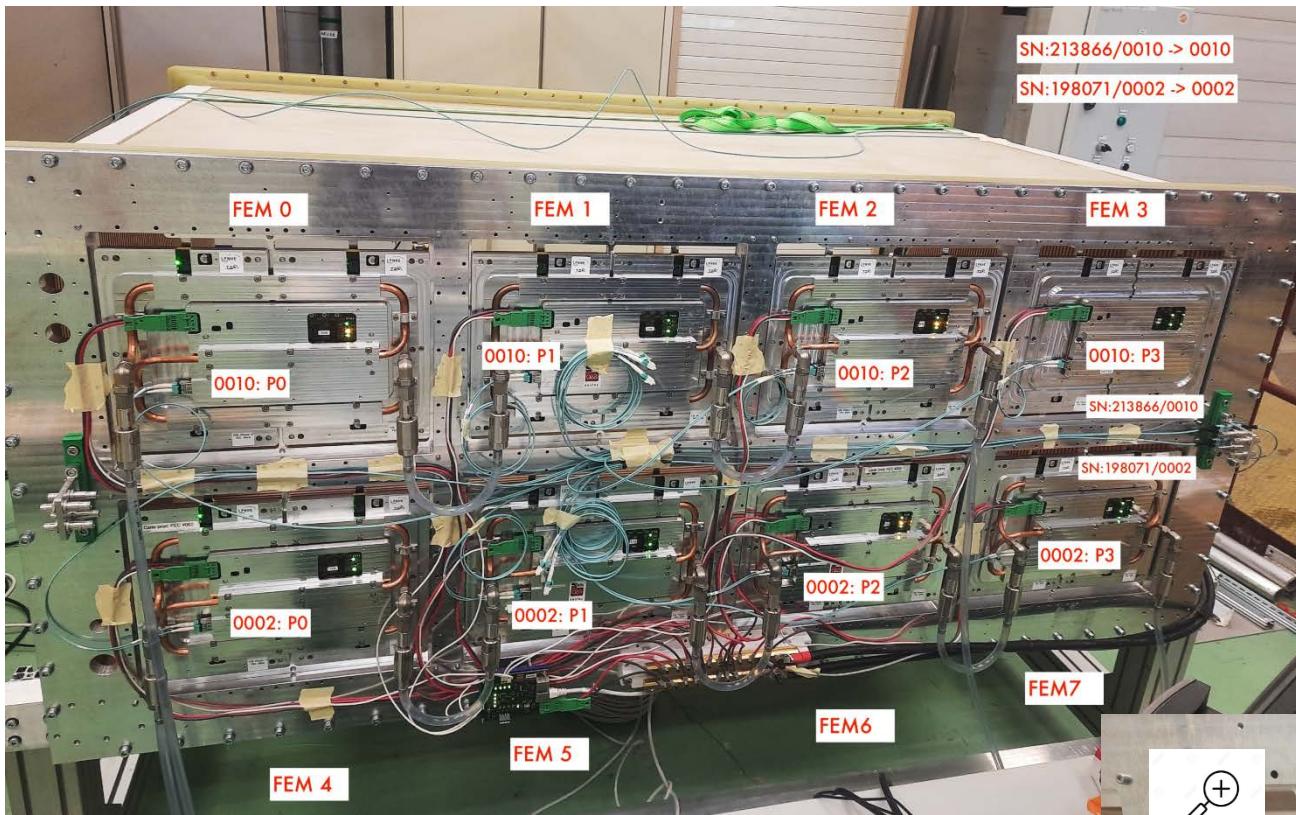

### COMPOSITION OF HA-TPC

- 2 module frames

- Cathode mid-plane

- Gas mixture (Ar + CO<sub>2</sub>, CH<sub>4</sub> and iCH<sub>4</sub>)

- 8 detector modules **micromegas**

Each detector module holds :

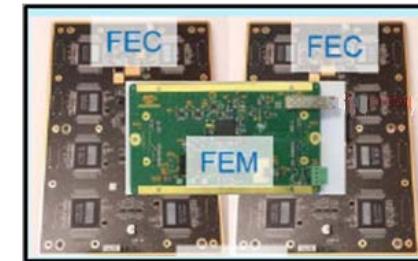

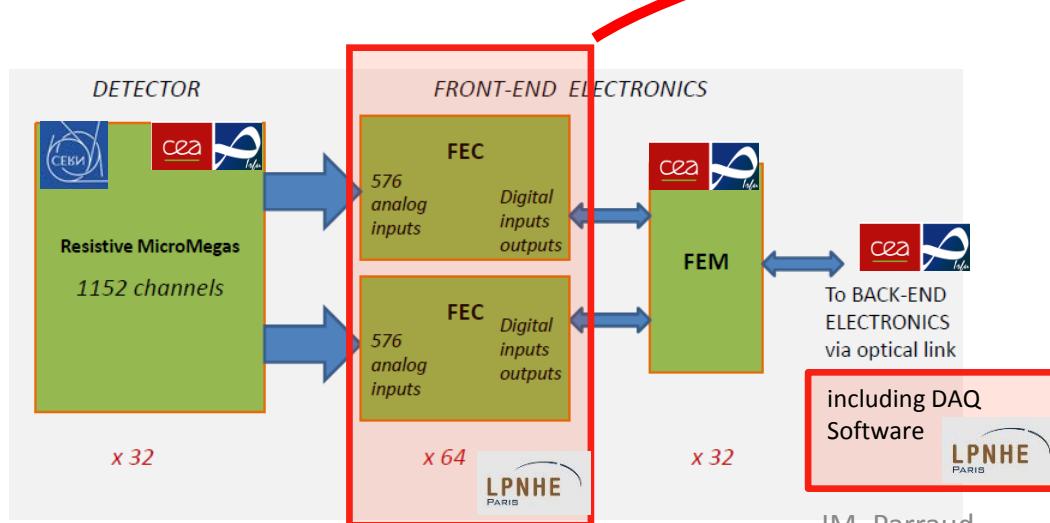

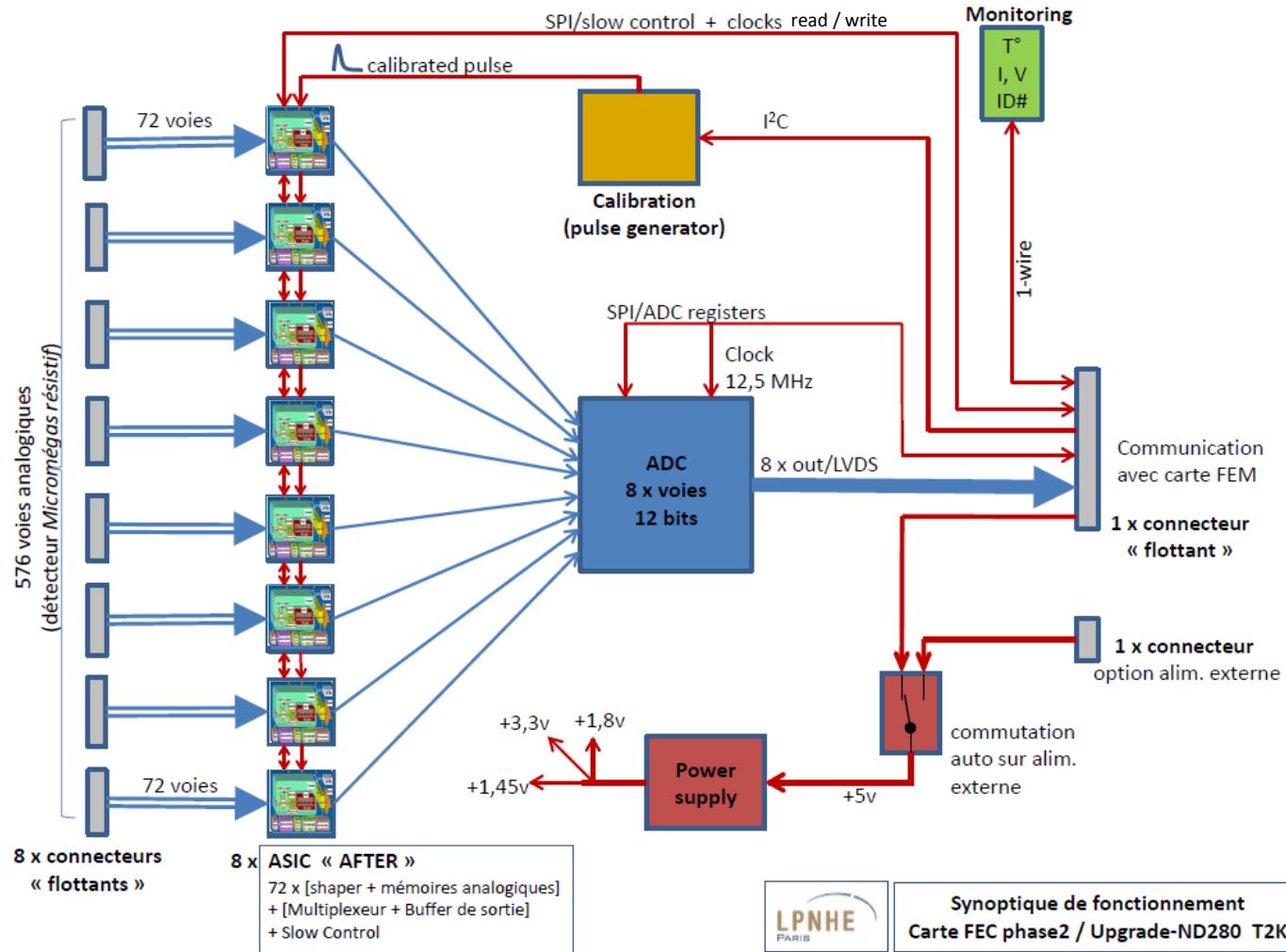

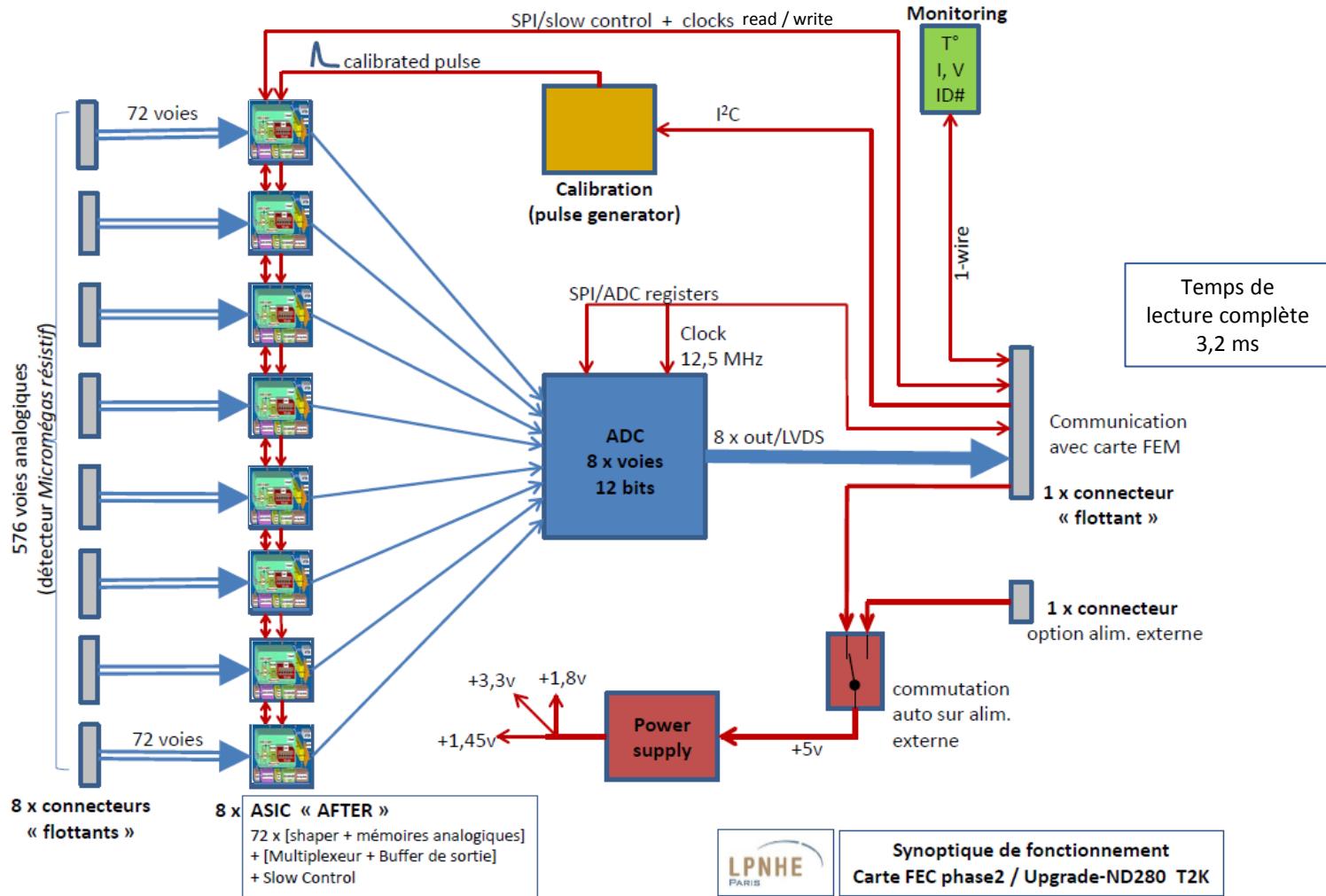

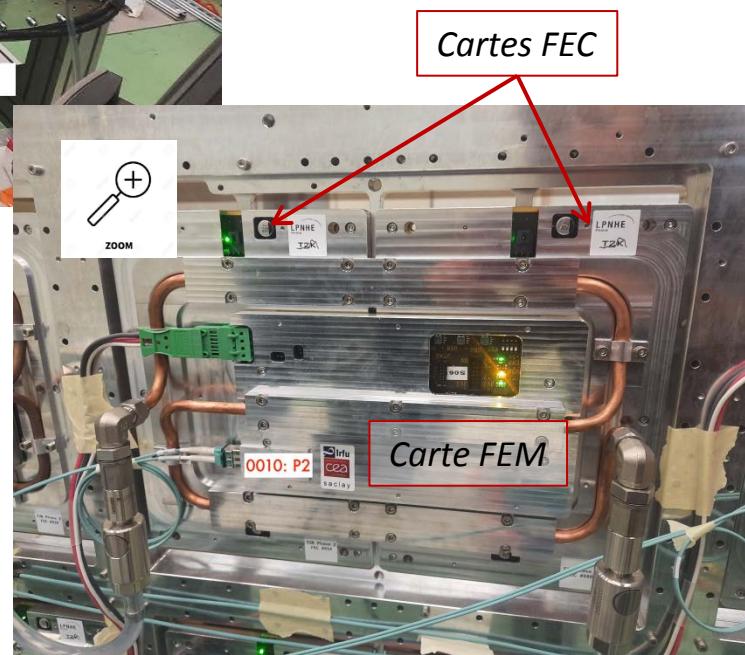

#### Two Front-End Cards (FECs), 576-channel each

These capture the analog signals of the 1152 pads of the detector module and convert the acquired samples in digital format using an octal-channel analog to digital converter (ADC).

#### One Front-End Mezzanine card (FEM).

This controls the two FECs and performs some elementary data processing such as baseline offset correction, zero-suppression and temporary data storage.

Slide de Diego

à traduire

# HA-TPC

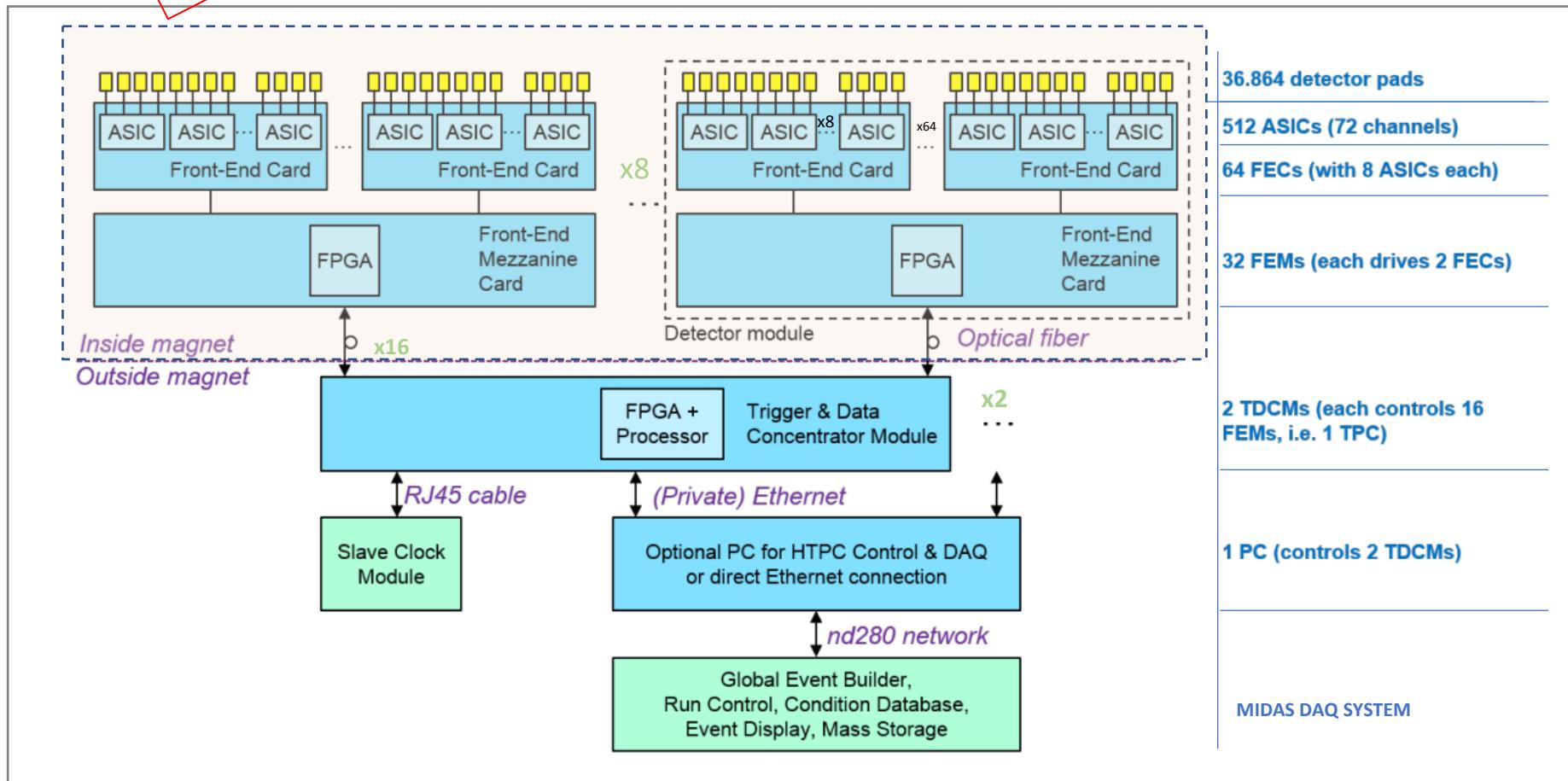

## ReadOut Architecture (1/2 TPC)

L'ancien calorimètre est remplacé par une *cible à scintillateurs* (SFGD) et 2 *chambres à dérive* (HA-TPC) équipées d'électronique de lecture.

En collaboration avec des équipes de l'[Irfu/CEA](#), du [CERN](#) et de labos [italiens](#), [polonais](#), [espagnols](#) et [allemands](#), l'équipe du [LPNHE](#) participe à la construction des **nouvelles HA-TPC**, à plusieurs niveaux de compétences techniques :

- ✓ électronique

- ✓ mécanique

- ✓ informatique

### Contribution LPNHE

## Contribution du LPNHE pour l'upgrade-T2K

3 livrables :

- ▶ Conception + fabrication

Cartes électroniques FEC (*front-end card*) : ***Qté Totale = 84***

(**64** sur le détecteur + 8 spares + 12 pour bancs-tests collab)

- Production : marché PUMA / Ouestronic : pré-série de **12** + série de **72**

- ▶ Conception conjointe avec l'Irfu + fabrication

Capots de refroidissement des cartes FEC : ***Qté Totale = 80***

(**64** sur le détecteur + 8 spares + 8 pour tests fabriqués au LPNHE)

- Production : Chanteloup-Associés : pré-série de **8** + série de **64**

- ▶ Développement des **softwares** DAQ : acquisition des données des HA-TPC

- software embarqué sur les cartes back-end *TDCM* de l'Irfu

- software sur PC d'acquisition de l'expérience

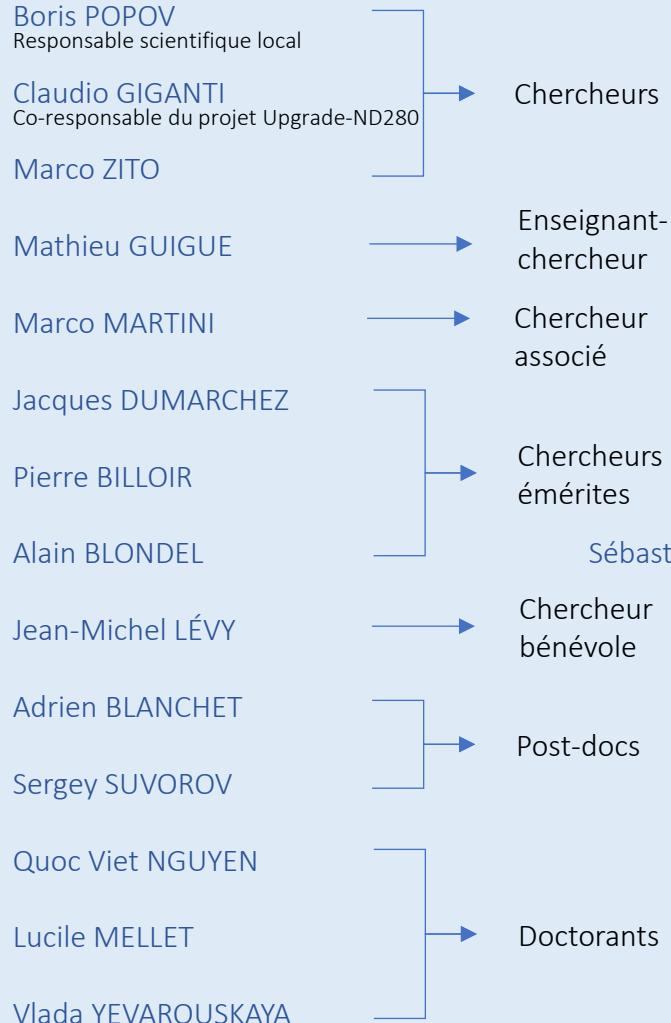

## Equipe Upgrade-T2K du LPNHE

### Equipe scientifique (physiciens)

### Equipe technique (ITA)

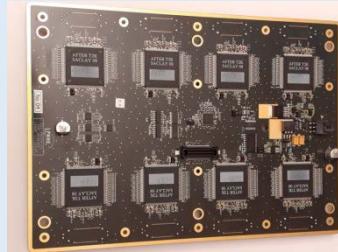

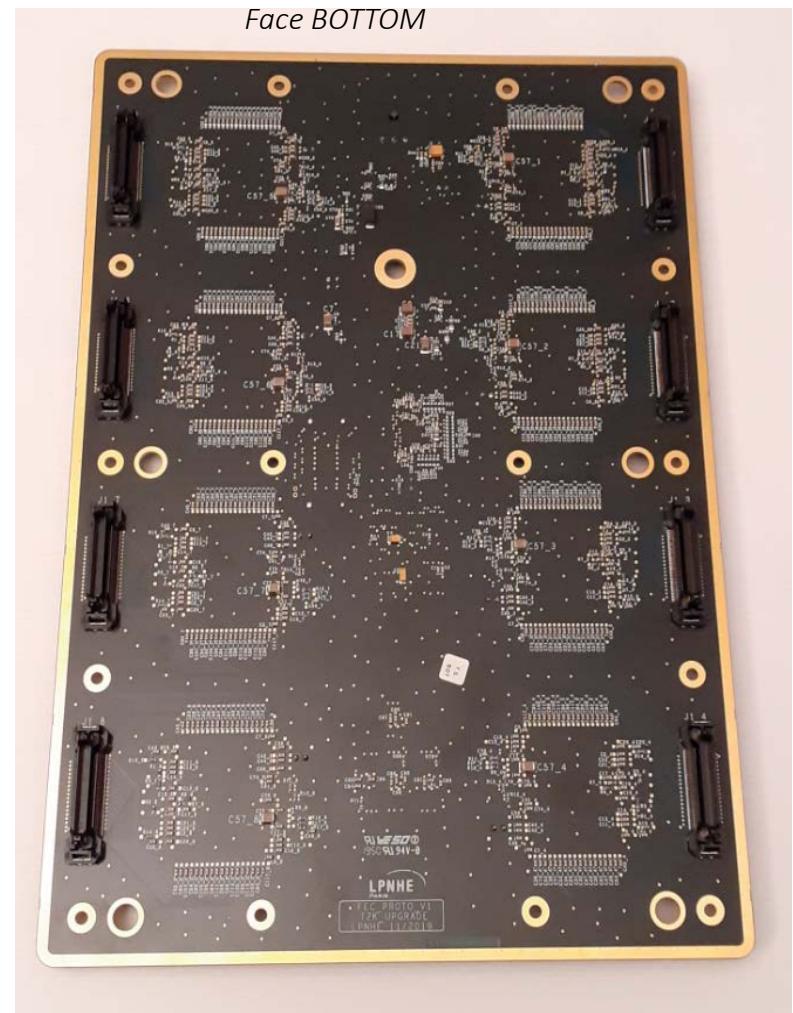

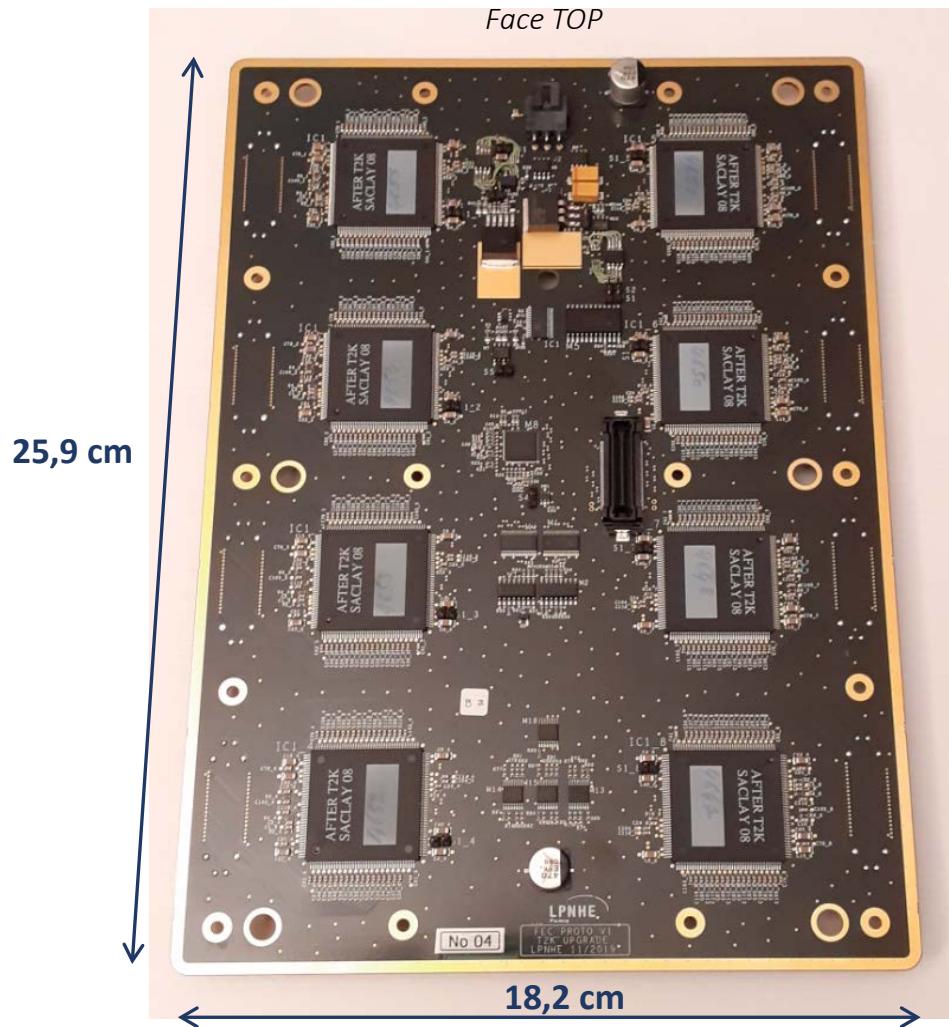

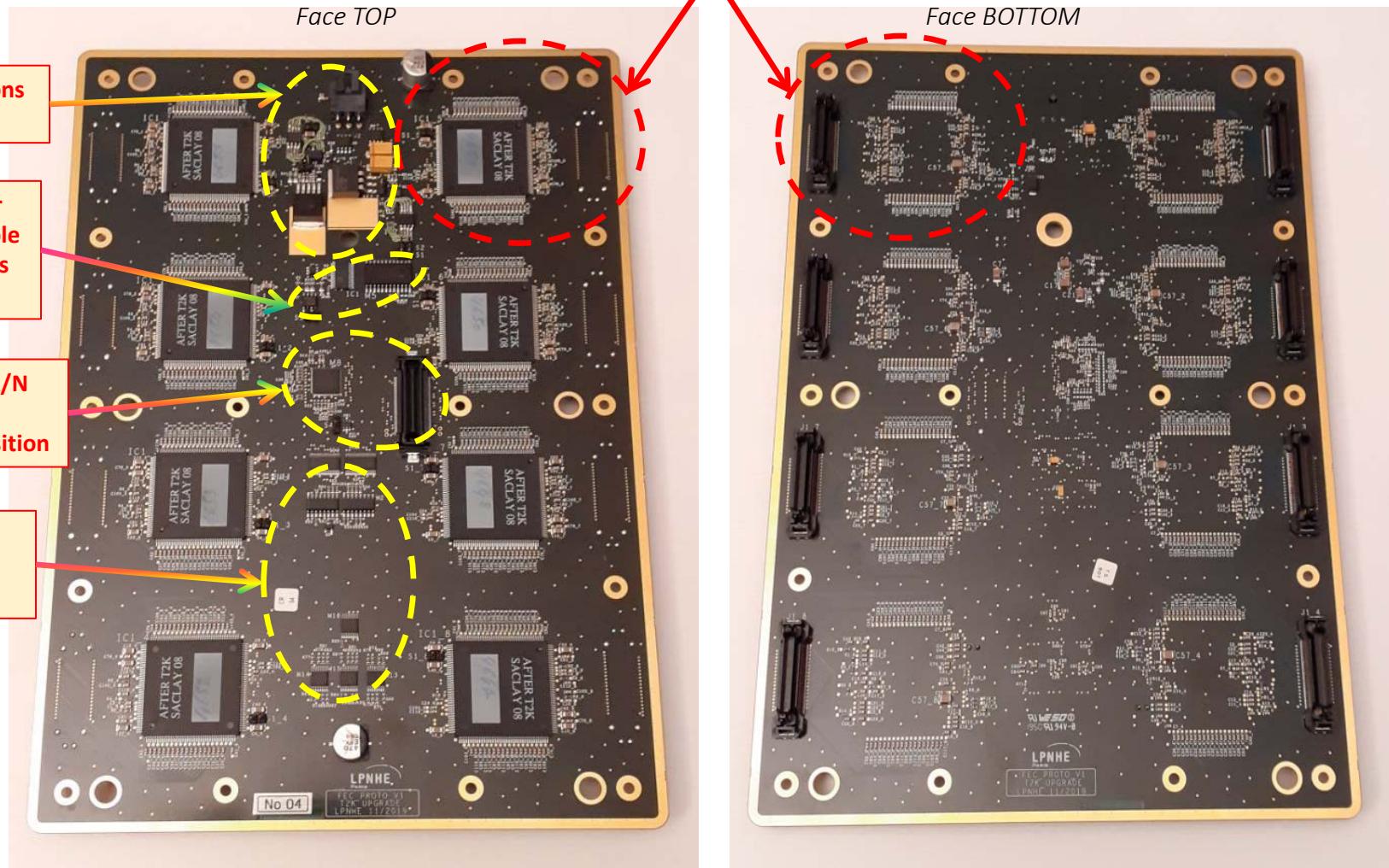

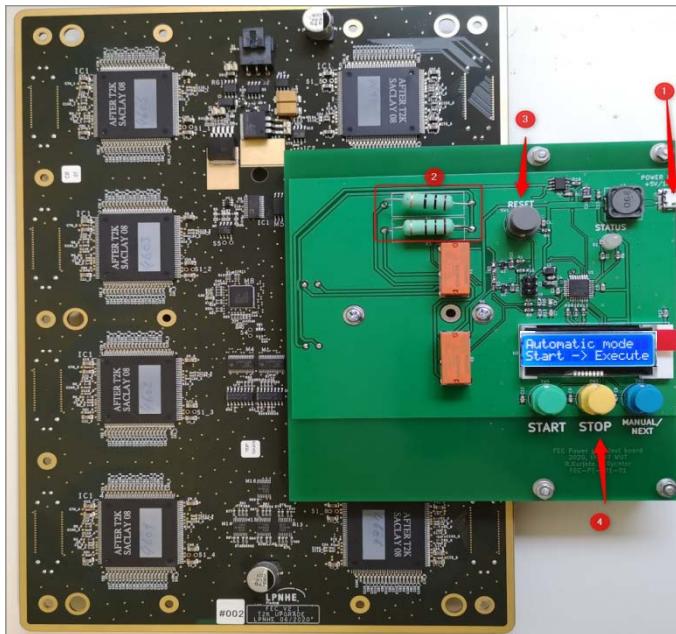

## Carte FEC (T2K - Phase 2)

Cette carte est une évolution de la carte FEC existante sur les TPCs de la phase 1 (Irfu/CEA) avec **2x plus de voies**.

Carte de traitement de *signaux analogiques et conversion numérique*, elle réutilise le chip **Asic AFTER** (design Irfu/CEA) déjà implanté et éprouvé sur les cartes de la phase I.

Carte FEC – Phase 1

## Carte FEC (T2K - Phase 2)

Cette carte est une évolution de la carte FEC existante sur les TPCs de la phase I (Irfu/CEA) avec **2x plus de voies**.

Carte de traitement de signaux analogiques et conversion numérique, elle réutilise le chip **Asic AFTER** (design Irfu/CEA) déjà implanté et éprouvé sur les cartes de la phase I.

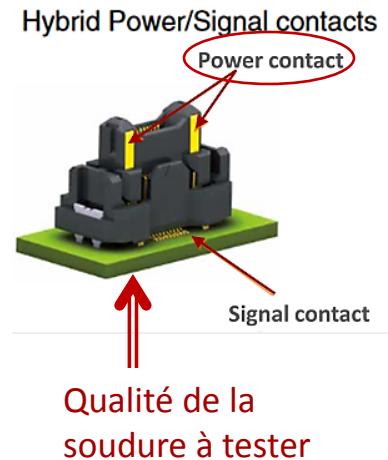

*Challenges:* → 576 voies de mesures par carte

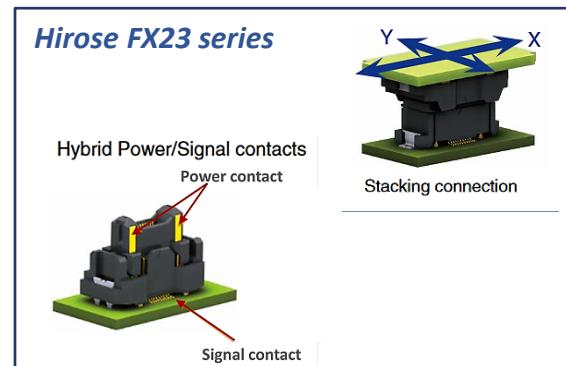

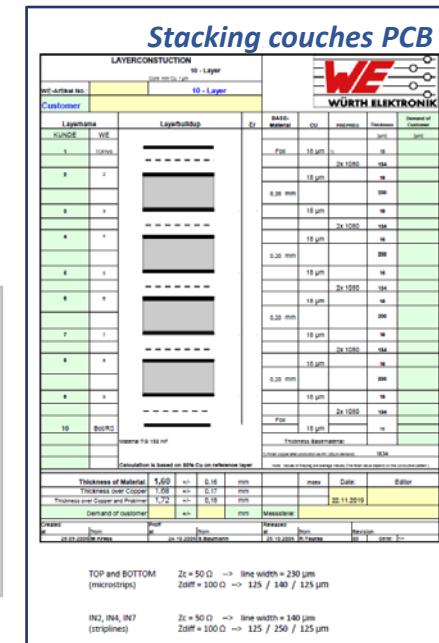

circuit imprimé sur 10 couches de cuivre

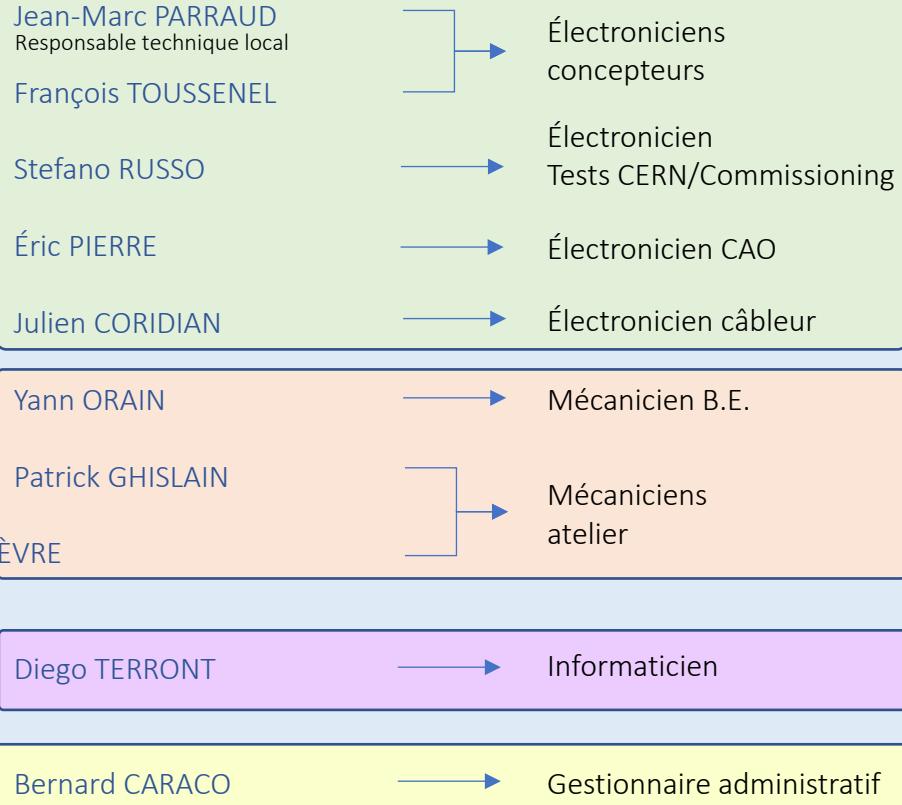

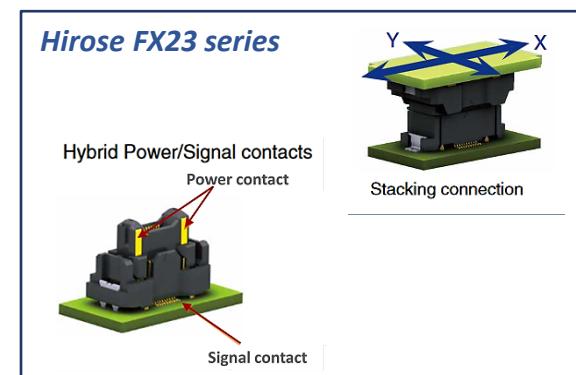

- choix de connectique « flottante » - - - - NOUVEAU pour la collab.

- MicroMegas detector** ↔ FEC (8 connecteurs)

- FEM** ↔ FEC (1 connecteur)

## Carte FEC (T2K - Phase 2)

Cette carte est une évolution de la carte FEC existante sur les TPCs de la phase I (Irfu/CEA) avec **2x plus de voies**.

Carte de traitement de signaux analogiques et conversion numérique, elle réutilise le chip **Asic AFTER** (design Irfu/CEA) déjà implanté et éprouvé sur les cartes de la phase I.

*Challenges : → 576 voies de mesures* par carte :

circuit imprimé sur *10 couches de cuivre*

- choix de connectique « flottante » - - - - NOUVEAU pour la collab.

MicroMegas detector ↔ FEC (8 connecteurs)

FEM ↔ FEC (1 connecteur)

*Contraintes* : → fabrication circuit imprimé **halogen free**

(sans *Fluor, Chlore, Brome, Iode, Astate*)

- process sans *Plomb* / **RoHS**

- lignes à **impédances contrôlées** ( $50 \Omega$  et  $100 \Omega$  diff.)

- soumis à un **champ magnétique** constant = 0,2 T

- début de la **pénurie** des composants électroniques

## Carte FEC (T2K - Phase 2)

### **FEC / Phase2 :**

Based on FEC/Phase1 that works fine for more than 10 years at T2K-Tokai site.

Use of the **same ASIC** (→ « **After** » / IRFU) for the read out and processing of analog signals coming from the detector.

**Qty=8** (qty=4 in Phase1)

Use of an **8 channel ADC** (AD9637-40), instead of a 4 channel ADC.

The **global architecture** remains the same as it was in Phase1.

## Carte FEC (T2K - Phase 2)

### **FEC / Phase2 :**

Based on FEC/Phase1 that works fine for more than 10 years at T2K-Tokai site.

Use of the **same ASIC** (→ « **After** » / IRFU) for the read out and processing of analog signals coming from the detector.

Qty=8 (qty=4 in Phase1)

Use of an 8 channel ADC (AD9637-40), instead of a 4 channel ADC.

The global architecture remains the same as it was in Phase1.

Boîtier LQFP - 160

Fig 2: Block diagram of the AFTER chip.

## Carte FEC (T2K - Phase 2)

### **FEC / Phase2 :**

Based on FEC/Phase1 that works fine for more than 10 years at T2K-Tokai site.

Use of the **same ASIC** (→ « **After** » / IRFU) for the read out and processing of analog signals coming from the detector.

**Qty=8** (qty=4 in Phase1)

Use of an **8 channel ADC** (AD9637-40), instead of a 4 channel ADC.

The **global architecture** remains the same as it was in Phase1.

Carte FEC (T2K - Phase 2)

Carte FEC (T2K - Phase 2)

Bloc 72 entrées analogiques

+ ASIC «AFTER» / boîtier LQFP

## Carte FEC (T2K - Phase 2)

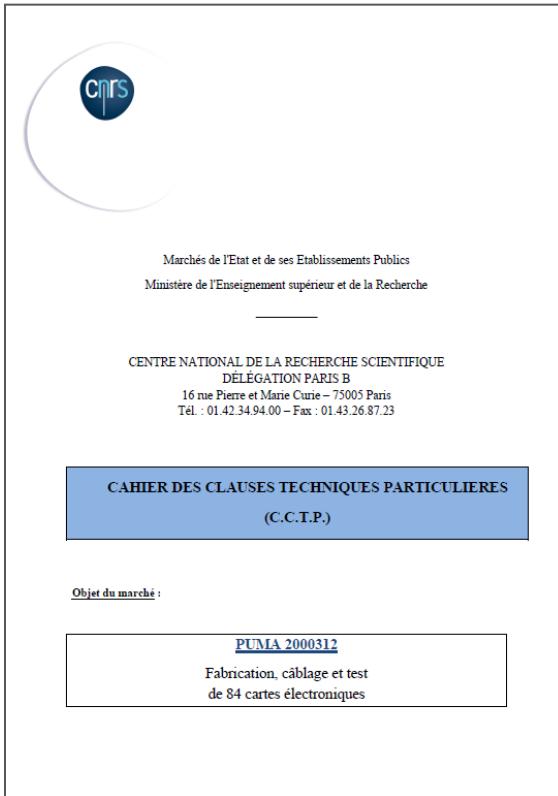

**Appel d'offres / PUMA pour la fabrication des 84 cartes FEC** → coût total estimé > 25 k€

### 1/ Fiche de consultation « MAPA » contractuelle

**LABORATOIRE PHYSIQUE NUCLÉAIRE ET HAUTES ENERGIES**      PROCÉDURE PUMA N° 2000312

**Fiche de consultation MAPA**

INTITULÉ DE LA CONSULTATION : FABRICATION, CABLAGE ET TESTS DE CARTES ÉLECTRONIQUES

ADRESSE DU PROFIL ACHETEUR DU CNRS

<https://www.puma.cnrs.fr/>

NUMÉRO D'ASSISTANCE DE LA PLATE-FORME : +33 (0)1 76 64 74 07

Date et heure limites de remise des réponses

15/05/2020 12:00

(Heure de Paris)

### Détermination du choix de l'entreprise

**! IMPORTANT**

#### XI.4 SÉLECTION DE L'OFFRE ÉCONOMIQUEMENT LA PLUS AVANTAGEUSE

Conformément à l'article R2352-5 du Code de la commande publique, le CNRS choisit l'offre économiquement la plus avantageuse.

Les critères d'attribution sont listés dans le tableau suivant :

| Critères et sous-critères                                        | Pondération |

|------------------------------------------------------------------|-------------|

| Prix                                                             | 30%         |

| Coûts des tranches fermes et conditionnelles                     | 20%         |

| Coûts des prestations supplémentaires éventuelles                | 10%         |

| Critères techniques                                              | 50%         |

| Garanties apportées en terme de fabrication de circuit imprimé   | 15%         |

| Garanties apportées en terme de câblage, test et conditionnement | 15%         |

| Garanties apportées en terme de contrôle qualité                 | 10%         |

| Contenu et qualité de l'offre                                    | 10%         |

| Délais, compatibilité avec le calendrier prévisionnel            | 15%         |

| Moyens mis en œuvre pour le développement durable                | 5%          |

Les offres irrégulières, inappropriées, ou inacceptables ne seront ni notées ni classées.

## Carte FEC (T2K - Phase 2)

**Appel d'offres / PUMA pour la fabrication des 84 cartes FEC** → coût total estimé > 25 k€

### 2/ Cahier des clauses techniques particulières (CCTP)

Document essentiel qui :

- définit les besoins

- recense les documents et le matériel à fournir par le LPNHE

(→ *dossier de fabrication, matériel de test, ...*)

et ceux à fournir par le prestataire

(→ *fiches de suivi qualité, fiches de tests, composants électroniques, ...*)

- recense toutes les opérations techniques à réaliser par le prestataire

- ✓ pour la fabrication

- ✓ pour les tests de validation

- ✓ pour le conditionnement et l'expédition

- définit les contrôles d'acceptation du matériel (recette)

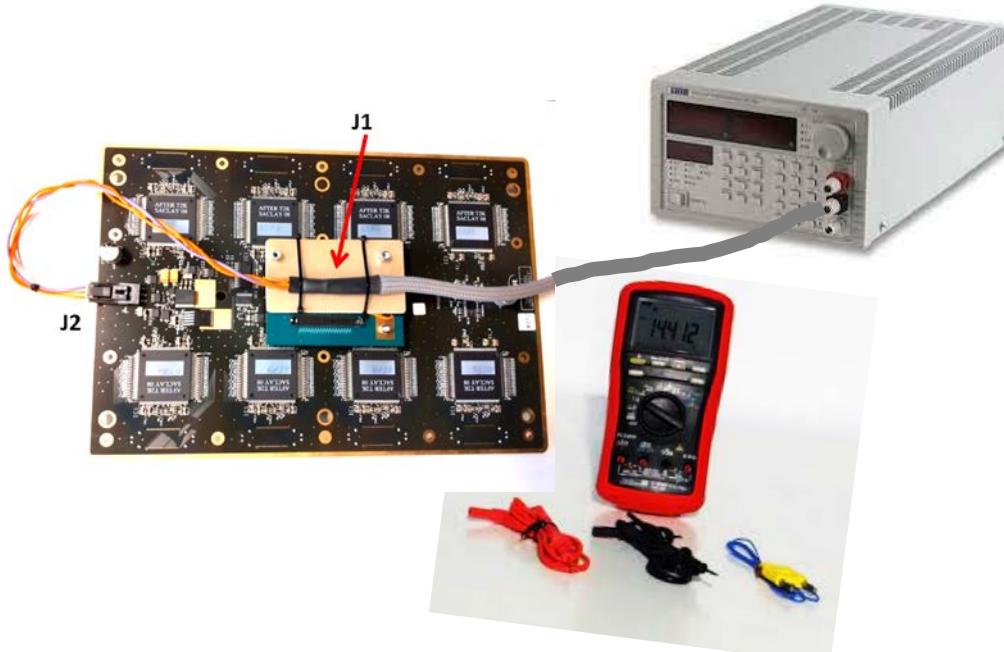

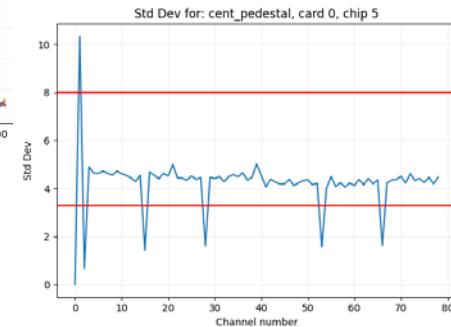

## Carte FEC / Tests

### Banc de tests des alimentations internes + consommation

- Tests de la production des cartes chez le sous-traitant / Ouestronic

- 84 cartes (12 pré-série + 72 de série) testées sans défaut.

### *Fiche de suivi individuelle relevés de mesures*

| LPNHE PARIS                                |                                                                           | FEC V2.1 - T2K-II    |            |

|--------------------------------------------|---------------------------------------------------------------------------|----------------------|------------|

| FICHE DE SUIVI - ENREGISTREMENT DES TESTS  |                                                                           |                      |            |

| DATE :                                     | 09/10/21                                                                  | SOUSTRAITANT :       | OUESTRONIC |

| SN :                                       | 016                                                                       |                      |            |

| TESTS                                      |                                                                           | RESULTATS            |            |

| Banc-test "alimentation"                   | Vérification si D12/led verte allumée                                     | OK                   |            |

|                                            | 56 (3,30 ±0,10Vdc)                                                        | 3,3Vdc               |            |

|                                            | 57 (1,80 ±0,05Vdc)                                                        | 1,8Vdc               |            |

| Banc-test des power-plus connecteur Hirose | 58 (1,32 ±0,05Vdc)                                                        | 1,33Vdc              |            |

|                                            | Conso courant (1,35 ±0,15A)                                               | 1,31A                |            |

|                                            | Test des soudures des alimentations sur J1 avec carte adaptatrice/testeur | OK                   |            |

| Banc de tests fonctionnels piloté par PC   | Programme de test : connexion avec la carte FEC                           | OK                   |            |

|                                            | Programme de test : vérification de la carte FEC                          | OK                   |            |

|                                            | Vérification des résultats des tests (rapport PDF)                        | OK                   |            |

|                                            | Sauvegarde des résultats des tests sur serveur<br>Download                | OK                   |            |

| TEST réalisé par :                         | LC                                                                        | Validation du test : | OK         |

| PANNE                                      |                                                                           | REPARATION           |            |

|                                            |                                                                           |                      |            |

## Carte FEC / Tests

**Banc de tests des « power-pins » du connecteur de liaison avec la FEM**

réalisé par l'équipe de l'[Université de Technologie de Varsovie](#).

- Tests de la production des cartes chez le sous-traitant / Ouestronic

- 84 cartes (pré-série + série) testées sans défaut

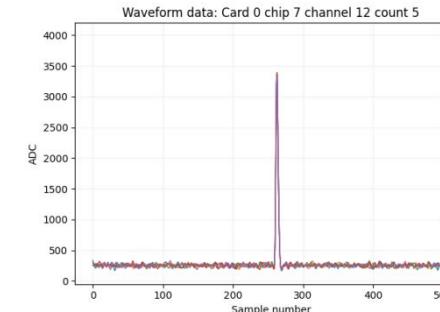

## Carte FEC / Tests

**Banc de tests fonctionnels** des cartes FEC

réalisé par l'équipe de l'[Université de Technologie de Varsovie](#).

| Fec test report:                                       |                        |                                                 |

|--------------------------------------------------------|------------------------|-------------------------------------------------|

| Date: 2021-04-28 09:46:13                              |                        |                                                 |

| Tester name: LC                                        |                        |                                                 |

| Test#1 Monitoring values                               |                        |                                                 |

| 0                                                      | FEC label              | 050                                             |

| 1                                                      | FEC DC438 ID           | 0xa0000034ed0ff125                              |

| 2                                                      | FEC_T (0.35°C)         | 22.49                                           |

| 3                                                      | FEC_Vdd (2.4 to 3.4V)  | 3.290                                           |

| 4                                                      | FEC_Vdd (2.4 to 3.0V)  | 1.214                                           |

| 5                                                      | FEC_Vdd (1.9V to 2.0V) | 1.060                                           |

| Test#2 Slave control registers:                        |                        |                                                 |

| Test#3 Pedestal run:                                   |                        |                                                 |

| Mean in range (245.0-255.0), 3.3 -> rms = 0.2 (pm 4.0) |                        |                                                 |

| 0                                                      | After chip #0          | Mean: Ok                                        |

| 1                                                      | After chip #1          | Mean: Ok                                        |

| 2                                                      | After chip #2          | Mean: Ok                                        |

| 3                                                      | After chip #3          | Mean: Ok                                        |

| 4                                                      | After chip #4          | Mean: Ok                                        |

| 5                                                      | After chip #5          | Mean: Ok                                        |

| 6                                                      | After chip #6          | Mean: Ok                                        |

| 7                                                      | After chip #7          | Mean: Ok                                        |

| Test#4 ADC9637 test patterns                           |                        |                                                 |

| 0                                                      | ADC channel #0         | Pattern 1 (Middle word 2545)                    |

| 1                                                      | ADC channel #1         | Pattern 2 (Middle word 4055)                    |

| 2                                                      | ADC channel #2         | Pattern 3 (Checkboard 1395 to 2730 toggle)      |

| 3                                                      | ADC channel #3         | Pattern 4 (Checkboard word toggle)              |

| 4                                                      | ADC channel #4         | Pattern 5 (Middle short 2048)                   |

| 5                                                      | ADC channel #5         | Pattern 6 (Full-scale word 4096)                |

| 6                                                      | ADC channel #6         | Pattern 7 (Checkboard 1395 to 2730 toggle)      |

| 7                                                      | ADC channel #7         | Pattern 8 (Zero word 0)                         |

| Test#5 Pulse test:                                     |                        |                                                 |

| 0                                                      | After chip #0          | DAC: 489 (0.120) ADC:2950 to 3200 ADC_AMPL_3049 |

| 1                                                      | After chip #1          | DAC: 489 (0.120) ADC:2950 to 3200 ADC_AMPL_3059 |

| 2                                                      | After chip #2          | DAC: 483 (0.120) ADC:2950 to 3200 ADC_AMPL_3049 |

| 3                                                      | After chip #3          | DAC: 483 (0.120) ADC:2950 to 3200 ADC_AMPL_3091 |

| 4                                                      | After chip #4          | DAC: 483 (0.120) ADC:2950 to 3200 ADC_AMPL_3045 |

| 5                                                      | After chip #5          | DAC: 483 (0.120) ADC:2950 to 3200 ADC_AMPL_3085 |

| 6                                                      | After chip #6          | DAC: 489 (0.120) ADC:2950 to 3200 ADC_AMPL_3077 |

| 7                                                      | After chip #7          | DAC: 483 (0.120) ADC:2950 to 3200 ADC_AMPL_3108 |

| FEC test final result:                                 |                        |                                                 |

| Passed                                                 |                        |                                                 |

- Tests de la production des cartes chez le sous-traitant / Ouestronic

- A testé les **84 cartes (pré-série + série)** avec succès

après reprises de soudures sur quelques cartes et remplacement de circuits actifs sur

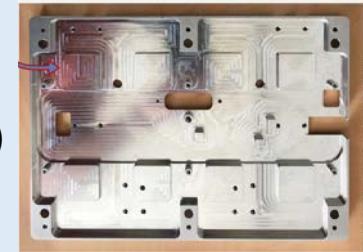

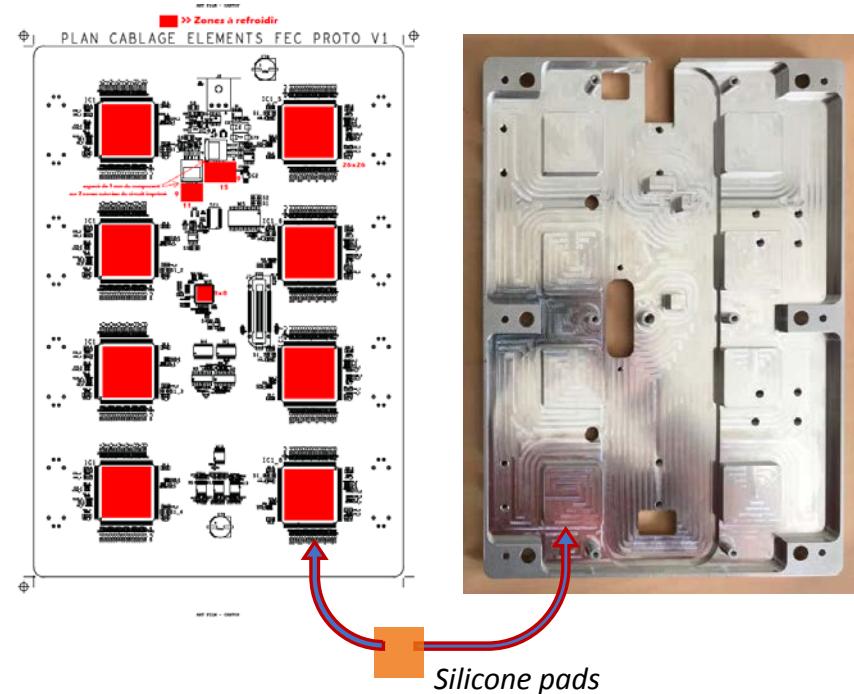

## Capot de refroidissement carte FEC

↳ Design réalisé en collaboration avec l'équipe du *BE/mécanique de l'IRFU*

Capot réalisé en **aluminium Fortal**.

Usinage à la *commande numérique*.

Le refroidissement de la carte est réalisé par **transfert thermique** entre les composants dissipateurs de chaleur et le capot.

## Capot de refroidissement carte FEC

↳ Design réalisé en collaboration avec l'équipe du *BE/mécanique de l'IRFU*

Capot réalisé en **aluminium Fortal**.

Usinage à la *commande numérique*.

Le refroidissement de la carte est réalisé par **transfert thermique** entre les composants dissipateurs de chaleur et le capot.

Le capot est lui-même refroidi par un serpentin en cuivre dans lequel circule de l'**eau refroidie**.

Toute la visserie d'assemblage est en **acier inox A4 (amagnétique)** pour ne pas perturber l'homogénéité du champ magnétique dans le détecteur.

## Développement softwares DAQ

### 1- Software sur PC d'acquisition :

→ Adrien Blanchet, Mathieu Guigue

Upgrade du précédent *soft de contrôle-commandes* de la *phase I*, construit autour de *MIDAS*.

→ Collaboration active avec l'équipe de l'Irfu-CEA

« *MIDAS est un système d'acquisition de données moderne* »

### 2- Software embarqué sur les cartes back-end *TDCM (phase II)* de l'Irfu :

→ Diego Terront

Transposition du précédent système (*Irfu-CEA*) tournant sur les cartes de la *phase I*

(1 x CPU, sans système d'exploitation)

en un système plus flexible utilisant **2 x CPU**, dont 1 tournant sur **Linux embarqué**.

→ Collaboration avec Denis Calvet / Irfu-CEA

→ Expérience accumulée qui pourra être partagée avec d'**autres projets**

Projet d' *Upgrade du détecteur ND280 / T2K-II*

2019

## Cartes électroniques FEC

## Capots de refroidissement

## Software DAQ

----- Revue IN2P3 « RSP » le 11/04/2019 -----

2020

Février 2020 : fab. 2 x FEC protos

+ essais à l'IRFUMai 2020 : Appel d'offres PUMA

→ Choix OuestronicÉté 2020 : **fab. 12 x FEC de pré-série**

Revue IRFU « PRR » le 29/10/2020

Nov. 2020 : **DÉBUT production de série (72xFEC)**

Août 2020 : fab. 2 x capots protos (IRFU)

Début 2020 : achat matériels informatiques et

**DÉBUT R&D Implémentation Linux embarqué**Été 2020 : **DÉBUT développements DAQ-MIDAS**

+ Tests OpenAMP intra-coeurs baremetal-Linux

2021

Févr. 2021 : fab. 8 x capots protos au LPNHE

Mars 2021 : **fab. 8 x capots de pré-série**

*Chanteloup-Associés*

2021

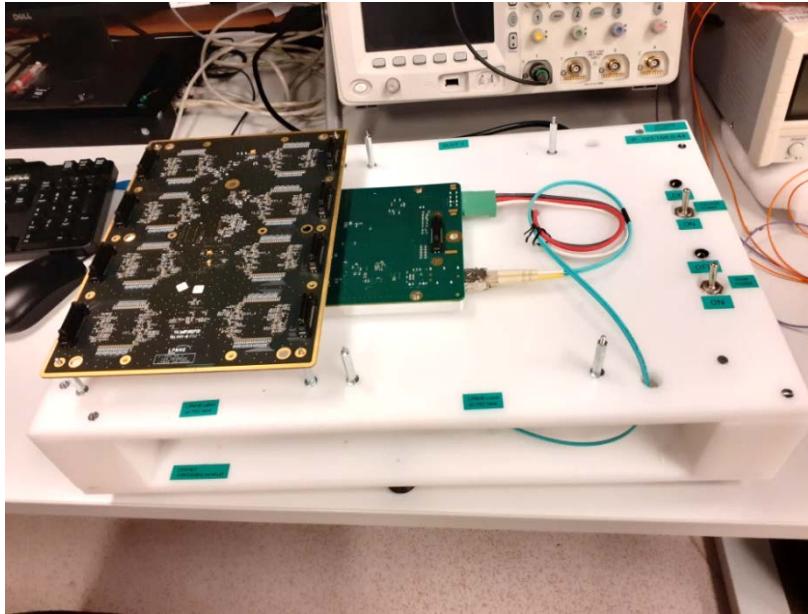

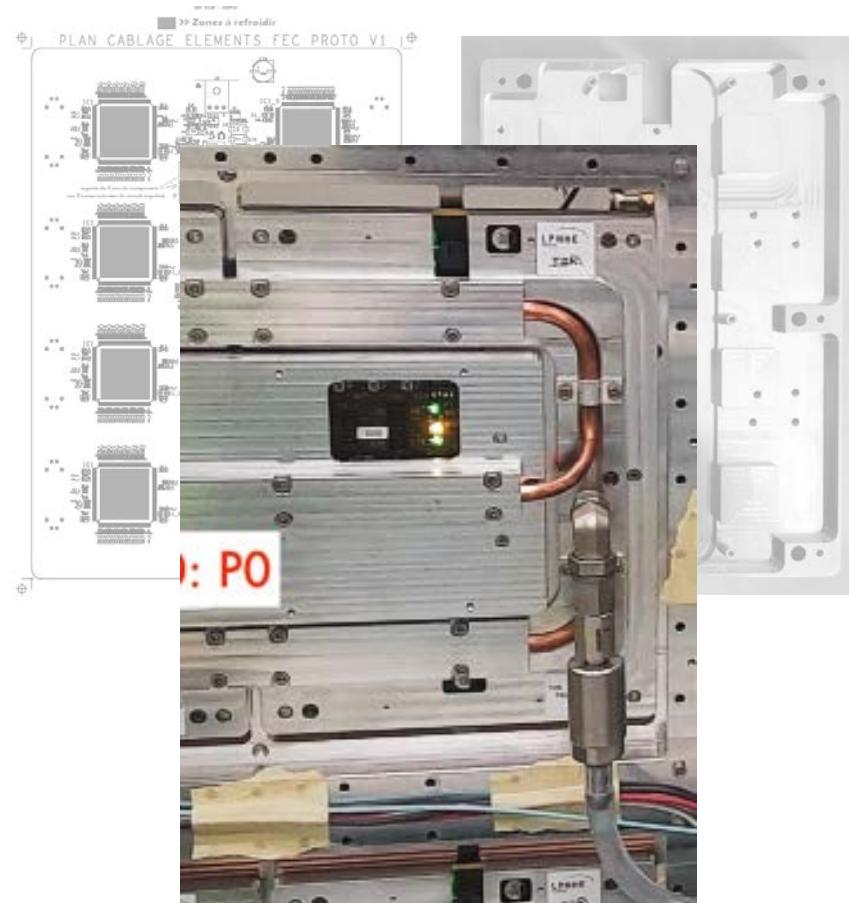

-- Juin 2021 : Tests en faisceau à DESY - 1 module (2 x FEC + capots) en champ magnétique -----

Juillet 2021 : **DÉBUT production de série (64 pcs)**

*Chanteloup-Associés*----- Nov. 2021 : Tests en faisceau au CERN - 1 module (2 x FEC + capots) en champ magnétique - **Software DAQ-MIDAS opérationnel** -----

2022

Nov 2021 : **FIN prod. + tests fonctionnels**

**72 x FEC de série**Févr. 2022 : **FIN prod. 64 x capots de série**

----- Février/ Avril 2022 : assemblage + tests au LPNHE -----

----- Avril 2022 : **DÉBUT intégration au CERN** ---------- Automne 2022 : Tests en faisceau au CERN - 1<sup>ère</sup> ½ TPC ---------- Automne 2022 → Début 2023 : **SUITE et FIN intégration au CERN**

des 3 autres ½ TPCFinalisation du développement soft DAQ-MIDAS

Migration du code serveur de commandes pour

la TDCM en version Linux embarqué----- Printemps 2023 : **commissioning** des 2 x TPC à J-Parc -----

Projet d' *Upgrade du détecteur ND280 / T2K-II*

Set-up au CERN-Genève

avril 2022

Photo Japon ?