# Time Distribution System Proposal for the Hyper-Kamiokande Experiment's Far Detector

# LPNHE Paris - INFN Roma - CEA IRFU Saclay $\label{eq:may-8} \text{May 8, 2022}$

# Contents

| In | ntroduction                                              | 1  |

|----|----------------------------------------------------------|----|

| 1  | Experiment's Requirements                                | 4  |

| 2  | Clock Generation and UTC                                 | 6  |

|    | 2.1 General Concept                                      | 6  |

|    | 2.2 Atomic Clock and time reference point                | 7  |

|    | 2.3 Global Navigation Satellite System (GNSS)            |    |

|    | 2.4 Reliability, Redundancy and Risk Mitigation          |    |

|    | 2.5 Instruments Physical Characteristics                 |    |

| 3  | First Distribution Stage                                 | 15 |

|    | 3.1 Function and principles                              | 15 |

|    | 3.2 Proposed hardware architecture                       | 15 |

|    | 3.3 Embedded firmware and software                       |    |

|    | 3.4 Prototyping                                          | 17 |

|    | 3.4.1 First Distributor Stage demonstrator               |    |

| 4  | Second Distribution Stage                                | 20 |

|    | 4.1 Introduction                                         | 20 |

|    | 4.2 Clock and Data Recovery                              | 20 |

|    | 4.2.1 Experimental tests                                 |    |

|    | 4.2.2 First Integration Test                             |    |

|    | 4.3 Time Distribution Module (TDM)                       |    |

|    | 4.4 Time Distribution Data Format                        |    |

| 5  | Time Distribution Endpoint                               | 29 |

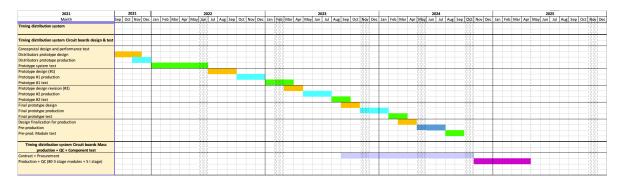

| 6  | Estimation of Cost, Human Resources and Project Schedule | 30 |

|    | 6.1 Cost Estimation                                      | 30 |

|    | 6.2 Estimated human resources                            |    |

|    | 6.3 Schedule                                             |    |

| A  | CGGTTS file example                                      | 33 |

# Introduction

A crucial information to reconstruct the Cherenkov ring(s) associated with an event in the Hyper-Kamiokande experiment is the arrival time of the light emitted in water on the detector's PMTs. To

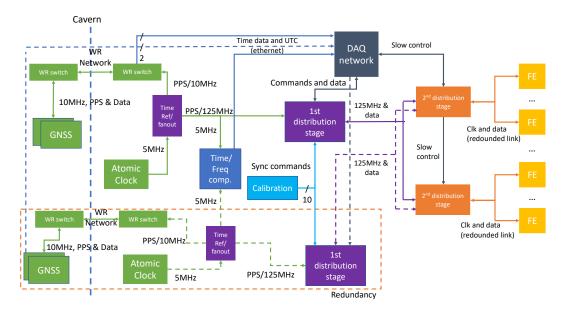

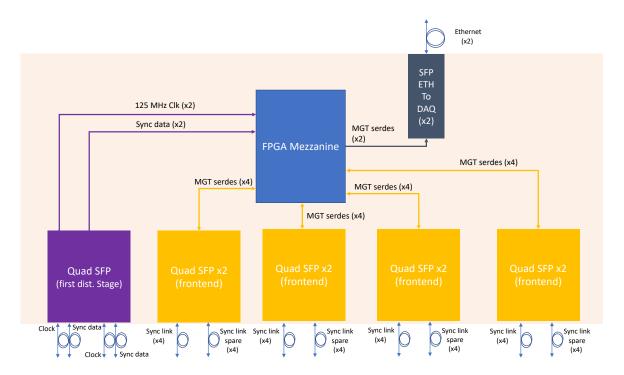

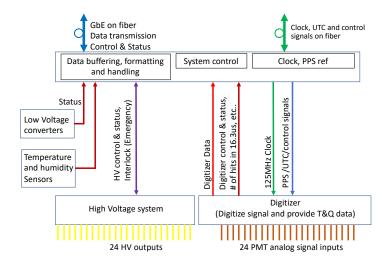

Figure 1: The proposed time distribution block scheme. The green boxes are part of the clock generation and UTC tagging described in section 2. The purple elements constitute the first distribution stage described in section 3, the orange ones are for the second distribution stage described in section 4, while the yellow ones refer to the time distribution endpoint, part of the front-end, described in section 5.

achieve this goal a reference time must be established and distributed to all the PMT front-end (FE) modules readout electronics.

The time synchronisation precision is directly related to the event's reconstruction accuracy; therefore, great care must be devoted to this task to control all sources of errors and inaccuracies. The Hyper-Kamiokande experiment requires a time distribution jitter smaller than 100 ps RMS and the clock skew between front-end boards to be constant over any power-on and reset.

The time tag of each particle interaction needs to be in a format that allows its correlation with data collected by other experiments worldwide; for this reason the generated local time base has to be associated with the Coordinated Universal Time (UTC) with an accuracy better than 100 ns. This absolute time tagging will also be used to identify the events generated in the detector by the particles sent from the J-PARC accelerator. Along with the time synchronisation some "critical information" like slow control data have to be transmitted by this subsystem hence a 100 Mbps or greater bandwidth bidirectional data channel must be provided.

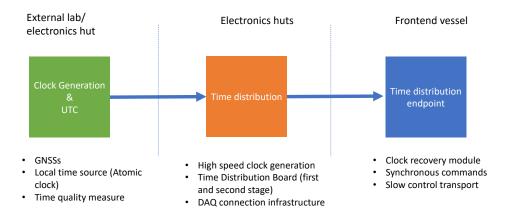

The full block scheme of the proposed system is depicted in Fig. 1 and it can be subdivided into 3 main parts, as shown in the conceptual diagram reported in Figure 2 which highlights also its sub-constituents and their envisioned positions.

To guarantee the most stable and precise reference, the local time base originates in an atomic clock working in free running mode. It generates a 5 MHz frequency that is sent to a time reference fan-out board. Here the 125 MHz reference clock is generated and sent to the distribution network along with a PPS (Pulse Per Second) "counted" using the 5 MHz time base. The 125 MHz frequency is distributed over different branches by means of time distribution modules and delivered to all the leaves represented by the FE modules using the so-called Time Distribution Endpoints or TDE. A 10 MHz clock is also generated and sent to a GNSS (Global Navigation Satellite System) along with the PPS. Here the time distance between the local PPS, the GNSS time and, in turn, a UTC prediction is measured and sent to the data acquisition computer infrastructure via Ethernet protocol where it is used to convert the event's local time tag to it.

In this document the terms "GNSS time", the "UTC prediction" associated to it and "UTC" itself will be used interchangeably even though the first and second terms are less precise and could differ from the third one by an a-posteriori applied correction. It is worth highlighting here the difference between the various time scales and their dissemination to build the context in which the time measurements

Figure 2: The block scheme that describes the 3 main time distribution sub-systems.

in Hyper-Kamiokande will be made. UTC is an International time scale computed monthly by the BIPM (Bureau International des Poids et Mesures) [1] following three steps. First, an ensemble of commercial atomic clocks spread in different countries produce their definition of the atomic time scale which average is called Echelle Atomique Libre (EAL)). The EAL, steered in frequency on a group of Primary and Secondary Frequency Standards, realises the definition of the SI second (which is called Temps Atomique International (TAI)). Finally, the TAI becomes UTC by adding Leap Seconds to match the rotation of the Earth. The UTC is a "conventional" time scale calculated a-posteriori and made available by BIPM in its monthly Circular T [2]. National Metrology Institutes (MI) or Designated Laboratories (DL) produce physical realizations of UTC, namely UTC(k), where "k" is an acronym or a label for each given country/organization. In the Circular T the offsets between UTC and each UTC(k) are published.

On the other hand, each GNSS constellation has its own time scale, that is generically called "GNSS Time" (GPS Time, Galileo System Time (GST) and so on). In addition, the GNSS operators generate a UTC prediction, either internally or based on some existing UTC(k), to relate their internal time scale to the rest of the world. Some parameters included in the GNSS navigation messages allow to make this correlation hence associating any ground user clock to this prediction of UTC. Circular T section 4 contains "Relations of UTC and TAI with prediction of UTC(k) disseminated by GNSS" but this is currently only referred to GPS and GLONASS. This Section is about to be transformed to include similar information from other GNSS together with some uncertainty estimation (under discussions inside formal Working Groups). At present time there is not yet a formal wording for such prediction of UTC broadcast by GNSS.

This document describes the R&D program carried out by LPNHE, INFN, and IRFU to select the most suited technologies to meet the experiment's requirements summarising all the efforts made over the last 2 years, and presents the envisioned solution for the Hyper-Kamiokande far detector.

The document starts by presenting the experimental requirements and then describes the proposed design in 3 main parts, following the block scheme reported in Figure 2. Section 2 describes how the HK far detector clock is generated and accorded to UTC. Details about the different instruments used (green boxes in Figure 1), their tested performances and calibration are highlighted with the strategy to mitigate failures and enhance the system reliability. Section 3 is devoted to the first part of the clock distribution network, receiving the base cadence, generating the main reference clock and distributing it to the second layer along with synchronous commands. This part corresponds to the purple boxes in Figure 1. As visible in the block diagram, it is connected to the data acquisition network (gray box) and the calibration system. In section 4 the second part of the distribution network (orange boxes of Figure 1) is described. It receives clock and data from the first distribution stage and passes them to the front-ends via optical fibers. On this bidirectional link the FEs move some slow control data to the DAQ. This is the reason why the second distribution stage is connected to the data acquisition network via standard Ethernet links. Specific reliability considerations designed to prevent synchronous link interruptions are described at the end of this section. Some preliminary results devoted to test the clock and data transmission concept are presented as well. Section 5 contains the description of the time

distribution elements included in the front-end module to handle the synchronous data and clock and broadcast them to all the concerned modules. This part is implemented as a logic element integrated on the FE electronics depicted as the yellow boxes in the diagram of Figure 1. The document ends with a section that describes our estimation of the cost and human resources required to produce the system along with a detailed schedule.

# 1 Experiment's Requirements

The full list of experiment's requirements relative to the time distribution system is reported below:

- 1. A high-speed reference clock must be distributed to all the FEs with a jitter of 100 ps RMS (measured on 10.000 cycles). The clock stability must be, at minimum, of 10<sup>-11</sup> @ 1 s and 10<sup>-12</sup> @100 s. At the present time, the selected frequency is 125 MHz as it is suited for the QTC's and discrete digitizer solutions, but it could be changed to a different frequency in case the selected digitizer would need it. The proposed method to fulfill this requirements has been presented in section 4.

- 2. The distributed clock absolute time difference between any two FEs must be kept within 10 ns. This means that the different cable lengths, due to the different FE positions in the detector, must be compensated by the time distribution system. The requirement is then met if any two FEs receive the synchronous data stream within 10 ns (according to the measured cable delay) and each of them has a jitter smaller than 100 ps on the distributed reference clock (see requirement 1). An online phase difference measurement can be performed only if it doesn't require any extra hardware. An online phase compensation is not required. The clock distribution description is in section 4.

- 3. The time distribution system must provide a synchronous and phase deterministic communication link to each FE with a bandwidth equal or greater than 100 Mbps. The link from the FEs to the time distribution and DAQ doesn't need to be phase deterministic. The proposed protocol description is presented in section 4.

- 4. The time distribution system must provide a TDCs synchronous reset every N periods of the 125 MHz distributed reference clock to all the FEs. For the discrete and QTC solution N is 2048, that corresponds to a reset frequency of 61.03 kHz. For the HKROC solution N is 15360, that corresponds to a reset frequency of 8.13 kHz. As for the first requirement, also this aspect will be re-evaluated once the digitiszer selection will be made. The method used to generate this signal is discussed in section 3.

- 5. A coarse counter is needed to extend the TDC's range. This coarse counter must be common to all the FEs and generated from a single point. This counter must be 32-bit long incremented at steps of N\*8 ns (see requirement 4). The implications of the counter wrapping are dealt outside of the time distribution system. Each FE will count the TDC resets and will check the received global coarse counter against that. The way the TDC reset is formed and distributed is presented in sections 3 and 4.

- 6. Two kinds of synchronous commands must be issued from various far detector's subsystems to all the FEs via the time distribution system. The first is a so-called acquisition veto. The time distribution system must provide an interface to receive this command from up to 10 different sources and send it embedded in the sync packet in the trigger field (see requirement 7). The described transport method implies that the time difference between its reception at time distribution system and its broadcast to FEs can be as high as 10's of microseconds since it could be issued in the next available sync packet (see requirement 4). The second kind of synchronous command is an emergency stop issued by one entity. Its interface is still to be decided. The section that handles the synchronous commands is presented in section 3.

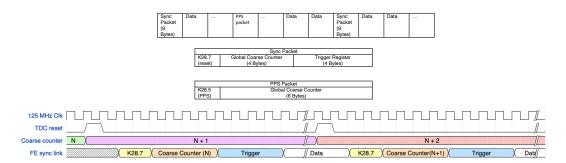

- 7. The TDC reset, the global coarse counter and the trigger register must be sent periodically in the same order forming a so-called synchronization packet. It is described in section 4.

- 8. The 1 Pulse Per Second (PPS) and a time code must be provided by the time distribution system to the multi PMT (mPMT) along with the synchronous packet. The PPS will be dispatched in a time deterministic manner to all the FEs as soon as it is generated. The method used is presented in section 4.

- 9. The local time base used to generate the distributed reference clock must be accorded to UTC within 100 ns at least. An accord is also required to the J-PARC time base. All the details of the local time base and the GNSS system are given in section 2.

- 10. The GNSS system (composed from 2 GNSS receivers, at least) must be monitored using a local clock to detect any possible time jump.

# 2 Clock Generation and UTC

# 2.1 General Concept

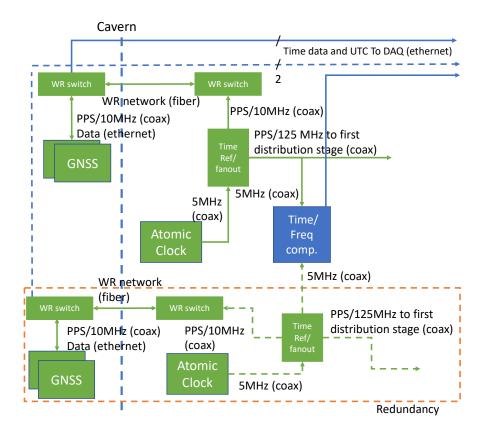

Figure 3: Detailed scheme of the clock generation section. The green boxes represent the clock and time generation instruments, the dashed orange box contains the hot spare clock generation chain while the blue box represents the subsystem used to monitor the time distance between the main and spare system.

The base clock represents the foundation of the cadence delivered to all the detector electronics elements; therefore it must be very stable and precise to guarantee, at each end-point, a signal that still meets all the requirements in spite of the deterioration due to the distribution process. To achieve this goal, many elements must work together as shown in the block scheme of Figure 3. As visible from it, the time origin is the atomic clock which delivers a stable 5 MHz clock cadence to the time reference/fanout element, physically embedded in the first distribution stage as described in section 3. Here the basic cadence is used to build all the needed clocks. The 125 MHz reference and the PPS (in accordance with requirements number 1 and 8) are sent to the first distribution stage while a 10 MHz frequency and a PPS are broadcast to the GNSS receivers via the White Rabbit which guarantees synchronicity and phase alignment over long distances. The Navigation satellite systems use this two periodic signals to measure the time distance between the Hyper-Kamiokande local time and the GNSS time giving a projection to the UTC and then fulfill the requirement 9. This information travels over the Ethernet link established by the WR network to the data acquisition system which converts the local time tag, recorded by the front-end, to UTC. A second identical chain is proposed to enhance the total system reliability. The time reference/fanout entity serves also as a reference point for calibration and to check the time distance between the main and spare clock generation blocks.

This section describes in detail all the elements of the proposed scheme, their interconnections and the characterization tests already performed on them. Reliability and risk mitigation considerations are given at the end of the section.

## 2.2 Atomic Clock and time reference point

The cadence generator technology that guarantees the best performance is the atomic clock, but, currently, on the market there is a vast range of instruments with different noise levels, stability characteristics and prices. The two candidate technologies proposed for Hyper-Kamiokande are the Passive Hydrogen Maser (PHM) (microwave amplification by stimulated emission of radiation) and the Rubidium (Rb) standard. The models under consideration are the rubidium clock FS725 from Stanford Research (SRS) [3] and the T4Science pHMaser 1008 [4]. Both output a PPS, a 5 MHz and a 10 MHz and, the selected rubidium clock, has also a PPS input used as a reference for its internal PLL. In other words, the clock's output frequencies can be periodically calibrated using the PPS input. This option could be used to mitigate the instrument's drift measured at  $10^{-11}$  over 1000 s. The proposed PHM doesn't have this feature.

The main characteristics of the two devices are summarised in Table  $1^1$ .

| Technology          | pHMaser 1008                             | SRS SF725                          |

|---------------------|------------------------------------------|------------------------------------|

| Frequency stability | $\sim 5 \times 10^{-13} \ @ 1 \text{ s}$ | $\sim 2 \times 10^{-11} @ 1 s$     |

| Equivalent jitter   | 0.5  ps                                  | 2 ps                               |

| Frequency drift     | $\sim 5 \times 10^{-15} @ 1 day$         | $\sim 1.6 \times 10^{-12} @ 1 day$ |

Table 1: Passive Hydrogen Maser pHMaser 1008 and Rubidium atomic clock SRS SF725 characteristics.

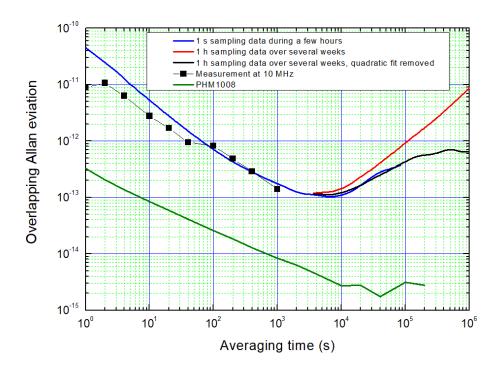

Atomic clocks performance As evident from the Table 1, the Passive Hydrogen Maser shows much better performance that goes up to 2 orders of magnitude with respect to the Rubidium, both at short and long timescales. This values have been verified in an extensive test campaign conducted in collaboration with the colleagues of the SYRTE laboratory, part of the Observatoire de Paris (OP) [5], one of the institutes that concur to the UTC definition. A more visual comparison involving Allan Standard Deviation (ASD) [6] can be found in Figure 4. The time at which the curves reach the minimum indicates the time at which long-term frequency drifts become dominant over the short-time fluctuations. The difference in performance of 2 orders of magnitudes between the PHM and Rb technologies are evident also in this plot where the green line is constantly and consistently below the others.

Time base system configuration Considering the far detector's need to synchronize all the frontends in a very tight manner, we plan to use the atomic clocks in the so-called "free-running" mode, so without steering the output using a PPS input coming from a GNSS receiver. Instead, the 5 MHz from the atomic clock is sent to the entity that generates the FE reference clock. The same entity also counts the number of cycles to reach one second and generates a local PPS. It then becomes the time distribution reference point as represented in Figure 3. It serves also as fan-out providing a very stable 10 MHz frequency and the PPS to the GNSS receivers to phase align their outputs overriding the instruments internal oscillators. As described in the next section, this logical entity will be integrated in the first distribution stage board for practical reasons. The Septentrio GNSS receivers measure the time distance between the PPS input and UTC. This information is then sent to the DAQ via Ethernet links and is used to convert the local time tag to UTC. We prefer this scheme to the one where the atomic clock is steered by the GNSS PPS for, at least, 3 reasons:

- The free-running scheme gives the control of the atomic clock drift while, in the other mode, the atomic clock's internal PLL follows the GNSS and won't be as precise as a post-processing correction. Moreover, according to the manual [3], the steering procedure is mainly intended for the instrument calibration.

- working in free-running mode allows also to avoid corrections on the atomic clock output frequencies that could bring possible errors due to GNSS receiver malfunction or satellites data misconfiguration. Configuring the atomic clock in steering mode could bring clock jump or excessive jitter on the output cadence if the PPS input from the GNSS receiver would jump out of the internal PLL adjustment range.

<sup>&</sup>lt;sup>1</sup>The Passive Hydrogen Maser also provides a 100 MHz clock output.

Figure 4: Allan Standard Deviation of the rubidium atomic clock calculated using different sampling times compared with the Passive Hydrogen Maser (green curve).

- The free-running clock configuration facilitates the use of multiple GNSS receivers giving the possibility to select the UTC time reference to use (see below).

It is also worth mentioning that any atomic clock drift, no matter its value, will affect all the detector's FEs equally then it will be invisible on the relative time tagging.

The conversion values to transform the local time tag into UTC (and fulfill the requirement 9) will be calculated periodically by the GNSS receivers and sent to the data acquisition system via Ethernet in a CGGTTS (Common Generic GNSS Time Transfer Standard) file [7]. The validity period of each conversion factor depends on the atomic clock performance and in particular on its drift, evaluated comparing its Allan standard deviation to the one of the GNSS receivers system. We have already performed this measurement, thanks to our SYRTE colleagues, on the purchased SF725 rubidium clock and the corresponding plot is reported in Figure 5. As visible from the purple curve, obtained comparing our atomic clock to the SYRTE UTC implementation called UTC(OP), it starts showing an evident drift at about 10<sup>4</sup> seconds after the GNSS alignment and this is the time when a new conversion value would be needed. A similar analysis will be done when the already ordered PHM atomic clock will arrive at our laboratory but, according to the data-sheet and previous experiences, we are expecting to see a drift at a day scale. If this result will be confirmed, it would mean that the local PPS to UTC conversion factor could be updated only once per day.

To compute the conversion factor we are planning to use a time transfer method based on the information included in the CGGTTS file produced by the GNSS receivers. According to the standard, each satellite receiver calculates the time distance between the local PPS and the GNSS system time at intervals of 16 minutes in which the measures are performed every 30 seconds for a total time of 13 minutes. The choice of these specific numbers has historical reasons and comes from the time when a receiver needed 13 minutes to acquire the full satellite navigation message and extra 3 minutes were foreseen to track the following scheduled satellite. In spite of an almost 20% inefficiency, the CGGTTS standard still uses these numbers to guarantee retro-compatibility with older systems. Every GNSS receiver then performs some corrections to take into account the signal's distortion due to the propagation in the atmosphere and the internal equipment delays, it computes a linear fit on the 26 acquired values and gives a time distance using the fit estimation at the 13 minutes midpoint. The

Figure 5: Allan standard deviation comparison between the SRS FS725 rubidium atomic clock and the GPS and GST (Galileo Standard Time) to the UTC definition of the Observatoire de Paris (UTC(OP)).

data will be further processed with a specific algorithm to compute the conversion factor to the data acquisition system. An example of CGGTTS file and some other details are given in the appendix A.

# 2.3 Global Navigation Satellite System (GNSS)

As already mentioned, the GNSS will be used to correlate the local time base with the universal coordinated time, or one of its implementations, by means of the information included in its data stream. To guarantee an accuracy at the level of 100 ns or better (as reported in the requirement number 9), many parameters must be taken under control and corrected, if needed. Some of them are related to the satellites, like e.g. the position of each transmitter at any given time. This implies that each satellite's orbit must be known with a precision that sometimes goes beyond the one included in the data stream. Some other elements are relative to the receiver and concern the electromagnetic signal that reaches the antenna, the interference and the reflection to which it is subjected. To improve the first kind of uncertainty, correction algorithms will be implemented on the received data by means of a computer infrastructure that elaborates information coming from the UTC consortium. This consortium is composed from many laboratories spread around the world working together on the UTC definition. As part of their duty, they publish a weekly report that includes parameters needed to reconstruct the universal time at the "state of the art" precision. The uncertainty related to the local equipment can be mitigated performing an accurate calibration of the receiver, the associated antenna and the connection cable against a cadence generated by a so-called group 1 laboratory, like SYRTE, able to guarantee a resolution below 5 ns.

After an extensive R&D study, the Septentrio PolaRx5 multi-frequency multi-constellation timing/reference receiver associated with a multi-frequency B3E6 choke ring antenna [8, 9] have been selected. A calibration procedure has been conducted on the first purchased set, presented in Figure 6, and the results are reported in the tables below:

Figure 6: The Septentrio PolaRx5 GNSS receiver and the associated antenna.

| Institute | Equipment status  | Measure MJD   | Receiver type           | BIPM code | RINEX name |

|-----------|-------------------|---------------|-------------------------|-----------|------------|

| OP        | Traveling         | NC-NC         | Septentrio<br>PolaRx5TR | LPN1      | LPN1       |

| OP        | Group 1 reference | 59508 - 59514 | Septentrio<br>PolaRx5TR | OP73      | OP73       |

Table 2: GNSS calibration equipment description.

| Receiver | Reference | Measure's | REFDLY | CABDLY | P1 DLY | TDEV  | P2 DLY | TDEV  |

|----------|-----------|-----------|--------|--------|--------|-------|--------|-------|

|          |           | MJD       |        |        |        |       |        |       |

| OP73     | Ref       | 59508 -   | 85.2   | 129.6  | 29.500 | NC    | 26.30  | NC    |

|          |           | 59514     |        |        |        |       |        |       |

| LPN1 1   | OP73      | 59508 -   | 88.3   | 127.1  | 25.832 | 0.024 | 22.871 | 0.022 |

|          |           | 59514     |        |        |        |       |        |       |

Table 3: GPS calibration table. All values are in ns.

| Receiver | Reference | Measure's | REFDLY | CABDLY | E1 DLY | TDEV  | E5a    | TDEV  |

|----------|-----------|-----------|--------|--------|--------|-------|--------|-------|

|          |           | MJD       |        |        |        |       | DLY    |       |

| OP73     | Ref       | 59508 -   | 85.2   | 129.6  | 31.700 | NC    | 31.300 | NC    |

|          |           | 59514     |        |        |        |       |        |       |

| LPN1 1   | OP73      | 59508 -   | 88.3   | 127.1  | 28.242 | 0.040 | 25.431 | 0.034 |

|          |           | 59514     |        |        |        |       |        |       |

Table 4: Galileo calibration table. All values are in ns.

The presented calibration will be done on all the used receivers before the deployment and the measured delay values will be stored in their configuration system. The values will be checked every 5 years using a portable device called "travelling station". This mobile station will be compared against

all the HK's GNSS receivers and with the one at the UTC consortium lab to align all the systems without moving them.

To achieve the best performances and use multiple devices together, each GNSS receiver will be provided with a 10 MHz and a PPS input cadences generated from the atomic clock. The 10 MHz frequency will be used to override the internal receiver's oscillator, as it has a more stable and precise clock for the internal logic. The PPS input will be used at start-up to synchronise multiple receivers outputs in order to use them together and switch from one to the other in case of malfunctions. The receiver and antenna position are also crucial for the UTC accuracy because a good data reception would allow to reduce the data post-processing and to reach a greater precision. The number of "seen" satellites has a great impact in terms of UTC definition reliability and precision. While it is true that even one satellite can give a precise UTC reference (once the antenna position is known with enough precision) in this configuration the system would completely depend on that specific satellite and changing it would bring jumps in the UTC reference. Moreover, correcting the received data would be more difficult and less precise. The minimum number of satellites that we are envisioning to see is 5 at any given time. They could belong to different constellations like the American GPS (Global Positioning System), the European Galileo and the Japanese QZSS (Quasi-Zenith Satellite System) and we would provide algorithms to combine them. The basic idea is to have a time reference from each constellation and, from them, get the UTC reference calculating the time distance between them.

GNSS-atomic clock interconnection topology To minimise the local time base uncertainty, the atomic clocks will be placed close to the far detector's electronics in a cavern where the satellites signal doesn't arrive. The GNSS equipment will be placed at the cavern's entrance, several kilometers away in a position that maximises its reception quality, then the two elements must exchange data over a very long optical fiber without loosing their synchronicity. The CERN White Rabbit technology will be used to build this link.

White Rabbit (WR) is the name of a collaborative project including CERN, GSI Helmholtz Centre for Heavy Ion Research and other partners from universities and industry to develop a fully deterministic Ethernet-based network for general purpose data transfer and sub-nanosecond accuracy time transfer. Its initial use was as a timing distribution network for control and data acquisition of the accelerator sites at CERN as well as in GSI's Facility for Antiproton and Ion Research (FAIR) project. The hardware designs and the source code are publicly available [10].

This protocol is based on the clock and data recovery so one optical fiber can be used to distribute the master clock and for a bi-directional communication link.

White Rabbit uses Synchronous Ethernet (SyncE) to achieve sub nanosecond synchronisation and IEEE 1588 Precision Time Protocol (PTP) to communicate time. The phase difference between the master and the slave is measured using a specific module based on phase frequency detectors [11]. A two-way exchange of the Precision Time Protocol synchronisation messages allows precise adjustment of clock phase and offset. The link delay is known precisely via accurate hardware timestamps and the calculation of delay asymmetry. The measurements results are computed to align the master and the slave clocks and remove skew due to the cabling and thermal effects.

The White Rabbit can be considered as a sort of an off-the-shelf solution since the hardware can be bought from companies that produce and sell WR compliant electronics devices.

This solution is very convenient because, over a single fiber, it is possible to transport the signals needed to the GNSS receivers (PPS and 10 MHz clock) and use the data link to transport the time information received from the satellites via Ethernet protocol. The planned topology consists in a White Rabbit switch configured as Grand Master placed close to the atomic clock inside the cavern that receives the PPS and 10 MHz clock from the fan-out reference board. It embeds the two frequencies into the data stream and sends them over a mono-mode fiber laid down in the entrance tunnel up to the building where the GNSS receivers are located. There, a second White Rabbit switch configured as a slave, outputs a PPS and 10 MHz clock replica phase aligned to the Grand Master. Ethernet cable connected from the WR switches to the DAQ network and to the GNSS receivers will transport the data needed to convert the local time tags to UTC. This last part is possible due to the White Rabbit protocol compatibility with the standard Ethernet.

The events generated by the J-PARC accelerator's particles' packets must be identified and separated from the noise and astrophysical events. For this purpose, a specific acquisition's window must be opened for each event at the far detector's site however a direct "trigger" signal can't be sent due

Figure 7: The White Rabbit test bench composed by two custom boards developed in the INFN test bench of Rome 1.

to the distance between them. The most effective solution to solve this problem is to guarantee that the two sites' time bases differ from a known quantity then the accelerator's site can "inform" the far detector about the time at which a particles' packet has been sent trusting that the far detector data acquisition system can correlate that time to its own.

The best way to measure the time distance between the two sites is the so-called "common view" technique possible when the two sites are both equipped with a GNSS receiver locked on the same satellites. This method allows a direct comparison between the two time bases following the time transfer method reported here [12].

An alternative solution consists in adopting the same common view method separately between each station and the Japanese UTC consortium lab: NICT. This method can be considered as "indirect" since it implies that both the far detector and the J-PARC time bases are measured against the so-called UTC(NICT). By knowing the time distance of each site to it, the time distance between the two experiment's time bases could be computed. This method would bring a slightly higher error but brings the advantage that both sites are related to an UTC implementation. In principle, both methods could be implemented at the same time and could be used as a crosscheck.

A data collection campaign will be performed, with a portable GNSS receiver, at the far detector site well ahead of the system deployment. This test will be useful to establish the best final antenna position and to check the number of common satellites available. The collected data will determine also the entity of the post-processing needed to achieve the experiment's requirements. The portable equipment, composed from the same elements installed at far detector site, will then be used as a "travelling station" to check the calibration parameter of the resident receivers during the regular data acquisition period.

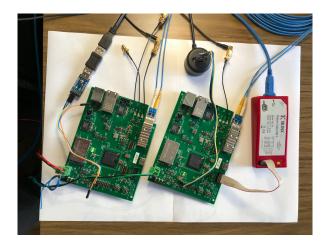

White Rabbit experimental tests A test campaign has been carried out to validate the White Rabbit as a viable solution to bring the base cadences from the atomic clock to the GNSS receivers. The concept has been tested using a couple of custom boards realised by the INFN branch of Rome 1 and presented in Figure 7. The connection scheme consists of two boards, equipped with Xilinx Spartan VI FPGA, connected with an optical fiber (the blue cable) and the transmitted and received clocks are extracted by means of black coaxial cables. The data bandwidth has been measured compliant to the Gigabit Ethernet standard, moreover, connecting one board to a computer, it has been verified that the data packets are correctly exchanged while the time information is dropped.

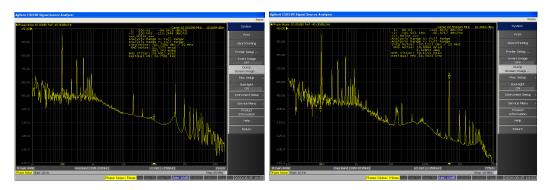

The clock characterisation has been carried out in two steps. First, the PPS provided by the two WR nodes has been verified to be stable over different resets and its total jitter on the RX side has been measured at 17.9 ps. Then the jitter on reconstructed clock has been measured in the frequency domain and is reported in the plot of Figure 8. The phase noise analysis starting form 10 Hz shows a jitter as low as 8 ps RMS while at frequencies below that threshold there is a great quantity of noise. If the same measurement is performed starting form 1 Hz the total jitter rises to 67 ps and there are

Figure 8: Frequency domain jitter measurements performed on the reconstructed clock using the White Rabbit scheme. On the left the phase noise analysis including frequencies as low as 1 Hz. On the right the same measurement starting at 10 Hz.

some hints that this additional noise is generated by the local oscillator on the transmission side.

# 2.4 Reliability, Redundancy and Risk Mitigation

To achieve the best performance and enhance reliability, 2 GNSS receivers connected to the same antenna and sharing the same PPS input, will be installed and data from both instruments will be sent to the data acquisition system via Ethernet. This information will be used to constantly monitor the equipment and guarantee that at least 1 receiver will be operational at any time in accordance to the requirement 10. To be more specific the DAQ will receive the CGGTTS files of both devices and will analyse them. In case of normal behaviour, they will provide the same time distance between the local PPS and the GNSS time while, in case of malfunctions, one will have a different offset.

To avoid single point of failure, the entire chain of atomic clock, GNSS receivers, time distribution reference point and the first distribution stage will be duplicated in a hot spare configuration. This means that the second chain will be always active and its 5 MHz time base will be constantly compared with the main one. This constant time comparison is assured using the Keysigth 53230A universal time/frequency counter [13] which measures the time distance between two signals with a resolution of 20 ps and sends it over Ethernet to the data acquisition system. This scheme provides a constant check of the HK time reference accuracy and an alternative, ready-to-use reference in case of malfunction of the main one. Tracking the time distance between the main and spare time references will give enough information to merge the data tagged with the two different time bases. To further enhance the system reliability, a third atomic clock will be acquired and used as a cold spare. It will be safely stored at the far detector site, according to the vendor recommendations, operated and checked regularly and thus ready to be used in case the main or the hot-cold one needs a long period of maintenance. The system maintenance will be addressed with a scheduled plan of interventions designed to change the parts before they arrive at the end of life. The plan will be realized using the information coming from the instruments producers and envisions to change the "physical package" of the atomic clocks or the entire instrument within ten years from the start of operation. We are also considering to replace the GNSS receivers approximately on the same time scale or before the end of producer's support. The switch to new devices will be staged to avoid any possible perturbation to the HK time base.

A risk mitigation strategy has been developed on the most crucial part of the time base generation scheme i.e. the atomic clock. As extensively discussed above, two technologies have been evaluated and, while the passive hydrogen maser clock shows much better performance than the rubidium, the second is still capable of delivering a cadence that meets all the experiment's requirements. This consideration, associated to a more affordable cost, makes it a preferable choice for the baseline solution. However, the two instruments will be still tested and compared to get long term performance data and reevaluated in the future. The Hyper-Kamiokande's clock generation scheme has been designed in such a way that the PHM clock could be used instead of the rubidium on the experiment without requiring any major system rework, if this need will be identified.

# 2.5 Instruments Physical Characteristics

The clock generation chain instruments physical and electrical characteristics are summarised in Table 5. The inventory as of March 2022 is also reported.

| Instrument                               | Dimension<br>(WHL or<br>DH) in mm<br>& weight | Power     | Operating<br>Conditions<br>(tempera-<br>ture °C and<br>humidity) | Position                          | Quantity<br>Needed | Available |

|------------------------------------------|-----------------------------------------------|-----------|------------------------------------------------------------------|-----------------------------------|--------------------|-----------|

| Rubidium<br>Atomic<br>Clock SRS<br>FS725 | 220x90x330<br>4 kg                            | 120W@220V | +10/+40<br>5%/95%<br>(non condensing)<br>RH                      | Electronic<br>Huts and<br>storage | 3                  | 1         |

| Septentrio PolaRx5 GNSS receiver         | 140x37x225<br>0.94 kg                         | 5W@220V   | -40/+65<br>5%/95%<br>(non condensing)<br>RH                      | Radon Hut                         | 4                  | 1         |

| Septentrio<br>B3E6<br>antenna            | 376x350<br>5 kg                               | NA        | -55/+85                                                          | Radon Hut<br>Roof                 | 2                  | 1         |

| Keysight time/Freq comp.                 | 212x88x272<br>4 kg                            | 90W@220V  | 0/+55                                                            | Electronics<br>Hut                | 2                  | 1         |

| White Rabbit switch                      | 446x44x222<br>3 kg                            | 80W@220V  | -10/+50<br>5%/95%<br>(non condensing)<br>RH                      | Electronic Huts and storage       | 5                  | 1         |

Table 5: Clock Generation and UTC instruments physical characteristics

# 3 First Distribution Stage

## 3.1 Function and principles

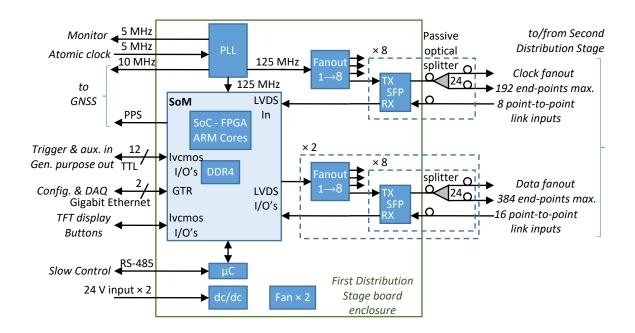

The main function of the First Distribution Stage (FDS) is to distribute with minimal skew and jitter a reference clock at the desired selected frequency to the Second Distribution Stage (SDS) which then fans out the reference clock to all front-ends, underwater. The variations of clock skew at any endpoint must be less than 100 ps during operation and after system restart. The master reference clock is provided to the FDS by an atomic clock at 5 MHz. It is scaled up in frequency to the desired value, 125 MHz in the current plan, by an appropriate clock synthesizer. In addition to the reference clock, the FDS must generate the required synchronization information for the front-ends: a periodic TDC reset signal with an associated coarse timestamp counter, and a 1PPS signal accompanied by a date code. The latency of synchronous signal distribution is required to be accurate to one period of the reference clock (i.e. 8 ns at 125 MHz). The FDS also has to provide a 10 MHz reference clock and a 1PPS signal for use on the GNSS receiver side. The FDS requires a certain number of user inputs for the fanout of external synchronous and asynchronous signals: a veto signal for the data acquisition, an emergency stop for high voltage sources, and possibly other ancillary signals. If this does not add too much complexity, the FDS may monitor the slow variations of delay of all, or a subset, of its transmission links, but it is not required to compensate for these variations. The FDS is housed in an electronic hut, outside of the water tank. Although reliability is a concern, this equipment remains accessible for replacement in case of failure.

The basic principle of operation of the FDS is to perform the distribution of clock and synchronization messages from their respective sources using a pair of commercial fanout chips driving the transmitter side of an array of optical transceivers, and accomplish the final expansion to the required number of end-points using passive optical splitters. The baseline scheme relies on separate physical media for clock and data: a first set of optical fibers distributes the pure clock, and a second set is used to broadcast serially encoded synchronization messages. Alternatively, other schemes based on a common media may be supported: clock embedded in serial data (using a CDR technique at the receiver end), and serial data carried over a modulated clock [14]. The FDS uses entirely commercial components, including an off-the-shelf System-on-Module (SoM) based on an FPGA with embedded processor cores.

## 3.2 Proposed hardware architecture

The block diagram of the proposed hardware architecture for the FDS is depicted in Fig. 9. The central part is a commercial SoM. The currently selected family of products is the TE-80x from Trenz [15] equipped with a System-on-Chip (SoC), Xilinx ZynqUltraScale+ (ZU2 to ZU4). This device features two multi-core ARM processors, a large array of programmable logic resources, over 250 user defined I/O pins, and 4 high-speed GTR serial transceivers. The SoC handles all the logic functions of the FDS with the assistance of external hardware. Reference clock frequency multiplication is accomplished by a dedicated PLL. The selected part is the AD9545 from Analog Devices [16]. This state-of-the-art clock synchronizer and jitter cleaner provides leading edge performance and features several characteristics that are not always found on competitor parts, e.g. zero-delay mode, sophisticated temperature compensation based on a digital filter, and more. The 5 MHz reference clock from the atomic clock is fed to one of the inputs of the AD9545. Outputs generate the 125 MHz reference clock to be distributed, a 10 MHz reference clock for the GNSS receiver and two jitter filtered copies of the 5 MHz input clock.

The broadcast of the reference clock and messages to the SDS takes places in two steps: a first expansion of signals, by a factor 8, is accomplished in the electrical domain by a pair of commercial PECL fanout chips, e.g. Texas Instruments CDCLVP1208. After the electrical to optical conversion performed by two groups of up to eight Small Form factor Pluggable (SFP) optical transceivers, the second, and final, step of clock and serial data signals expansion is done in the optical domain by passive optical splitters. The fanout ratio of the selected optical splitters is 1:24, although 1:16 or 1:32 devices may also be considered. In total, the FDS provides a combined electrical and optical clock and synchronization data expansion factor of up 1:256 in its largest configuration of eight TX SFPs for clock, eight TX SFPs for serial data, and two groups of eight 1:32 optical splitters. Transceivers in the 1310 nm wavelength window and 80 km reach seem adequate devices on the FDS side, while

Figure 9: Block diagram of the first stage clock distributor. The central part is an electronic board based on a commercial System-on-Module, a PLL, fanout chips and SFP transceivers. The PLL receives the 5 MHz reference from the atomic clock and generates the 125 MHz clock to be distributed to the second distribution stage. The programmable logic of the SoM generates the required serial data. Fanout chips connected to SFP transceivers followed by passive optical splitters perform the expansion of the root clock and serial data signals by the desired factor.

more cost-effective 20 km reach counterparts shall be sufficient on the SDS side. According to the datasheet of a typical 80 km reach transceiver, the minimum output optical power of the device is 0 dBm. The quoted attenuation of a 1:32 passive optical splitter is 17.2 dB. The minimum receiver sensitivity of a common 20 km reach SFP transceiver is -23 dBm. The safety margin on the optical budget is therefore around 5.8 dB. This is expected to remain sufficient after taking into account the loss in fiber couplers (0.1 dB per junction) and the attenuation over the length of the fibers themselves which will be very small given the short distance to cover (few tens of meters). Long reach transceivers and passive optical splitters are only usable with single mode optical fibers. Using single mode optical fibers between the FDS and SDS is not an issue because all the connections between these sub-systems are outside of the water and inexpensive fiber couplers can be used. Determinism in terms of latency for the clock distribution path relies essentially on:

- The delay alignment performance of the synthesizer PLL between its different outputs,

- the stability of the input to output delay of a single 1:8 fanout chip and that of SFP transceivers,

- the stability of propagation time through passive optical splitters and all the fiber cabling involved.

By adopting the simplest possible structure and placing the minimum number of elements in the clock distribution chain, it is expected to reach the best achievable stability in terms of latency and the minimum amount of added jitter. The path for synchronous message distribution adopts the same architecture, although it is less critical than the clock path in terms of acceptable skew and jitter. The serial data to be distributed originates from the FPGA logic of the SoC. The serializer primitive of an ordinary differential output pin pair is planned to be used. The maximum supported rate is expected to be 500 Mbps (i.e. 250 Mbps of user data before encoding), which is well within the 1250 Mbps capability of the I/O pins of the target device. The FDS is an asymmetric unit that provides

clock and data broadcast capability from one source to a large number of end-points, but it has only a limited number of point-to-point communication links in the opposite direction: 16 in a minimal implementation, and up to 48 pushing the design to the limits of the number of I/O pins available on the selected SoM. No information is expected to flow from the SDS to the FDS and only a subset of the units that make the SDS have a return path to the FDS (at least one among the units served by the same passive optical splitter in the forward direction). The return path may be used to loop back the received clocks, or possibly transmit serial data from a subset of SDS units to the FDS. The planned rate is 500 Mbps or some sub-multiple of it. On the FDS, each return link uses the RX side of an SFP transceiver and connects to a pair of regular FPGA input pins. For monitoring the stability of the corresponding part of the clock distribution system, the FDS may measure the phase shift between its local reference clock and the clocks that are looped back by the fraction of SDS units that have a return link to the FDS. One of the possible methods for the precise measurement of the phase offset between a reference clock and a synchronous delayed copy is the Digital Dual Mixer Time Difference (DDMDT) technique [17]. This proven method is notably used by White Rabbit.

The FDS logic generates a local 1PPS signal by counting the fixed appropriate number of clock cycles of the generated reference clock (i.e. 125,000,000 for a 125 MHz reference clock). This 1PPS signal is sent to all front-end (accompanied by a time code), and it is also sent to the GNSS receiver along with a 10 MHz clock, synchronous to the reference clock provided by the atomic clock. This information is used on the GNSS side to measure, and periodically record, the delay between the generated 1PPS and the 1PPS synchronous to the UTC obtained from the GNSS receiver. A 5 MHz output is provided to compare the reference clock of the main atomic clock to that of the spare atomic clock. An additional 5 MHz output is available for delay calibration or some other purpose.

The FDS has about 10 TTL level user I/O's for receiving external synchronous signals, one, and possibly two, Gigabit Ethernet ports for control and configuration, a local microcontroller with a RS485 interface for remote supervision, redundant power supply inputs (24 V), two fans, and optionally a small TFT screen and navigation buttons. The FSD is expected to fit in a single 1U 19" rack mountable enclosure. For increased flexibility, part of the functions (e.g. clock multiplication) are housed on a mezzanine card while core components are placed on a motherboard that also receives the SoM. An external, commercial, redundant, power supply unit is used to power the FDS. For system redundancy, the complete FDS is duplicated. If the main FDS fails, the secondary unit takes over. Switching between the two units is however not glitch free and system reconfiguration is expected to take up to few tens of seconds.

#### 3.3 Embedded firmware and software

All the time critical tasks and programmable hardware related functions of the FDS are coded in FPGA logic. Embedded software running on the ARM processor cores of the SoC is used to control system operation and exchange housekeeping data with an external PC and the DAQ over standard Gigabit Ethernet. A small piece of embedded software also runs on the local microcontroller to control fan speed, perform local monitoring and communicate with the control PC over RS485.

# 3.4 Prototyping

#### 3.4.1 First Distributor Stage demonstrator

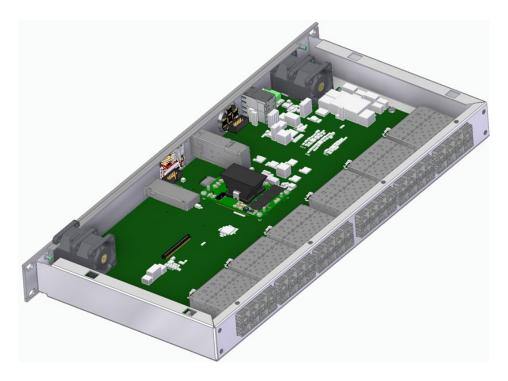

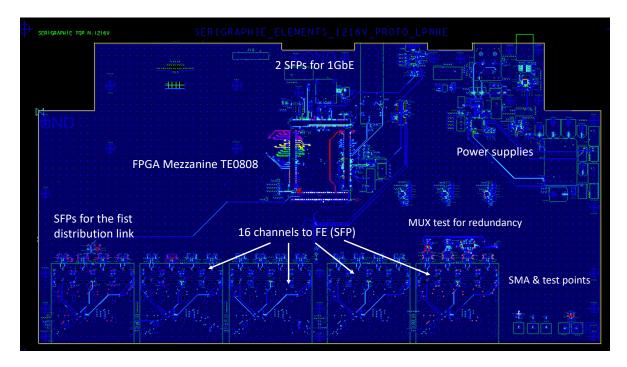

The RDHK clock distributor demonstrator is a unit designed to evaluate several principles and technical options for clock distribution. It is composed of three main elements: a custom made motherboard, a commercial SoM, and a custom made mezzanine card called "CLK\_MEZZ". All these elements, two fans, a small display and a navigation panel fit in a standard 1U 19" enclosure. A 3D image of the RDHK is shown in Fig. 10. The RDHK motherboard houses the required DC/DC converters and voltage regulators to derive all the power voltages used on-board from a 24 V input. For redundancy, a second 24 V input is provided. The motherboard has connectors to plug the SoC module and mezzanine card, a dual SFP cage connected to GTR transceiver pins of the SoC to provide two Gigabit Ethernet ports, a QSFP cage for connectivity up to 40 Gbps (using an appropriate SoM), a RS232-USB interface for console I/O, an 8-bit microcontroller and RS-485 port (RJ45 connector) for remote monitoring, a local 125 MHz oscillator, and various ancillary circuits. The RDHK motherboard provides 6 groups of 8 SFP cages for communicating with downstream devices, i.e. up to 48-port in total. The CLK\_MEZZ

Figure 10: The RDHK in its enclosure.

mezzanine card comprises the required PLL to generate the 125 MHz clock from the 5 MHz clock provided by the atomic clock. It provides also two SFP cages for additional optical I/O capability, and an RJ45 connector for cascading two RDHK units in a master-slave configuration. The RDHK is compatible with SoM model TE803 from Trenz in its different options of equipped SoC and SDRAM.

In the downstream direction, from the RDHK to external devices, each group of 8 SFP transmitters is driven by a common serial source via an 1:8 fanout chip (CDCLVP1208, Texas Instruments). The serial source can be a pair of output pins from the FPGA of the SoM or an output pair of a sextuple D flip-flop (MC10EP451, ON Semiconductor) which is external to the SoM. The inputs of the sextuple D flip-flop originates from the SoM, while the clock is derived directly by the PLL placed on the mezzanine card. In this way, the serial streams to be distributed can be retimed locally with a discrete flip-flop that is not influenced by the variations of delay through the FPGA. When the serial stream to be fanout is taken directly from FPGA output pairs, any potential variations of delay through the FPGA are also propagated. The serial stream transmitted over each group of 8 SFPs can be serial data or a clock (e.g. the constant binary data word "1100" serialized at 500 Mbps is equivalent to a 125 MHz clock). Each group of 8 SFP transmitters is selectable to send either serial data or a serialized clock. In the upstream direction, from external devices to the RDHK, each of the 48 SFP receivers is connected to a distinct pair of FPGA I/O's of the SoM, providing up to 48 point-to-point link in this direction. It should be noted that the desired number of ports is reached by using regular FPGA I/O pins for transmission and reception, instead of embedded FPGA high-speed serial transceivers which are much less numerous than ordinary I/O's. Transmission can use Xilinx UltraScale+ component OSERDESE3 or the native TX\_BITSLICE primitive. Both can perform serialization from 4-bit or 8-bit parallel words at a serial rate up to 1.25 Gbps, although it is intended to run no faster than 500 Mbps. For the distant partner, this rate is compatible for reception with regular FPGA input pins or the receiver part of various Xilinx FPGA high-speed transceivers (e.g. GTP, GTH). Reception on the RDHK side can use Xilinx ISERDESE3 components or native RX\_BITSLICE primitives. These can implement a 4-bit or 8-bit descrializer, up to gigabit per second serial rate. However these, blocks do not incorporate CDR circuitry. Consequently, descrialization uses the local reference clock. Correct data reception necessarily requires that the remote partner uses the clock it has recovered from the RDHK to clock the serializer driving the return path link to the RDHK, i.e. the communication link must be fully synchronous in both directions to the same common clock source.

Figure 11: Picture of the RDHK motherboard and the installed SoM.

A picture of the RDHK board is shown in Fig. 11. The board has been delivered at the end of March 2022 and is still under debugging at the time of writing this document. Its companion card, the CLK\_MEZZ, has been designed, laid out and will be fabricated soon. Although no result can be presented at this time on the RDHK prototyping effort, the development and debugging of this unit will continue over the coming weeks and the experience gained is expected to help significantly the design of the FDS for Hyper Kamiokande which is planned to re-use the main concepts and tested components.

# 4 Second Distribution Stage

# 4.1 Introduction

Figure 12: A block scheme of the second distribution stage. The module's is controlled by an FPGA mezzanine (blue box) which has links with other time distribution's entities via optical fibers (blue lines with circles) in turn connected via SFP (small from factor pluggable) electro-optical transceivers to the FPGA high speed serial lines (MGT). Each quad SFP block contains 4 bidirectional fiber connections to front-ends (yellow boxes) and first distribution stage (purple box).

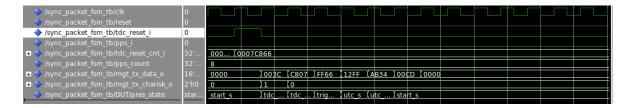

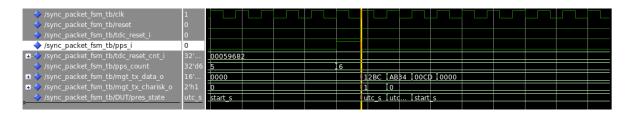

The second distribution stage, whose block diagram is reported in Figure 12, receives the reference clock, the TDC reset, the global coarse counter, the PPS and the synchronous commands from the first stage (purple box and related blue lines in the scheme) and pass them to the front-ends. To accomplish this task (and fulfill the requirement number 2 and 3) it establishes a bi-directional, synchronous and phase deterministic link to each node over an optical fiber pair used also to exchange critical slow control information between the data acquisition system and the front-ends (yellow boxes). This module, hence, has also Ethernet connections to the DAQ network via optical fibers (gray box). All the links are handled by the FPGA's Multi-Gigabit Transceivers (MGT). The synchronous link's characteristics enumerated above represent the most critical aspect of the second distribution layer and an extensive R&D campaign has been carried out in the last two years to select the most suited technology for the Hyper-Kamiokande experiment.

#### 4.2 Clock and Data Recovery

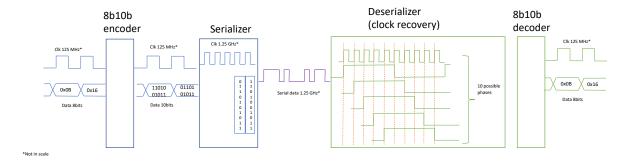

Many solutions have been evaluated and the selected one is based on the Clock and Data Recovery (CDR) scheme: the process of extracting time information (clock) and data from a single serial stream. The CDR is implemented by means of a specific serializer-deserializer (ser-des) couple to be used on both sides of the link. The simplicity, reliability and the convenience of this technique has fueled its use in many different fields so that all the modern FPGAs have CDR compliant ser-des already embedded in the silicon. This represents a further advantage for the experiment because it allows sending slow control data and distribute the system clock using one single fiber. It doesn't require any dedicated chip-set beside the FPGA already used to perform all the digital operations needed for the data collection and communication with the DAQ. Reducing the components on the electronics boards

Figure 13: A schematic view of the clock and data recovery concept.

has advantages on many critical aspects of the HK's design like the in-water electronics footprint, its power dissipation and the number of links and connectors between the design entities.

A time distribution scheme based on the CDR requires that one entity, called master, receives the precise clock, the master clock, along with data and distributes it to the different nodes, called slaves. This implies that the master establishes a CDR compliant serial link to each slave where the data and clock is merged and serialised. Each receiver separates back data and clock from the serial stream using a desirialiser. In order to guarantee the performance required by the experiment, extreme care must be devoted to the ser-des configuration to achieve low jitter and a fixed phase relation between the transmitter's and receiver's clock. This last aspect is particularly critical since, in the standard configuration, the FPGA's ser-des locks on a random phase after each reboot or reset. Details of the CDR concepts are reported in the block scheme of Figure 13.

A minimum number of data transitions per second needs to happen on the line to properly extract time information, therefore, data must be encoded in a specific way that guarantees the clock reconstruction on the receiving side. One of the most common encoding techniques is the so-called "8b/10b". The phase deterministic locking mechanism selected for Hyper-Kamiokande is described on the Xilinx FPGA documentation relative to the ser-des [18, 19] in the receivers section when the PMA manual alignment mode is discussed. This technique has been widely used in many physics experiments since more than a decade and it is recognised as practical and reliable hence there are many references in literature, the first published in 2011 [20].

The proposed locking system idea is quite simple: during the link locking phase, the master sends a conventional word to the slave, usually a so-called "8b10b" comma, over the serial line. The slave receives the serial data stream, parallelises it and looks for this conventional word. If it is not found, the firmware performs a so-called "slide" which consists in shifting the parallel word alignment by 1 serial stream unit interval. This procedure goes on until the conventional word has been recognised. Since the clock is extracted from the data stream, the shift mechanism just described produces also a phase shift of the reference clock and, when the data alignment is reached, the reference clock replica on the slave has the same phase as the master's.

The fixed phase clock and data recovery scheme is considered simpler and more robust then a "direct" scheme in which the clock and data are sent on two separate fibers in a network scheme such as the one between second distribution stage and the front-ends. This aspect becomes critical in the conditions like the Hyper-Kamiokande's where the fibers' length between the clock distribution and the different FEs varies depending on the vessel's position in the far detector barrel and the in-water equipment has tight constraints in term of power dissipation, heat dissipation and reliability with no maintenance foreseen for very long periods of time.

The CDR scheme is considered more robust because it requires one optical transceiver to transfer data and clock while the direct solution needs two. This difference brings an obvious reliability advantage since these optical components are considered fragile in terms of lifetime. Moreover, having less components simplifies the board design, reduces the power consumption and the heat dissipation especially in a tight environment as the Hyper-Kamiokande in-water vessel where the FE electronics is hosted.

The CDR scheme is also considered simpler especially when the connection's fibers are of different lengths. In such a scenario, the master electronics would receive from each slave a data stream

Figure 14: The custom solution test-bench based on the KC705 evaluation boards. On the left the first board configured as transmitter (TX) and on the right the second configured as receiver (RX). In the photo, the orange optical fiber and the 2 cables that bring the transmitted and reconstructed clock to an oscilloscope are visible.

that is not aligned with its reference clock. This misalignment needs to be carefully compensated on a channel to channel base at risk of misinterpreting the received data or causing catastrophic failures due to gate meta-stability.

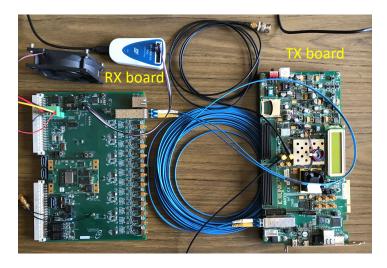

#### 4.2.1 Experimental tests

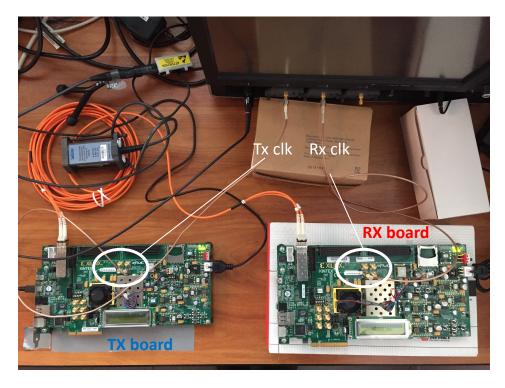

A test campaign has been conducted to evaluate the proposed clock and data recovery concept. The experimental tests are based on evaluation boards and prototypes used as platforms to develop the firmware and the methods that will be used in the final release.

The study has started using a couple of Xilinx evaluation boards KC705 equipped with the Xilinx Kintex 7 FPGA [21]. A specific firmware has been written to establish a 1 Gigabit Ethernet communication link over an optical fiber with a special ser-des configuration that implements the fixed phase CDR method. The firmware has been installed on the boards set, one acting as transmitter (TX) and the other as receiver (RX). On each board, SMA connectors were used to output the transmitted and reconstructed clock signals so that their quality could be measured. The described setup is presented in Figure 14.

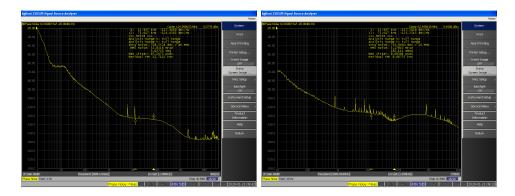

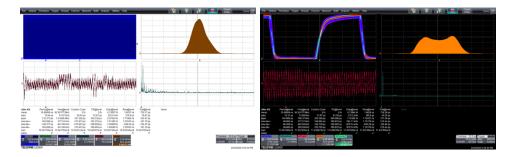

The first phase has been devoted to the data bandwidth compliance verification with the 1 Gbps Ethernet protocol; then, the attention has been focused on the jitter performances measurement for the embedded clock which represents the most important element at this stage of the R&D. An extensive measurement campaign has been carried out and the cadence characteristics have been evaluated in time and frequency domains. In the time domain the jitter has been measured by means of an oscilloscope (Lecroy Wavepro 760Zi 6 GHz 40Gsps) and the results are reported in Figure 15.

The jitter that affects the transmitted clock is equal to 32 ps which gives a measure of the cadence quality before the distribution. As can be seen from the Figure, the reported histogram doesn't have a perfect gaussian shape, sign of a deterministic component. This effect is even more evident on the receiver board where the reconstructed clock has a total jitter of 61 ps and the relative histogram has two clear peaks. Unfortunately, the measurement in the time domain doesn't provide any other detail

Figure 15: Time domain jitter measurements for the custom solution implemented on the KC705 evaluation boards set. On the left the transmitted clock is reported with a total jitter of 32 ps. On the right the received clock has 50 ps jitter and an evident deterministic component.

about that.

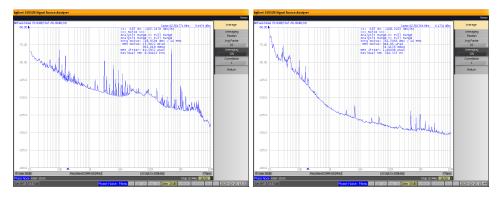

Figure 16: Frequency domain jitter measurements for the custom solution implemented on the KC705 evaluation boards set. On the left the transmitted clock is reported with a total jitter of 29.5 ps with evident components at 500 kHz. On the right the received clock is presented with a 50.1 ps jitter and the same evident deterministic component.

The same clock signals have been evaluated also in the frequency domain using a phase noise analyser. The principle of this kind of measurement can be explained in a simplified way as follows. The clock under study is sent to an instrument capable to recognise its frequency and generate a cadence of equal characteristics but with very low jitter. The two clocks, the input one and the one generated internally, are combined using the heterodyne function (the same used in the demodulation operation) which result is the difference between the two. This waveform is then plotted and represents the frequency deconvolution of the clock jitter while the area under the curve is equal to the total jitter.

For this test, a Keysight E5052B has been used and the phase analysis plots of the transmitted and received clocks are reported in Figure 16. From the plots the total jitter values can be obtained: 29.5 ps for the TX and 50.1 ps for the RX, very similar to the measurement in the time domain. Moreover spikes (spurious frequencies) at 500 kHz are evident on both the transmitted and received clock which are the source of the deterministic jitter. The fact that the same "modulation" frequency is present on both sides of the link calls for an effect generated by the board hardware. Further versifications have identified the cause of this noise in the DC to DC power supply converters that feed the FPGA.

A second test-bench has been realised using a custom board as receiver (see Fig. 17) with a different power supply scheme and FPGA: a Xilinx Zynq 7000. For this new chip a compatible firmware has been designed so that the same 1 Gigabit Ethernet link has been established and a similar set of measurements has been carried out. The jitter on the received clock this time is lower (40.6 ps total) and the "modulation spikes" are less pronounced (Fig. 18 left). The custom board is equipped also with a so-called jitter cleaner component, a Phase-Locked Loop (PLL) SI5345 capable to filter the jitter and produce a cleaner clock. A measurement of the jitter has been performed also on the clock treated by this filter and the results are shown in the right plot of Figure 18. The excellent filtering

Figure 17: The custom solution test-bench modified using a custom board (on the left) as receiver and a KC705 as transmitter on the right. The connection scheme is the same as in the previous setup.

capability of the PLL is evident since the measured jitter is now 2.4 ps and the modulation components are almost gone.

Figure 18: Frequency domain jitter measurements performed on the clock reconstructed by the custom board. On the left the clock before the jitter cleaner PLL and on the right as measured after the filter.

The phase stability has been also tested using an oscilloscope in infinite persistence mode triggered on the transmitted clock. The receiver board has then been reset multiple times and the RX clock has been reconstructed always with the same phase distance to the TX clock every time the link has been re-established.

The results of this extensive test campaign are very encouraging because all the Hyper-Kamiokande specifications are largely met and this clock distribution scheme is mature enough to be used in the experiment. The R&D described here shows different important aspects of the proposed solution. The method used and the selected components, including the jitter cleaner to be hosted on the FE side, are very effective and can mitigate eventual noise issues that will be discovered in the later integration stage. The group has enough skills on the time distribution to analyse, identify problems and solve them.

#### 4.2.2 First Integration Test

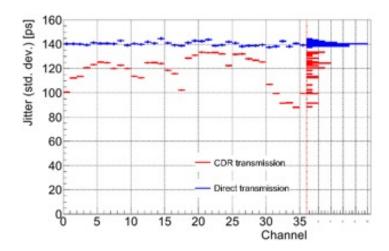

Once the clock distribution concept based on CDR has been evaluated, a new test campaign has been launched to measure its performances against the first prototypes of the digitisers under development for the experiment. Since that R&D is still ongoing a limited set of tests have been carried out but still sufficient to give indications of the possibility to integrate the different parts at the final stage.

Figure 19: TDC resolution of a QTC receiving the clock from a clock and data recovery scheme (CDR, red dots) compared with the setup in which the clock is feed directly on a dedicated fiber (direct, blue dots).

This effort is also a first attempt to realise the so-called "vertical slice test" which consists in realizing an electronics chain with all the components needed to acquire signals from a PMT. Starting the time distribution integration with the front-end at this early stage allows also to better identify the interfaces and prevent problems which could be hard to solve once the designs will be more mature.

The test has been conducted on the digitisers solution based on the QTC chips on which a prototype firmware, implemented on the same evaluation board presented before and without jitter cleaner, acted as time distribution master feeding a clock embedded with data to the QTC board. The firmware was written to provide the needed information to this specific FE implementation and analog data have been acquired based on the distributed clock. To better evaluate the performances, this data has been compared with others recorded while the front-end was receiving the clock directly from an external source on a dedicated fiber.

Figure 19 reports the TDC measure resolution on the y axis versus the number of channels. The clock and data recovery scheme allows to perform a slightly more precise measure while the channel-to-channel dispersion could be explained by the spurious frequencies described in the previous paragraph. Even though the results already meet the experiment's requirements we are confident that the use of jitter cleaner on the final FE configuration will reduce the spread and further increase the resolution.

# 4.3 Time Distribution Module (TDM)

The number of slaves to be served, i.e. the front-ends, in the HK case, doesn't allow the implementation of all the master's functionalities on a single electronics board hence they have to be divided upon different cards, called Time Distribution Module (TDM), as depicted in the block scheme of Fig. 1.

Each TDM is also connected to the data acquisition system using a standard Ethernet link to exchange slow control information, like the upload firmware for the FE's FPGAs or the acquisition related commands, and pass them to all the front-end modules connected to it. A non-deterministic channel from the in-water electronics to the TDM is also established and is used to send housekeeping information and slow control data to the DAQ.

Each time distribution module is designed to perform the following tasks:

- Receive the master clock and distribute it embedded into time related data with a jitter at the endpoint smaller than experiment's requirement.

- Guarantee a constant channel to channel phase difference over each reset and power up compensating the differences introduced by different cable lengths.

- Guarantee a bidirectional data bandwidth of at least 100 Mbps (at net of the data encoding).

Figure 20: First time distribution module prototype board layout.

- Communicate to the data acquisition system to exchange slow control data.

- Implement a redundant optical fiber link to each FE to be activated by a software command.

Board Architecture Following the mentioned tasks and according to the experiment's requirements, the TDM architecture has been designed around a Xilinx XCZU9EG Zynq ultrascale+ system on chip (SoC) FPGA [22] installed on a so-called "system-on-module" designed by Trenz[23]. A system on chip is a kind of FPGA on which a general-purpose processor is embedded on the silicon device along with the programmable part and specific connections are designed to exchange data between the two sides. The selected device hosts a quad-core Cortex-A53 and a dual-core Cortex-R5F Arm architecture associated to about 600.000 logic cells, 300 IO pins and up to 24 high-speed ser-des. As mentioned, this FPGA comes pre-assembled on a electronics board which hosts a number of features like the main power supply section, a double data rate (DDR) memory for the processor and so on. This choice makes the TDM design simpler since the most complex part, the FPGA and its ancillary sections, are brought to the board via this module avoiding the routing of a very complex and dense part. The link between the TDM and the system-on-module is performed using 4 high-speed connectors each of which has 160 pins that guarantees to exploit almost all the FPGA resources. The time distribution module can be then considered a sort of mother-board for the FPGA module on which all the specific features needed for Hyper-Kamiokande are implemented. As mentioned previously, the core features of this broad are the high-speed serial links to the front-ends and the data acquisition system. To implement them, on the TDM, there are 4 groups of SFPs each capable of driving 8 fibers connected to 4 FPGA ser-des for a total of 32 SFPs and 16 ser-des. This connection scheme guarantees the clock and data distribution to 16 FEs having a link redundancy of 2, as explained in the following paragraph. Another group of 4 optical transceivers is devoted to the first to second distribution stage connection. Of this group, two fibers are used to receive the reference clock and two the synchronous data from the main and spare first distribution layer. The last main section is devoted to the DAQ communication where 2 1Gbps Ethernet links are implemented. The board design is completed by all the circuitry needed to power and control the optical transceivers and to monitor the system environmental and operation parameters.

The first prototype of the time distribution module has been designed in December 2021 and the fabrication is started in March 2022. A picture of the board layout is reported in Figure 20.