# **EyeScan with XpressK7**

F. Costanza, on behalf of the LAPP ITk Team XYZ meeting, Avr x<sup>th</sup> 2022

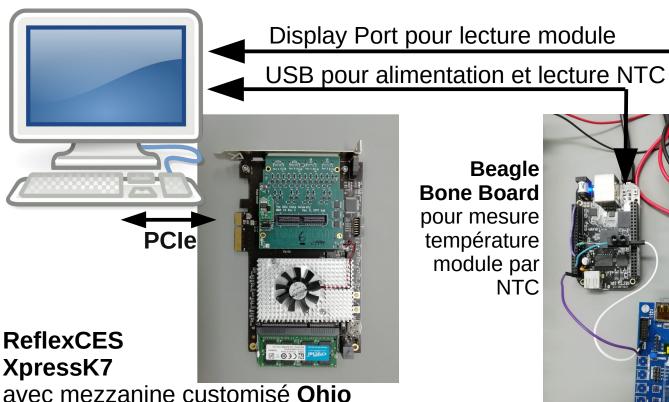

## Banc de tests XpressK7+YARR

Trés bon pour s'entraîner avec les modules RD53A.

On prévoit de l'utiliser pour les tests à réception des modules: procedure pas

Beagle **Bone Board** pour mesure température module par **NTC**

Alimentation module (1.8 V, ~0.8A)

**Power Supply**

Multi Module Adapter MMA

(jusqu'à 4 front-ends)

**RD53A on Single Chip Card (SCC)**

### Development pour EyeScan

#### Firmware:

Integration sur XpressK7 de IBERT et EyeScan par LogiCORE™ IP

Integrated Bit Error Ratio de Xilinx utilisant l'interface JTAG.

Configuration en temps réel par le module "Virtual Input/Output" utilisant l'interface JTAG.

Configuration de l'ohio board.

Flux constant de commandes [Synch + 31xNoop] pour la synchronisation de l'horloge du RD53A

Envoi des commandes de configuration du module RD53A en temps réel.

#### Hardware:

- Cartes de adaptations:

- services mini-Display Port (RD53A SCC) ↔ pigtail

- Firefly ↔ FMC (XpressK7)

- Trés minimaliste. Elle donne accès en temps réel:

- Reset de FPGA et module RD53A;

- Command de configuration des outputs du module RD53A par la valeur de son registre 68: Clk640MHz, Aurora, PRBS, GND.

- Registres de monitorage FPGA: counter pour monitorer les horloges, RD53A synched, RD53A ready.

Eye Scan w/ XpressK7

| hw_vio_1    |       |   |          |           |          |  |  |  |

|-------------|-------|---|----------|-----------|----------|--|--|--|

| Q           | +   - | - |          |           |          |  |  |  |

| Name        | Value |   | Activity | Direction | VIO      |  |  |  |

| Ղ₄ Reset    | [B] 0 | * |          | Output    | hw_vio_1 |  |  |  |

| 🖫 Configure | [B] 1 | * |          | Output    | hw_vio_1 |  |  |  |

| > 🖫 Reg68   | [H] 0 | * |          | Output    | hw_vio_1 |  |  |  |

| 🖫 Synched   | [B] 1 |   |          | Input     | hw_vio_1 |  |  |  |

| ጌ Ready     | [B] 1 |   |          | Input     | hw_vio_1 |  |  |  |

| > 🖫 Counter | [H] 0 |   | <b>*</b> | Input     | hw_vio_1 |  |  |  |

### Testée avec succès en loopback interne

| Name                 | TX                                | RX                                | Status     | Bits     | Errors | BER       | BERT Reset |

|----------------------|-----------------------------------|-----------------------------------|------------|----------|--------|-----------|------------|

| Ungrouped Links (0)  |                                   |                                   | Status     | Dies     | Litoro | DEIX      | DEIN NOSCE |

|                      |                                   |                                   |            |          |        |           |            |

| V 📎 Link Group 0 (4) |                                   |                                   |            |          |        |           | Reset      |

| ⊗ Link 0             | Quad_115/MGT_X0Y0/TX (xc7k325t_1) | Quad_115/MGT_X0Y0/RX (xc7k325t_1) | 1.250 Gbps | 1.835E14 | 0E0    | 5.448E-15 | Reset      |

| ⊗ Link 1             | Quad_115/MGT_X0Y1/TX (xc7k325t_1) | Quad_115/MGT_X0Y1/RX (xc7k325t_1) | 1.250 Gbps | 1.835E14 | 0E0    | 5.448E-15 | Reset      |

| ⊗ Link 2             | Quad_115/MGT_X0Y2/TX (xc7k325t_1) | Quad_115/MGT_X0Y2/RX (xc7k325t_1) | 1.250 Gbps | 1.835E14 | 0E0    | 5.448E-15 | Reset      |

| ⊗ Link 3             | Quad_115/MGT_X0Y3/TX (xc7k325t_1) | Quad_115/MGT_X0Y3/RX (xc7k325t_1) | 1.250 Gbps | 1.835E14 | 0E0    | 5.449E-15 | Reset      |

| TX Pattern |   | RX Pattern |   | TX Pre-Cursor     | TX Post-Cursor    | TX Diff Swing  |

|------------|---|------------|---|-------------------|-------------------|----------------|

|            |   |            |   |                   |                   |                |

| PRBS 7-bit | ~ | PRBS 7-bit | ~ | 1.67 dB (00111) 🗸 | 0.68 dB (00011) 🗸 | 1018 mV (1100) |

| PRBS 7-bit | ~ | PRBS 7-bit | ~ | 1.67 dB (00111) 🗸 | 0.68 dB (00011) 🗸 | 1018 mV (1100) |

| PRBS 7-bit | ~ | PRBS 7-bit | ~ | 1.67 dB (00111) 🗸 | 0.68 dB (00011) 🗸 | 1018 mV (1100) |

| PRBS 7-bit | ~ | PRBS 7-bit | ~ | 1.67 dB (00111) 🗸 | 0.68 dB (00011) 🐱 | 1018 mV (1100) |

| PRBS 7-bit | ~ | PRBS 7-bit | ~ | 1.67 dB (00111) 🗸 | 0.68 dB (00011) 🐱 | 1018 mV (1100) |

| DFE Enabled | Inject Error | TX Reset | RX Reset | RX PLL Status | TX PLL Status | Loopback Mode  |

|-------------|--------------|----------|----------|---------------|---------------|----------------|

|             |              |          |          |               |               |                |

| <b>✓</b>    | Inject       | Reset    | Reset    |               |               | Near-End PMA 🗸 |

| <b>✓</b>    | Inject       | Reset    | Reset    | Locked        | Locked        | Near-End PMA 🔍 |

| <b>✓</b>    | Inject       | Reset    | Reset    | Locked        | Locked        | Near-End PMA ✓ |

| <b>✓</b>    | Inject       | Reset    | Reset    | Locked        | Locked        | Near-End PMA 🗸 |

| <b>✓</b>    | Inject       | Reset    | Reset    | Locked        | Locked        | Near-End PMA 🗸 |

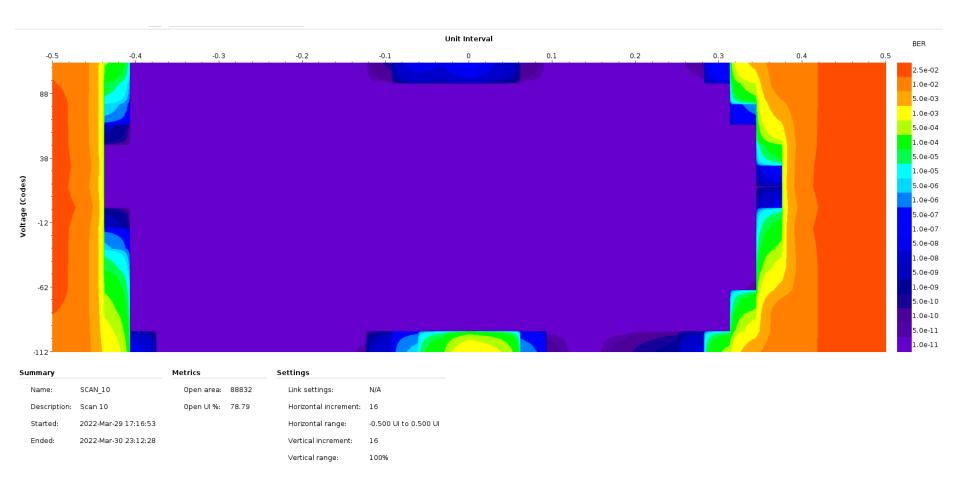

# Interface EyeScan

### Testée avec succès en loopback interne