## Dernières évolutions architecturales

**J.-P. Cachemiche, CPPM**P. Bibron, J. Languouet, R. Le Gac, CPPM

#### Résumé

- Implémentation des liens sériels TFC et WR

- Implémentation de l'arbre d'horloge

## **Serial links**

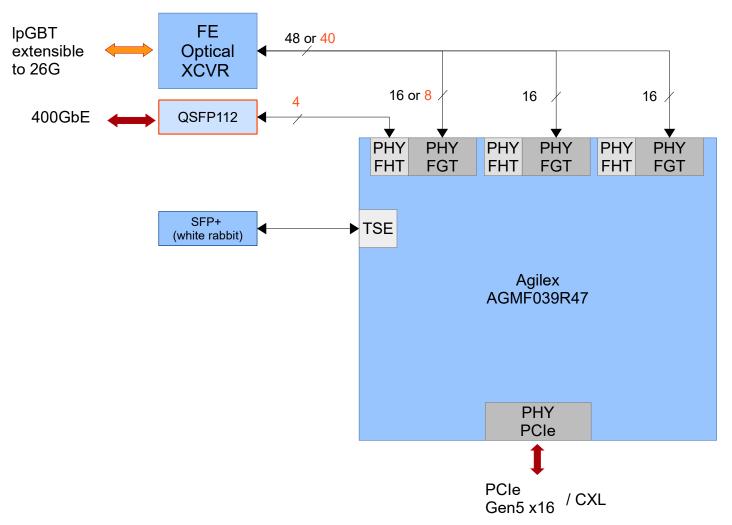

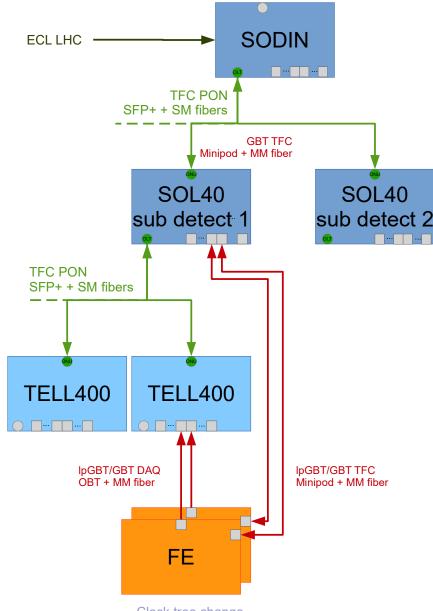

## Former serial link diagram

Missing dedicated link for fast control, white rabbit is only foreseen for clock distribution. Using IpGBT (point to point) links is possible but requires more PCIe400 on the overall system. TFC-PON has a ratio of 1 to 128.

TSE IP (ethernet over LVDS) leaves high speed serializer free but is limited to 1.6Gbps. White rabbit could evolve toward 10GBE?

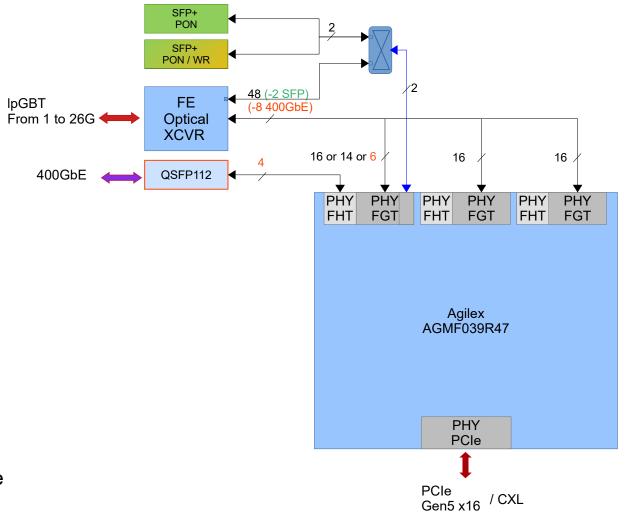

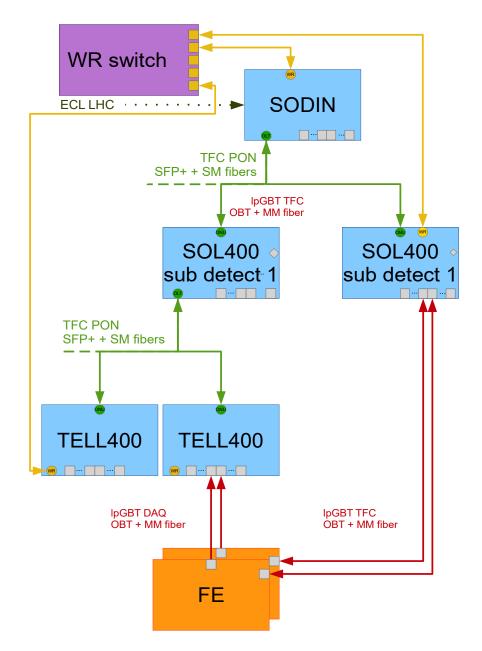

# Proposition of serial link diagram

2 SFP+ cages wired to high speed serializer. SFP+ cage can accept a 1GbE optoelectronic XCVR (for WR) or a OLT/ONU PON optoelectronic XCVR.

Number of bidir links available for FE:

| Number of FE links | Use of SFP+ | Use of<br>400GbE |

|--------------------|-------------|------------------|

| 48                 | ×           | ×                |

| 46                 | ✓           | <b>√</b>         |

| 40                 | ×           | <b>√</b>         |

| 38                 | ✓           | <b>√</b>         |

48 links still possible by adding a crossbar.

Using 400GbE makes 8 links unavailble for FE because of bandwidth limitation inside the FPGA.

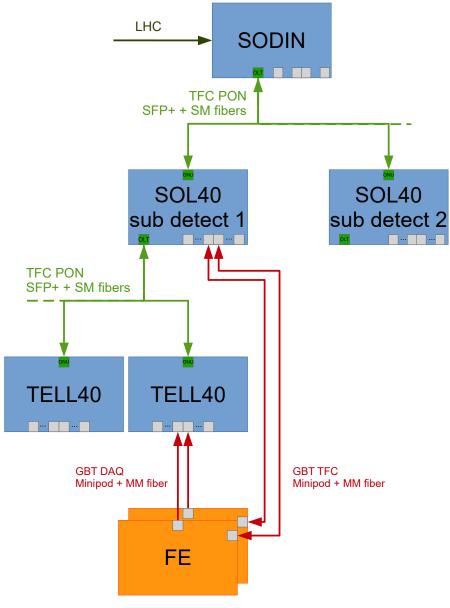

# Use case current system PCle40

### Use case: transition PCle400 as TELL400

### Use case: PCle400 with WR

#### **SOL400**

To mitigate the fact that there is only 2 links for PON ONU, PON OLT and WR. More SOL400 are required to benefit from WR clock distribution for FE.

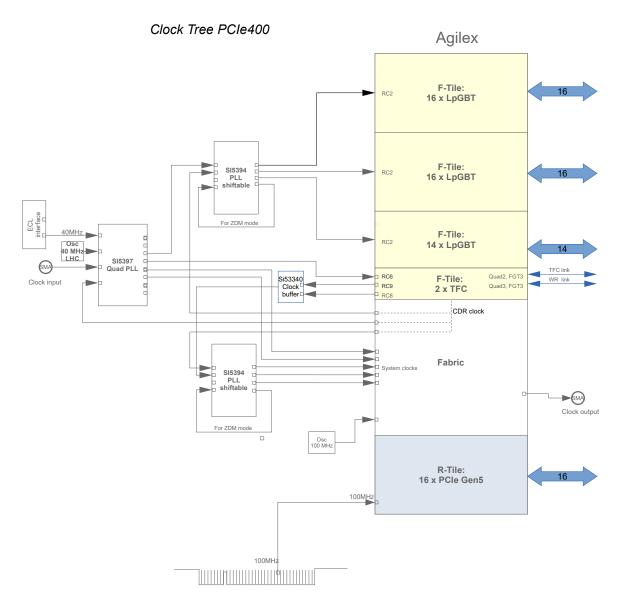

### **Clock tree**

## Former clock tree

# Missing features

#### No FINC/FDEC on SI5394

| Pin Name  | Pin Number      |        |        | Function              |                                                                                                                                                                                                                                                                                      |

|-----------|-----------------|--------|--------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | Si5395          | Si5394 | Si5392 | Pin Type <sup>1</sup> | runction                                                                                                                                                                                                                                                                             |

| LOS0b     | -               | -      | 30     | 0                     | Loss of Signal for IN0 <sup>3</sup> This pin indicate a loss of clock at the IN0 pin when low.                                                                                                                                                                                       |

| LOS1b     |                 | =      | 31     | 0                     | Loss of Signal for IN1 <sup>3</sup> This pin indicate a loss of clock at the IN1 pin when low.                                                                                                                                                                                       |

| LOS2b     | 0 <del>-0</del> | -      | 35     | 0                     | Loss of Signal for IN2 <sup>3</sup> This pin indicate a loss of clock at the IN2 pin when low.                                                                                                                                                                                       |

| LOS3b     | >=              | ==     | 36     | 0                     | Loss of Signal for IN3 <sup>3</sup> This pin indicate a loss of clock at the IN3 pin when low.                                                                                                                                                                                       |

| LOS_XAXBb | 5               | 28     | 28     | 0                     | Loss of Signal on XA/XB Pins <sup>3</sup> This pin indicates a loss of signal at the XA/XB pins when low.                                                                                                                                                                            |

| FINC      | 48              | _      | ::     | Ĩ                     | Frequency Increment Pin <sup>2</sup> This pin is used to step-up the output frequency of a selected output. The affected output and its frequency change step size is register configurable. This pin is internally pulled low and can be left unconnected when not in use.          |

| FDEC      | 25              | 5      | 5773   | 1                     | Frequency Decrement Pin <sup>2</sup> This pin is used to step-down the output frequency of a selected output. The affected output driver and its frequency change step size is register configurable. This pin is internally pulled low and can be left unconnected when not in use. |

Figure 7.1. Si5392/94/95 Block Diagram

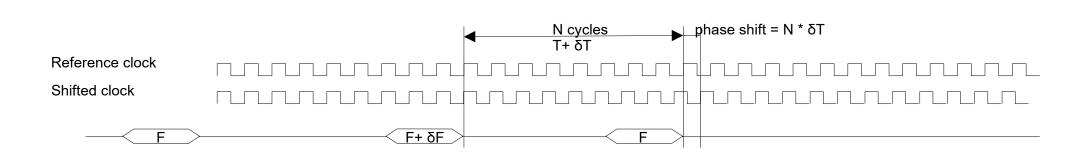

# Phase adjust principle

#### Frequency increment or decrement during a controlled amount of clocks

#### Exemple:

F = 100 MHz $\delta F = 0.010001 \text{MHz}$

$\delta T = 1/100000000 - 1/100010001 = 1 ps$

Programming of 100.010001 MHz during 500 cycles → phase shift = 500 ps

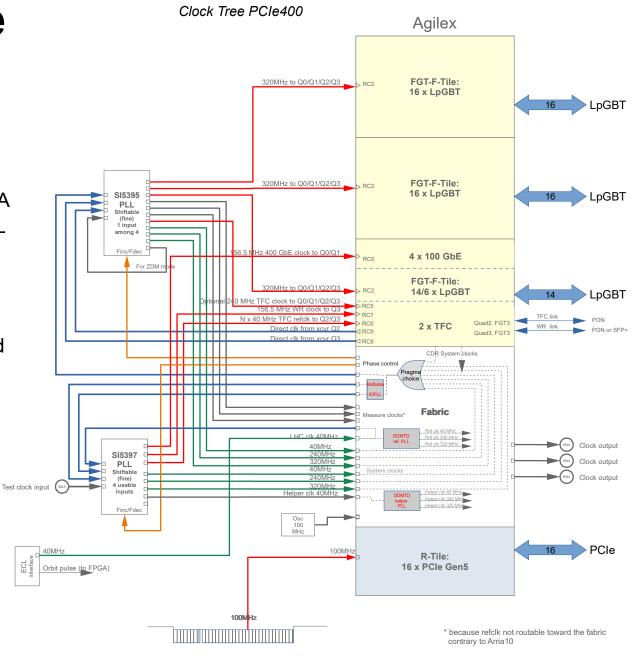

## New clock tree

#### **Simplifications**

- only 2 PLLs,

- no more clock buffers

- SMA input directly on FPGA

- LHC freq generated by PLL in free running mode (internal source)

#### **New features**

- CDR cleaned clocks routed to xcvrs

- DDMTD helper clock