# R&T PCIe400 : Update status refroidissement

12 mai 2022

Julien Langouët,

Kévin Arnaud, Paul Bibron, Jean-Pierre Cachemiche, Renaud Le Gac, CPPM

### **Sommaire**

**Étude dissipation thermique FPGA**

Étude température environnement serveur

**Étude maquette thermique PCIe400**

**Update modèle 3D PCIe400**

### Étude dissipation thermique FPGA

#### **Objectif: Vérifier l'hypothèse des 180W dissipés par le FPGA AGMF039**

#### Mesures de courant consommé I<sub>core</sub> avec random pattern generator

- Problème de firmware pour atteindre un taux d'occupation de 90 % avec random pattern generator

- Même nombre de random pattern generator pour occuper un Arria10 1.15MLE et un Agilex Iseries 2.7MLE à 90 %.

- → Dû à l'utilisation d'attributs « keep » (introduits pour les simulations gate level)

- Nécessite une nouvelle série de mesures sur devkit Agilex I-series après correction du firmware

#### Estimation d'un toggle rate (TR) plus réaliste que 50 %

- Estimer le toggle rate équivalent des différents firmwares de la PCle40. 2 méthodes possibles :

- Onnaissant le  $I_{core}$  et le **taux d'occupation (TO)** et la  $T_j$  de chaque firmware, déduction du toggle rate équivalent (d'un firmware à base de random pattern generator).

- ightharpoonup Nécessite un **abaque** de  $I_{core}$  en fonction du **TO**, **TR** et  $T_j$  sur un Arria10 (utilisation du Power and Thermal Calculator de Intel?)

- O Utiliser l'estimation du power analyzer (dans flow de compilation) sur les firmwares des PCIe40

- → Le PTC estime un toggle rate pour chaque « modules », comment obtenir un toggle rate moyen global ? Moyenne pondérée ?

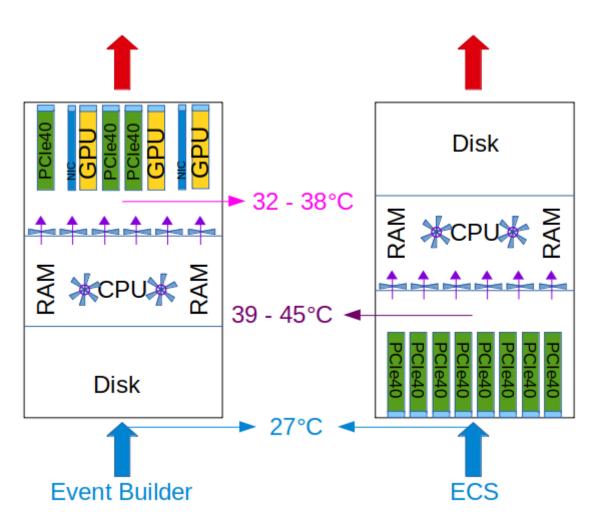

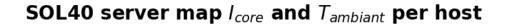

### Étude température environnement serveur

Objectif : Avoir une idée de la température dans un serveur typique

Mesures sur l'ensemble du système installé au CERN

(116 EB:329 cartes)

- Consommation électrique des CPU ~30W x2

- Varie : jusqu'à 40W x2

- Consommation électrique des RAM ~20W x16

- Stable sur plusieurs mois

(7ECS:34 cartes)

- Conso CPU/RAM?

Quelle est la consommation électrique des CPU nominale ?

Quelle est l'influence de l'activité des CPU sur la température ambiante ?

Reproduire des mesures lors de tests en charge, quand ?

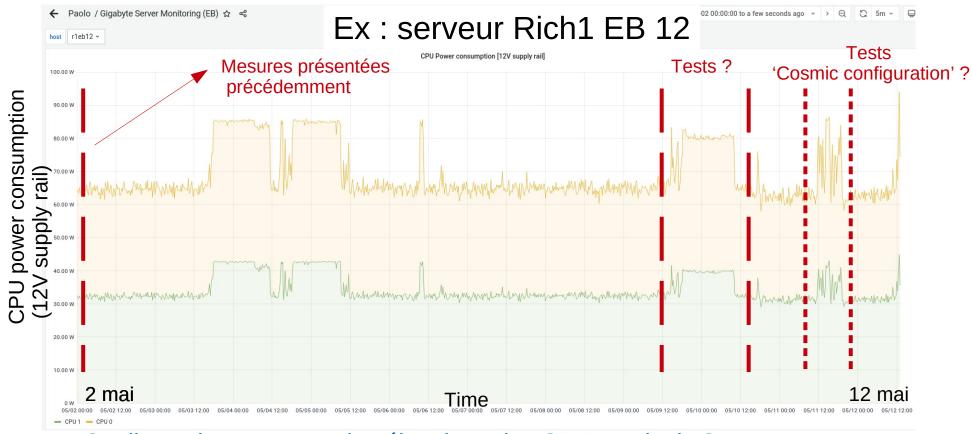

### Étude température environnement serveur

Objectif : Avoir une idée de la température dans un serveur typique

Quelle est la consommation électrique des CPU nominale ?

Quelle est l'influence de l'activité des CPU sur la température ambiante ?

- Reproduire des mesures lors de tests en charge, quand ?

### Étude maquette thermique PCIe400

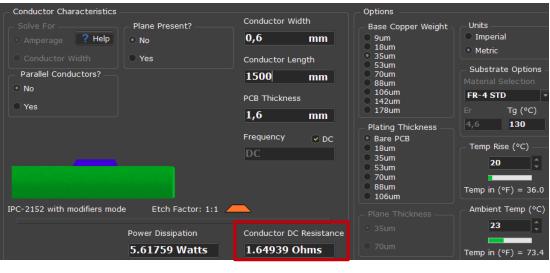

#### Résistance chauffante pour émuler le FPGA

- Fabrication de PCB de tests pour comparer la résistance en CAO et la résistance mesurée

Fil de cuivre + scotch capton

PCB simple-face (35µm)

mesure:  $1.25\Omega$  (ohm-mètre de précision)

- Difficultée rencontrée : mauvais refroidissement lors des tests, T → R →

le point de fonctionnement évolue en fonction du refroidissement.

- Utilisation d'une alimentation de laboratoire : Générateur de tension

- O Point de fonctionnement maximal 9V, 9A => 80W, température ~230°C (destruction du PCB

#### Suite:

- Maîtrise de la caractérisation d'une résistance chauffante

- Évaluation de la faisabilité avec une alimentation basse tension (3.3V)

- Calcul de la géométrie d'une résistance avec prise en compte de la température

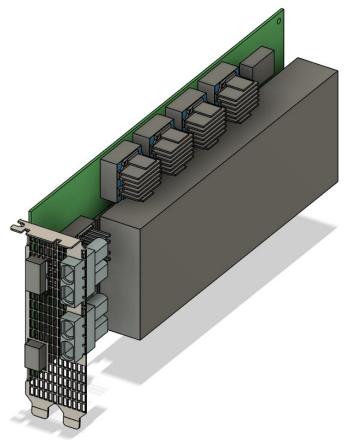

### Modèle 3D pour simulations CFD

#### **Modification**

- Hauteur radiateur (pour respecter précisément normes PCIe)

- Longueur PCB pour correspondre au standard '3/4' ou 'full length'

- Ajout des pad thermiques

- Ajout des radiateurs XCVR optiques

- Remplacement des cages SFP par des pavés pour faciliter le maillage en simulation

Dimensions heatsink FPGA: 3/4 LxWxH: 199x70x25.8mm full LxWxH: 257x70x25.8mm

Nextcloud:/PCIe400/hardware/3D\_model/PCIe400/PCIe400-PROP3-3\_4\_v19.step

Nextcloud:/PCIe400/hardware/3D\_model/PCIe400/PCIe400-PROP3-4 4 v2.step

## backup

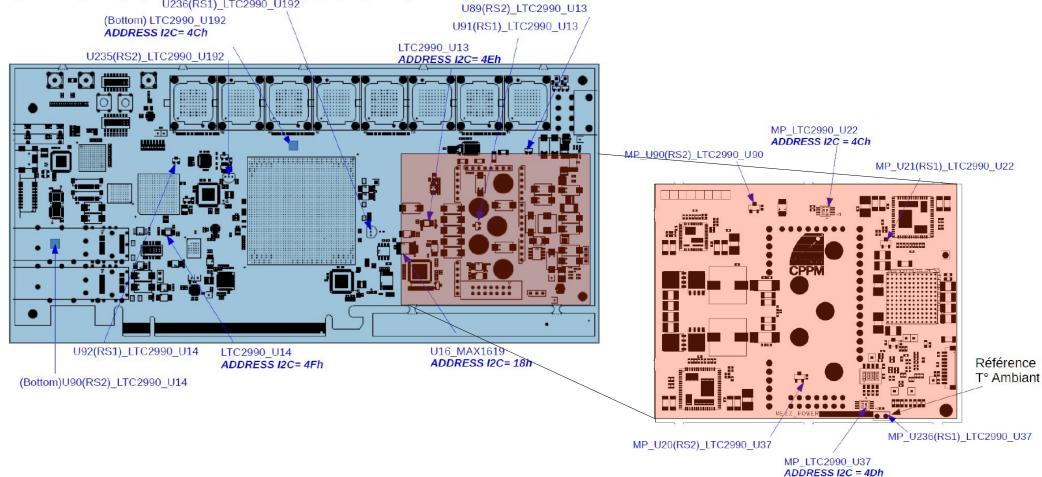

### Thermal sensors locations

# T<sub>ambiant</sub> and FPGA I<sub>core</sub> by ECS server

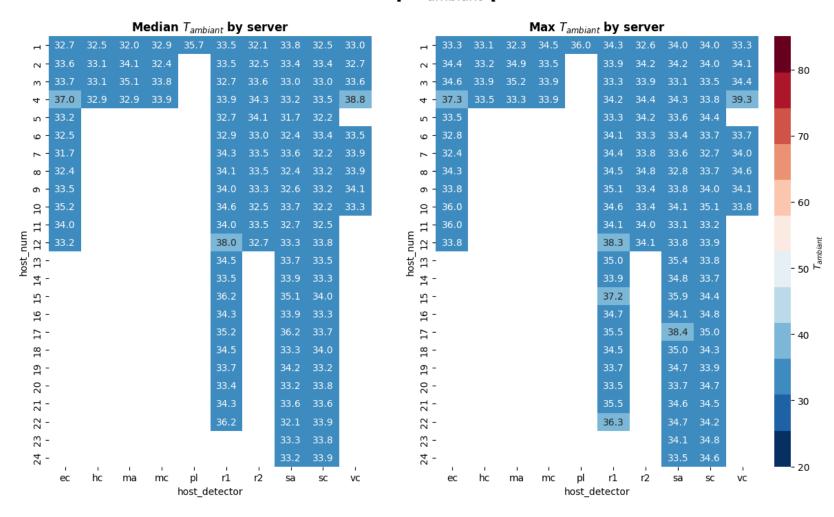

### T<sub>ambiant</sub> by Event Builder server

#### TELL40 server map $T_{ambiant}$ per host

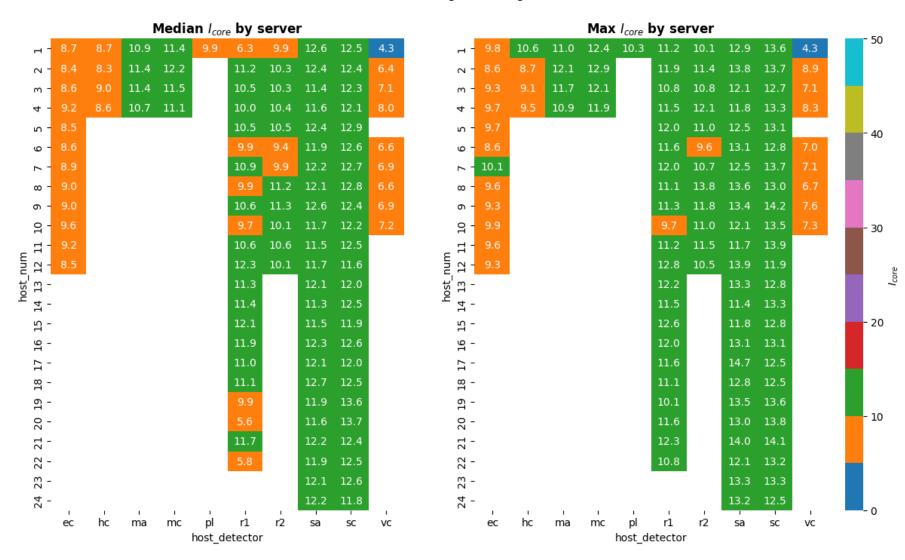

### I<sub>core</sub> by Event Builder server

#### TELL40 server map *l<sub>core</sub>* per host