# **R&T BICMOS**

Liste de diffusion : rt-sige-l@in2p3.fr

Wiki: https://forge.in2p3.fr/projects/rt-sige/wiki

S. Chen

J. Mesquida

G. Monier

M. Piat

D. Prêle

E. Bechetoille

S. Manen

L. Alvado

L. Leterrier

D. Charrier

D. Thers

## Contexte scientifique

#### Objectif scientifique et technique de la R&T transverse 'BiCMOS'

- Recommandation du GT microélectronique en 2021 :

- Offrir une alternative pérenne au seul CMOS fin

- Répondre à un large champ de besoin de hautes performances analogique frontale (restant compatible avec un peu de mixte)

- Maintenir une technologie BiCMOS SiGe (fin de l'AMS 0.35u SiGe...)

- ✓ En <u>physique nucléaire</u>

- o concilier **孝 dynamique/linéarité**, **↘ bruit et consommation**

- o avec un nombre croissant de voies  $\sim 10^3$ - $10^4 \rightarrow \sim 10^4$ - $10^5$

- o et à un coût raisonnable

- ✓ En <u>astroparticules</u>

- concilier → produit gain bande ; → bruit jusqu'aux basses

fréquences ; → dynamique/linéarité sur lignes adaptées

- o applications spatiales (faible conso. / durcissement) et/ou cryogéniques

- => forte complémentarité avec le WP1.1 Technologie Alternative de la MI2I

# Expériences cibles

#### En BiCMOS SiGe

- REA (Rénovation de l'Électronique d'Acquisition) au GANIL :

- Besoin de préamplificateur de charge configurable à distance dédié aux détecteurs silicium fortement capacitifs (~ 600 pF)

- NECTAR, Nuclear rEaCTions At storage Rings au LP2I https://www.lp2ib.in2p3.fr/nucleaire/nex/erc-nectar/

- cellules photovoltaïques pour la détection d'ions lourds

- => détecteurs fortement capacitifs et problématique thermique (UHV)

- signaux basse fréquences

- ATHENA et CMB S4 : Électronique de lecture pour détecteurs cryogéniques (SQUID, TES, KID)

- technologie BiCMOS SiGe ST130 et 'spare'

- performances bas bruit basse fréquence + produit gain bande > 4 GHz

# Expériences cibles

En CMOS ou BiCMOS, 'technologie alternative' (MI2I WP1.1)

- upgrades de XEMIS II, détecteurs à Xénon liquide pour imagerie médicale

- nombre de voies x 100 (~106), dynamique (800 keV), faible bruit & basse consommation (2.5mW/voie —> 1.5mW/voie)

- GRIT, nouvelle version de l'iPACI (v2 -> v3)

- nombre de voies x2 et optimisation du design.

- + SAR 10-bit 40 MHz

- + Mémoires analogiques

- Astroparticules

- Multiplexeurs cryogéniques (signal et thermométrie)

- Amplificateur chopper (réduction du bruit 1/f des MOS)

- JFET (bas bruit en 1/f) à base de NPN : G = C+E, canal D-S = B

### Sélection de technologies

#### Recensement des technologies accessibles :

- **BiCMOS SiGe**: GF 130, IHP 250 & 130, ST 130, AMS 350

- CMOS: XFAB 180 et SOI 180, ON, TSMC 130

Comparaison de plusieurs fondeurs sur la base de données non confidentielles

=> Difficile voir impossible tant qu'une NDA n'est pas signée

#### Critères de choix

- Pérennité à 8-10 ans

- Caractéristiques techniques : nœud, Vmax, Ft, Beta ...

- Coût

- Fondeur Français/Européen

Choix du fondeur IHP, dont la techno en 130nm SG13S

Choix d'un fondeur 'alternatif' XFAB 180nm CMOS et/ou SOI

Choix du fondeur ST 9MW SiGe 130nm à l'APC

# TRL (degré de maturité technologique)

| Niveau | Définition                                                                                                     | Nom synthétique               |  |  |

|--------|----------------------------------------------------------------------------------------------------------------|-------------------------------|--|--|

| TRL1   | Principes de base observés et identifiés                                                                       | Principe de base              |  |  |

| TRL2   | Concept technologique et/ou application formulés                                                               | Application formulée          |  |  |

| TRL3   | Preuve du concept analytique et preuve expérimentale de la fonction et/ou de la caractéristique critique       | Preuve du concept             |  |  |

| TRL4   | Vérification fonctionnelle en environnement de laboratoire au niveau composant et/ou maquette                  | Validation fonctionnelle      |  |  |

| TRL5   | Vérification en environnement représentatif de la fonction critique au niveau composant et/ou maquette         | Modèles à échelle réduite     |  |  |

| TRL6   | Démonstration en environnement représentatif des fonctions critiques de l'élément au niveau modèle             | Validation de la conception   |  |  |

| TRL7   | Démonstration en environnement opérationnel de la performance de l'élément au niveau modèle                    | Qualification d'un modèle     |  |  |

| TRL8   | Système réel développé et jugé apte à l'expérience                                                             | Qualification du système réel |  |  |

| TRL9   | Système réel ayant été utilisé à l'identique et avec succès lors d'une expérience dans l'environnement idoine. | Opération du système réel     |  |  |

TRL initial: (colorer la case correspondant à votre TRL initial)

| TRL1 | TRL2 T | TRL3 TRL4 | TRL5 | TRL6 | TRL7 | TRL8 | TRL9 |

|------|--------|-----------|------|------|------|------|------|

|------|--------|-----------|------|------|------|------|------|

### NDA et Design Kit

#### Signatures de NDA

- En collaboration avec Claude Colledani et Alban Maczka

- Demande de NDA en licence « globale » IN2P3

#### Signature entre le directeur de l'institut et le fondeur

- => optimisation des démarches

- => Accès à ces technologies au-delà du périmètre de la R&T

- 12 laboratoires signataires : APC, CPPM, IJCLAB, IPHC, IP2I, LAPP, LPNHE, LPC, LPC-Caen, LPSC, OMEGA, SUBATECH

- Cohérence avec la culture MI2I

#### NDA avec IHP signée en Janvier NDA avec XFAB signée la semaine dernière

Installation des **Kit IHP 130/250 nm** dans le cadre du projet **OMMIC** par l'IP2I au CC, test de l'accès distant, maintenance des kits, documentation utilisateurs

=> Travail à poursuivre avec le kit XFAB maintenant que le NDA est signé

# Etat des principaux risques

| Exemples de libellés             | Action pour réduire le risque                                                                                                                                                 | Responsable de<br>l'action | Criticité | Tendance |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------|----------|

| Pérennité de la technologie.     | <ul> <li>Changer de technologie mais délais très long .</li> <li>Orientation vers le nœud 130nm de IHP et 180nm de XFAB .</li> </ul>                                          | D. Charrier                | <b>*</b>  | •        |

| Incertitude délai signature NDA. | Risque écarté avec XFAB car NDA signée cette semaine .                                                                                                                        | D. Charrier                | <b>*</b>  | <b>→</b> |

| Incertitudes caractéristiques.   | <ul> <li>Changer de technologie mais délais très long .</li> <li>Caractéristiques IHP moins bonnes qu'espérées .</li> <li>Caractéristiques XFAB à découvrir .</li> </ul>      | D. Prêle                   | <b>*</b>  | 17       |

| Durée des fonderies.             | <ul> <li>Changer de technologie mais délais très long</li> <li>Durée fabrication IHP 130 de 5 mois &gt; IHP 250.</li> <li>Durée fabrication XFAB estimée à 6 mois.</li> </ul> | D. Prêle                   | <b>*</b>  | <b>→</b> |

|                                  |                                                                                                                                                                               |                            |           |          |

|                                  |                                                                                                                                                                               |                            |           |          |

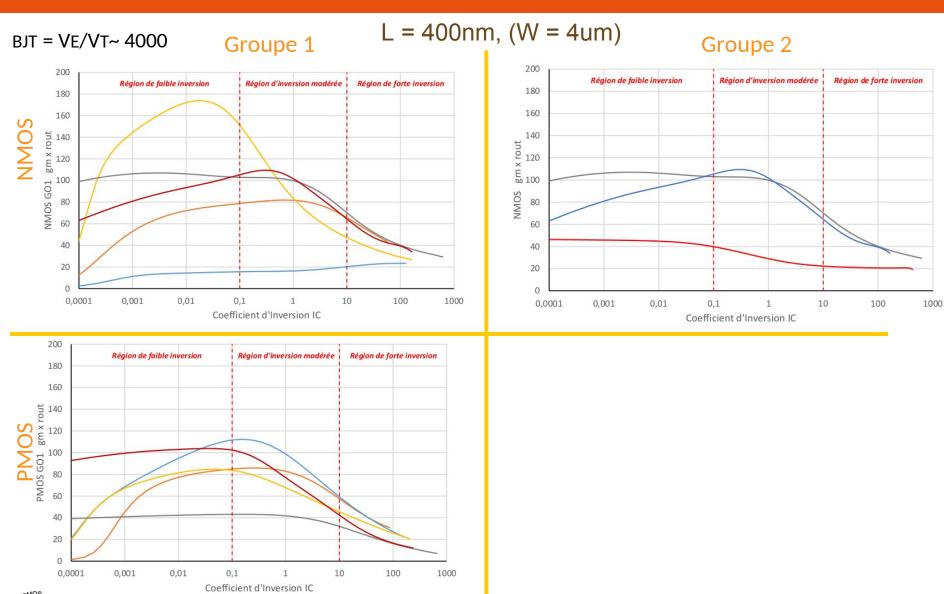

## Avantages/inconvénient d'un Transistor BJT / CMOS

#### **Avantages**

- Bruit série meilleur que le MOS

- gm/lc = 1/Vt ~ 40 constant et supérieur à gm/ld MOS à surface équivalente

- bruit en 1/f bien meilleur que les MOS : intérêt pour ATHENA/CMB S4, pour les CSA lents (NECTAR).

- grand r\_out = V<sub>E</sub> / Ic

#### Inconvénients

Présence d'un bruit parallèle : shot & flicker noise de base

#### Conséquences

- faible bruit sur impédance de source faible :

- détecteurs fortement capacitif : détecteurs Si GANIL, photovoltaïques ou faiblement capacitif mais à hautes fréquences

- détecteur faiblement résistif : SQUID

- produit gain-bande élevé

- Bande passante élevée

- permet des taux de contre réaction élevé, donc faible dérive en température, meilleure linéarité, plus faible dispersion

Etages de puissance

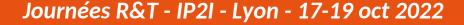

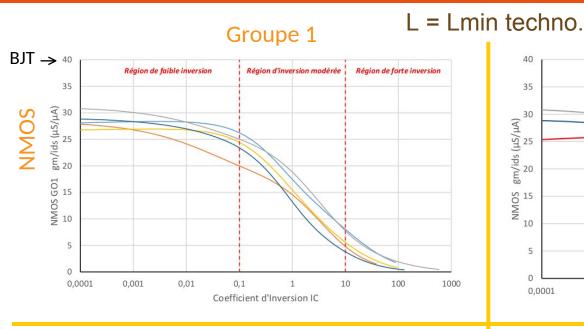

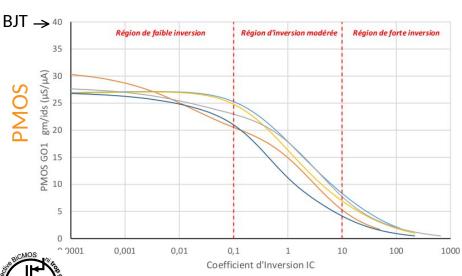

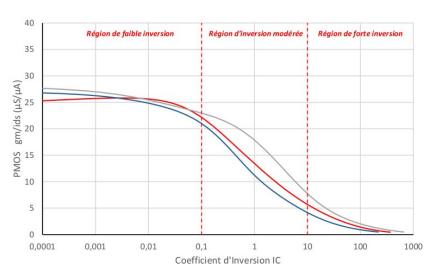

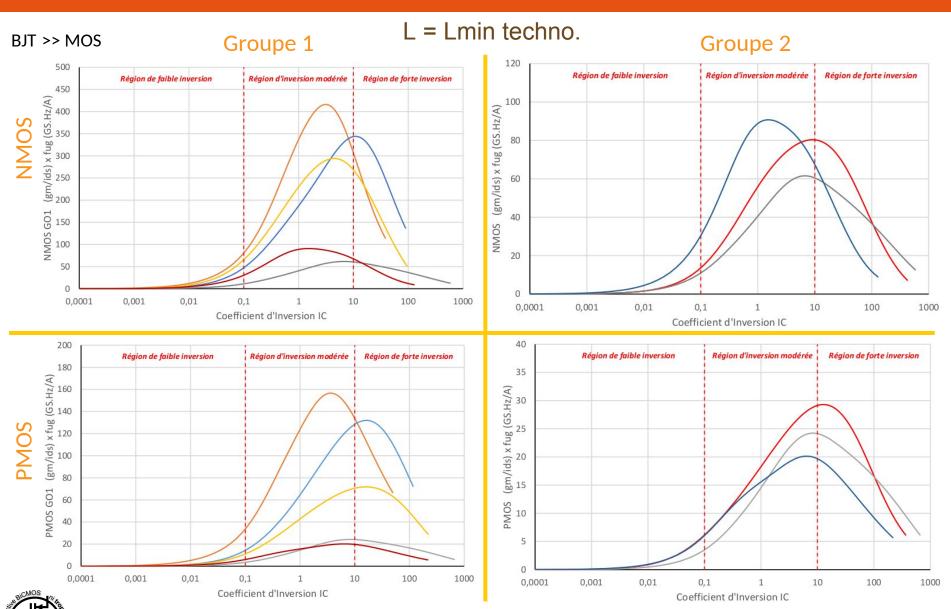

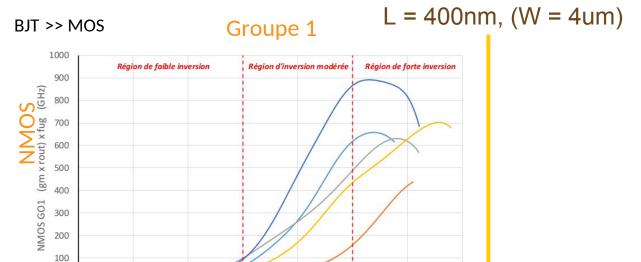

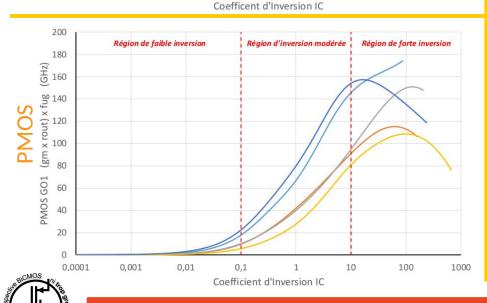

#### Facteurs de mérite des MOS

#### Nmos ou Pmos monté en diode

- simulations DC, variable : V<sub>GS</sub> = V<sub>DS</sub>

- extraction de Id, Vth, g<sub>m</sub>, r<sub>out</sub>, f<sub>T</sub>

#### Quelques facteurs de mérite

- Efficacité de transconductance : gm/ld

- Efficacité de vitesse : f<sub>T</sub>.gm/ld

- Gain intrinsèque : g<sub>m</sub>.r<sub>out</sub>

- Produit Gain-Bande: f<sub>T</sub>.g<sub>m</sub>.r<sub>out</sub>

#### Expression des facteurs de mérite en fonction du coefficient d'inversion IC

- IC =  $I_{DS}/(I_0.W/L)$

- I<sub>0</sub> dépend uniquement de facteur technologique : u, Cox, V<sub>T</sub>

- régime de faible inversion : IC < 0.1</li>

- régime d'inversion modérée : 0.1 < IC < 10</li>

- régime de forte inversion : 10 < IC</li>

#### Technologies évaluées :

TSMC 130, IHP 130, IHP 250, TSI 180, AMS 350, ON SEMI 350, ST 130 ...

# Transconductance efficiency : $g_m/I_d = f(IC)$

# Speed efficiency : $f_T.g_m/I_d = f(IC)$

# Intrinsec gain : $g_m.r_{out} = f(IC)$

# Gain bandwidth product : $f_T.g_m.r_{out} = f(IC)$

Groupe 2

10

100

1000

0,1

0,0001

0,001

0,01

## Facteurs de mérite, briques de base

#### Travail à finaliser

- facteurs de mérites 'bruit' et 'dynamique'

- avec les MOS XFAB et ST

- avec les transistors bipolaires

#### Identification de quelques briques de bases à développer

- Bloc pour mesure de densité spectrale de bruit de transistors dès le Hz

- paramètre qui est généralement mal modélisé

- argument important sur la justification d'une technologie BiCMOS

- CSA configurables,

- source de courant bas bruit

- ampli de tension bas bruit,

- OTA

- amplificateur de puissance

- •

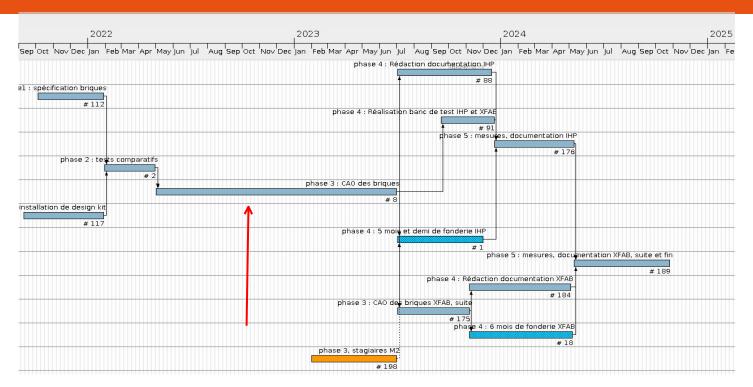

#### Calendrier

- Jalon fort : dates fonderies, IHP 130nm juillet 2023 et XFAB 180nm oct. 2023

- tâches principales

- comparaisons de techno. CMOS/BiCMOS par des facteurs de mérites

- CAO de briques de bases

- carte de test et mesure des circuits, documentation

- => validation d'une technologie 'pérenne' et 'low cost' pour la communauté

- => publication IEEE « Transactions on Circuits and Systems »

### Merci pour votre attention