# **PICMIC** status

I.Laktineh on behalf or the PICMIC groups IP2I, IPHC,IJCLAB,CPP

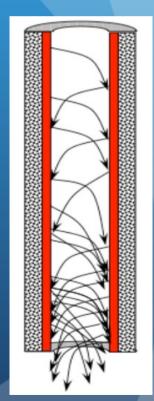

## Micro Channel Plate (MCP)

- MCP is considered as the best timing device with a few picoseconds of time resolution.

- Most often there are two plates with the channels oriented in a slightly tilted way (chevrons) to increase the gain and at the same time reduce the ion return impact.

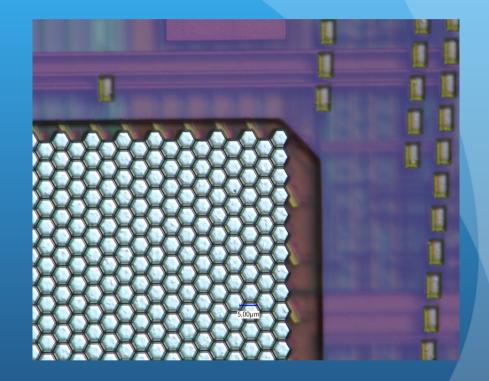

- MCP has an excellent intrinsic spatial resolution since the avalanche produced by the incoming particle is constrained to one of the glass tube whose diameter can ba as small as 2 µm

- MCP are often used for their timing while their spatial resolution is not appropriately exploited.

CHANNEL S

GI 455

STRUCTURE

- ELECTRODING

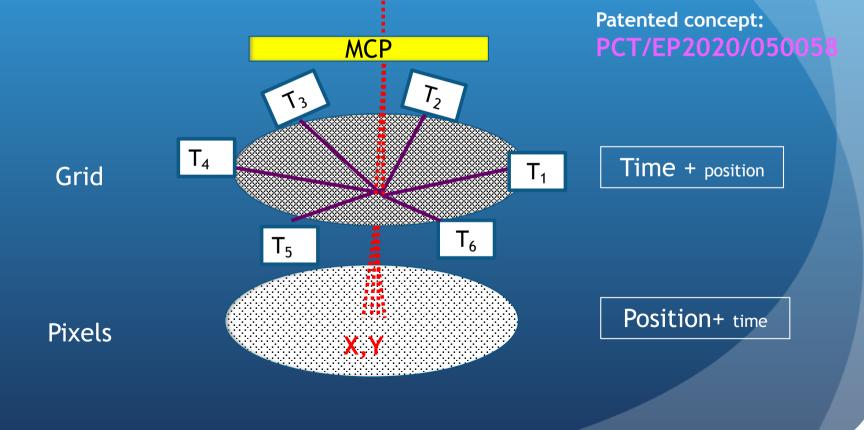

#### To fully exploit MCP we propose the following scheme:

- A transparent grid placed downstream and read out by sensors with excellent time resolution

- A detection matrix with micrometric pixels to measure with great precision the position of the avalanche while requiring limited number of electronics channels.

#### **Concept description**

The avalanche crosses a transparent grid connected on its periphery to a few timing sensors

The avalanche is then collected by pixels

Measure X,Y, from the fired woven strips by crossing them geometrically

2- Measure T\_i (from time sensors)

3-Substract time propagation using speed propagation and X-Y)4- average on the (T\_i-T\_i(propag))

$$\mathsf{T}_{abs} = \frac{\sum_{0}^{N} T_{i} - T_{i-propag}}{N}$$

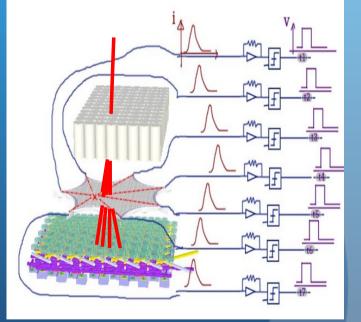

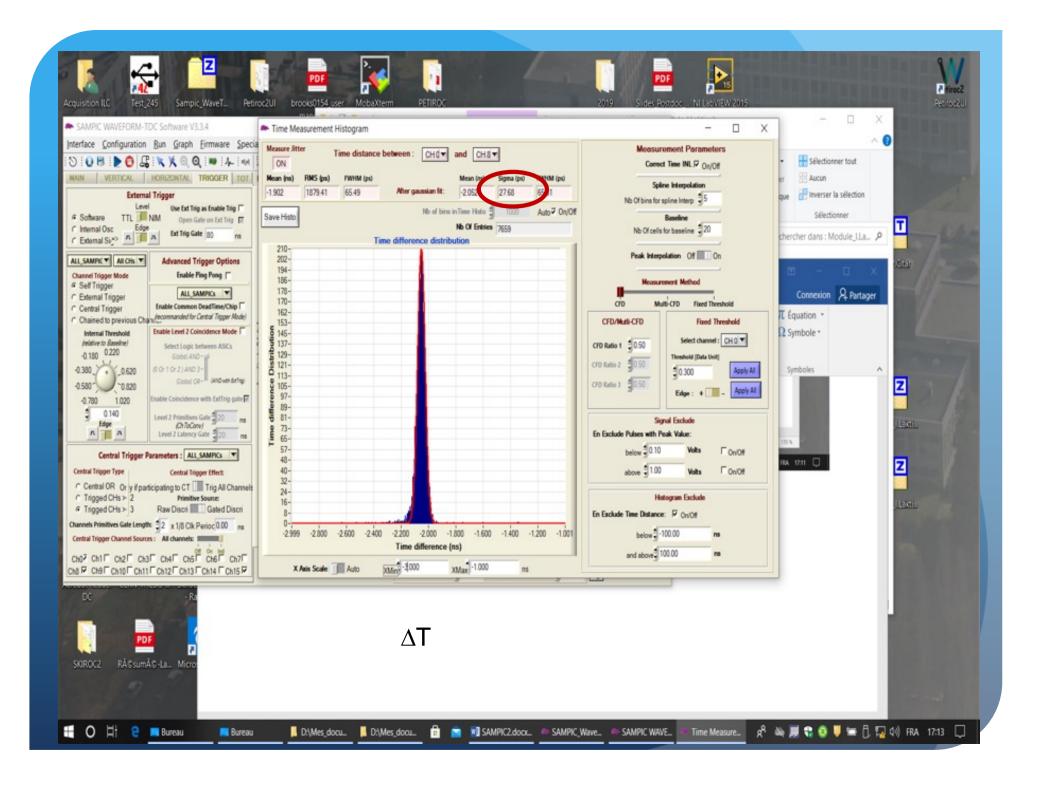

## Time Measurement

#### Principle components for this measurement already exist.

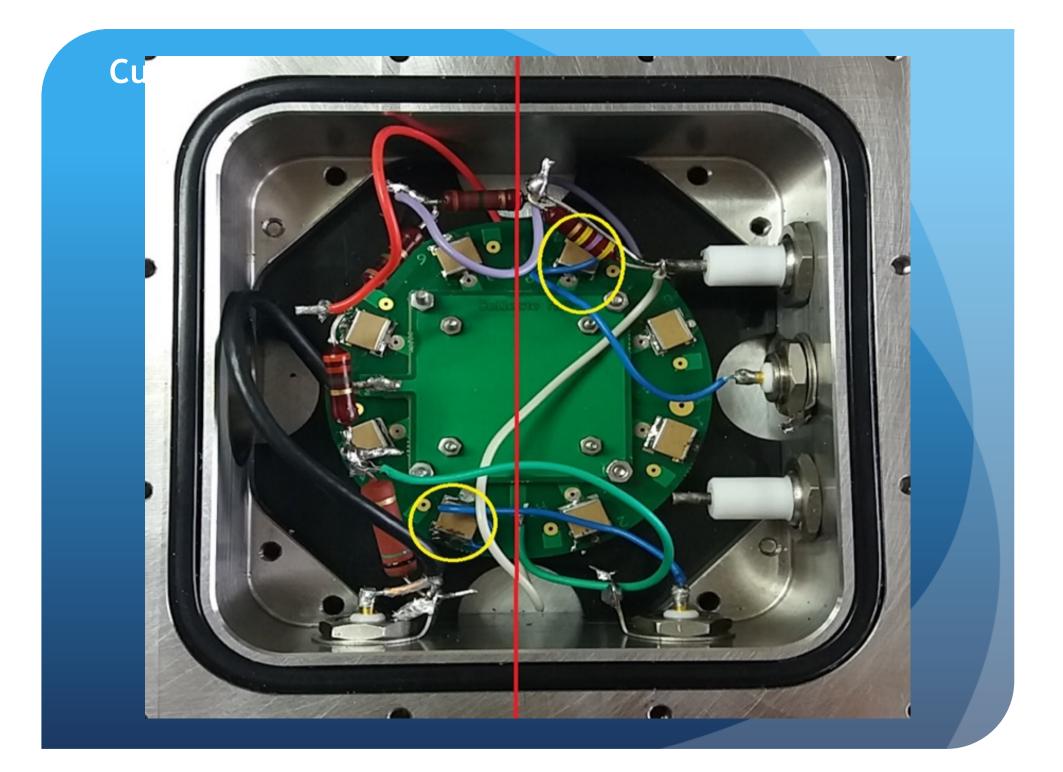

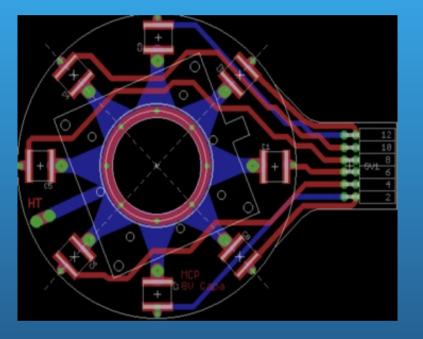

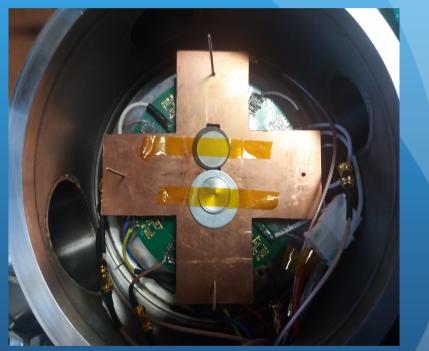

8-point PCB for the time measurement. PCB to be in contact with the grid (already produced and tested) SAMPIC: TDC ASIC allowing to reach 3 ps time resolution

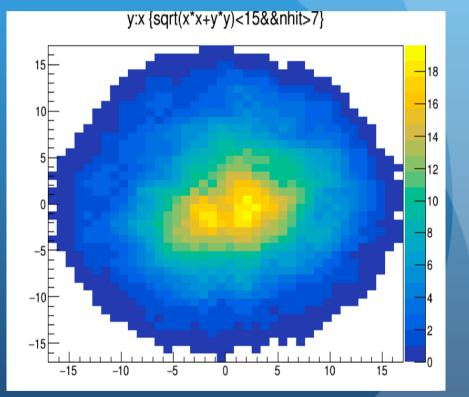

Waiting to have the pixel matrix, two algorithms using the difference of time arrival among the different channels were developed to obtain the position of the hitting particle  $\rightarrow$  a new concept: delay plane

- A new timing PCB equipped with 16 channels was conceived and produced

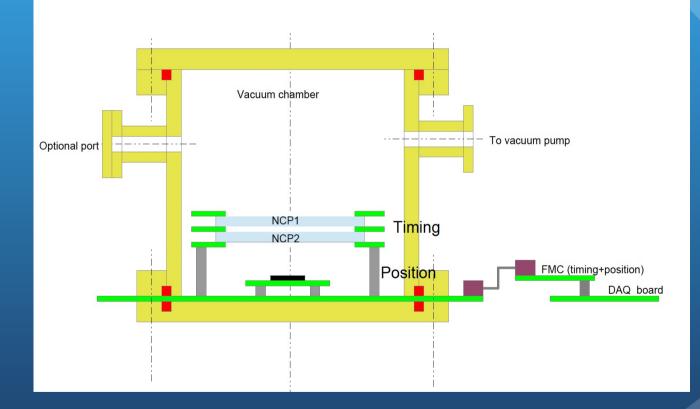

- A new setup thanks to R. Barbier is used to host this large PCB

### Position measurement

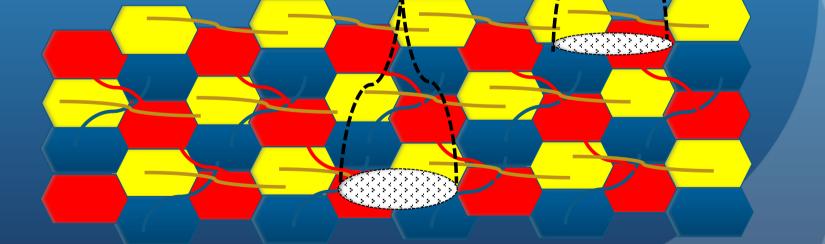

To reach few microns resolution with a limited number of electronic channels, a genuine concept was developed, successfully **tested** and **patented**.

- Connect the pixels in woven strips

- Two neighboring pixels are connected to two different strips

- Each strip is connected to one electronic channel

- Share the charge among a few ones

- □ Crossing the fired strip to determine the position

NXN  $\rightarrow$  3N : Reduction of electronic channels, power consumption and occupancy

## **Position Measurement**

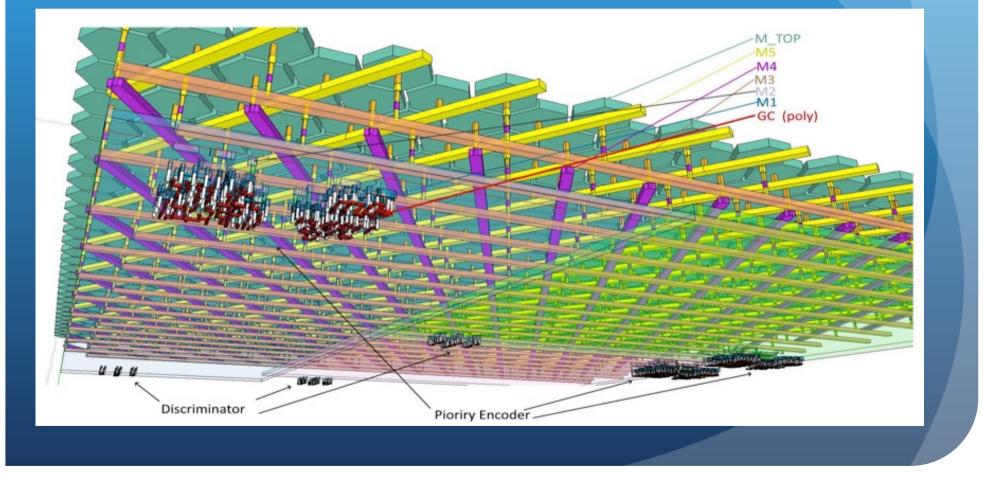

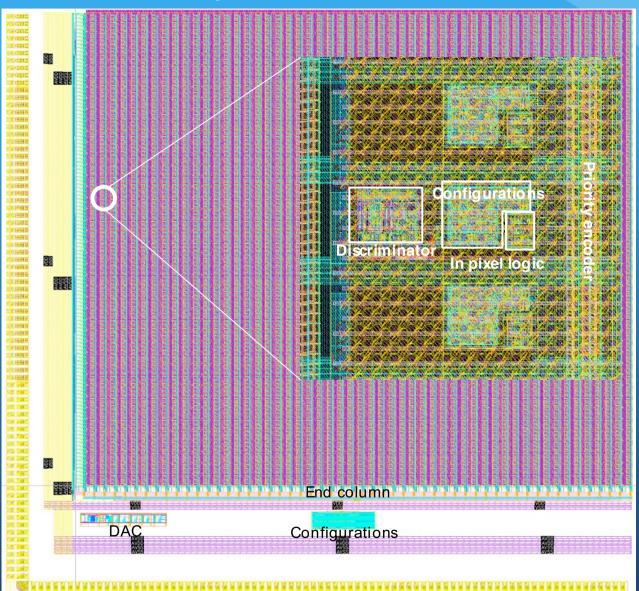

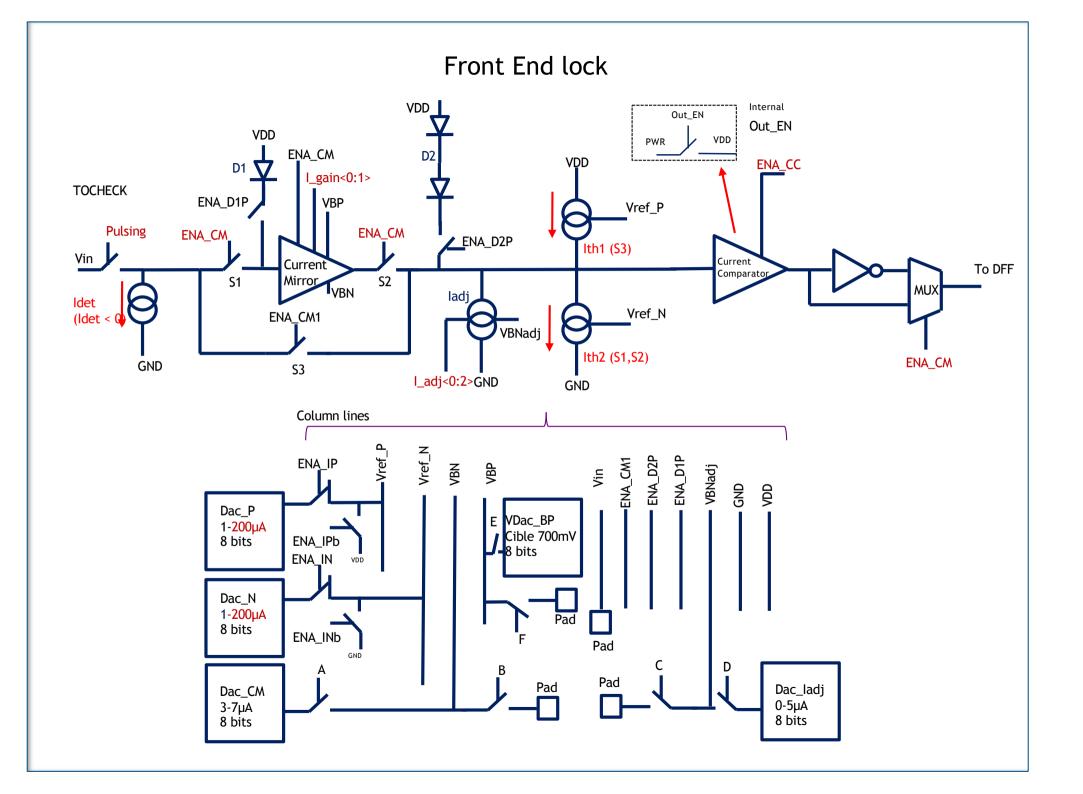

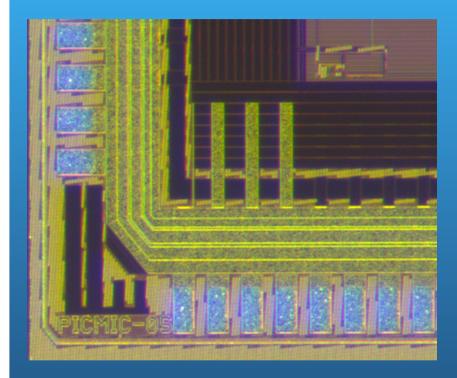

Exploiting the expertise IN2P3 in µelectronics, we propose to read out the connected pixels by CMOS discriminators in TJ 180 nm (6 metal layers) technology.

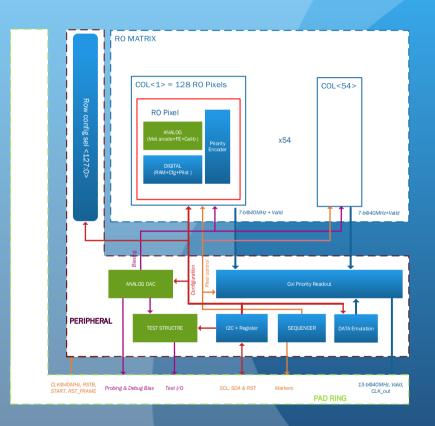

## **PICMIC Architecture**

Priority Encoder

| Parameters                       | Value                                                                                  |

|----------------------------------|----------------------------------------------------------------------------------------|

| Design Flow                      | Cadence DoT flow                                                                       |

| Technology                       | TJ CIS 180nm                                                                           |

| Power supplies                   | 1.8V                                                                                   |

| Power density                    | >172mW/cm <sup>2</sup> (only analog static current)                                    |

| Die dimension                    | ~7.5x7.5 mm <sup>2</sup> (6.5x7.5mm <sup>2</sup> active)                               |

| Anode dimension                  | ~22µ²(5µm hexagonal pitch)                                                             |

| Readout pixel dimension          | 50µmx140µm                                                                             |

| Readout matrix                   | 128x54 cells (only 2556 active)                                                        |

| Input clock                      | 40MHz                                                                                  |

| Read-out port                    | 13-bit parallel, 1 sync clock out, 1<br>marker (programmable 1clk cycle<br>resolution) |

| I/O Pad                          | CMOS                                                                                   |

| Slow control                     | I2C                                                                                    |

| Max data rate (1Mhz hit<br>rate) | 390Mbps                                                                                |

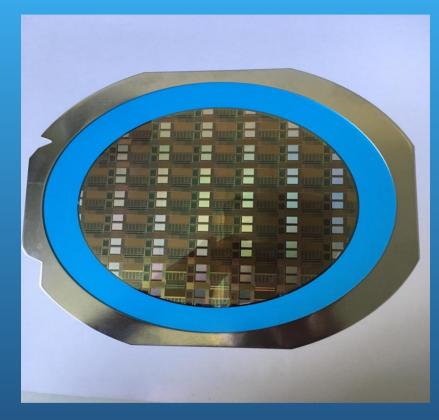

## **PICMIC** Layout

Only 2556 RO cells are active among the 6912

The active RO cells are placed in a way to improve heating dissipation

The 2556 RO cells allow reading out the 2 216 000 pixels

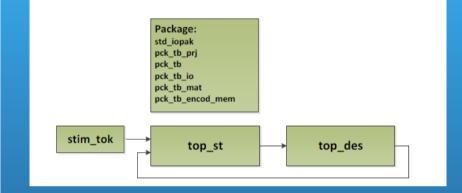

## PICMIC Simulation (Digital Matrix + Peripheral)

□ The simulation validates:

- □ I2C Register R & W

- □ Analog matrix output by different hit patterns

- Output data stream with CTS

| Name  | O▼ Cursor O▼<br>0<br>0 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | K→ DBU_SDA<br>>DIU_SCL<br>⊡>जी drx8b | 1<br>1<br>'h 00 |                                                                        |  |  |  |  |  |  |  |

|-------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----------------|------------------------------------------------------------------------|--|--|--|--|--|--|--|

|       | ess) 'h 0000<br>0<br>0 | 0000 )0051 (0052 (0053 )0054 )0055 (0055 )0057 (0056 )0053 )0058 )0058 (0055 )0055 (0055 )0055 )0055 (0055 )0055 )0055 (0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 )0055 | ⊞ <b>≣e</b> } dtx8b                  | 'h 50<br>'h 0F  | 00 (50 )(37 )(07 )(50 )(50 )(50 )(07 )(07 )(07 )(07 )(07 )(07 )(07 )(0 |  |  |  |  |  |  |  |

| START | U                      | Write Configuration Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                      |                 |                                                                        |  |  |  |  |  |  |  |

#### Output data stream

| DBU_SDA              | 1     |     |    |                |     | Л        |     |     |     |       |    |    |

|----------------------|-------|-----|----|----------------|-----|----------|-----|-----|-----|-------|----|----|

|                      | 1     | uuu | ſ  |                | mmm | U        | mmm | UЛ  | nnn | T T T |    | Л  |

| ti                   | 'h 02 | 10  | 02 |                |     |          |     |     |     | オ     | 03 |    |

| ⊕– <b>€_</b> → dtx8b | 'h 00 | 00  |    | 50             | 09  | 51       |     | 00  |     |       |    | 50 |

| 🗄 📲 🚾 i_state[2:0]   | 'h 2  | 2   | 0  | χ <sub>1</sub> | 3   | $(\Box)$ | 1   | 2   |     |       | 0  | )  |

| Ⅲ, , REG_09[7:0]     | 'h 03 | 03  |    |                |     |          |     | - / |     |       |    |    |

#### Read Configuration Registers

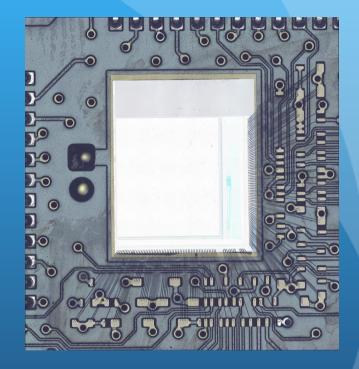

The chip was submitted in November 2021 (TowerJazz) and received on July 2022

# The chip was submitted in November 2021 (TowerJazz) and received on July 2022

#### Tests were carefully prepared by IPHC electronics team.

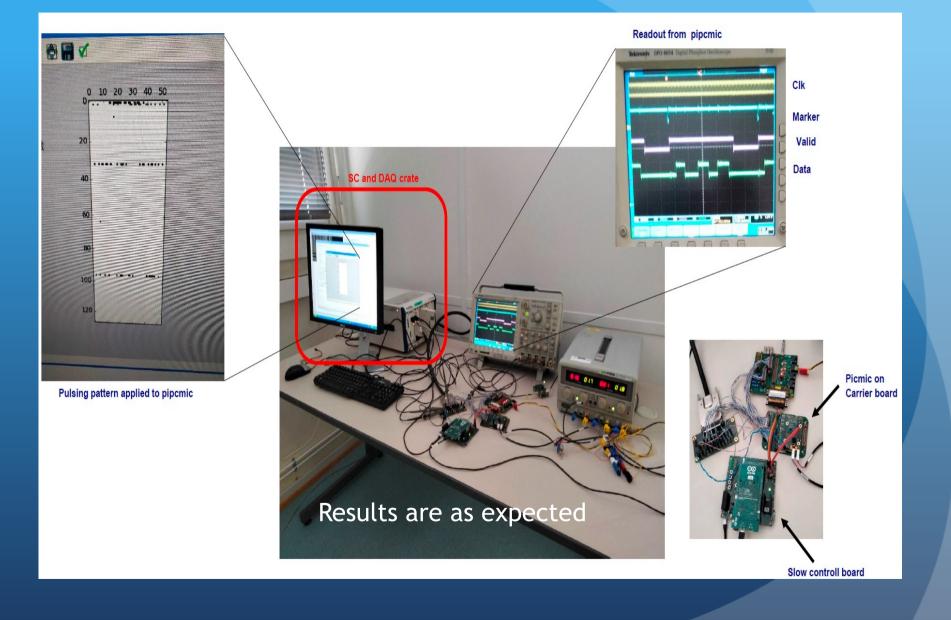

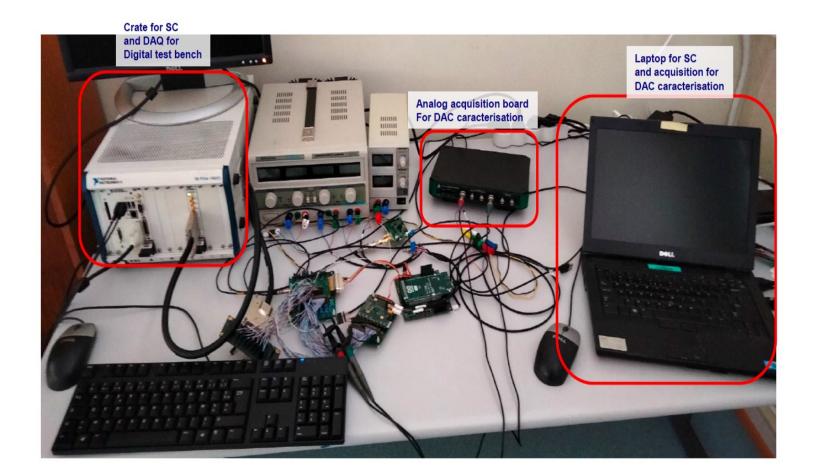

#### A system used for other application was adapted to test PICMIC chip

## Digital test bench

## Digital and DAC characterization test bench

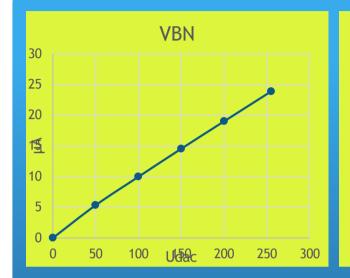

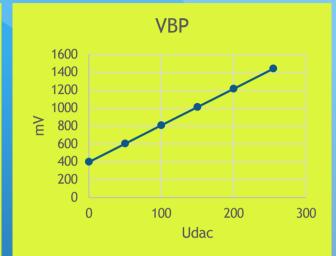

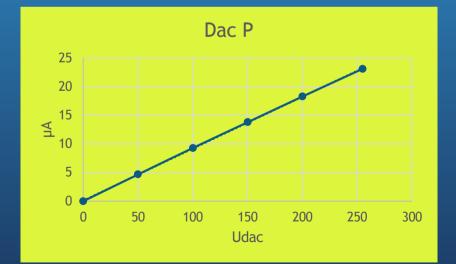

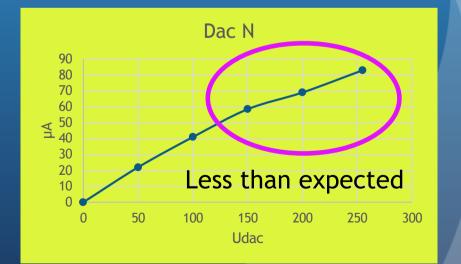

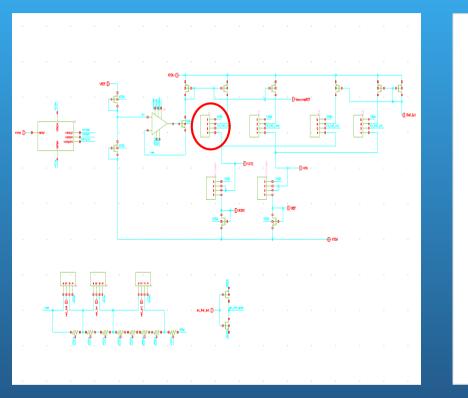

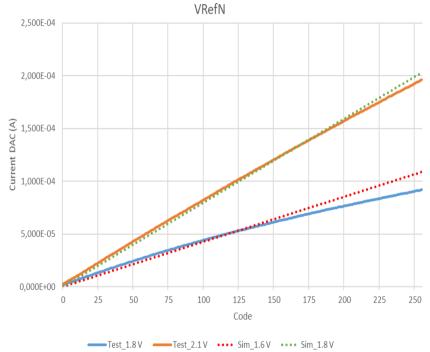

#### DAC measurements

## Problem understood and a solution found

Either increase the VDD from 1.6 to 2 V or use an external DAQ

Next step is to test the sensor using charge injection

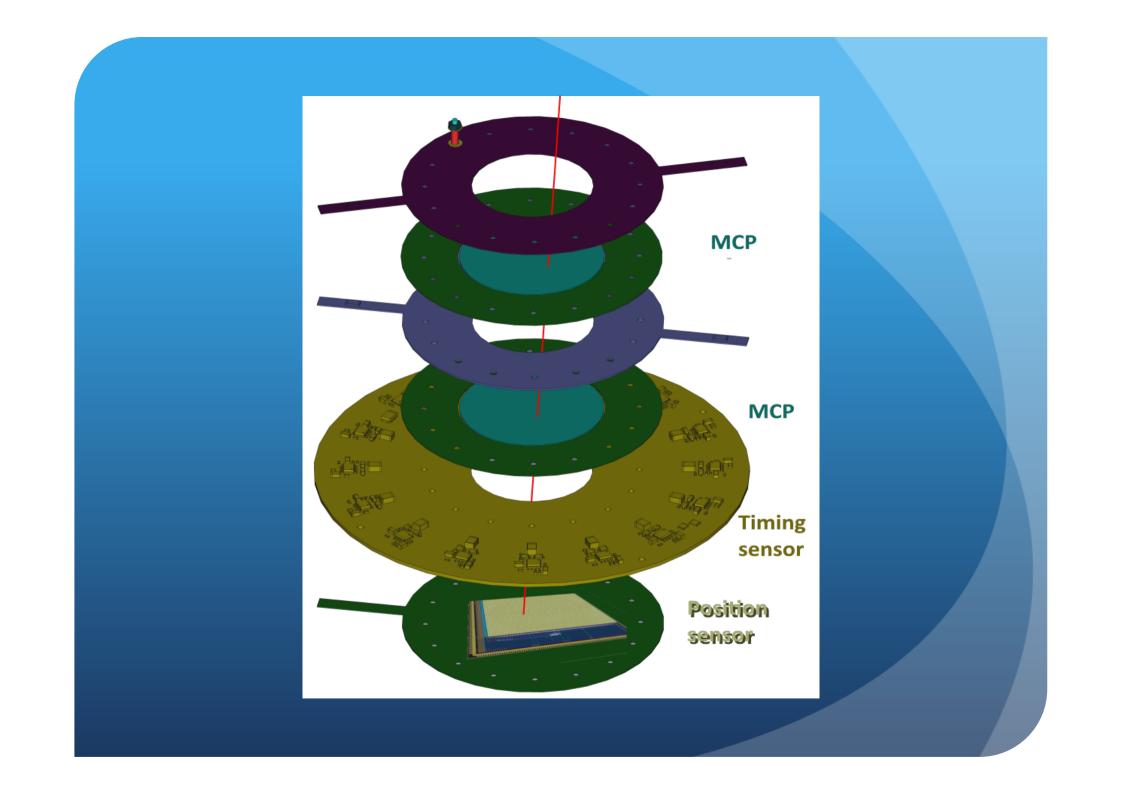

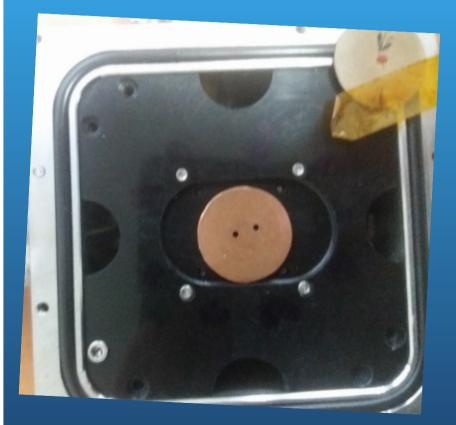

## Towards the first PICMIC demonstrator

The position sensors are being validated, we envisage to build our first prototype

## Towards the first PICMIC demonstrator

The position sensors are being validated, a new board to host the sensor is being designed by IP2I. The design and realization of the first prototype has started.

The first version will use SAMPIC module to

- 1) Measure the time information from the 8 (16) sensors as in the present scheme.

- 2) To distribute the same clock (40 MHz) to both the timing and position chips

- 3) To collect data from both and associate them.

The two last will need a card that be developed By IJCLAB colleagues and placed within the SAMPIC module.

The protocol has been agreed upon among IJCLAB, IPHC and IP2I and the design will start soon

# Next step

SAMPIC is an excellent toot but has dead time of about 1  $\mu$ s.

We envisage to use another TDC with negligible dead time to use PICMIC with higher rate

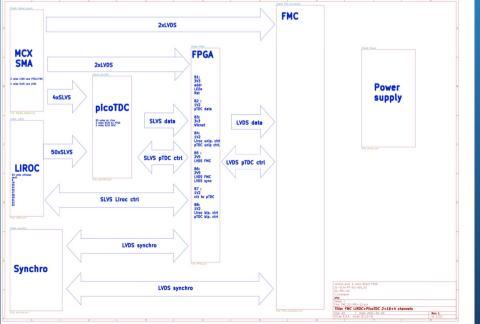

### Next step: Time Measurement

A board integrating a low-jitter timing preamplifier and discriminator (LIROC-OMEGA) as well as a precise TDC (picoTDC-CERN) was conceived. The board will use the GBTX developed by the CERN to communicate with The DAQ system.

The timing board will soon be finalized (all components are available)

## Next step: Acquisition

**IDROGEN board that was** developed within the DAQGEN of the IN2P3 will be used.

To be able to exploit the IDROGEN board we need:

develop appropriate interface/mezzanine boards between the IDROGEN and the timing and position boards.

□ develop an appropriate firmware

This workis now in advanced stage thanks to A. Back and D. charlet from IJCLAB.

# Summary

- Principle of very precise time measurement is ok

- > Principle of very position measurement is being validated

- A first demonstrator using SAMPIC for time measurement and combining both time and position measurements based on SAMPIC DAQ will allow to have the first demonstrator.

- In parallel a new DAQ system using IDROGEN and exploiting the Liroc of OMEGA group and the CERN picoTDC chips are being developed and will be ready early next year.