Frédéric Morel on behalf of C4Pi digital team

## Context (1/2)

#### Starting point:

- ♥ The need of a digital bloc for the decoder of the DAC

- ♥ Can we try to implement the digital flow?

#### Final point:

- ♥ Development of small blocks with a final integration in Virtuoso

- Scripts following best practices in digital design

#### Purpose of this presentation:

- Use It is mainly a translation of the documentations provided by Tower

- ☼ To ease and to speed up, digital flow setup

- There are "bugs" in digital PDK to be compatible with Virtuoso

- ♥ Sorry, there are a lot of technical details

### Context (2/2)

- Implementation of a small block for DAC

- ♥ No IO have been used

- ♥ No memories have been used

- Two kinds of methodology tested:

- Stylus Common-UI with home made scripts based on OA libraries

- Stylus Flowkit 2.0 methodology based on LEF libraries

- Write flow template command:

- □ write\_flow\_template -type stylus

- □ -tools {

- genus innovus quantus tempus voltus}

- □ -enable feature {

- opt\_postcts\_split opt\_postroute\_split opt\_signoff

- report\_static\_ir report\_dynamic\_ir

- sta\_glitch sta\_eco }

- □ -optional\_feature

- report\_inline

- Intermediate step saved in innovus database format (default in flowkit)

- Final layout view saved in OA from innovus

# Stylus Flowkit (1/2)

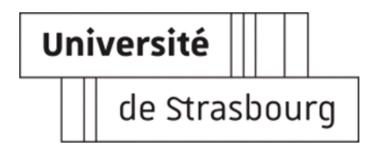

# Motivations - Why Stylus? 3 different components

© 2019 Cadence Design Systems, Inc. All rights reserved.

26/11/2020

# Stylus Flowkit (1/2)

### Overview of both flows - Stylus Flowkit (FK) Key concepts

- Code generation is performed once

- Allows the user to make arbitrary modifications in a straightforward way

- Simplify the means for adding user content

- No external tools are used

- In particular, makefiles are no longer generated.

- All flow configuration and state is stored in the database

- Includes the history of steps run

- Easy to figure out the flow that has produced a particular result.

- Can restart the flow from a saved DB

- Flow control and "shopping-list" using friendly YAML markup language

- Only available in Stylus Common-UI

10 © 2019 Cadence Design Systems, Inc. All rights reserved.

cādence°

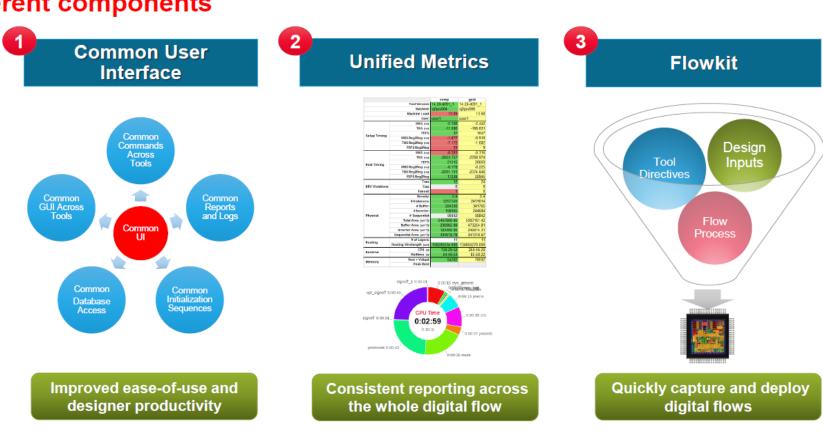

### MIMOSIS1 sequencer trial in 180 nm

- MIMOSIS1 is a reticule size MAPS based on ALPIDE for CBM experiment

- Fully reworked digital part to sustain higher peak hit rate without trigger

- A robust and versatile sequencer used in several sensors developed at IPHC

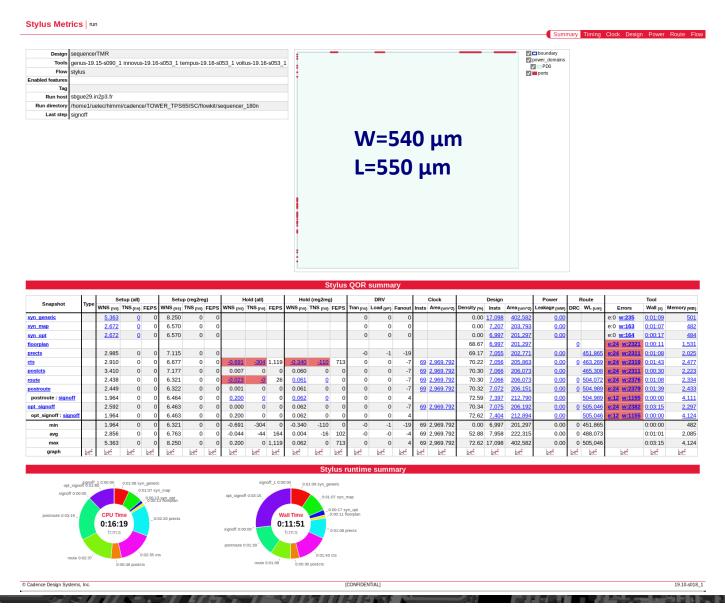

### MIMOSIS1 sequencer trial in 65nm

| Design      |        |             | Power        | Route       |

|-------------|--------|-------------|--------------|-------------|

| Density (%) | Insts  | Area (um^2) | Leakage (mw) | DRC WL (um) |

| 72.62       | 7,404  | 212,894     | 0.00         | 505,046     |

| 75.51       | 10,488 | 74,380      | 2.11         | 292,598     |

#### **Nothing new:**

- Smaller (~3 times)

- Faster (~2 times)

- Less power (60 % less, except leakage)

- Both in 4 metals, no clear impact of M1&M2 for 65 nm standard cells

### Conclusion

- We have gone through all the steps of the digital flow except:

- ♦ Scan chain

- ♥ Macros (IO, memories, home made analog)

- ↓ LEC with conformal (Logical Equivalence Checking)

- ♥ No Digital on Top flow / No hierarchical flow

- We can distribute flowkit scripts as is

- Need to be adapted to your needs

- ♥ Could be a starting point for a common digital flow

- We digest the digital design documentation (not presented here due to NDA)

- Ease the ramp-up

- Need to fix few variables for a common definition

- Delay margins

- ♥ PGV generations (area capacitance, voltage, RC corner)

₩ ..