# Possible contributions to future development in 65nm technology

**Andrei Dorokhov**

10/03/2021

## possible contribution (1)

- Evolution of CE65 chip charge collection R&D and optimization :

- Larger area (now is < 2 mm x 2mm)</p>

- ♥ Different pixel pitch also to be defined after first tests of CE65

- Hexagonal pixels\* (similar to staggered layout in mimosa22AHR, AMS0.35 run in 2010 and in FASTPIX ATTRACT project in 2020) in order to decrease chare sharing in between pixels (3 pixels instead of 4)

- **♦ Technology options...**

(\*) Talk by Gianluca Aglieri Rinella and Walter Snoeys, « Sketches for next submission, Chip Proposals, Floorplan » https://indico.cern.ch/event/1012366/cont ributions/4249722/attachments/2197004/371 4850/20210225\_Chip\_Proposals\_GAR\_WS.pdf

Sketches for next submission Chip Proposals Floorplan

> Gianluca Aglieri Rinella Walter Snoeys

#### Hit rate capability and hexagonal pixels

- Hexagonal pixels: much better approximation of a circle.

- Charge collection in the corner easier as corner is closer.

- Charge division not between 4 but between 3 pixels (-> better for efficiency and window of operation)

- Purpose is not to draw circuit in hexagonal layout, collection electrodes will be on a hexagonal grid, rest remains Manhattan layout

- Thinner sensitive layer make modifications as were done in the 180 nm process more needed.

- Area of a 28 cm column: 1.2 mm<sup>2</sup> (10 μm) or 1.82 mm<sup>2</sup> (15 μm)

- Pixel area: 65 μm² (10 μm) or 146 μm² (15 μm)

#### Hit rate capability:

- Propagation time over 28 cm is minimum ~ 80 ns.

- Area for single independent group of pixels is a fraction of the area of a single column, or a fraction of 1 mm<sup>2</sup>, eg < 0.1 mm<sup>2</sup> for 16 independent sectors

- Can assume maximum one hit in a single independent sector at the same time, but this is an underestimation of the maximum hit rate

- Need good statistical model

## IPHC

## possible contribution (1)

- Evolution of CE65 chip circuit R&D and optimization:

- **♥** Front End circuit:

- Analogue amplifier/SF for analogue information (charge sharing)

- > Digital Pixel: amplifier + discriminator for final pixel matrix

- Stitching considerations(\*) impact for pixel circuit for larger detector:

- Top level rules (additional rules)

- Yield (because of pixel circuit complexity, pixel transistor count ~100, usually only few transistors in imaging applications)

- Layout issues boundaries of repeated blocks (hexagonal pixels for example)

for Stitching

Practical Design Considerations

CMOS Sensor Design Group, RAL

> Speed / power – there is a challenge for ex. If total matrix line is 28cm X 10 cm...

(\*) Experience from RAL, talk by

Iain Sedgwick, « Practical Design

Considerations for Stitching »

https://indico.cern.ch/event/101442

0/contributions/4257813/attachments

/2201756/3724170/Stitching\_Talk.pdf

### IPHC

# Conclusions for possible contribution (1)

- For contributions (1) we already agreed, that we will have manpower to fulfill them

- In addition to that, we may contribute to another analogue block(s), which we already designed in MLR1 run (DACs for ex.)

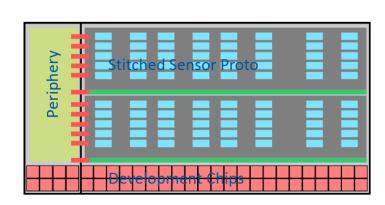

We have expressed our interest in development of stitched sensor prototype for ALICE ITS upgrade (\*)

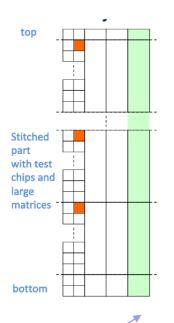

#### Sketch of floorplan

20220225 | TPSCo65 design meeting | Sketches towards next submission

(\*) From talk by Gianluca Aglieri Rinella and Walter Snoeys, « Sketches for next submission, Chip Proposals, Floorplan »

## possible contribution (2)

- Our possible contribution to the development of stitched sensor prototype includes:

- **♥ Study of readout architectures for the stitched sensor (\*):**

- Global strobe with in-pixel storage and zero suppressed readout of binary information steered from the periphery (evolution of ALPIDE)

- Hit-driven asynchronous hit information (position and time) transmission with pulse width modulation or other types of encoding

- Backend design of sensor prototypes

<sup>(\*)</sup> More details in talk by Gianluca Aglieri Rinella and Walter Snoeys, « Sketches for next submission, Chip Proposals, Floorplan »

#### IPHC

# Conclusions for possible contribution (2)

- We have strong motivation to do contribution (2)

which are inline with ours future R&D

- Need still to define our resources and availability...