Maxime Morenas/OMEGA on behalf of ATLAS HGTD IEEE NSS, 5 October 2020

# ALTIROC1

A 25 pico-second time resolution ASIC for the ATLAS **High Granularity Timing Detector (HGTD)**

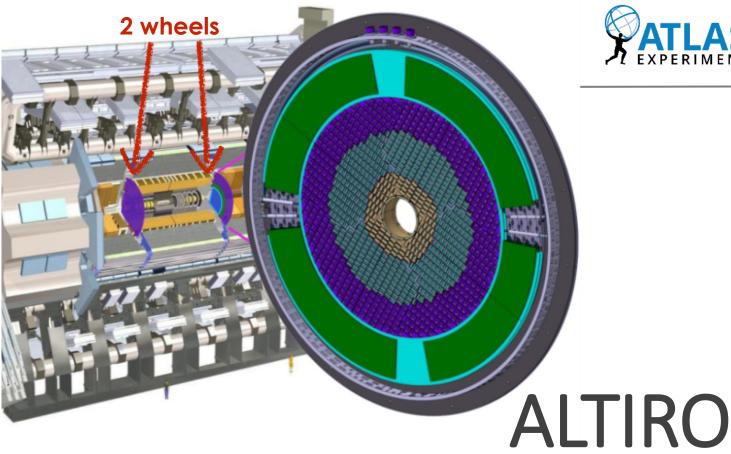

# High Granularity Timing Detector in HL-LHC

### **REQUIREMENTS of the HGTD DETECTOR**

- Luminosity measurement: sum of the hits for each Bunch Crossing

- Time measurement for minimum ionizing particle

with a resolution between 25 ps to 50 ps per track over the detector's lifetime

35 ps to 70 ps per hit

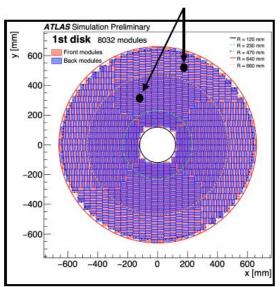

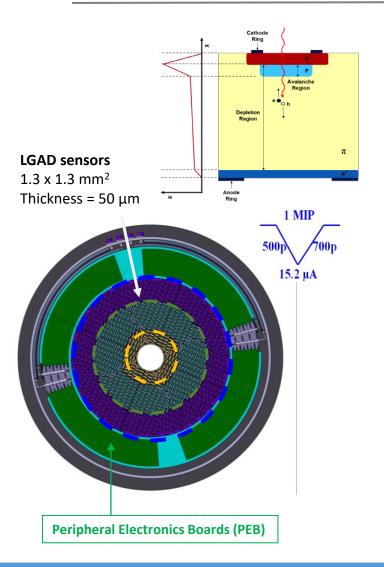

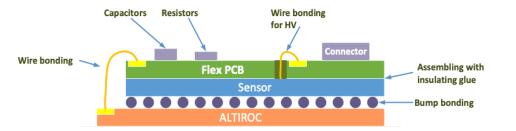

Active area: LGAD sensor bump-bonded onto 2 ASICs (225 channels/ASIC)

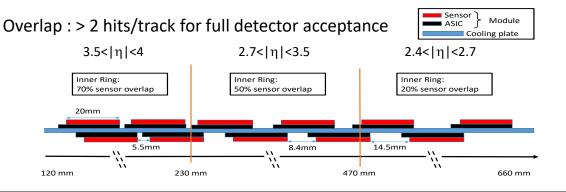

- Inner ring  $\ : 12 \text{ cm} < \text{R} < 23 \text{ cm} (3.5 < \eta < 4.0 \text{ }) \text{ replaced each } 1000 \text{ fb}^{-1}$

- Middle ring : 23 cm< R< 47 cm (2.7 <  $\eta$  < 3.5) replaced at 2000 fb  $^{\text{-1}}$

- Outer ring : 47 cm< R< 64 cm (2.4 <  $\eta$  < 2.7) never replaced

Rings replacement allows to keep:

- $2.5 \times 10^{15} n_{eq}$ /cm<sup>2</sup> max (w/SF=1.5) and TID 2 MGy max (w/SF=2.25)

- Charge in irradiated sensor > 4fC

| Maximum jitter (σ <sub>elec</sub> ) | 25 ps at 10 fC at the start of the HL-LHC and 70 ps for 4 fC at the end |

|-------------------------------------|-------------------------------------------------------------------------|

| TDC contribution                    | < 10 ps                                                                 |

| Time walk contribution              | < 10 ps                                                                 |

| Clock contribution                  | < 15 ps                                                                 |

Main contributors to time resolution

$\sigma_{hit}^2 = \sigma_{Landau}^2 + \sigma_{clock}^2 + \sigma_{elec}^2$ with  $\sigma_{elec}^2 = \sigma_{Time \ walk}^2 + \sigma_{jitter}^2 + \sigma_{TDC}^2$

| TDC conversion time | < 25 ns |

|---------------------|---------|

|---------------------|---------|

| PAD size                     | 1.3 x 1.3 mm <sup>2</sup> x 50 μm => <b>Cdet = 4 pF</b> |

|------------------------------|---------------------------------------------------------|

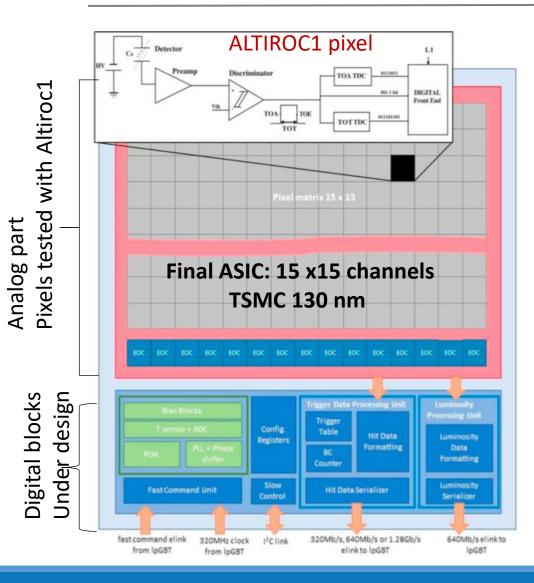

| ASIC size and channels /ASIC | 2x2 cm <sup>2</sup> 15x15=225 channels/ASIC             |

| Single PAD noise (ENC)       | < 3000 e- or 0.5 fC                                     |

| Minimum threshold            | 2 fC                                                    |

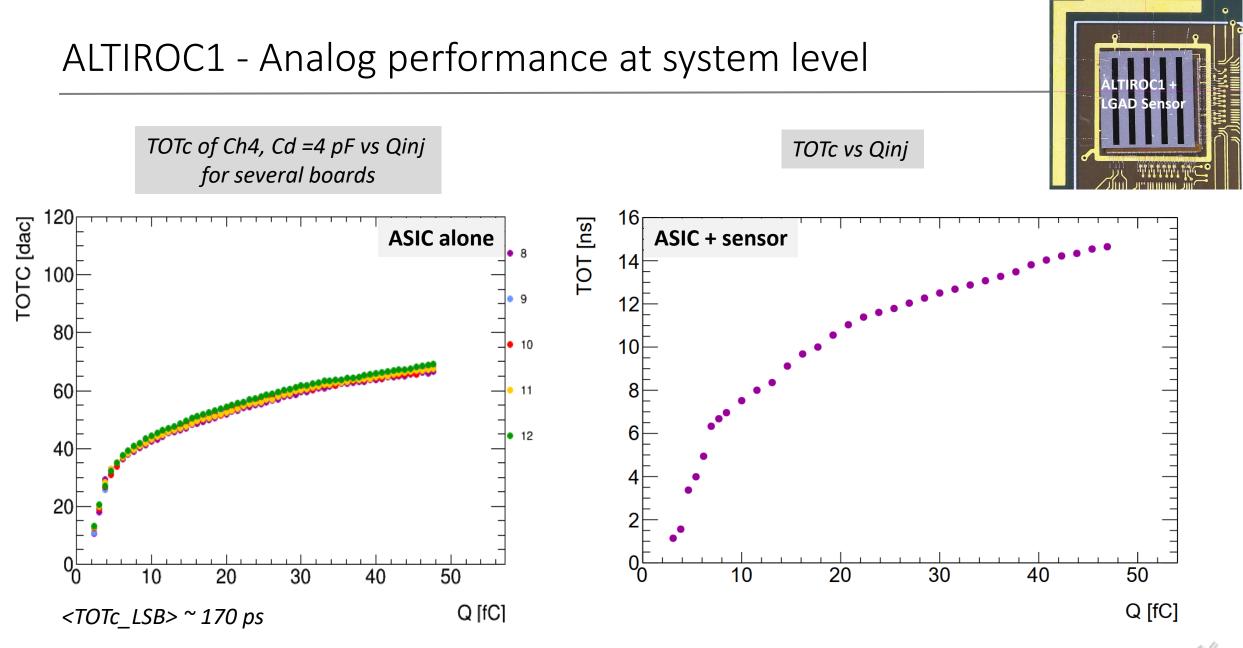

| Dynamic range                | 4 fC to 50 fC                                           |

| TID Tolerance             | <b>2 MGy</b> (inner modules replaced after each 1000 fb <sup>-1</sup> , middle ring after 2000 fb <sup>-1</sup> ) | AS |

|---------------------------|-------------------------------------------------------------------------------------------------------------------|----|

| Full chip SEU probability | < 5 % / hour                                                                                                      |    |

**Voltage and Power dissipation per ASIC** 1.2V and 300 mW cm<sup>-2</sup> => 1.2 W/ASIC (225 ch) or 4.4 mW/channel and 200 mW for the common part

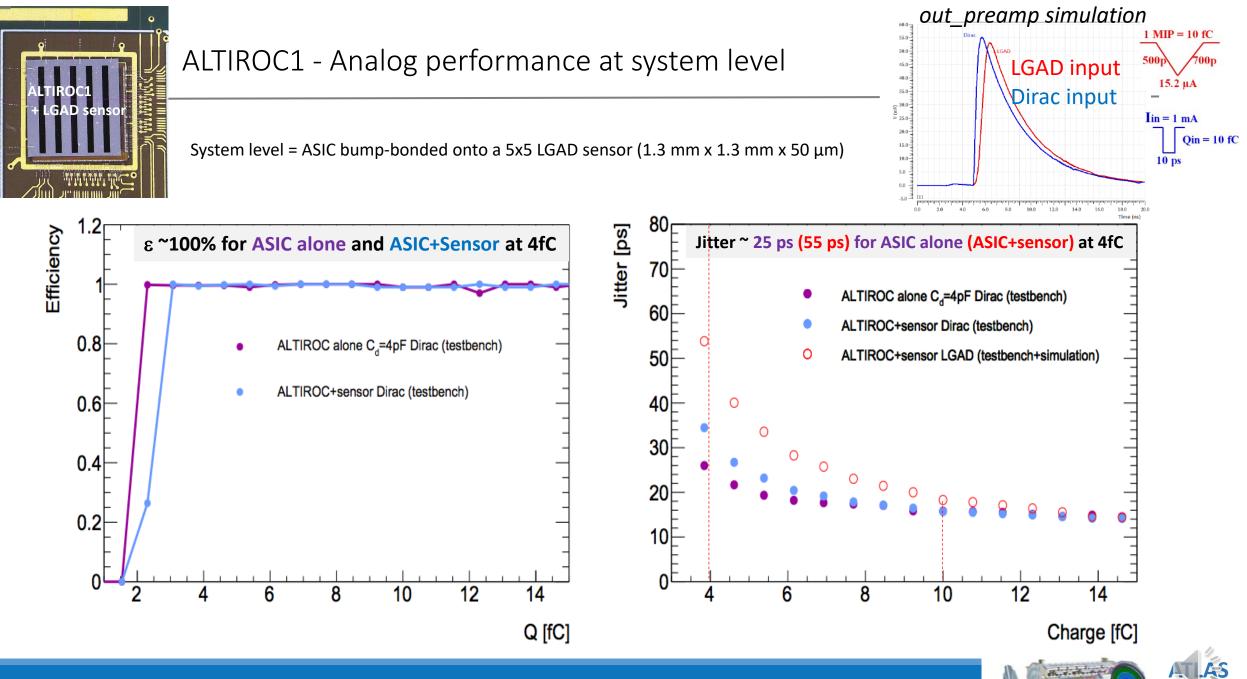

# Front end electronics-ASIC: ALTIROC, analog part

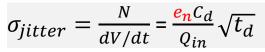

• Main challenge = small jitter (low noise/capacitance) down to 4 fC

#### $\Rightarrow$ Analog FE performance crucial

- $\dot{Q_{in}}$ : MIP charge ( 10 fC at start, 4 fC at end) e<sub>n</sub>: noise spectral density of input trans.

- A voltage **preamplifier** followed by a **discriminator**:

$\Rightarrow$  ALTIROC1 prototypes (5x5 ch), which integrate

- Time walk correction made with a Time over Threshold (TOT) architecture

- **Two TDC** (Time to Digital Converter) to provide digital **Hit data** =Time of Arrival (TOA) + Time Over Threshold (TOT) measurement

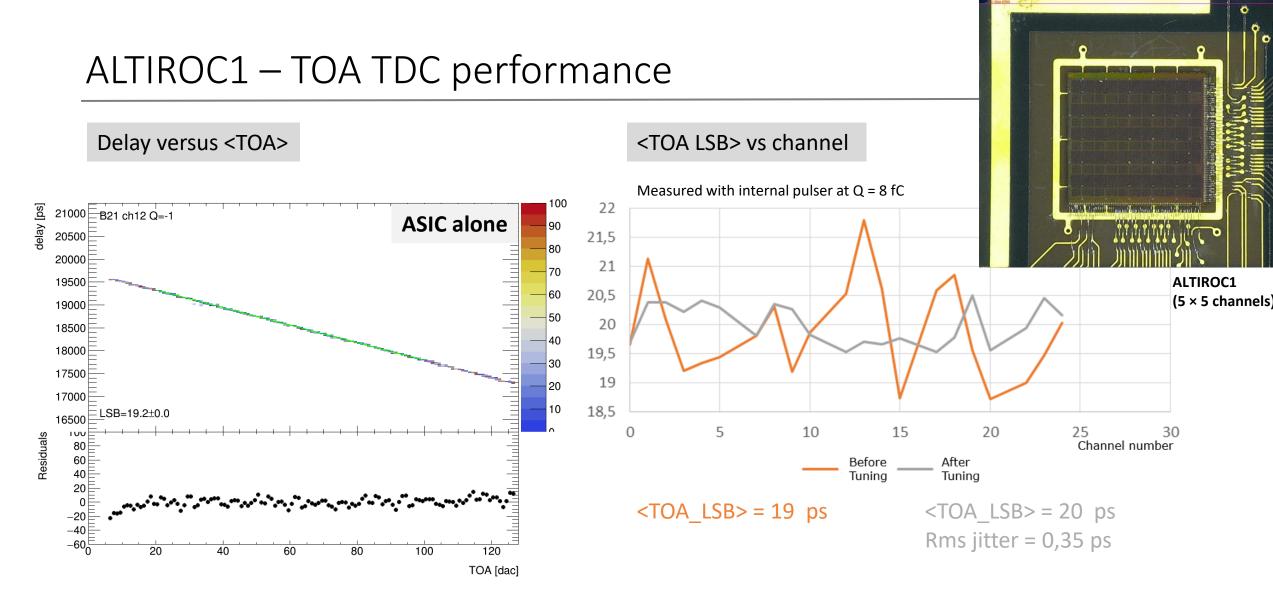

- TOA TDC: bin of 20 ps (7 bits), range of 2.5 ns, to be centered on the bunch crossing

- TOT TDC: bin of 160 ps (9 bits), range of 20 ns

- One local memory (SRAM):

- 17 bits of the time measurement (Hit data) stored until LO/L1 trigger (~ 1 MHz) if hit detected (otherwise 1 bit stored), trigger latency = 10  $\mu$ s in Altiroc1, will be 35  $\mu$ s in full size ASIC (Altiroc2)

- Phase shifter

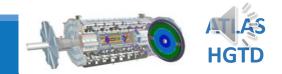

# TOA TDC Architecture : Vernier Delay Line

- START pulse comes first and initializes the TDC operation. STOP pulse follows the START with a delay that represents the time interval to be digitalized.

- At each tap of the Delay Line, STOP signal catches up to the START signal by the difference of the propagation delays of cells in Slow and Fast branches: i.e. 140ps 120ps = 20ps (LSB).

- The number of cells necessary for STOP signal to surpass the START signal represents the result of TDC conversion

- Cycling configuration used in order to reduce the total number of Delay Cells.

- TDC range is equal to 128 \* 20 ps = 2.56 ns

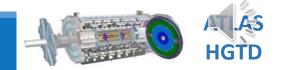

## TESTBENCH

- ALTIROC1 : testbench measurements (ASIC alone or with sensor), irradiation tests, testbeam

- Setup: ASIC board (ASIC alone or bump bonded onto sensor) + FPGA board

- Charge injection (0 up to 50 fC) using ASIC internal calibration pulser controlled by cmd\_pulse input, generated by the FPGA, synchronous to 40 MHz clock

- ASIC alone: Cd=4 pF can be set by SC to mimic sensor capacitor

- External trigger, width and delay tunable by 10 ps steps : used to characterize the TOA and TOT TDC alone

шШ

Altiroc1 tesboard

- TOA\_LSB and TOT\_LSB can be adjusted to 20 ps and 160 ps per channel using Slow Control parameters

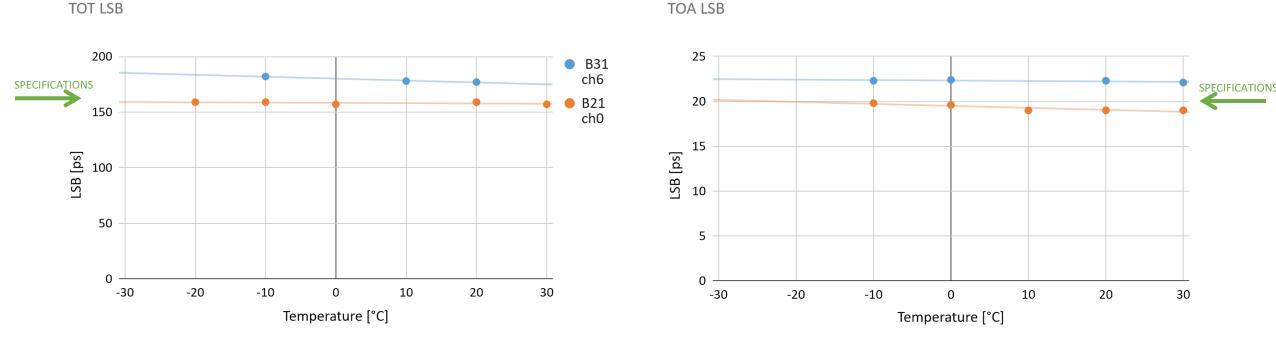

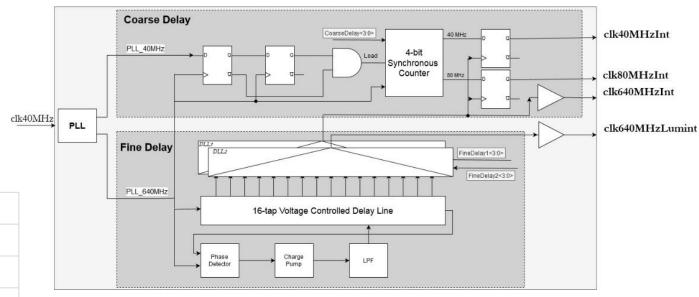

# ALTIROC1 - DLL performance in temperature

3 DLL : Fast (120 ps), Slow (140 ps), Coarse (160 ps)

TDC for TOATDC for TOTAchieving 20 ps LSBAchieving 160 ps LSB

- Different <LSB> because not tuned

- Average temperature variability : below 3%

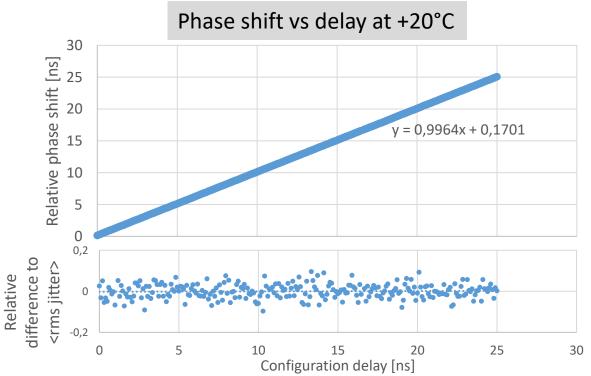

# ALTIROC1 – Phase shifter performance

- Used to center the 2.5 ns measurement time window of the TOA TDC on the Bunch Crossing

- Requirements:

- Step 100 ps ± 10 ps, range 25 ns

- Power dissipation < 10 mW

- Results :

- Shift the 40 MHz clock by steps of 98 ps LSB and range achieved

- <output clock rms jitter><sub>temperature,range</sub>: 14 ps

HGTD

ATLAS HGTD Electronics – IEEE NSS – 05 November 2020

ATLAS HGTD Electronics – IEEE NSS – 05 November 2020

# SUMMARY & CONCLUSIONS

- Good analog performance demonstrated with ALTIROC1 prototypes

- Very useful to understand system issues with sensor

- Jitter (ASIC+sensor) < 35 ps at 4 fC with calibration pulse

- Vth (ASIC+sensor) can be set at 2 fC

- More results about under irradiation tests and testbeam presented by Dr. Yusheng Wu (2 nov.)

- Design of first full size ASIC (ALTIROC2) is on going, submission end 2020

- Mix of Digital On Top (DOT) and Analog On Top (AOT), compromise between power dissipation, timing verifications, analog performance

- Analog performance crucial, floor plan (power distribution, grounding) done AoT

- Tests at system level will be done

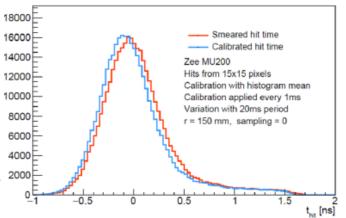

# BACK UP : TOA calibration

Pixels

Goal: measure the same hit time for tracks from the same interaction  $\Rightarrow$  Need to correct various effects :

hit time = TOA\_t0 = t0\_static\_ASIC + t0\_static\_online + t0\_dynamic\_offline

- t0 dispersion inside one ASIC: t0\_static\_ASIC

- Due to ck skew between channels, static dispersion. Offline correction using <u>ASIC internal calibration pulser</u> to have to\_static\_ASIC better than 5 ps

- t0 dispersion between ASICs: t0\_static\_online and t0\_dynamic\_offline

- Due to TOF (η, φ, flex cable length), static dispersion. Online correction using each <u>ASIC phase shifter</u> to adjust the TOA window and so to get t0\_static\_online within ~ 100 ps.

- Due to dynamic variations (drift of 40 MHz clock-RF, temperature ...).

Offline correction using minimum bias physics events to re-adjust each

ASIC t0 and so to have t0\_dynamic\_offline within the needed accuracy

of 10 ps (average of hits done over different integration windows)