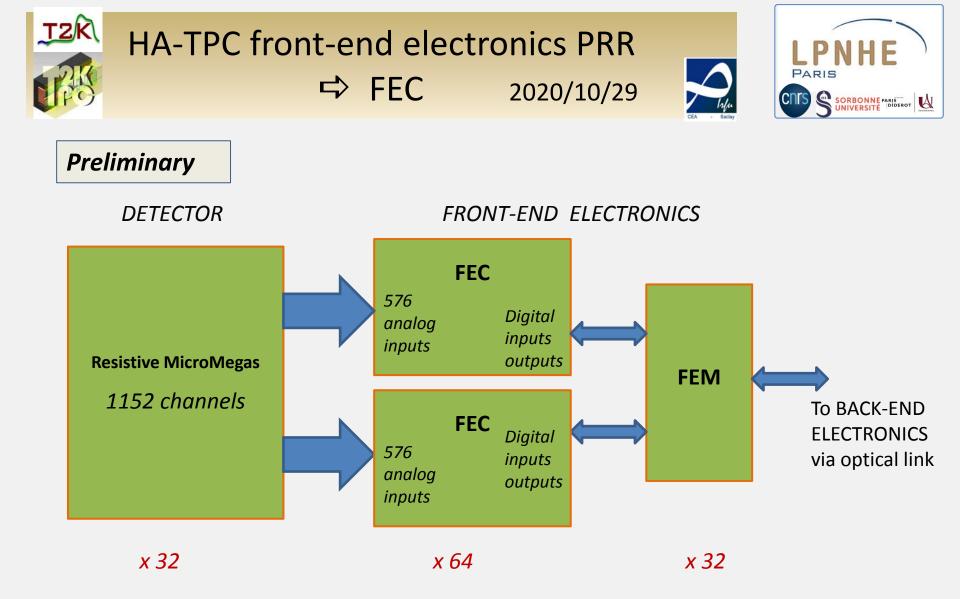

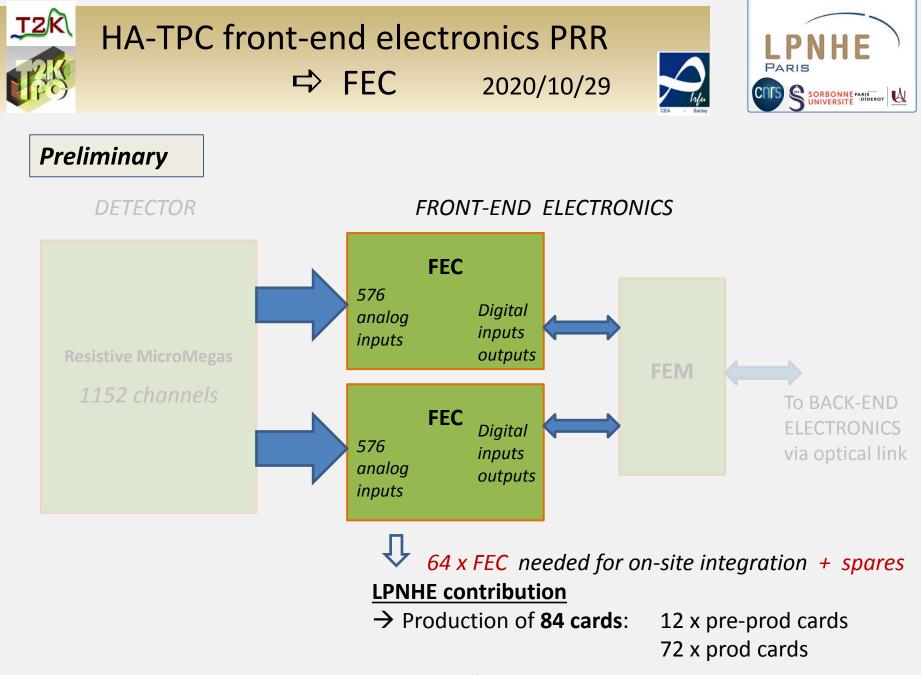

# Front End Card - FEC / T2K Phase2

LPNHE electronics staff : Eric Pierre François Toussenel Jean-Marc Parraud

LPNHE scientist Manager :

**Boris Popov**

Acknowledgements to Denis Calvet and all the IRFU T2K team members for their collaboration

#### FEC / Phase2 :

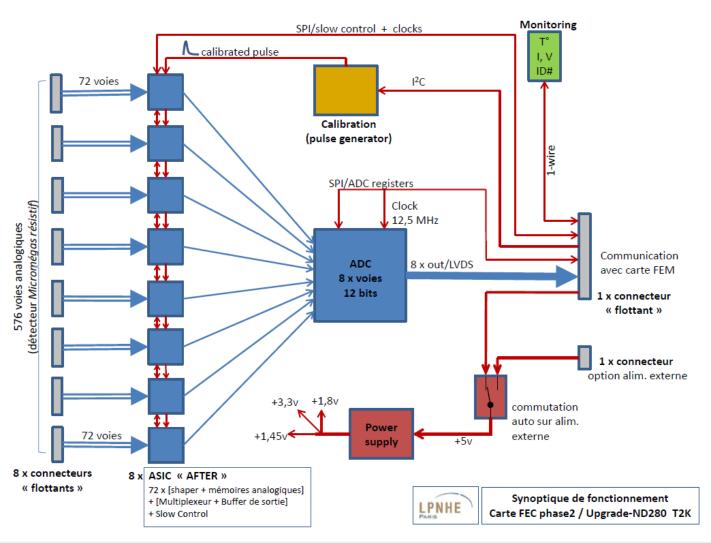

**Based on FEC/Phase1** that works fine for more than 10 years at T2K-Tokai site.

Use of the same ASIC (→ « After » / IRFU) for the read out and processing of analog signals coming from the detector. Qty=8 (qty=4 in Phase1)

Use of an **8 channel ADC** (**AD9637-40**), instead of a 4 channel ADC.

The **global architecture remains the same** as it was in Phase1.

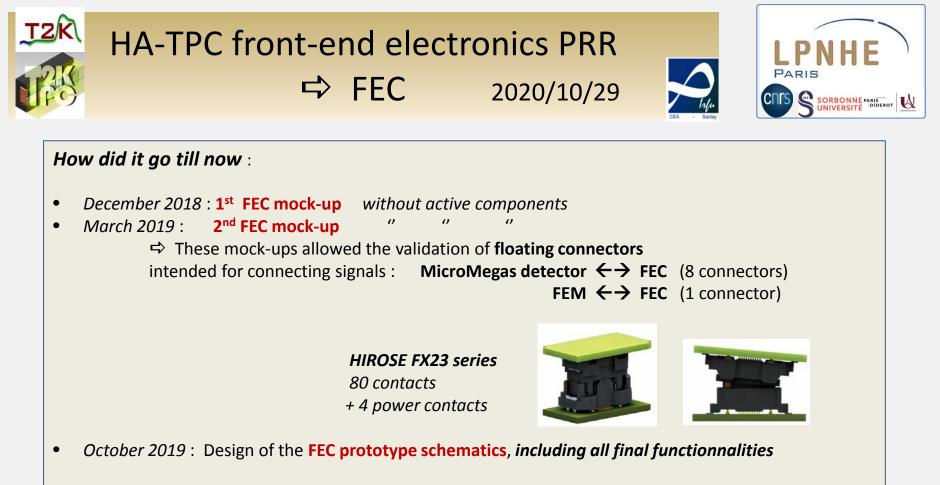

- February 2020 : FEC prototype manufacturing

February to June 2020 : Tests at IRFU with FEM prototype and acquisition system

*worked fine* after few fixes (2 wrong footprints, 1 missing connection on eFuse)

August 2020 : 12 x pre-prod FEC manufacturing, few changes versus prototype mentioned above

- September 2020 : 4 x tested at IRFU with pre-prod FEM and acquisition system

2 x tested at Warsaw with their new testbench

work fine / now waiting for production, qty = 72

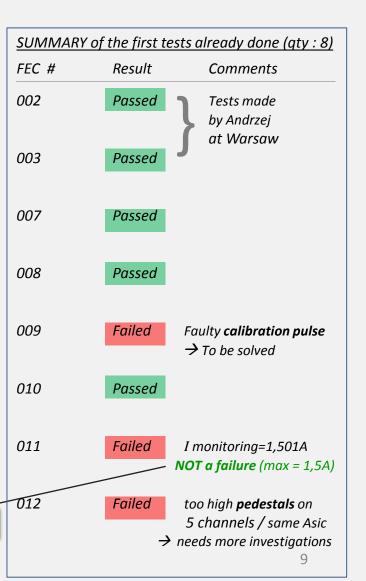

Tests made on FEC prototypes at IRFU

$\rightarrow$  Thanks to Denis Calvet !

$\rightarrow$  Power consumption measurement :  $\approx$  1,5 A / board

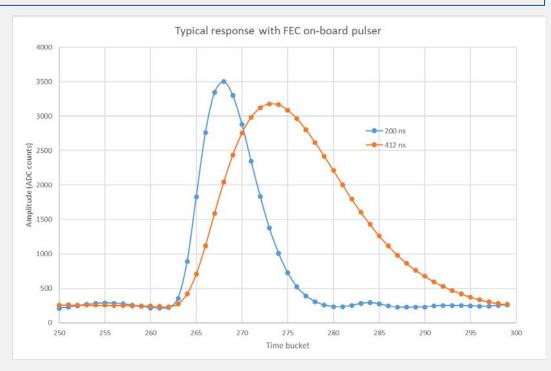

- → Calibration pulse response measurements

- 2 pulse widths injected : > 200 ns > 412 ns

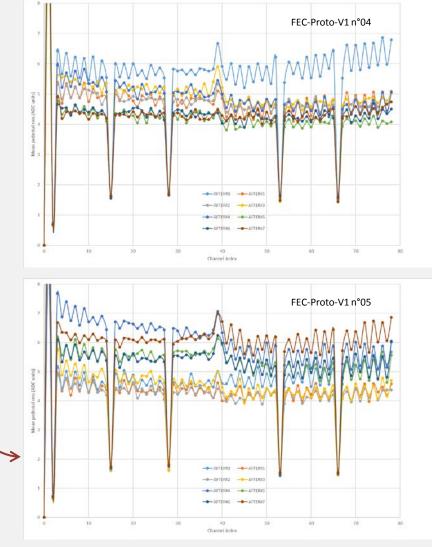

FEC-Proto-V1 n°05

### Tests made on FEC prototypes at IRFU

### → Pedestals measurement

> without shielding> inputs not connected

! AFTER ASIC channels # 0, 1, 2, 15, 28, 53, 66 are NOT data channels

(see document "ASIC After datasheet", P. Baron and E. Delagnes).

### Test Bench intended for FEC production

This testbench has been developed by our colleagues of Warsaw University of Technology, and *delivered to LPNHE one week ago.*

→ Many thanks to our Warsaw colleagues for their good job.

This testbench, including *hardware* and *software*, has been **successfully turned on at LPNHE**.

A few FEC tests have been performed.

>> In order to test the forthcoming FEC, this testbench will be installed at the manufacturer site (*Ouestronic-Rennes*).

FEC in test

### Test Bench intended for FEC production

#### « Passed » example FEC 007 test report / page #1

| Dat  | te: 2020-10-26         | 16:01:30                     |                                        |                   |    |

|------|------------------------|------------------------------|----------------------------------------|-------------------|----|

| Tes  | ster name: Dieg        | jo                           |                                        |                   |    |

| Test | #1 Monitoring value    | s                            | Passe                                  | d                 |    |

| 0    | FEC label              | - 007                        |                                        |                   | OK |

| 1    | FEC DC2438 ID          |                              | e30000024da8fa26                       |                   |    |

| 2    | FEC_T (to 35°C)        |                              | 29.469                                 |                   |    |

| 3    | FEC_Vdd (3.2V to 3.4V) |                              | 3.290                                  |                   |    |

| 4    | FEC_I (1.1A to 1.5A)   |                              | 1.396                                  |                   |    |

| 5    | FEC_Vad (1.9V to 2.0V) |                              | 1.950                                  |                   |    |

|      |                        |                              |                                        |                   |    |

| Test | #2 Slow control reg    | isters:                      | Passe                                  | d                 |    |

| Test | #3 Pedestal run:       |                              | Passe                                  | d                 |    |

| 8    | After chip #8          | Mean OK                      |                                        | STDDEV OK         | ОК |

| 9    | After chip #9          | Mean OK                      |                                        | STDDEV OK         | ок |

| 10   | After chip #10         | Mean OK                      | Mean OK                                |                   | ок |

| 11   | After chip #11         | Mean OK                      | Mean OK                                |                   | ок |

| 12   | After chip #12         | Mean OK                      | Mean OK                                |                   | ок |

| 13   | After chip #13         | Mean OK                      | Mean OK                                |                   | ок |

| 14   | After chip #14         | Mean OK                      | Mean OK                                |                   | OK |

| 15   | After chip #15         | Mean OK                      |                                        | STDDEV OK         | ок |

| Test | #4 AD9637 test pat     | tems                         | Passe                                  | d                 |    |

| 0    | ADC channel #0         | P#1 (Midscale short 2048)    |                                        | MAX 2048 MIN 2048 | OK |

| 1    | ADC channel #1         | P#2 (+Full-scale short 4095) | P#2 (+Full-scale short 4095)           |                   | ок |

| 2    | ADC channel #2         | P#4 (Checkerboard 1365 to    | P#4 (Checkerboard 1365 to 2730 toggle) |                   | ОК |

| 3    | ADC channel #3         | P#7 (One/zero-word toggle)   | P#7 (One/zero-word toggle)             |                   | OK |

| 4    | ADC channel #4         | P#1 (Midscale short 2048)    | P#1 (Midscale short 2048)              |                   | ок |

| 5    | ADC channel #5         | P#2 (+Full-scale short 4095) | P#2 (+Full-scale short 4095)           |                   | OK |

| 6    | ADC channel #6         | P#4 (Checkerboard 1365 to    | 2730 toggle)                           | MAX 2730 MIN 1365 | ОК |

| 7    | ADC channel #7         | P#7 (One/zero-word toggle)   |                                        | MAX 4095 MIN 0    | ок |

| Test | #5 Pulser run          |                              | Passe                                  | d                 |    |

| 8    | After chip #8          | DAC: 483 G(120) ADC(2850     | to 3200)                               | ADC AMPL: 3044    | ок |

| 9    | After chip #9          | DAC: 483 G(120) ADC(2850     | DAC: 483 G(120) ADC(2850 to 3200)      |                   | ОК |

| 10   | After chip #10         | DAC: 483 G(120) ADC(2850     | DAC: 483 G(120) ADC(2850 to 3200)      |                   | ОК |

| 11   | After chip #11         | DAC: 483 G(120) ADC(2850     | to 3200)                               | ADC AMPL: 2966    | ок |

| 12   | After chip #12         | DAC: 483 G(120) ADC(2850     | to 3200)                               | ADC AMPL: 3078    | ок |

| 13   | After chip #13         | DAC: 483 G(120) ADC(2850     | to 3200)                               | ADC AMPL: 3029    | ок |

| 14   | After chip #14         | DAC: 483 G(120) ADC(2850     |                                        | ADC AMPL: 3045    | ок |

| 15   | After chip #15         | DAC: 483 G(120) ADC(2850     | to 3200)                               | ADC AMPL: 3025    | OK |

#### « Failed » example FEC 009 test report / page #1

| Test# |                                           | 0                                      |                              |                                     |    |

|-------|-------------------------------------------|----------------------------------------|------------------------------|-------------------------------------|----|

|       | 1 Monitoring values                       |                                        | Failed                       |                                     | OH |

| 0     | FEC label                                 |                                        | 009                          |                                     |    |

| 1     | FEC DC2438 ID                             |                                        | 6c0000024dc35c26             |                                     |    |

| 2     | FEC_T (to 35°C)                           |                                        | 25.156                       |                                     | 0  |

| 3     | FEC_Vdd (3.2V to 3.4                      | 1                                      | 3.270                        |                                     |    |

| 4     | FEC_I (1.1A to 1.5A)                      |                                        | 1.401                        |                                     | OF |

| 5     | FEC_Vad (1.9V to 2.0                      | JV) 1.3                                | 330                          |                                     | FA |

| Teett | D Claur control regio                     | teres                                  | Deece                        | 4                                   |    |

|       | 2 Slow control regis                      | ders.                                  | Passe                        |                                     |    |

|       | 3 Pedestal run:                           |                                        | Passe                        |                                     |    |

| 0     | After chip #0                             | Mean OK                                |                              | STDDEV OK                           | 0  |

| 1     | After chip #1                             | Mean OK                                |                              | STDDEV OK                           | 0  |

| 2     | After chip #2                             |                                        |                              | STDDEV OK                           | OF |

| 3     |                                           | ter chip #3 Mean OK                    |                              | STDDEV OK                           | OF |

| 4     | After chip #4                             | Mean OK                                |                              | STDDEV OK                           | 01 |

| 5     | After chip #5                             | Mean OK                                |                              | STDDEV OK                           | 0  |

| 6     | After chip #6                             | Mean OK                                |                              | STDDEV OK                           | 0  |

| 7     | After chip #7                             | Mean OK                                |                              | STDDEV OK                           | O  |

| Test# | 4 AD9637 test patte                       | ems                                    | Passe                        | d                                   |    |

| 0     | ADC channel #0                            | P#1 (Midscale short 2048)              | P#1 (Midscale short 2048)    |                                     | OH |

| 1     | ADC channel #1                            |                                        | P#2 (+Full-scale short 4095) |                                     | OF |

| 2     | ADC channel #2                            | P#4 (Checkerboard 1385 to 2730 toggle) |                              | MAX 2730 MIN 1365                   | OF |

| 3     | ADC channel #3                            | P#7 (One/zero-word toggle)             |                              | MAX 4095 MIN 0<br>MAX 2048 MIN 2048 | OF |

| 4     | ADC channel #4                            |                                        | P#1 (Midscale short 2048)    |                                     | Oł |

| 5     | ADC channel #5                            |                                        | P#2 (+Full-scale short 4095) |                                     | OF |

| 6     | ADC channel #8                            | P#4 (Checkerboard 1365 to 2730 toggle  |                              |                                     | OF |

| 7     | ADC channel #7 P#7 (One/zero-word toggle) |                                        |                              | MAX 4095 MIN 0                      | OF |

| Test# | 5 Pulser run                              |                                        | Failed                       |                                     |    |

| 0     | After chip #0                             | DAC: 483 G(120) ADC(285                | 0 to 3200)                   | ADC AMPL: 69                        | FA |

| 1     | After chip #1                             | DAC: 483 G(120) ADC(285                | 0 to 3200)                   | ADC AMPL: 64                        | FA |

| 2     | After chip #2                             | DAC: 483 G(120) ADC(285                | 0 to 3200)                   | ADC AMPL: 72                        | FA |

| 3     | After chip #3                             | DAC: 483 G(120) ADC(285                |                              | ADC AMPL: 63                        | FA |

| 4     | After chip #4                             | DAC: 483 G(120) ADC(285                | 0 to 3200)                   | ADC AMPL: 74                        | FA |

| 5     | After chip #5                             | DAC: 483 G(120) ADC(285                | 0 to 3200)                   | ADC AMPL: 68                        | FA |

| 6     | After chip #8                             | DAC: 483 G(120) ADC(285                |                              | ADC AMPL: 71                        | FA |

| -     | After chip #7                             | DAC: 483 G(120) ADC(285                | 0 to 3200)                   | ADC AMPL: 70                        | FA |

Jean-Marc Parraud / LPNHE Paris

Shielding/cooling plate

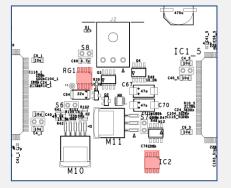

Thanks to the IRFU mechanical team ! >> Zones à refroidir PLAN CABLAGE ELEMENTS FEC PROTO V1 ↓ ¢ FEC cooling : In order to keep a temperature of 25~30°C, cooling is required. **Components requiring** cooling are : - Regulator MIC29502 *P≈2,5W* - Regulator LM1086 P≈0,7W - ADC AD9637 *P≈0,5W* - Asic AFTER (x8) Ð P≈0,5W each Silicone pads

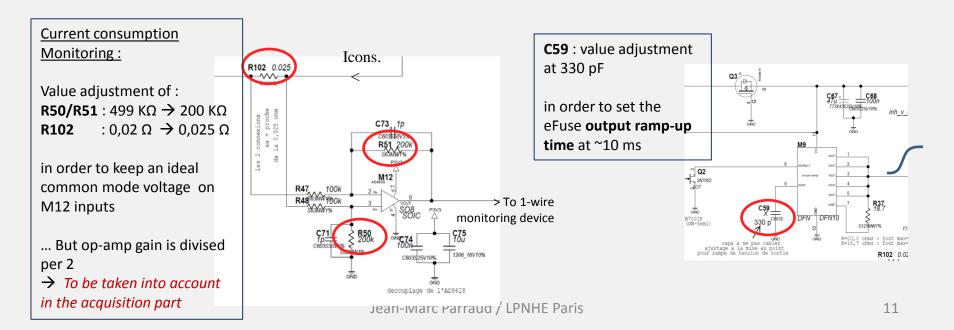

### **Improvements made on FEC**

Following the prototype tests :

> Change of improper **footprints**  $\rightarrow$  IC2 / DS2438 (1-wire monitoring device) RG1 / LP2951 (linear regulator / +1,45v)

> Connection GND  $\leftarrow$   $\rightarrow$  Pad M9 / STEF05 (eFuse) that was missing !

### Following the pre-prod FEC tests :

### Topics to keep an eye on

### Tests in magnetic field :

Because of *Covid-19 pandemic*, beam tests could not take place in October 2020 (DESY) as planned. Thus, pre-prod FEC could not have been tested in a 0,2 T magnetic field.

- → There is an alternative to do this magnetic test at *IJCLab-Orsay*. Date to be determined. (? Covid ?)

- We are rather confident to the issue : *FEC/Phase1* was insensitive to this environment.

*FEC/Phase2* : no magnetic component, only 1 inductor-22 nH for the ADC/1,8v filtering. This inductor is not mandatory and has been placed *as a precaution.* >> It can safely be *replaced by a 0 Ω* resistor if necessary.

#### Analog inputs are not voltage-referenced :

Input pads towards AFTER Asic are not referenced, and may *eventually* be charged at a potential greater than the one accepted by the Asic input.

- → Existing leakage currents on PCB must eliminate this possibility

- ightarrow No damage has never been observed till now

- >> In series capacitors may be replaced by 1 kv ones

- >> As a last resort, a 100 MΩ to GND can be added at each input pad (qty=576 !)

**Planned schedule** : (before Covid-19 containment annoucement)

#### FEC Boards

- November 2020 : Launch of FEC prod (qty=72) to external company (Ouestronic)

- End of February 2021: 1<sup>st</sup> batch of 16 FEC tested and delivered

⇒ These 16 boards are intended to equip the first ½ HA-TPC planned for March 2021

- April 2021 : Last batch of 56 FEC tested and delivered

#### FEC Cooling plates

- November 2020 : 8 plates manufactured at LPNHE workshop

- December 2020 : 8 plates manufactured by external company (Chanteloup Associés)

⇒ These 16 cooling plates are intended to equip the first ½ HA-TPC planned for March 2021

• April 2021 : 64 plates manufactured by external company (Chanteloup Associés)

Risks of delay on the schedule :

• **COVID-19!** Delay on our work at LPNHE in case of sanitary containment

Delay on FEC production  $\rightarrow$   $\bigcirc$  **Ouestronic** was open during previous containment, ... maybe the same for next one

Delay on cooling plates production. *No information about Chanteloup Associés in that case*