# Test Beam 2020/03: **Preparation Meeting**

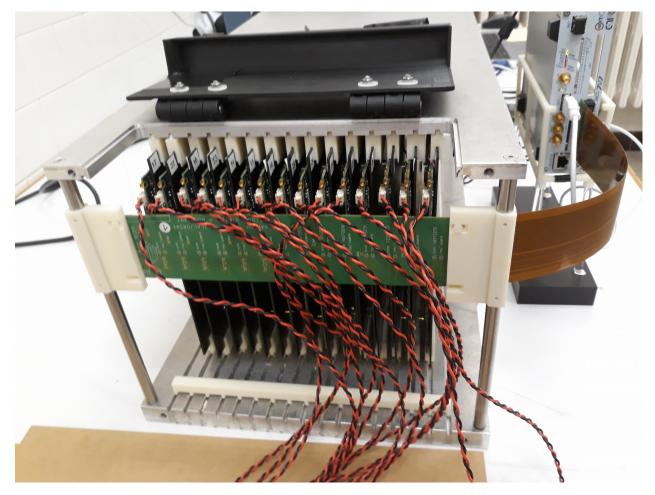

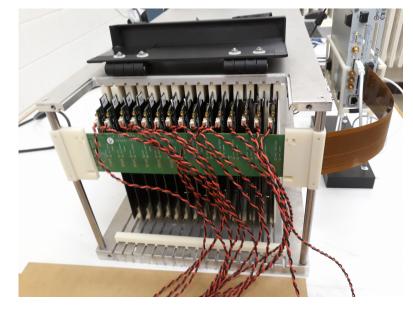

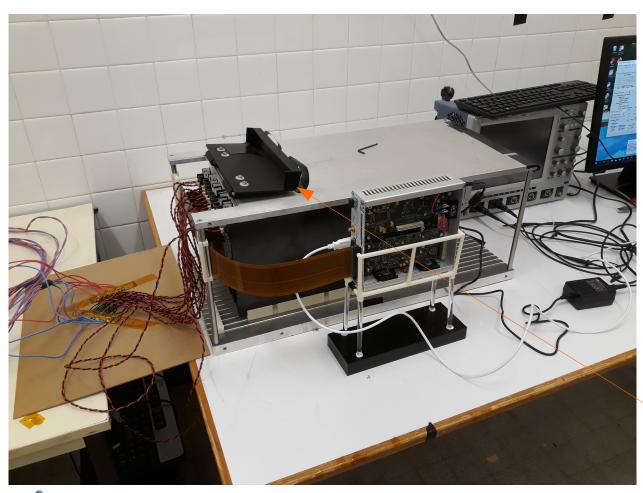

- Stack with 15 operative slabs since the end of the quarantine

- 15000 cells

- 13824 of them are equipped

- Some optimization works were needed to make it run

- For the very first tries we couldn't control more than 8 slabs..

- Solved by improving the power distribution to avoid tension drops

- And by optimizing the clock signal propagation through the kapton core

- By adding the right capacitances in the CoreDaughter (as foreseen)

11<sup>th</sup> February 2020

- We are ready to go to beam test tomorrow if needed.

- For the ffirst time, we have 15 slabs together with common conditions

- same power supply

- Same DAQ

- Same mechanical structure (i.e. same grounding etc)

- Robust and flexible box!

- Easy to cable, uncable, remove or swap positions

- Also robust and flexible slab conception on the carbon frame

- Easy to access to the chips, soldering points,

- Easy to plug or unplug from the SLboard

## **Report on the slabs (I)**

- ▶ Due to the COVID, the new HV kapton sheets didn't arrive on time.

- ► Therefore, the stack has slabs with two types of HV power delivery.

- No difference on perfomance observed so far

### **Report on the slabs (II)**

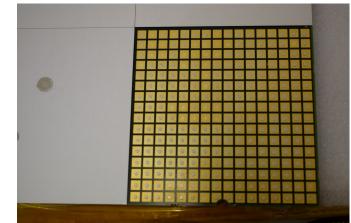

- 4 types of ASUs

- 2 FEV10

- 9 FEV11

- 2 FEV12

- 2 COBs (dammaged at Hybrid)

- 2 version of SK2

- SK2

- SK2

- SK2a

- SK2a

- 2 Si sensor thicknesses

- 320um

- 320um

- 500um

- 500um (only one wafer per ASU)

### **SLAB status (evolution)**

|       |      | DESY 2017 |                  | CERN 2018 |                  |                                                                           |

|-------|------|-----------|------------------|-----------|------------------|---------------------------------------------------------------------------|

|       | SLAB | status    | calibrated cells | status    | calibrated cells | Comments and 2020 status                                                  |

| FEV11 | 13   |           | 0%               |           | 0%               | Glue spilled in the SMBv. Recovered for 2020                              |

| FEV11 | 14   |           | 0%               |           | 0%               | Error in the SR retour $\rightarrow$ fixed                                |

| FEV10 | 15   |           | 0%               |           | 0%               | Recovered but without knowing the original issue                          |

| FEV11 | 16   |           | 92%              |           | ?                | At CERN : low performance on the corners of the ASU and SMB interface     |

| FEV11 | 17   |           | 93%              |           | 95%              | Dellaminated wafers !!                                                    |

| FEV11 | 18   |           | 94%              |           | ?                | At CERN : a pattern of lower MIP values is seen in the center of the ASU. |

| FEV11 | 19   |           | 93%              |           | 93%              |                                                                           |

| FEV11 | 20   |           | 94%              |           | 96%              |                                                                           |

| FEV11 | 21   |           | 54%              |           | 0%               | Stopped working at DESY 2018. Fully recovered for 2020                    |

| FEV11 | 22   |           | 84%              |           | 87%              |                                                                           |

| FEV10 | 23   |           | 0%               |           | 0%               | FEV10 Never used $\rightarrow$ operative now.                             |

| FEV12 | 24   |           | 0%               |           | 0%               | New FEV12 (used in 2019)                                                  |

| FEV12 | 25   |           | 0%               |           | 0%               | New FEV12 (used in 2019)                                                  |

| COB   | 26   |           | 0%               |           | 0%               | Only one wafer and partially dellaminated $\rightarrow$ Hybrid Disaster   |

| COB   | 27   |           | 0%               |           | 0%               | Only one wafer and partially dellaminated $\rightarrow$ Hybrid Disaster   |

### **Commissioning procedure**

A commissioning procedure has been prepared and carefully tested.

- Based on the feature of the DAQ software of producing and reading ASCII configuration files

- Hands-on done

- Automatizable process (i.e. with EUDAQ)

- Within ~3h we can tune up a system of 15000 cells and be ready for beam tests

- For cosmics it takes one or two full days → since we need a much more dedicated masking procedure to cope wit the very low rates of signals.

- All material and tutorials to be uploaded here

- https://twiki.cern.ch/twiki/bin/view/CALICE/SiWDESY202011

- (work in progress!!)

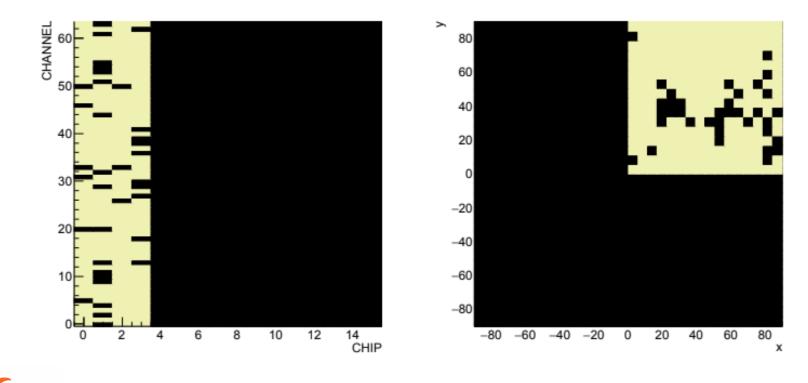

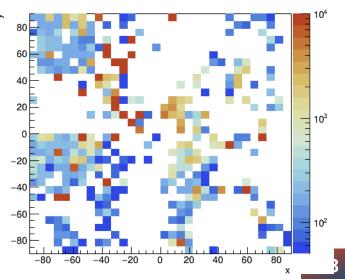

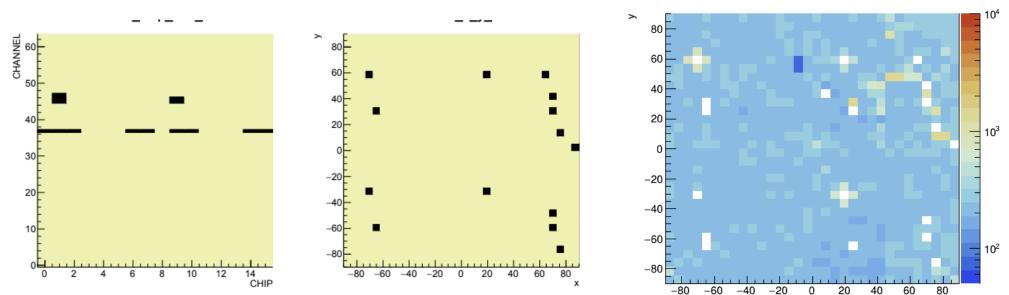

### **FEV12: Results of the masking procedure**

- SLAB 25 (24 is very similar)

- black is masked

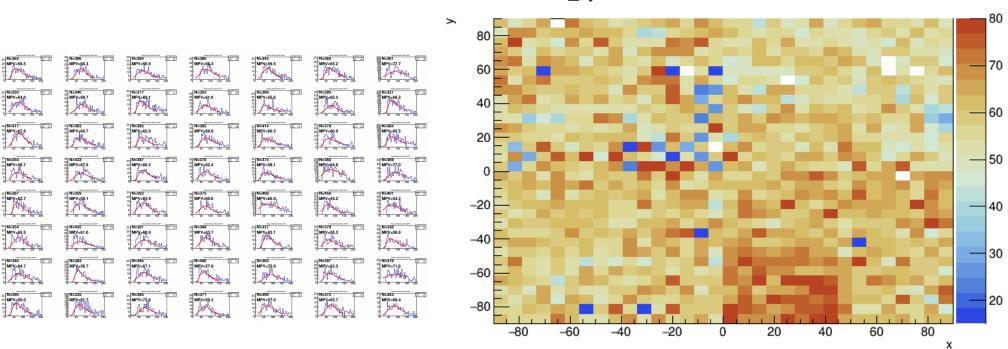

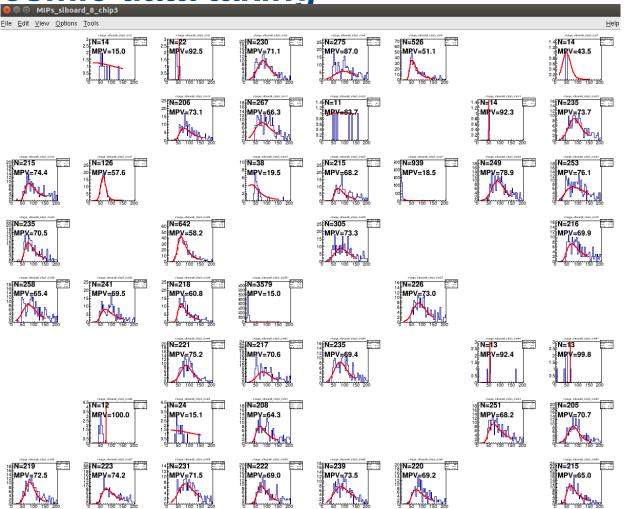

### FEV12: Results of the cosmic run

SLAB 25 (24 is very similar)

20 MPV=64.0

MPV=58.7

Quite homogeneous response

MIPM\_xy

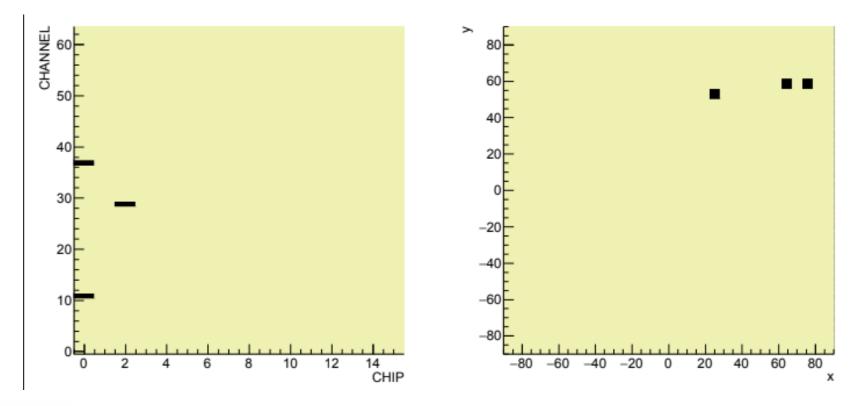

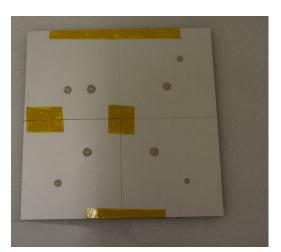

### **COB: Results of the masking procedure**

SLAB 27 (28 is very similar)

11<sup>th</sup> February 2020

- black is masked

- Remember: the wafer is partially disconnected from the PCB

### **COB: Results of the cosmic data taking**

- SLAB 27 (28 is very similar)

- black is masked

- Remember: the wafer is partially disconnected from the PCB

- Some cosmics... more than I expected after the beating that the board has suffered

- In some cases, we recover the PAD-Wafer contact by mechanical pressure!

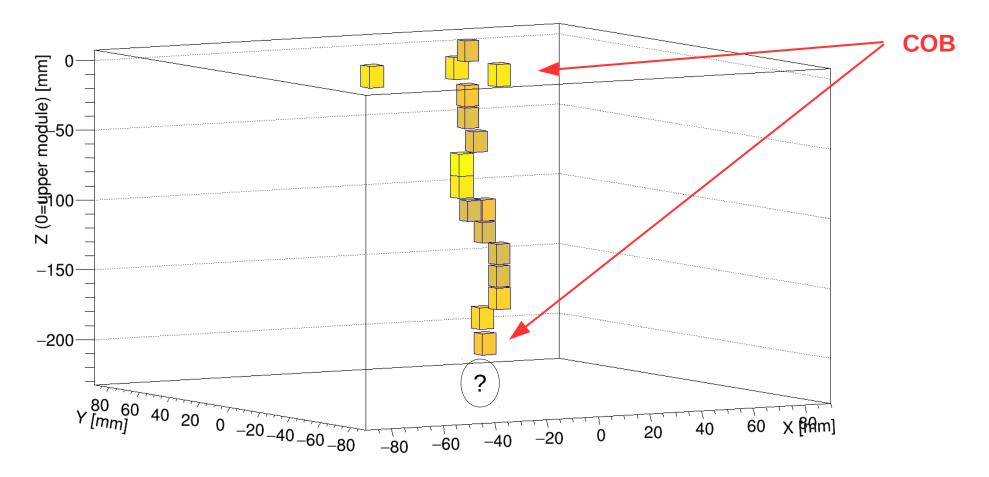

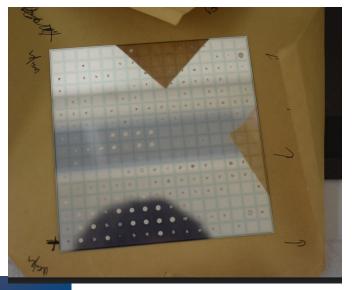

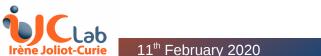

### A very bad FEV11 → slab 17

### SLAB 17 (FEV11)

- Travel Europe/Japan several times

- Arrived to France just before the quarantine. After several days in customes it arrived to France very well packed and protected.

- However... the wafers were simply partially dettached from the PCB. One of them was completely dettached.

11<sup>th</sup> February 2020

- Some bricolage done trying to recover it...

- It is not broken but only few channels are connected.

MIPN

### **Standard FEV10/11: Results of the masking procedure**

#### SLAB 19 (FEV11)

- black is masked

- Crosses are around the channel 37

- Basically the same channels that were masked for TB2017  $\,\rightarrow\,$

- But few more because we more conservative for cosmic data taking.

### **Standard FEV10/11: Results of the masking procedure**

#### SLAB 19 (FEV11)

Satisfactory results of the cosmic run for most of the slabs

Lower performance on the edges of some boards? Effect seen in the past in several slabs (TB2018 CERN)

- Worsten wafer adherence? (i.e. glue aging issue)?

- Or ust a noise/signal competition issue ?  $\rightarrow$  Remember that the ASICs near the connectors are historically the ones much noise sensitive

15

### A very good FEV10: Results of the masking procedure

- SLAB 23, SK2, 320um

- Never connected to a DAQ interface before

- Similar performance than the FEV12

MIPN

х

### A very good FEV10: Results of the masking procedure

- SLAB 23, SK2, 320um

- Never connected to a DAQ interface before

- Similar performance than the FEV12

- Why? Only difference with the FEV11s is on the decoupling capacitances

- 68uF for DVDD

- Instead of 33uF in the other FEV10/11

- Instead of 120uF in the FEV12

Components in the ASU

Photos : CHIP capacitances

- Can we further optimize the decoupling capacitances?

- To be tested this afternoon

#### Comments

120uF for AVDD, 68uF for DVDD in all ASICS

Other components : C14, C25, C24, C23, C22, R1, C20, C21 (all chips)

### **Comments on the masking procedure**

- ▶ We are masking between 3-20 % of the channels

- ► THIS IS FOR COSMICS!

- In the first part of the commissioning (the one that assumes short acquisitions and high rates) we expect to mask the same channels than in 2017 (~5%)

- For the FEV10/11

- The good FEV10 and the good FEV12 have almost no masking done at this phase (~1% or lower)

### Next steps towards the beam test (1)

11<sup>th</sup> February 2020

- Produce the patch pannel

- On stand-by because of the quarantine

- Quick tests today on the difference of performance using different values of decoupling capacitances on DVDD

- If we see that the noise conditions improve considerably...

- ... do we want to modify the existing slabs? Yes if the interventions are minimal?

- Incremental optimizations on the mechanical structure

- i.e. adapt the cover to the "thicker than expected" HV cables

19

### Next steps towards the beam test (2)

- Continue with the data taking and give continuous feedback to the experts

- To check the performance stability and/or spot unforeseen issues

- So far the DAQ software crashed only when I did something stupid...

### Data taking Ideas:

- Study in more detail the time correlations...

- Prepare more DQ tools

- i.e. even some tracking/event displays

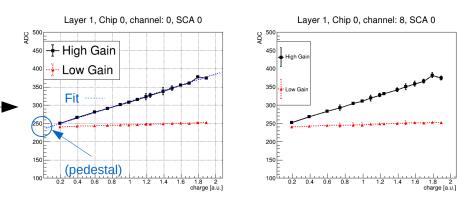

- Linearity /pedestal studies

- I took enough data to repeat these studies systematically

- Volunteers to analyze the data?

- We can compare the forced trigger pedestal with the autotrigger pedestal and this one with the pedestal measured by linearity checks...