# Parylene coating for hybrid pixel module on single chip card

M. Bomben – LPNHE & Univ. de Paris

#### Introduction

- In what follows I first give some background information on our problematic

- Material is taken from internal documentation

- Then I will show pictures and schematics of

- The hybrid module to be coated with parylene

- The card and the connectors to be masked

#### Motivation and information

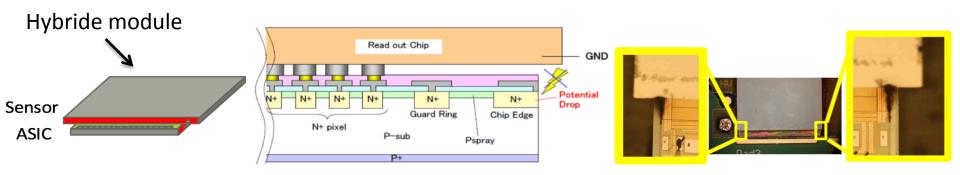

- The issue of high voltage operation is discharge. Discharge has

occurred at the edge of sensor and ASIC. To avoid the discharge, we

plan to do a Parylene (Type N) coating after the module assembly.

- See also next slide

- Type-C has halogen, chlorine, it might cause pollution. Thus, we chose the parylene type N as a baseline for parylene material.

# High voltage issue

Figure 1: Left) A schematic view of a hybrization. Center) Discharge will occur with high voltage due to the difference in potential of the sensor and the ASIC surfaces. Right) Example of discharged module. Obviously it was happened at the edge of both.

#### **Thickness**

- A HV tolerance of parylene coating is 1,000 V / 5  $\mu$ m, thus, more than 5  $\mu$ m is thick enough to prevent discharge. Target thickness is considered two variations. One is 5  $\mu$ m to be minimum for HV tolerance. Other is 20  $\mu$ m to do complete underfilling the gap between the sensor and the ASIC. We will decide the thickness by further studies.

- Plus: no significant bump disconnections were observed with 6-μmthick parylene coating

- Final thickness will be decided later (studies on-going).

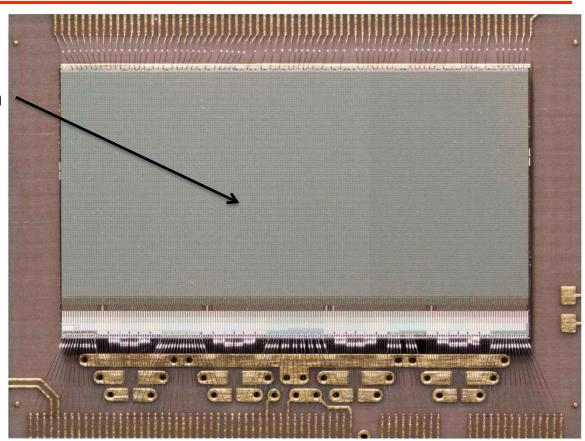

# Chip and wirebonding picture

The chip size is 20.0 mm by 11.8 mm

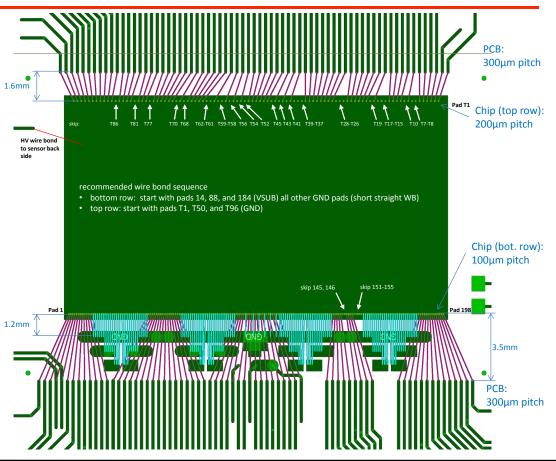

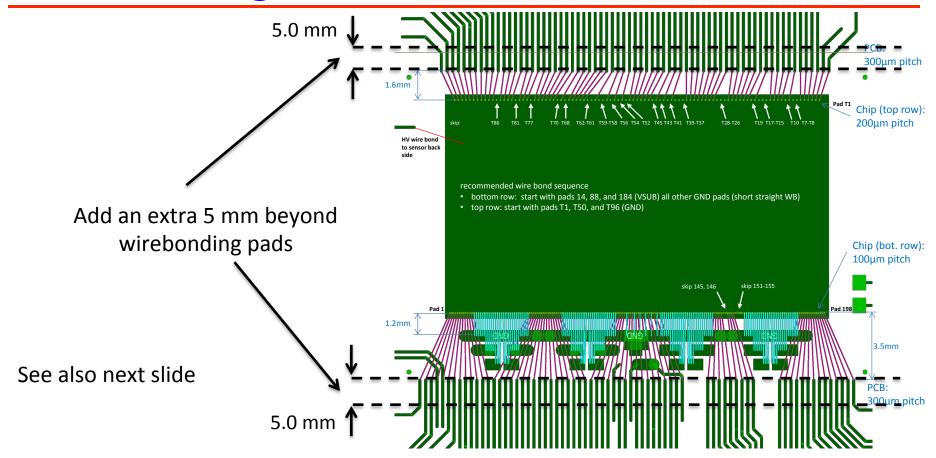

#### Wirebonding schematics and dimensions

### Wirebonding schematics

#### Wirebonding clearance

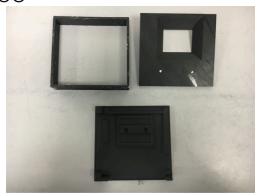

#### **Masking with 3D printed parts**

of 5mm or so for the UK FE-I4 flex modules

RD53 SCC's (see attached). It wasn't exact as it involved the placement of a mask by hand which was also affected by the way the chip was attached i.e. screws with nuts and CF required the mask to be offset sometimes.

RD53A SCC

- 3D printed masks for protection of connectors and jumpers from parylene ingress

- Onyx material (nylon + carbon fibre strands) used with Markforger 3D printer

- Small masks with wall thickness of a few mm's has worked well with many FE-I4 flex modules shown above

- Large 3D printed box for masking single chip cards before irradiation seem to cause lots of outgassing in the chamber

Jon 28/4/2020

J.Taylor 22/01/20

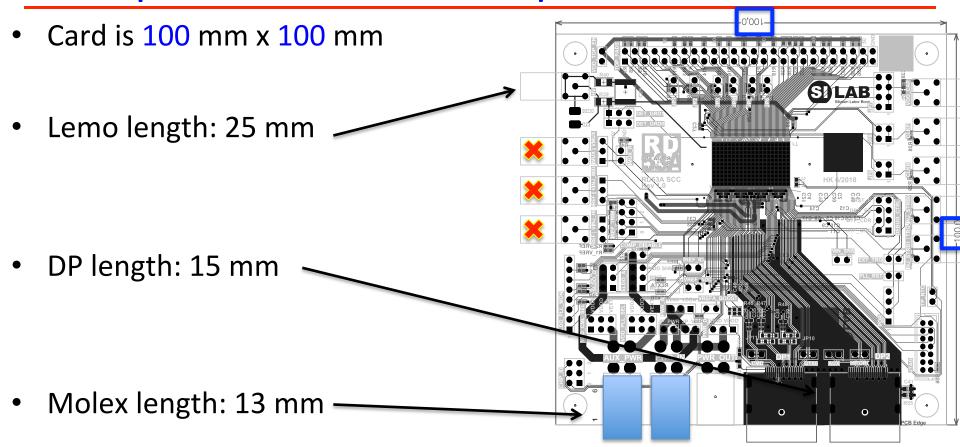

# Card plus connectors footprint

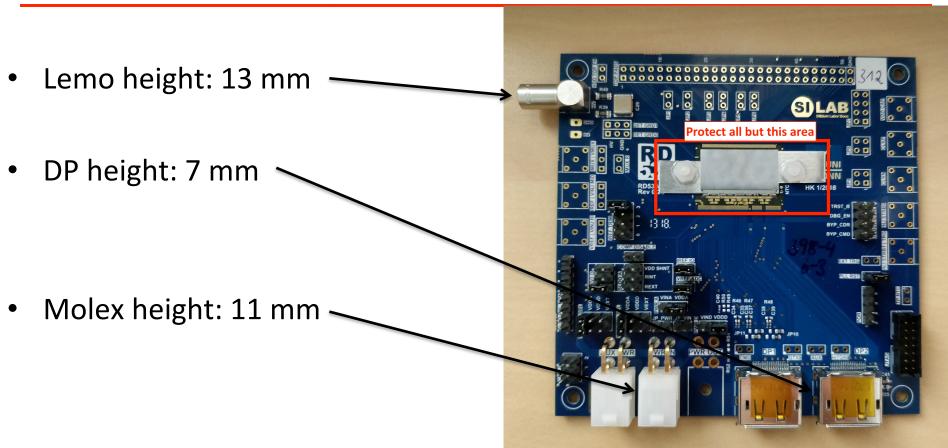

### Connectors height